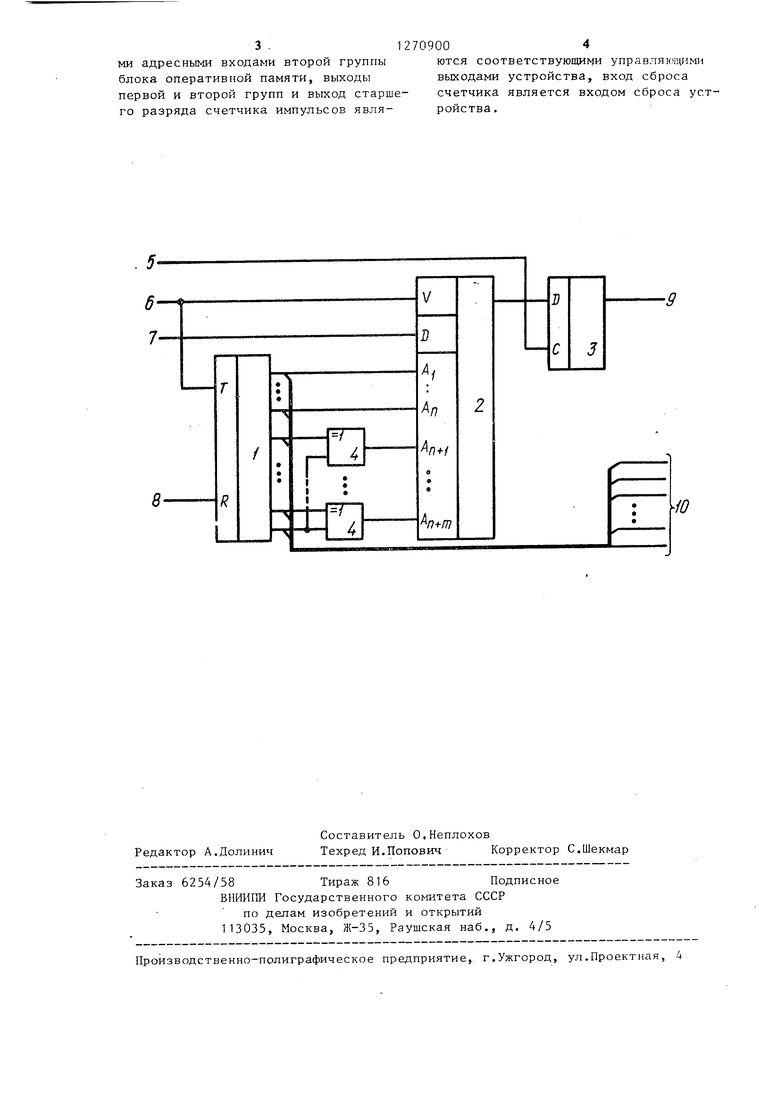

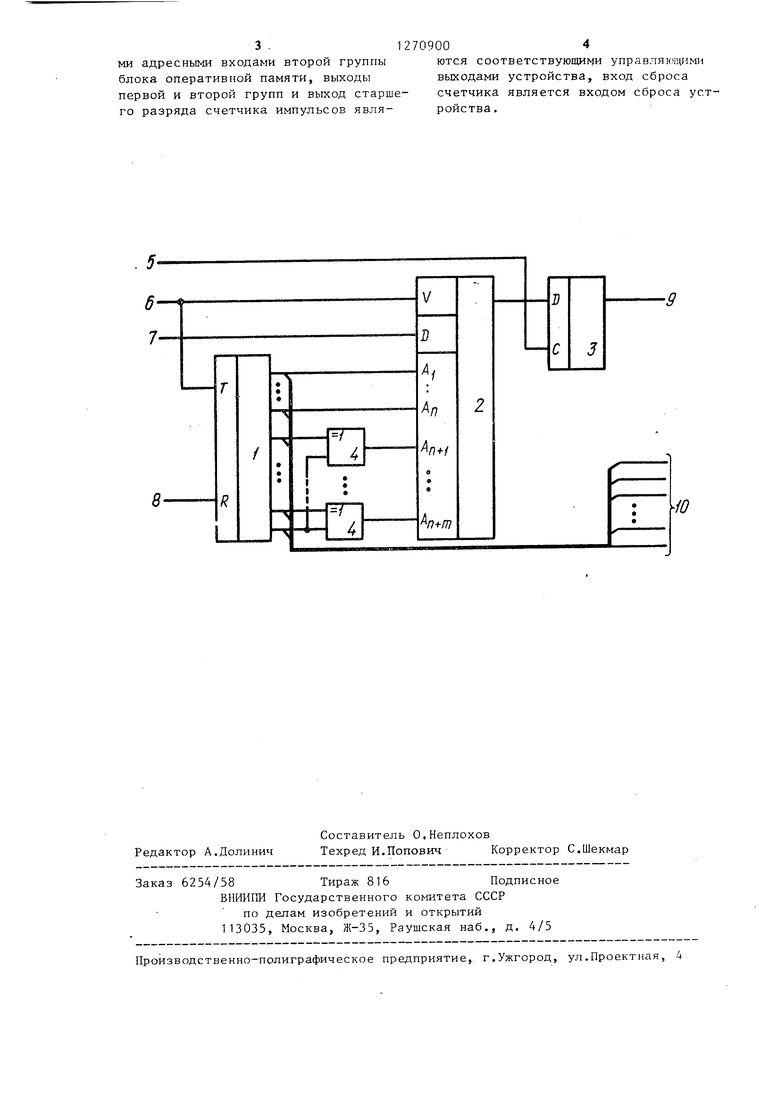

Изобретение относится к вычислительной те- хнике и может быть использовано для преобразования кодов, изменяющих по-рядок. следования разрядов Целью изобретения является расширение функциональных возможностей устройства за счет изменения порядка следования разряда кода. На чертеже представлена структур,ная схема устройства. Устройство Содержит счетчик 1 импульсов, блок 2 оперативной памяти, D-триггер. ,3, элементы 4 ИСКЛЮЧАЮЩЕЕ -ШИ, первый тактовый вход 5 устройства, второй тактовый вход 6 устройства, информационный вход 7 устройства, вход 8 сброса устройства, информационньй выход 9 устройства, управляющие выходы 10 устройства. Устройство работает следующим образом. Перед подачей преобразуемого кода на вход блока 2 оперативной памяти на счетчик 1 импульсов подается сигнал, приводящий его в нулевое состояние. В процессе преобразования синхронно с разрядами последовательного кода, поступающего на вход блока 2 оперативной записи, подаются импульсы на счетный вход счет чика 1 импульсов и вход записи блока 2 оперативной памяти с первого тактового входа 5 устройства, таким образом, что для каходой комбинации сигналов на выходах счетчика 1 импульсов., определяющей адрес ячейки памяти блока 2 оперативной памяти, сначала производится считывание содержимого соответствующей ячейки па мяти, а затем запис ь нового значения в нее. В промежутках между тактовыми импульсами, поступающими на первый тактовый вход 5 устройства, на второй в тактовый вход 6 устройства подаются импульсы, обеспечивающие запоминание считываемой из ячейки информации в D-триггере 3, на время д следующего такта считывания. В том случае, если необходимо из менить порядок следования всех разрядов, например 8-разрядного кода н обратньм, выходы первых трех разрядов составляющих вторую группу счет чика импульсов подключаются к первы входам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых подключаются к выходу четвертого (старшего) разряд счетчика. В результате при нулевом 02 значении четвертого разряда счетчика 1 импульсов адресация блока 2 оперативной памяти монотонно увеличивается, в то время, как при единичном значении чегтвертого разряда счетчика 1 импульсов она монотонно убывает. Этим достигается то, что при считывании разрядов входного кода их порядок следования меняется на обратный. В том случае, если к первой группе входов .отнесены выходы первого и второго разрядов счетчика 1 импульсов, которые подключаются к адресным входам блока 2 оперативной памяти непосредственно, а ко второй группе - выход третьего разряда устройство будет производить перестановку тетрад кодов, а последовательность разрядов внутри тетрад не изменится , Производя различные разбиения выкодов счетчика 1 импульсов на первую и вторую группы, можно получить различные варианты изменения следования разрядов входного кода. Формула изобретения Устройство для преобразования последовательного кода в код, состоящее из счетчика импульсов, первая группа выходов которого соединена с соответствующими адресными входами первой группы блока оперативной памяти, информационный вход которого является информационным входом устройства, вход записи объединен со счетным входом счетчика импульсов и подключен к первому тактовому входу устройства, отличающееся тем, что, с целью расщирения функциональных возможностей устройства за счет изменения порядка следования разрядов кода, в него введены элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и D-триггер, выход которого является информационным выходом устройства, вход подключен к вькоду блока оперативной памяти, синхровход является вторым тактовым входом устройства, выходы второй группы счетчика импульсов подключены к первым входам соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых объединены и подключены к выходу старшего разряда счетчиков импульсов, выходы злементов ИСКЛЮЧАЩЕЕ ИЛИ соединены с соответствующими адресными входами второй группы блока оперативной памяти, выходы первой и второй групп и выход старшего разряда счетчика импульсов являются соответствующими управляющими выходами устройства, вход сброса счетчика является входом сброса устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования последовательного кода | 1988 |

|

SU1640827A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

| Преобразователь кодов | 1988 |

|

SU1644124A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Преобразователь двоичного кода | 1984 |

|

SU1208607A1 |

| Устройство для формирования характеристических матриц | 1988 |

|

SU1596334A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Устройство для отображения информации | 1989 |

|

SU1695373A1 |

Изобретение относится к вычиспительной технике и быть использовано для преобразований кодов, изменяющих порядок следования разрядов. Изобретение позволяет расширить функциональные возможности устройства за счет изменения порядка следования разрядов кода. Устройство содержит счетчик импульсов, блок оперативной памяти, триггеру элементы ИСКПЮЧАНЩЕЕ ИЛИ. 1 ил.

| Устройство для преобразования двоичного кода | 1975 |

|

SU557360A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровые фильтры в электросвязи и радиотехнике./Под ред | |||

| Гольденберга Л.М., М.: Радио и связь, 1982, с | |||

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-11-15—Публикация

1985-02-19—Подача