ИзоС метение относится к области вы- числител ной и информационно-измерительной техники и может быть использовано при измерениях физических величин и параметров случайных процессов

Цель изобретения - повышение точности работы в реальном масштабе времени.

Сущность устройства заключается в следующем

Устройство осуществляет вычисление оценки ты математического ожидания m по мере поступления на вход устройства величин XN, которые равны

XN mn-ЈN , N- 1.2 ...(1)

где Јм - независимые одинаково распределенные случайные величины с нулевым средним.

При этом предполагается, что известна априорная информация о плотности распределения вероятностей Јi в виде нескольких первых моментов а , )1г плотности.

Тогда оценка ты вычисляется при поступлении каждого значения XN по следующей рекуррентной формуле:

mN +ON А

Мы Щы - IOM (ты ), mi о ; (2) ты ты-1- X.aJN(xN-mN -1 У -Oj

где N - номер очередного значения величины

ты - рекуррентная оценка среднего арифметического из N значений xi: ты - 1 -XN

О

I

СЈ

ты ты - 1 -

N

mi

(3)

z) - функция ограничения

z , а$

iЈ( a. b, ,

(4)

ON - величина порога ограничения. О /2;(5)

ajN - коэффициенты, определяемые при поступлении каждого значения XN из следующей системы линейных уравнений:

о

aiN tfll +32N (712 + ... farN O lr -А-ОЬо

о aiN «21 + a2N 022 + .... + агМ О2г - 2 А-ОЮ

aiN Ori + a2N 0r2 +.... + arN Orr -rA-Oj--10

ооо

aiN ObO + 2 + .... + r.arN Or - 10 - 1

(6)

В этой системе r+1 уравнений приняты следующие обозначения:

о о о

, I oik-OI Ok при l + k$r (7) Oi«) о№npni + k г,

k 0i+k M|ii- априорно известные центральные моменты:

15

20

СП М Јi 0 , оз М i-vO ,

02 М $ - Atf-1 ° - (xN-mNN

02 м fi ; г- номер наивысшего известного центрального момента;

Д- вспомогательный параметр:

oft - рекуррентная оценка центрального момента, полученная при поступлении очередного значения хм:

.:+ЈО О

-iy+K + arOk

(8)

В соответствии с изложенным, алгоритм работы устройства заключается в следующем.

На вход устройства поступает очеред- ное N-e значение XN.

По формуле (3) уточняется оценка среднего арифметического.

По формуле (8) уточняются оценки центральных моментов,

Вычисляются коэффициенты из системы уравнений (6).

По формуле (2) вычисляется новое значение оценки математического ожидания. Эта оценка стремится с ростом N к оптимальной, т.е. она обеспечивает асимптотически наилучшую точность при заданной априорной информации.

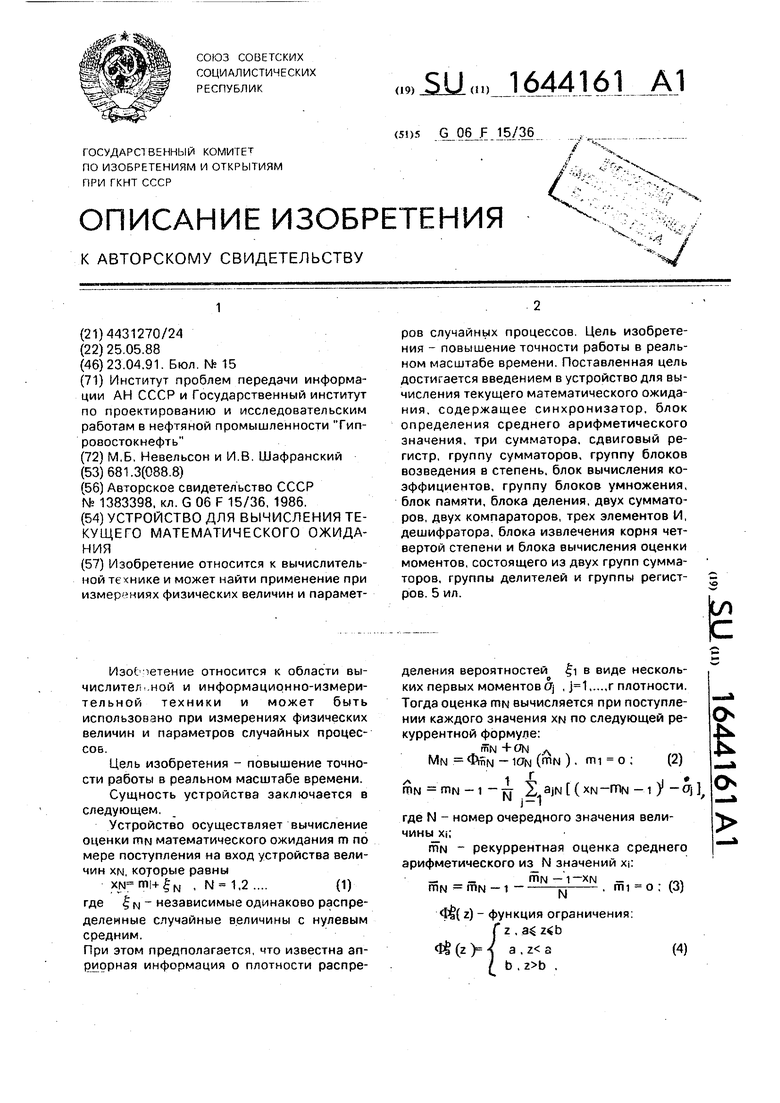

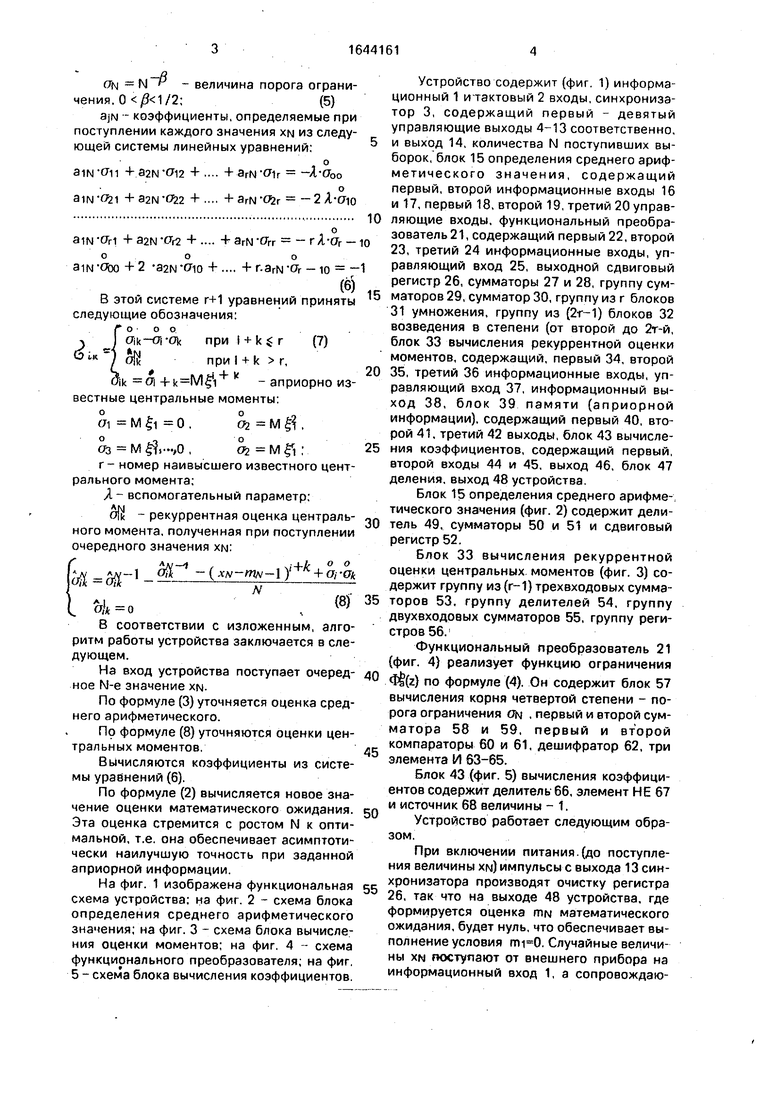

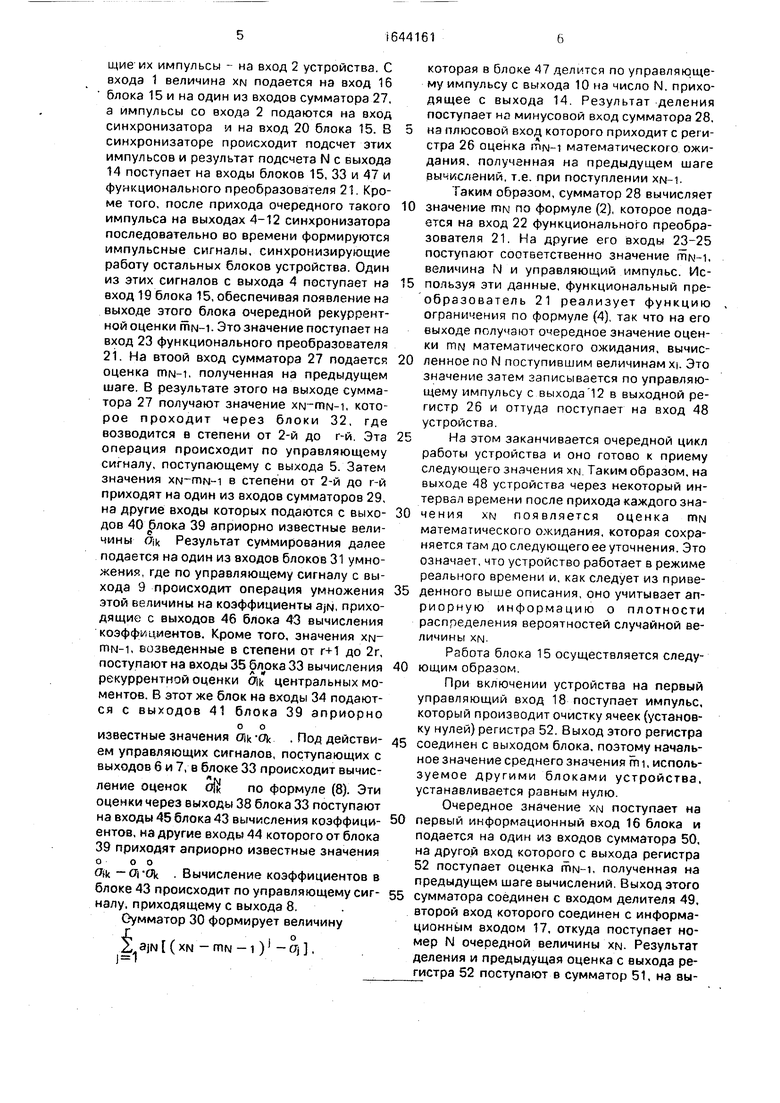

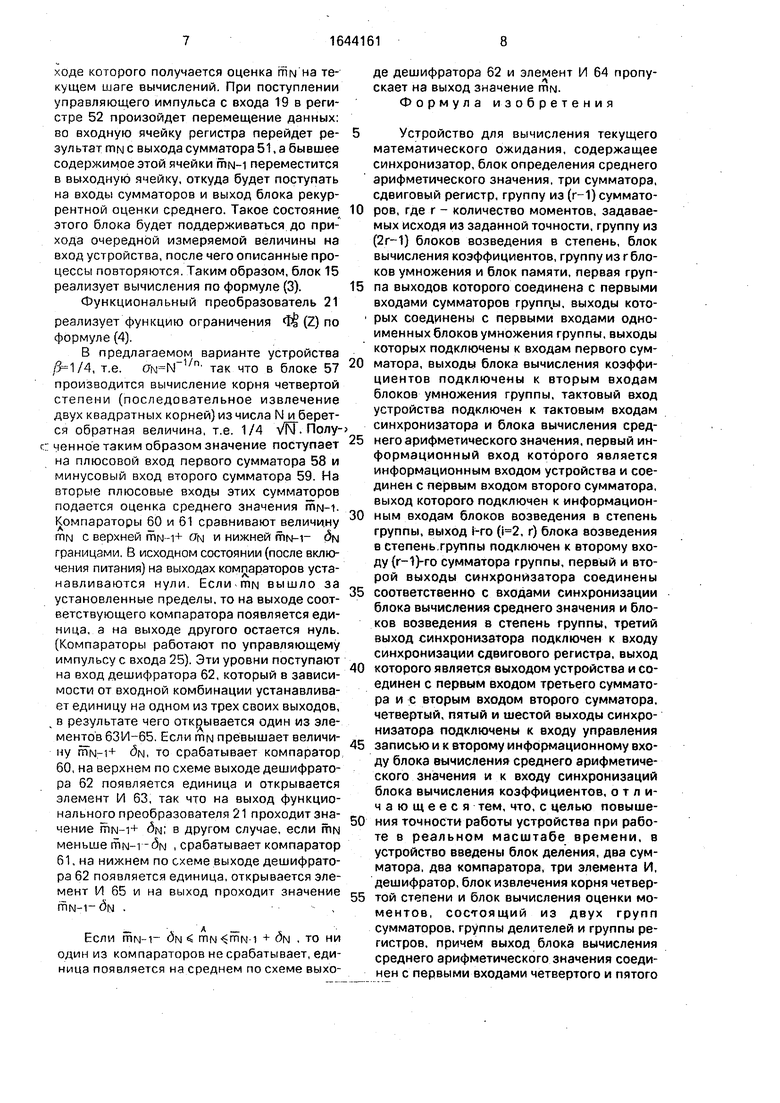

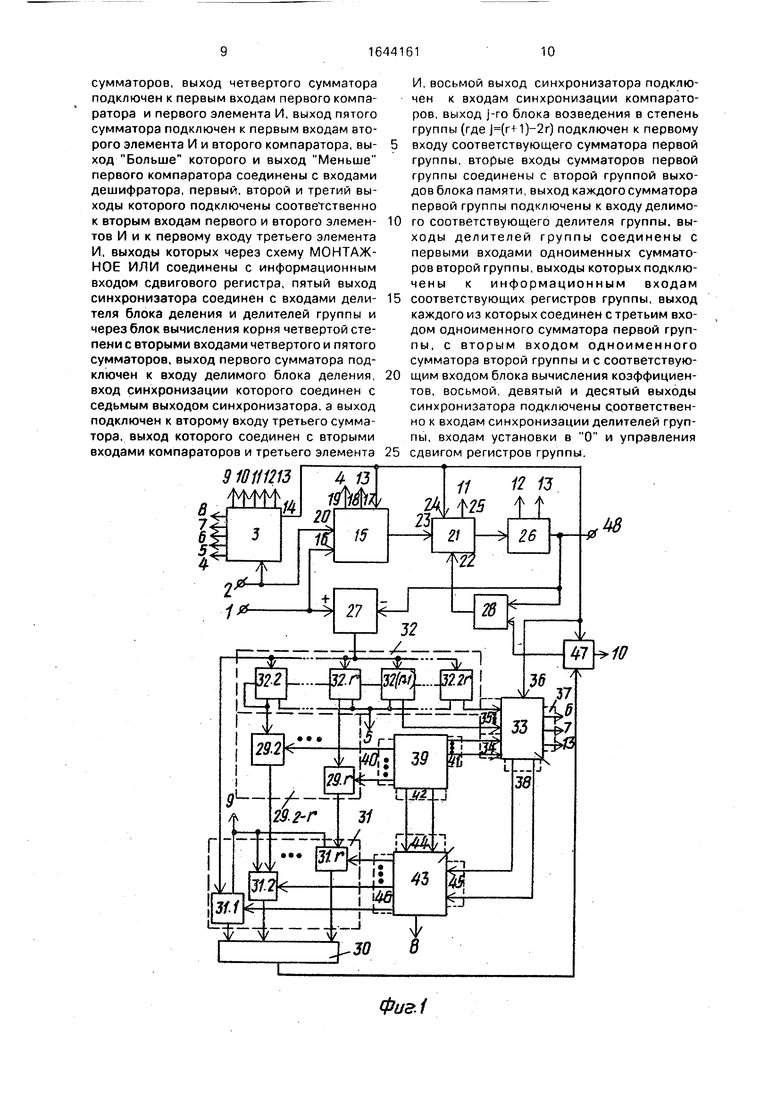

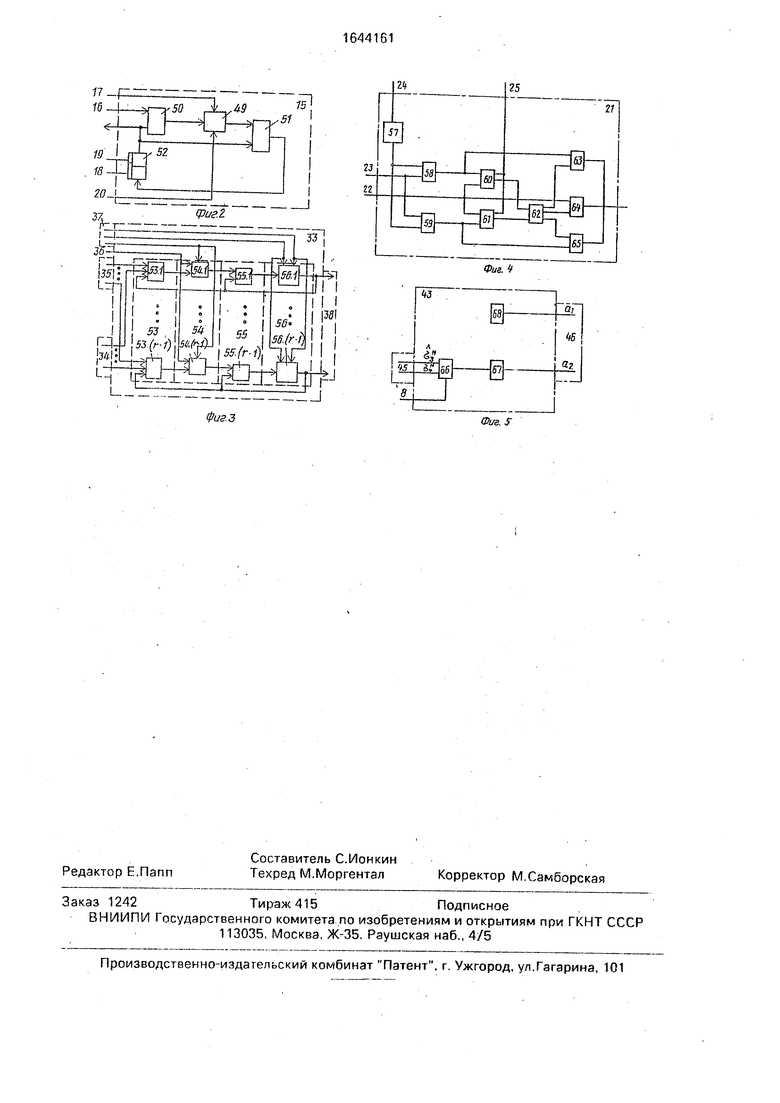

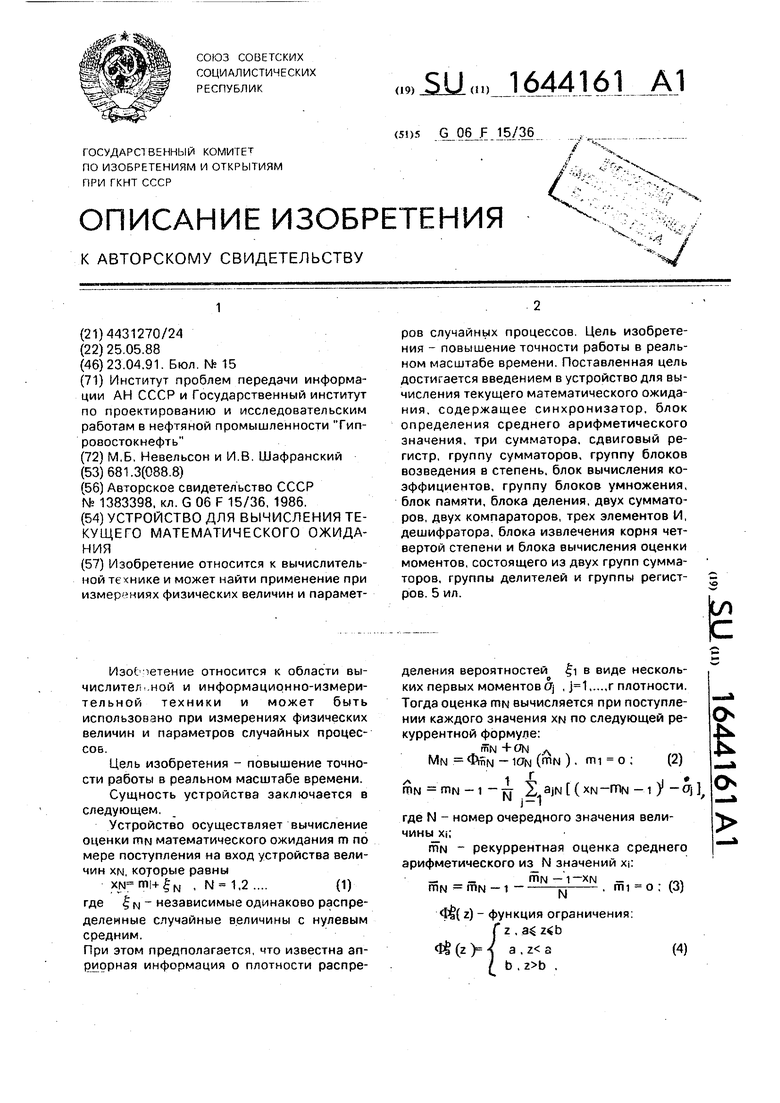

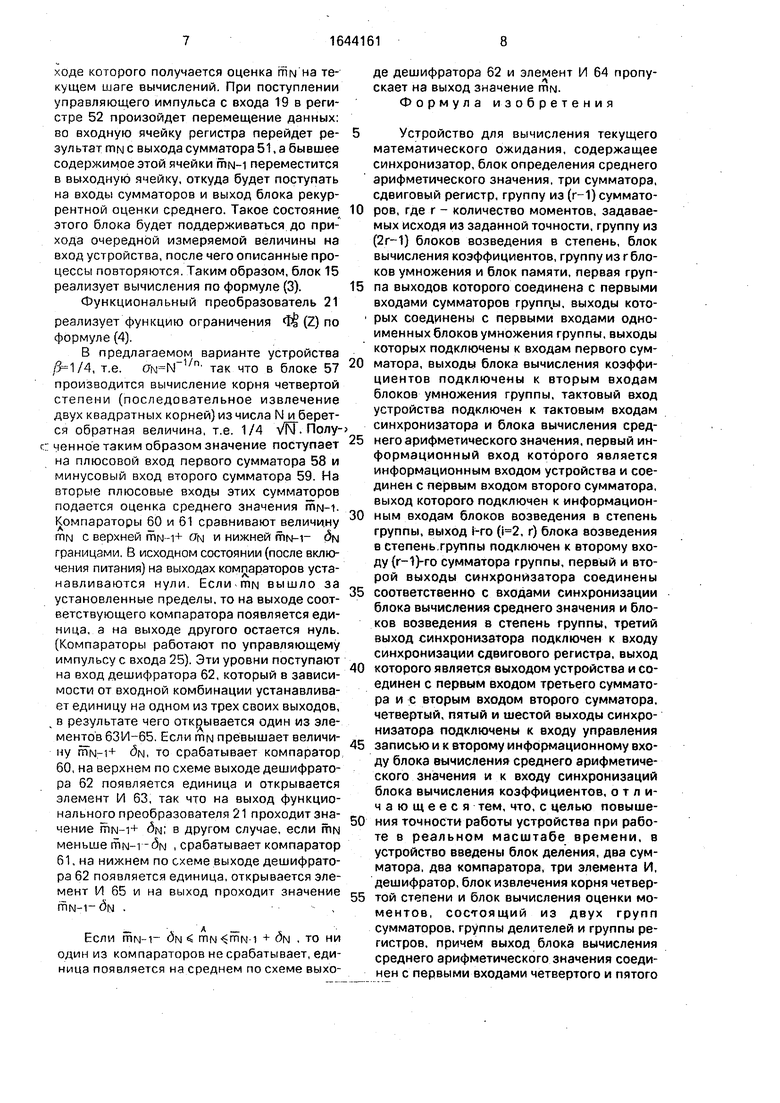

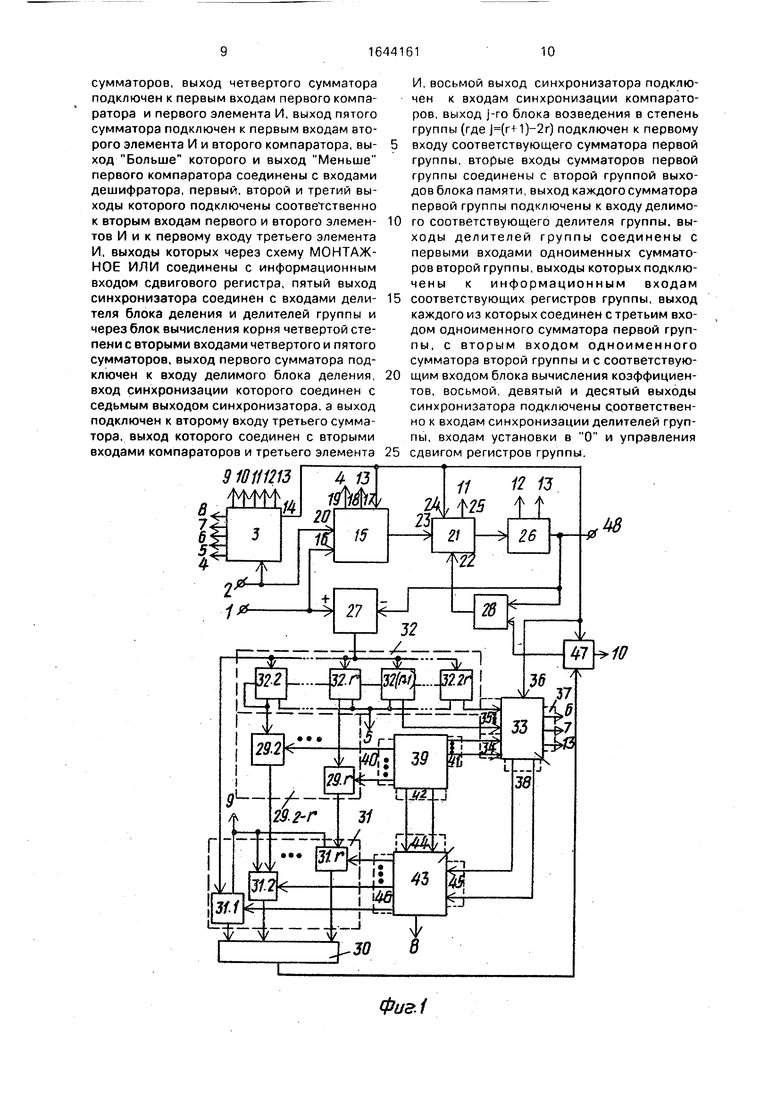

На фиг. 1 изображена функциональная схема устройства: на фиг. 2 - схема блока определения среднего арифметического значения; на фиг. 3 - схема блока вычисления оценки моментов; на фиг. 4 -- схема функционального преобразователя; на фиг, 5 - схема блока вычисления коэффициентов.

0

5

0

5

0

5

0

5

0

g5

Устройство содержит (фиг. 1) информационный 1 итактовый 2 входы,синхронизатор 3, содержащий первый - девятый управляющие выходы 4-13 соответственно, и выход 14, количества N поступивших выборок, блок 15 определения среднего арифметического значения, содержащий первый, второй информационные входы 16 и 17, первый 18, второй 19, третий 20 управляющие входы, функциональный преобразователь 21, содержащий первый 22, второй 23, третий 24 информационные входы, управляющий вход 25, выходной сдвиговый регистр 26, сумматоры 27 и 28, группу сумматоров 29, сумматор 30, группу из г блоков 31 умножения, группу из (2г-1) блоков 32 возведения в степени (от второй до 2т-й, блок 33 вычисления рекуррентной оценки моментов, содержащий, первый 34, второй 35, третий 36 информационные входы, управляющий вход 37, информационный выход 38, блок 39 памяти (априорной информации), содержащий первый 40, второй 41, третий 42 выходы, блок 43 вычисления коэффициентов, содержащий первый, второй входы 44 и 45, выход 46, блок 47 деления, выход 48 устройства.

Блок 15 определения среднего арифме-, тического значения (фиг. 2) содержит делитель 49, сумматоры 50 и 51 и сдвиговый регистр 52.

Блок 33 вычисления рекуррентной оценки центральных моментов (фиг. 3) содержит группу из (г-1) трехвходовых сумматоров 53, группу делителей 54, группу двухвходовых сумматоров 55, группу регистров 56.

Функциональный преобразователь 21 (фиг. 4) реализует функцию ограничения

ф|(г) по формуле (4). Он содержит блок 57 вычисления корня четвертой степени - порога ограничения ом , первый и второй сумматора 58 и 59, первый и второй компараторы 60 и 61, дешифратор 62, три элемента И 63-65.

Блок 43 (фиг. 5) вычисления коэффициентов содержит делитель 66, элемент НЕ 67 и источник 68 величины - 1.

Устройство работает следующим образом.

При включении питания.(до поступления величины XN) импульсы с выхода 13 синхронизатора производят очистку регистра 26, так что на выходе 48 устройства, где формируется оценка ты математического ожидания, будет нуль, что обеспечивает выполнение условия . Случайные величины XN поступают от внешнего прибора на информационный вход 1, а сопровождающие их импульсы - на вход 2 устройства. С входа 1 величина XN подается на вход 16 блока 15 и на один из входов сумматора 27, а импульсы со входа 2 подаются на вход синхронизатора и на вход 20 блока 15. В синхронизаторе происходит подсчет этих импульсов и результат подсчета N с выхода 14 поступает на входы блоков 15, 33 и 47 и функционального преобразователя 21. Кроме того, после прихода очередного такого импульса на выходах 4-12 синхронизатора последовательно во времени формируются импульсные сигналы, синхронизирующие работу остальных блоков устройства. Один из этих сигналов с выхода 4 поступает на вход 19 блока 15, обеспечивая появление на выходе этого блока очередной рекуррентной оценки гпм-1. Это значение поступает на вход 23 функционального преобразователя 21. На втоой вход сумматора 27 подается оценка mw-1, полученная на предыдущем шаге. В результате этого на выходе сумматора 27 получают значение , которое проходит через блоки 32, где возводится в степени от 2-й до r-й. Эта операция происходит по управляющему сигналу, поступающему с выхода 5. Затем значения хы гпм-1 в степени от 2-й до г-й приходят на один из входов сумматоров 29, на другие входы которых подаются с выходов 40 блока 39 априорно известные величины Oii Результат суммирования далее подается на один из входов блоков 31 умножения, где по управляющему сигналу с выхода 9 происходит операция умножения этой величины на коэффициенты а$м, приходящие с выходов 46 блока 43 вычисления коэффициентов. Кроме того, значения XN miM-1, возведенные в степени от г+1 до 2г, поступают на входы 35 блока 33 вычисления рекуррентной оценки oik центральных моментов. В этот же блок на входы 34 подаются с выходов 41 блока 39 априорно о о

известные значения oik Ok .Под действием управляющих сигналов, поступающих с выходов б и 7, в блоке 33 происходит вычис«.

ление оценок щ по формуле (8). Эти оценки через выходы 38 блока 33 поступают на входы 45 блока 43 вычисления коэффициентов, на другие входы 44 которого от блока 39 приходят априорно известные значения о о о

Oik - О -Ok . Вычисление коэффициентов в блоке 43 происходит по управляющему сигналу, приходящему с выхода 8.

Сумматор 30 формирует величину

. о

ajN ( XN - mw - i) - oj ,

}

,1

которая в блоке 47 делится по управляющему импульсу с выхода 10 на число N. приходящее с выхода 14. Результат деления поступает на минусовой вход сумматора 28, 5 на плюсовой вход которого приходит с регистра 26 оценка тм-1 математического ожидания, полученная на предыдущем шаге вычислений, т.е. при поступлении XN-L Таким образом, сумматор 28 вычисляет

0 значение по формуле (2), которое подается на вход 22 функционального преобразователя 21. На другие его входы 23-25 поступают соответственно значение тм-1. величина N и управляющий импульс. Ис5 пользуя эти данные, функциональный преобразователь 21 реализует функцию ограничения по формуле (4), так что на его выходе получают очередное значение оценки ITIN математического ожидания, вычис0 ленное по N поступившим величинам xi. Это значение затем записывается по управляющему импульсу с выхода 12 в выходной регистр 26 и оттуда поступает на вход 48 устройства.

5На этом заканчивается очередной цикл

работы устройства и оно готово к приему следующего значения XN Таким образом, на выходе 48 устройства через некоторый интервал времени после прихода каждого зна0 чения XN появляется оценка глм математического ожидания, которая сохраняется там до следующего ее уточнения. Это означает, что устройство работает в режиме реального времени и, как следует из приве5 денного выше описания, оно учитывает априорную информацию о плотности распределения вероятностей случайной величины XN

Работа блока 15 осуществляется следу0 ющим образом.

При включении устройства на первый управляющий вход 18 поступает импульс, который производит очистку ячеек (установку нулей) регистра 52. Выход этого регистра

5 соединен с выходом блока, поэтому начальное значение среднего значения mi, используемое другими блоками устройства, устанавливается равным нулю.

Очередное значение XN поступает на

0 первый информационный вход 16 блока и подается на один из входов сумматора 50, на другой вход которого с выхода регистра 52 поступает оценка ты-1, полученная на предыдущем шаге вычислений. Выход этого

5 сумматора соединен с входом делителя 49, второй вход которого соединен с информационным входом 17, откуда поступает номер N очередной величины XN. Результат деления и предыдущая оценка с выхода регистра 52 поступают в сумматор 51, на выходе которого получается оценка ты на текущем шаге вычислений. При поступлении управляющего импульса с входа 19 в регистре 52 произойдет перемещение данных: во входную ячейку регистра перейдет результат ты с выхода сумматора 51, а бывшее содержимое этой ячейки гпм-1 переместится в выходную ячейку, откуда будет поступать на входы сумматоров и выход блока рекуррентной оценки среднего. Такое состояние этого блока будет поддерживаться до прихода очередной измеряемой величины на вход устройства, после чего описанные процессы повторяются. Таким образом, блок 15 реализует вычисления по формуле (3).

Функциональный преобразователь 21

реализует функцию ограничения Ф| (Z) по формуле (4).

В предлагаемом варианте устройства , т.е. так что в блоке 57 производится вычисление корня четвертой степени (последовательное извлечение двух квадратных корней) из числа N и берется обратная величина, т.е. 1/4 VhT. Полу-; ценное таким образом значение поступает на плюсовой вход первого сумматора 58 и минусовый вход второго сумматора 59. На вторые плюсовые входы этих сумматоров подается оценка среднего значения тм-1. Компараторы 60 и 61 сравнивают величину ты с верхней тм -1+ ON и нижней ты-г- дм границами. В исходном состоянии (после включения питания) на выходах компараторов устанавливаются нули Если ITIN вышло за установленные пределы, то на выходе соответствующего компаратора появляется единица, а на выходе другого остается нуль. (Компараторы работают по управляющему импульсу с входа 25). Эти уровни поступают на вход дешифратора 62, который в зависимости от входной комбинации устанавливает единицу на одном из трех своих выходов, в результате чего открывается один из элементов 63И-65. Если тм превышает величину ты-1+ дп, то срабатывает компаратор

60,на верхнем по схеме выходе дешифратора 62 появляется единица и открывается элемент И 63, так что на выход функционального преобразователя 21 проходит значение гпм-1+ 5м; в другом случае, если ты меньше тм-1 -им , срабатывает компаратор

61,на нижнем по схеме выходе дешифратора 62 появляется единица, открывается элемент И 65 и на выход проходит значение гпм-1-dN .

Если fnN-i- ды mivKrnN 1 + дм , то ни один из компараторов не срабатывает, единица появляется на среднем по схеме выходе дешифратора 62 и элемент И 64 пропускает на выход значение .

Формула изобретения

Устройство для вычисления текущего

математического ожидания, содержащее синхронизатор, блок определения среднего арифметического значения, три сумматора, сдвиговый регистр, группу из (г-1)сумматоров, где г - количество моментов, задаваемых исходя из заданной точности, группу из (2г-1) блоков возведения в степень, блок вычисления коэффициентов, группу из г блоков умножения и блок памяти, первая группа выходов которого соединена с первыми входами сумматоров групп.ы, выходы кото- рых соединены с первыми входами одноименных блоков умножения группы, выходы которых подключены к входам первого сумматора, выходы блока вычисления коэффициентов подключены к вторым входам блоков умножения группы, тактовый вход устройства подключен к тактовым входам синхронизатора и блока вычисления среднего арифметического значения, первый ин- формационный вход которого является информационным входом устройства и соединен с первым входом второго сумматора, выход которого подключен к информационным входам блоков возведения в степень группы, выход 1-го (, г) блока возведения в степень группы подключен к второму входу {г-1)-го сумматора группы, первый и второй выходы синхронизатора соединены

соответственно с входами синхронизации блока вычисления среднего значения и блоков возведения в степень группы, третий выход синхронизатора подключен к входу синхронизации сдвигового регистра, выход

которого является выходом устройства и соединен с первым входом третьего сумматора и с вторым входом второго сумматора, четвертый, пятый и шестой выходы синхронизатора подключены к входу управления

записью и к второму информационному входу блока вычисления среднего арифметического значения и к входу синхронизации блока вычисления коэффициентов, отличающееся тем, что, с целью повышения точности работы устройства при работе в реальном масштабе времени, в устройство введены блок деления, два сумматора, два компаратора, три элемента И, дешифратор, блок извлечения корня четвертой степени и блок вычисления оценки моментов, состоящий из двух групп сумматоров, группы делителей и группы регистров, причем выход блока вычисления среднего арифметического значения соединен с первыми входами четвертого и пятого

сумматоров, выход четвертого сумматора подключен к первым входам первого компаратора и первого элемента И, выход пятого сумматора подключен к первым входам второго элемента И и второго компаратора, вы- ход Больше которого и выход Меньше первого компаратора соединены с входами дешифратора, первый, второй и третий выходы которого подключены соответственно к вторым входам первого и второго элемен- тов И и к первому входу третьего элемента И, выходы которых через схему МОНТАЖНОЕ ИЛИ соединены с информационным входом сдвигового регистра, пятый выход синхронизатора соединен с входами дели- теля блока деления и делителей группы и через блок вычисления корня четвертой степени с вторыми входами четвертого и пятого сумматоров, выход первого сумматора подключен к входу делимого блока деления, вход синхронизации которого соединен с седьмым выходом синхронизатора, а выход подключен к второму входу третьего сумматора, выход которого соединен с вторыми входами компараторов и третьего элемента

И, восьмой выход синхронизатора подключен к входам синхронизации компараторов, выход j-ro блока возведения в степень группы (где j(rH)-2r) подключен к первому входу соответствующего сумматора первой группы, вторые входы сумматоров первой группы соединены с второй группой выходов блока памяти, выход каждого сумматора первой группы подключены к входу делимого соответствующего делителя группы, выходы делителей группы соединены с первыми входами одноименных сумматоров второй группы, выходы которых подклю- чены к информационным входам соответствующих регистров группы, выход каждого из которых соединен с третьим входом одноименного сумматора первой группы, с вторым входом одноименного сумматора второй группы и с соответствующим входом блока вычисления коэффициентов, восьмой, девятый и десятый выходы синхронизатора подключены соответственно к входам синхронизации делителей группы, входам установки в О и управления сдвигом регистров группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления математического ожидания | 1986 |

|

SU1383398A1 |

| Устройство для определения параметров распределения случайных величин | 1981 |

|

SU1084811A1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И УСТРАНЕНИЯ АНОМАЛЬНЫХ ИЗМЕРЕНИЙ | 2005 |

|

RU2301445C1 |

| Адаптивный цифровой фильтр | 1986 |

|

SU1387173A1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И УСТРАНЕНИЯ АНОМАЛЬНЫХ ИЗМЕРЕНИЙ ПРИ ФИКСИРОВАННОМ ЗНАЧЕНИИ ВЕРОЯТНОСТИ ЛОЖНОЙ ТРЕВОГИ | 2007 |

|

RU2361268C1 |

| ПРИБОР ДЛЯ РЕЙТИНГОВОЙ ОЦЕНКИ УРОВНЯ ГОТОВНОСТИ К ИННОВАЦИОННОЙ ДЕЯТЕЛЬНОСТИ | 2014 |

|

RU2548478C1 |

| Статистический анализатор | 1986 |

|

SU1401482A1 |

| Устройство для вычисления оценок математического ожидания и дисперсии | 1983 |

|

SU1280392A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА КАНАЛА ПЕРЕДАЧИ ДАННЫХ | 2012 |

|

RU2504830C2 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И УСТРАНЕНИЯ АНОМАЛЬНЫХ ИЗМЕРЕНИЙ | 2016 |

|

RU2616568C1 |

Изобретение относится к вычислительной технике и может найти применение при измерениях физических величин и параметров случайных процессов Цель изобретения - повышение точности работы в реальном масштабе времени Поставленная цель достигается введением в устройство для вычисления текущего математического ожидания, содержащее синхронизатор, блок определения среднего арифметического значения, три сумматора, сдвиговый регистр, группу сумматоров, группу блоков возведения в степень, блок вычисления коэффициентов, группу блоков умножения, блок памяти, блока деления, двух сумматоров, двух компараторов, трех элементов И, дешифратора, блока извлечения корня четвертой степени и блока вычисления оценки моментов, состоящего из двух групп сумматоров, группы делителей и группы регистров 5 ил.

9 Ю11ШЗ tHttjg

4 13

кШ

11

12 13

25 t f

М

10

Фи&1

ФизЗ

Фие. f

Фиг.$

| Устройство для вычисления математического ожидания | 1986 |

|

SU1383398A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-04-23—Публикация

1988-05-25—Подача