Изобретение относится к импульсной технике и предназначено для использования н качестве выходного буферного устройства для БИС И2Л-типа.

Целью изобретения является снижение потребляемой мощности vi увеличение уровня логической единицы на выходе устройства,

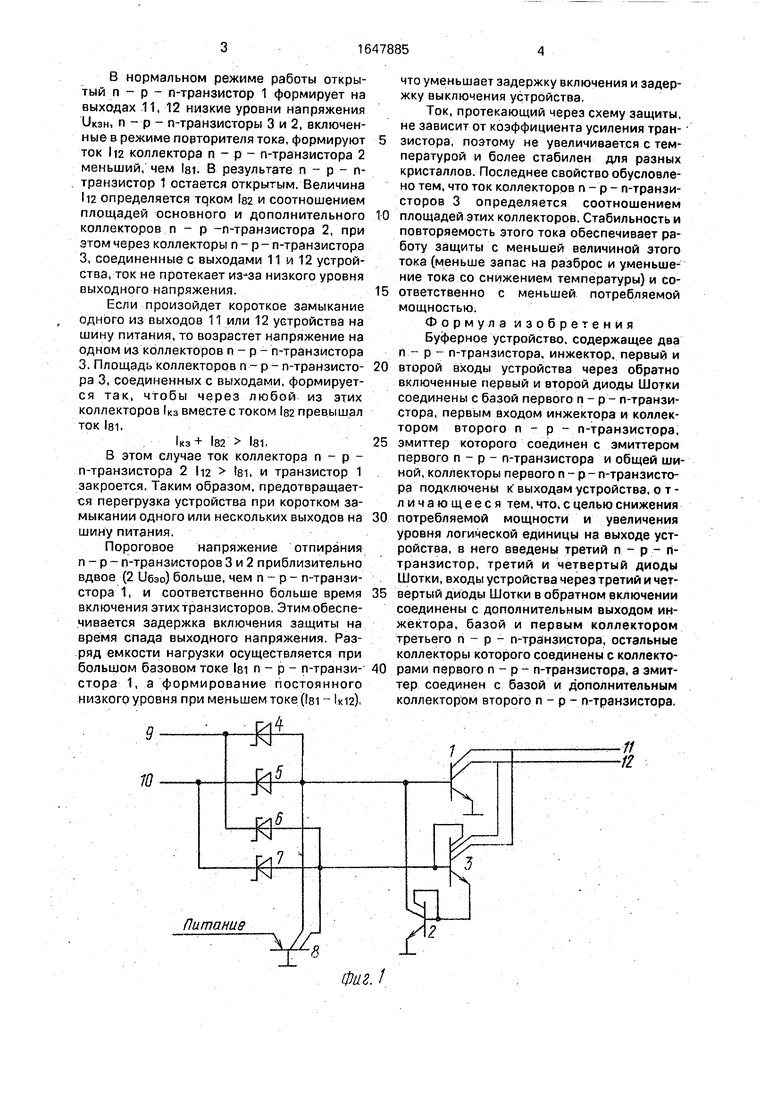

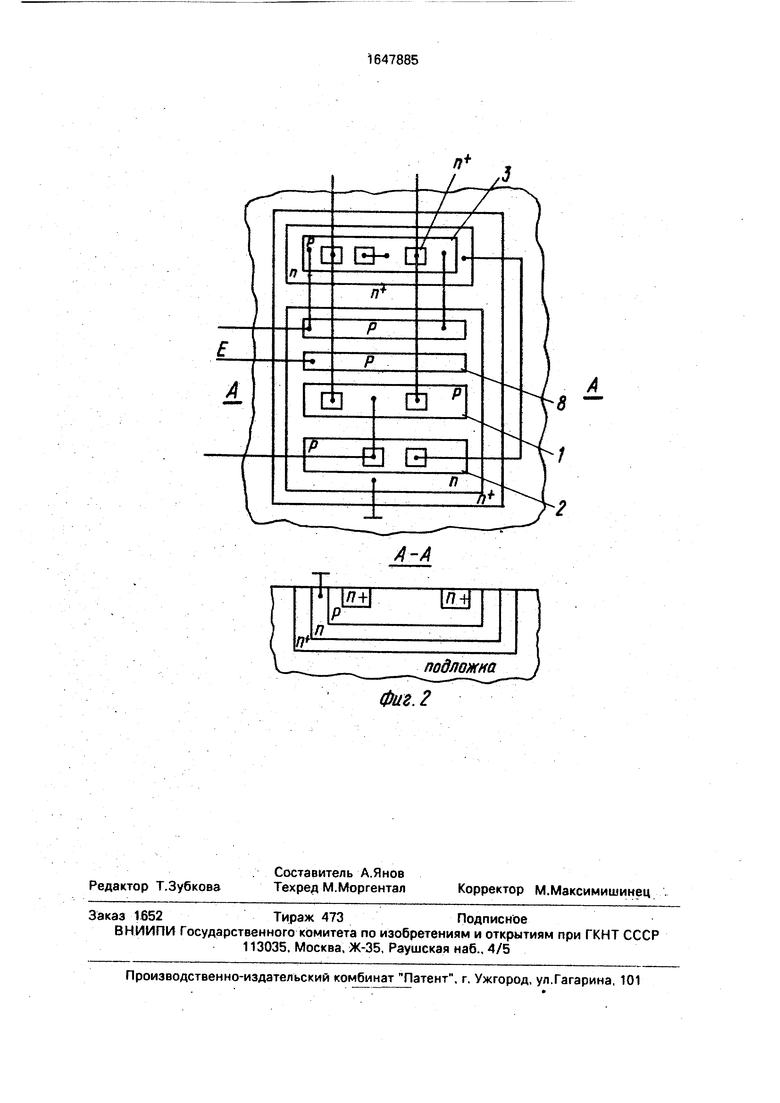

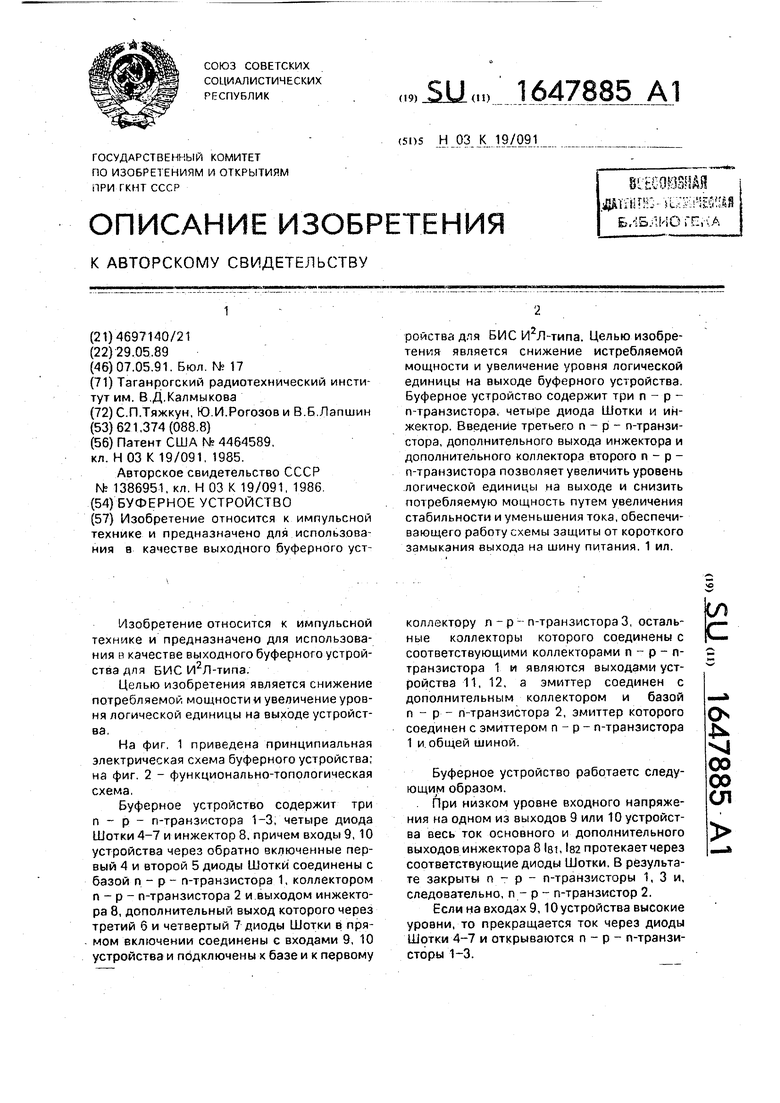

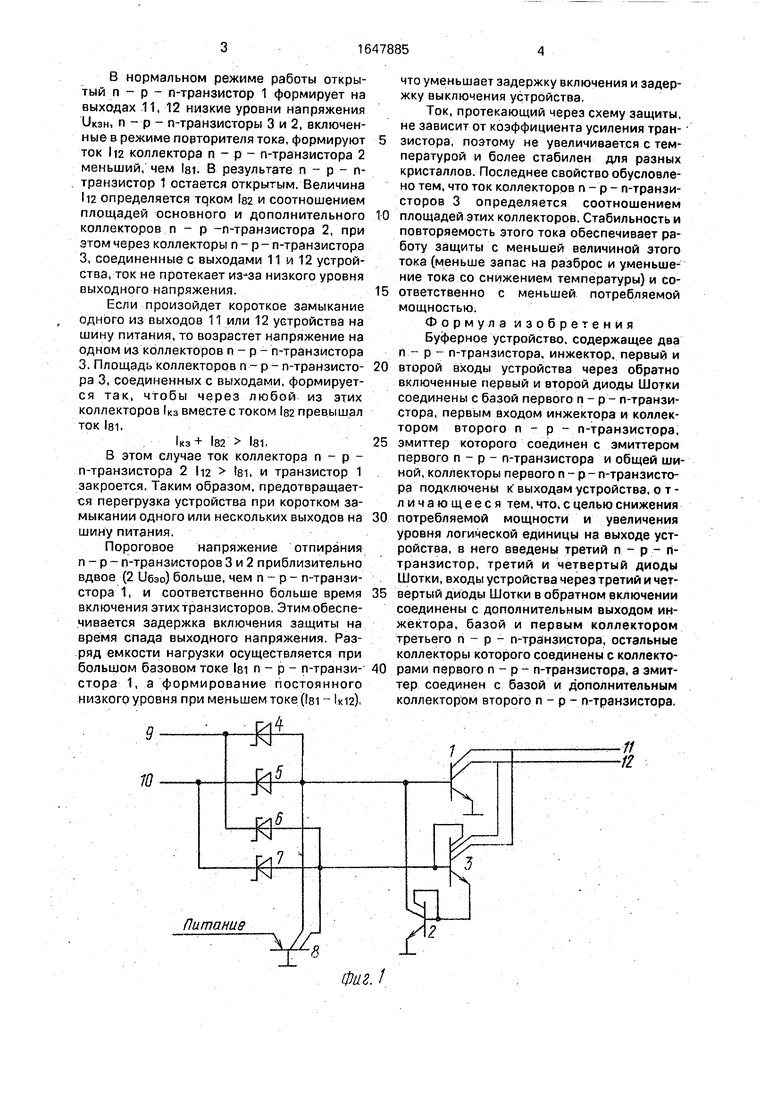

На фиг, 1 приведена принципиальная электрическая схема буферного устройства; на фиг. 2 - функционально-топологическая схема,

Буферное устройство содержит три п - р - п-транзистора 1-3, четыре диода Шотки 4-7 и инжектор 8, причем входы 9, 10 устройства через обратно включенные первый 4 и второй 5 диоды Шотки соединены с базой п - р- п-транзистора 1, коллектором п - р - п-транзистора 2 и выходом инжектора 8, дополнительный выход которого через третий 6 и четвертый 7 диоды Шотки в прямом включении соединены с входами 9, 10 устройства и подключены х базе и к первому

коллектору л-р- п-транзистора3, остальные коллекторы которого соединены с соответствующими коллекторами п - р - п- транзистора 1 и являются выходами устройства 11, 12, а эмиттер соединен с дополнительным коллектором и базой п - р - п-транзистора 2, эмиттер которого соединен с эмиттером п - р - п-транзистора 1 и общей шиной

Буферное устройство работаете следующим образом.

При низком уровне входного напряжения на одном из выходов 9 или 10 устройства весь ток основного и дополнительного выходов инжектора 8 lei, lea протекает через соответствующие диоды Шотки, В результате закрыты п - р - п-транзисторы 1, 3 и, следовательно, п - р - п-транзистор 2.

Если на входах 9,10 устройства высокие уровни, то прекращается ток через диоды Шотки 4-7 и открываются п - р - п-транзисторы 1-3.

(Л

С

о

Jb

х| 00 00 СП

В нормальном режиме работы открытый п - р - п-транзистор 1 формирует на выходах 11, 12 низкие уровни напряжения Укэн, п - р - п-транзисторы 3 и 2, включенные в режиме повторителя тока, формируют ток Ii2 коллектора п - р - п-транзистора 2 меньший, чем lei. В результате п - р - п- транзистор t остается открытым, Величина ha определяется TqKOM 1в2 и соотношением площадей основного и дополнительного коллекторов п - р -п-транзистора 2, при этом через коллекторы п - р - п-транзистора 3, соединенные с выходами 11 и 12 устройства, ток не протекает низкого уровня выходного напряжения.

Если произойдет короткое замыкание одного из выходов 11 или 12 устройства на шину питания, то возрастет напряжение на одном из коллекторов п - р - п-транзистора 3. Площадь коллекторов п - р - п-транзистора 3, соединенных с выходами, формируется так, чтобы через любой из этих коллекторов вместе с током Isa превышал ток lei.

кз+ I82 181.

В этом случае ток коллектора п - р - п-транзистора 2 h2 tei, и транзистор 1 закроется. Таким образом, предотвращается перегрузка устройства при коротком замыкании одного или нескольких выходов на шину питания.

Пороговое напряжение отпирания п - р - п-транзисторов 3 и 2 приблизительно вдвое (2 Обэо) больше, чем п - р - п-транзистора 1, и соответственно больше время включения этих транзисторов, Этим обеспечивается задержка включения защиты на время спада выходного напряжения. Разряд емкости нагрузки осуществляется при большом базовом токе lei п - р - п-транзистора 1, а формирование постоянного низкого уровня при меньшем токе (1в1 - 1к12),

что уменьшает задержку включения и задержку выключения устройства.

Ток, протекающий через схему защиты, не зависит от коэффициента усиления транзистора, поэтому не увеличивается с температурой и более стабилен для разных кристаллов. Последнее свойство обусловлено тем, что ток коллекторов п - р - п-транзисторов 3 определяется соотношением

площадей этих коллекторов. Стабильность и повторяемость этого тока обеспечивает работу защиты с меньшей величиной этого тока (меньше запас на разброс и уменьшение тока со снижением температуры) и соответственно с меньшей потребляемой мощностью.

Формула изобретения Буферное устройство, содержащее два п - р - п-транзистора, инжектор, первый и

второй входы устройства через обратно включенные первый и второй диоды Шотки соединены с базой первого п - р - п-транзистора, первым входом инжектора и коллектором второго п - р - п-транзистора,

эмиттер которого соединен с эмиттером первого п - р - п-транзистора и общей шиной, коллекторы первого п - р-п-транзистора подключены к выходам устройства, отличающееся тем, что, с целью снижения

потребляемой мощности и увеличения уровня логической единицы на выходе устройства, в него введены третий п - р - п- транзистор, третий и четвертый диоды Шотки, входы устройства через третий и четвертый диоды Шотки в обратном включении соединены с дополнительным выходом инжектора, базой и первым коллектором третьего п - р - п-транзистора, остальные коллекторы которого соединены с коллекторами первого п - р - п-транзистора, а эмиттер соединен с базой и дополнительным коллектором второго п - р - п-транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Однофазный D-триггер | 1988 |

|

SU1647855A1 |

| Одноразрядный сумматор | 1988 |

|

SU1599854A1 |

| Разностный элемент | 1988 |

|

SU1538247A1 |

| Троичный счетный триггер | 1979 |

|

SU864503A1 |

| Инжекционный динамический элемент | 1980 |

|

SU953731A1 |

| Преобразователь уровня | 1988 |

|

SU1499481A1 |

| Транзисторно-транзисторный инвертор | 1989 |

|

SU1651372A1 |

| Логическое устройство | 1984 |

|

SU1213521A1 |

| Устройство согласования | 1986 |

|

SU1383483A1 |

| Согласующее устройство | 1986 |

|

SU1348995A1 |

Изобретение относится к импульсной технике и предназначено для использования в качестве выходного буферного уст2 ройства для БИС И2Л-типа. Целью изобретения является снижение истребляемой мощности и увеличение уровня логической единицы на выходе буферного устройства. Буферное устройство содержит три п - р - n-транзистора, четыре диода Шотки и инжектор. Введение третьего п - р - п-транзи- стора, дополнительного выхода инжектора и дополнительного коллектора второго п - р - n-транзистора позволяет увеличить уровень логической единицы на выходе и снизить потребляемую мощность путем увеличения стабильности и уменьшения тока, обеспечивающего работу схемы защиты от короткого замыкания выхода на шину питания. 1 ил.

-и

4

10

-&

Питание

Л /Г

JL 8

Фиг.1

-ft

12

подложиа

Фиг. 2

| Патент США Nk 4464589 | |||

| кл | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| И @ Л ячейка | 1986 |

|

SU1386951A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-05-07—Публикация

1989-05-29—Подача