5

fe

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный счетчик | 1988 |

|

SU1626376A1 |

| Счетчик импульсов | 1989 |

|

SU1676095A1 |

| Сумматор кодов фибоначчи | 1976 |

|

SU732864A1 |

| Сервопривод с цифровым управлением | 1980 |

|

SU962952A1 |

| Цифро-аналоговый преобразователь | 1977 |

|

SU809540A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Преобразователь кодов | 1986 |

|

SU1578813A1 |

| Устройство для сравнения двоичных чисел | 1981 |

|

SU1001081A2 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для организации прямого счета в частично-развернутой форме 1-го кода Фибоначчи. Цель изобретения - повышение контролепригодности путем счета в частично-развернутой форме 1-го кода Фибоначчи - достигается тем, что в счетчик импульсов введены D-триггер 2, вход 7 расширения устройства, выход 8 расширения устройства, в каждую ячейку введены элемент И 11. элемент ИЛИ 12, вход 15 ячейки и выход 18 ячейки, а синхронный триггер 9 выполнен в виде DV-триггера. Счетчик также содержит п

(

4 М

00 00

чэ

однотипных ячеек 1, вход 2 синхронизации, информационный выход 4, выход 5 переноса,

Изобретение относится к автоматике и вычислительной технике и может быть использовано для огранизации прямого счета в частично-развернутой форме (ЧРФ) 1-го кода Фибоначчи.

Целью изобретения является повышение контролепригодности путем счета в ЧРФ 1-го кода Фибоначчи.

ЧРФ 1-го кода Фибоначчи получается из минимальной формы (МФ) 1-го кода Фи- боначчи путем мгновенной развертки каждой единицы в i-м разряде кода в две единицы, расположенные в (Ы)-м и (1-2)-м разрядах преобразованного в ЧРФ кода.

Пример. МФ 010100100

ч ЧРФ 001111011

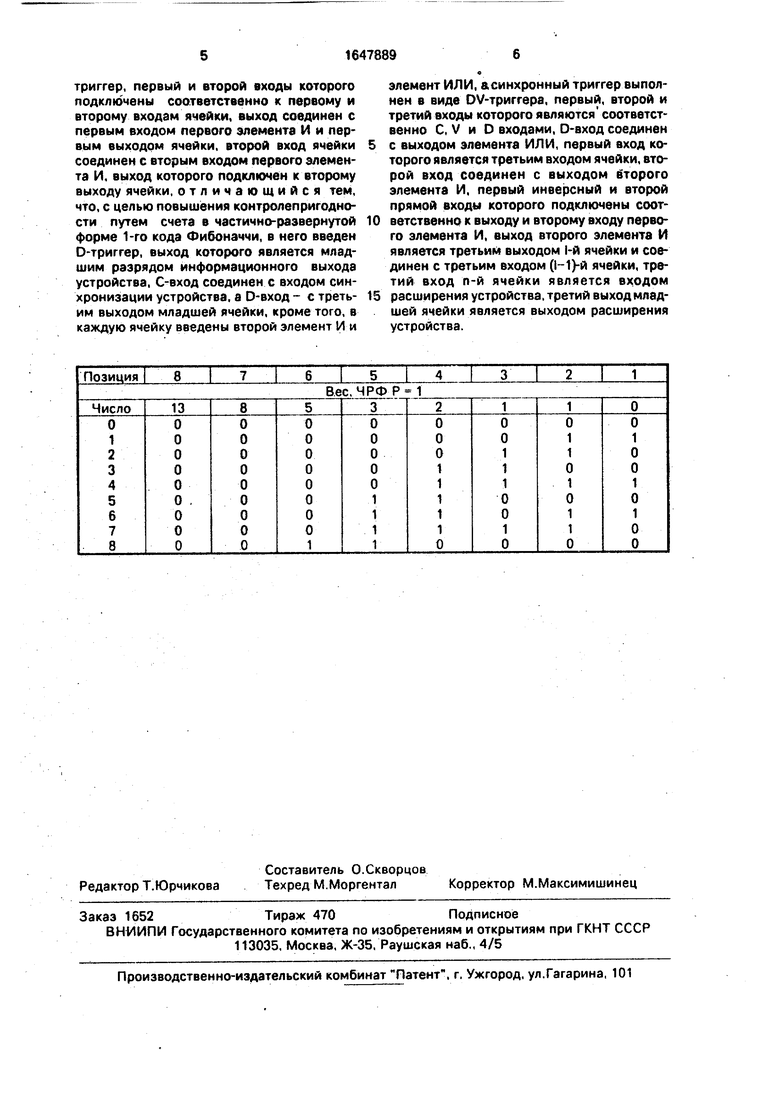

В таблице приведены кодовые эквиваленты первых девяти целых чисел в ЧРФ.

На чертеже изображена функциональ- ная схема устройства.

Устройство содержит п однотипных ячеек 1, D-триггер 2, вход 3 синхронизации, информационный выход 4, выход 5 переноса, вход 6 заема, вход 7 расширения устрой- ства, выход 8 расширения устройства.

Каждая ячейка 1 содержит DV-триггерЭ, первый элемент И 10, второй элемент И 11, элемент ИЛИ 12, первый, второй и третий входы 13, 14 и 15 соответственно, первый, второй и третий выходы 16, 17 и 18 соответственно.

Вход 3 синхронизации устройства подключены к входам 13 ячеек 1 и С-входу триггера 2. Выходы 16 ячеек 1 являются старшими разрядами выхода 4 устройства. Выход триггера 2 является младшим разрядом выхода 4 устройства. Выход 5 переноса соединен с выходом 17 ячейки 1.п, вход 15 которой подключен к входу 7 расширения устройства. Вход 6 заема устройства соединен с входом 14 ячейки 1.1, выход 18 которой подключен к D-входу триггера 2 и выходу 8 расширения устройства. Выход 17 1-й ячейки соединен с входом 14 (I + 1)-й ячейки. Выход 18 i-й ячейки соединен с входом 15 (1-1)-й ячейки.

В каждой ячейке С-и V-входы триггера 9 подключены соответственно к входам 13 и 14 ячейки. D-вход триггера 9 соединен с выходом элемента ИЛИ 12, первый и второй входы которого подключены к входу 15 и выходу 18 ячейки. Выход триггера 9 соединен с выходом 16 ячейки и первым входом

вход 6 заема, элемент И 10, входы 13, И ячеек и выходы 16, 17 ячеек. 1 табл. 1 ил.

элемента И 10, выход которого соединен с выходом 17 ячейки и инверсным входом элемента И 11, выход которого соединен с выходом 18 ячейки. Вторые входы элементов И 10, 11, V-вход триггера 9 подключены к входу 14 ячейки. DV-триггер 9 и D-триггер 2 выполнены с динамическим управлением.

При наращивании структуры до (2п + 1)-й разрядности выход 4.1 старшей секции следует опустить, соединить соответствующие вход 7 расширения младшей секции с выходом 8 расширения старшей секции, при этом вход 7 расширения старшей секции подключить к шине информационного нуля устройства. Вход 6 заема старшей секции соединить с выходом 5 переноса младшей секции, при этом вход 6 заема младшей секции подключить к шине информационной единицы устройства.

Устройство работает следующим образом,

Элементы И 10 образуют блок сквозного переноса и формируют на своих выходах унитарный код, нулевые разряды которого блокируют изменение состояния старших разрядов устройства на следующем такте работы устройства. Элементы И 11 преобразуют унитарный код в единичный позиционный код. Элементы ИЛИ 12 удваивают единичный код до ЧРФ, который и определяет состояние разрядов изменяемой части кода на следующем такте работы устройства,

Возможен перевод счетчика в режим прямого счета в классическом двоичном коде, для чего необходимо входы 15 каждой ячейки подключить к шине информационного нуля устройства и исключить триггер 2.

Формула изобретения Счетчик импульсов, содержащий п (п 1, 2, 3,...) однотипных ячеек, вход синхронизации, информационный выход, вход заема и выход переноса, причем вход синхронизации соединен с первым входом каждой-из ячеек, первые выходы ячеек являются старшими разрядами выхода устройства, второй выход i-й (1 1,2, 3п) ячейки

соединен с вторым входом (1 + 1)-й ячейки, второй выход n-й ячейки соединен с выходом переноса устройства, второй вход младшей ячейки соединен с входом заема устройства, кроме того, каждая ячейка содержит первый элемент И и синхронный

триггер, первый и второй входы которого подключены соответственно к первому и второму входам ячейки, выход соединен с первым входом первого элемента И и первым выходом ячейки, второй вход ячейки соединен с вторым входом первого элемента И, выход которого подключен к второму выходу ячейки, отличающийся тем, что, с целью повышения контролепригодности путем счета в частично-развернутой форме 1-го кода Фибоначчи, в него введен D-триггер, выход которого является младшим разрядом информационного выхода устройства, С-вход соединен с входом синхронизации устройства, а D-вход - с третьим выходом младшей ячейки, кроме того, в каждую ячейку введены второй элемент И и

элемент ИЛИ, асинхронный триггер выполнен в виде DV-триггера, первый, второй и третий входы которого являются соответственно С, V и D входами, D-вход соединен с выходом элемента ИЛИ, первый вход которого является третьим входом ячейки, второй вход соединен с выходом второго элемента И, первый инверсный и второй прямой входы которого подключены соответственно к выходу и второму входу первого элемента И, выход второго элемента И является третьим выходом 1-й ячейки и соединен с третьим входом (1-1)-й ячейки, третий вход n-й ячейки является входом расширения устройства, третий выход младшей ячейки является выходом расширения устройства.

| Стахов А.П | |||

| Алгоритмическая теория измерений и основания компьютерной арифметики | |||

| - Измерения, контроль, автоматизация | |||

| Вып | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Каган Б.М., Каневский М.М | |||

| Цифровые вычислительные машины и системы | |||

| - М.: Энергия | |||

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Парный рычажный домкрат | 1919 |

|

SU209A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-05-07—Публикация

1988-11-09—Подача