Фае. 7

Изобретение относится к вычислительной технике.

Известны устройства для преобразования двоичного кода в код с другим основа- нием. использующий принцип суммирования кодовых эквивалентов.

Недостатком этих устройств является невозможность преобразования кода Фибоначчи в код золотой пропорции.

Наиболее близким техническим решением к предлагаемому является преобразователь кодов (авт.св. СССР № 1552380, кл. Н 03 М 7/30, 1988), содержащий сдвигающий регистр, блок элементов И, накапливающий сумматор, блок управления, элемент задержки и генератор кодовых эквивалентов, имеющий сдвигающий регистр разрядностью п, где п - разрядность кодового эквивалента разряда с наибольшим весом, и блок маскирования. Генерирование кодовых эквивалентов в рассматриваемом устройстве основывается на закономерностях между эквивалентами соседних весов разрядов кода Фибоначчи в коде золотой пропорции и осуществляется путем сдвига кодового эквивалента предыдущего старшего веса разряда кода Фибоначчи на один разряд в сторону младших разрядов сдвиговым регистром генератора с одиовремен- ныммаскированиемнулями

соответствующих разрядов с отрицательными степенями и установкой, при четных порядковых номерах разрядов входного кода, определенного разряда кодового эквивалента в единичное состояние блоком маскирования.

Блок маскирования содержит сдвигающий регистр разрядностью1 k/2, где k - число разрядов, имеющих отрицательные значения степеней кодового эквивалента, k элементов И, k/2 элементов ИЛИ, триггер и преобразователь унитарного кода в единичный, на реализацию функций которого необходима комбинационная схема, содержащая k элементов И, k/2 элементов ИЛИ и k/2 элементов НЕ.

Таким образом, для реализации всего генератора кодовых эквивалентов устройства по прототипу требуется два сдвигающих регистра общей разрядностью п + k/2, 2k элементов И, k элементов ИЛИ, один триггер и k/2 элементов НЕ.

Цель изобретения - сокращение аппаратурных затрат.

Поставленная цель достигается тем, что в преобразователь кода Фибоначчи в код золотой пропорции, содержащий сдвигающий регистр, блок элементов И, накапливающий сумматор, блок управления, Элемент задер кки и генератор кодовых эквивалентов, причем выход блока эквивалентов И соединен с информационным входом накапливающего сумматора, первый выход блока управления соединен с тактовым входом накапливающего сумматора и через элемент задержки - с тактовыми входами генератора кодовых эквивалентов и сдвигающего регистра, информационный вход которого является информационным входом

0 преобразователя, информационный выход которого соединен с выходом накапливающего сумматора, вход запуска и вход начальной установки преобразователя соединены с соответствующими входами

5 блока управления, второй вход которого является выходом готовности преобразователя, третий выход блока управления подключен к входам начальной установки сдвигающего регистра, накапливающего

0 сумматора и генератора кодовых эквивалентов, группа выходов которого соединена с первой группой входов блока элементов И, введены новые связи, а именно: четвертый выход блока управления соединен с входом

5 задания режима генератора кодовых эквивалентов, выход сдвигающего регистра соединен с второй группой входов блока элементов И.

Поставленная цель достигается также

0 изменением структуры генератора кодовых эквивалентов. В отличие or генератора кодовых эквивалентов по прототипу, в предлагаемом устройстве генератор кодовых эквивалентов содержит первый, второй и

5 третий сдвигающие регистры и коммутатор, причем выходы разрядов второго и третьего сдвигающего регистров соединены соответственно с первой и второй группами информационных входов коммутатора, выход

0 группы которого являются соответствующими k младшими выходами группы генератора кодовых эквивалентов (где k - порядковый номер разряда кода золотой пропорции с весом а0)- выходы разрядов

5 первого сдвигающего регистра являются старшими (п - k) выходами группы генератора кодовых эквивалентов, тактовый вход генератора кодовых эквивалентов соединен с тактовыми входами псового, второго и

0 третьего сдвигающих регистров, вход задания режима генератора кодовых эквивалентов соединен с управляющим входом коммутатора, вход начальной установки ге- нератсрз кодовых эквивалентов соединен с

5 входами начальной установки первого, второго и третьего сдвигающих регистров,

Таким образом, для реализации генератора кодовых эквивалентов предложенным устройством необходимы три сдвигающих регистра общей разрядностью п + k и k-разрядный коммутатор, т е требуются меньшие аппаратурные затраты по сравнению с аппаратурными затратами на реализацию устройства по прототипу.

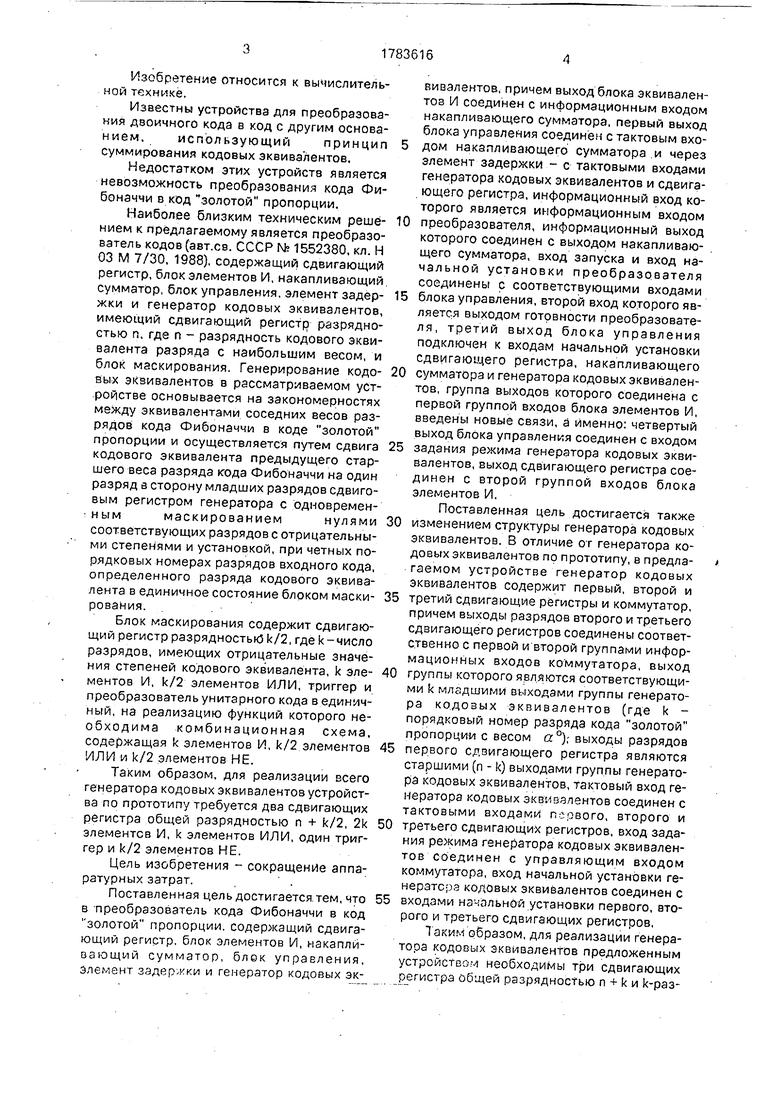

Функциональная схема предлагаемого устройства приведена на фиг 1; функцио- нальная схема блока управления - на фиг 2.

Преобразователь кодов (фиг 1) содержит информационный вход устройства 1, сдвигающий регистр 2, блок 3 элементов И, накапливающий сумматор 4, блок управления 5, элемент задержки 6, генератор кодовых эквивалентов 7, информационные выходы устройства 8, вход 9 запуска преобразователя, вход 10 начальной установки преобразователя, Генератор кодовых эквивалентов 7 содержит первый 11, второй 12 и третий 13 сдвигающие регистры и коммутатор 14.

Информационный вход 1 устройства подключен к информационному входу сдвигающего регистра 2, информационный выход 8 преобразователя соединен с выходом накапливающего сумматора 4 выход блока 3 элементов И соединен с информационным входом накапливающего сумматора 4, первый выход блока управления 5 соединен с тактовым входом накапливающего сумматора 4 и через элемент задержки 6 - с тактовыми входами первого 11 второго 12 и третьего 13 сдвигающих регистров генератора кодовых эквивалентов 7 и с тактовым входом сдвига- ющего регистра 2, вход 9 запуска и вход 10 начальной установки преобразователя соединены с соответствующими входами блока управления 5, второй зыход которого является выходом готовности преобразователя, тре- тий выход блока управления 5 подключен к входам начальной установки сдвигающего регистра 2, накапливающего гумматора 4 и сдвигающих регистров 11-13 (енератора кодовых эквивалентов 7, четвертый выход блока управления 5 соединен с управляющим входом коммутатора 14 генератора кодовых эквивалентов 7, выход сдвигающего регистра 2 соединен с второй группой входов блока 3 элементов И, выходы разрядов второго 12 и третьего 13 сдвигающих регистров генератора кодовых эквивалентов 7 соединены соответственно с первой и второй группами информационных входов коммутатора 14, выходы группы которого соединены с соответст- вующими k младшими входами первой группы входов блока 3 элементов И, выходы разрядов первого сдвигающего регистра 11 генератора 7 соединены со старшими (n - k) входами первой группы входов блока 3 эле- ментов И.

Первый сдвигающих регистр 2 предназначен для хранения и последовательного сдвига в сторону старших разрядов исходного преобразуемого кода Фибоначчи Коммутатор 14, первый 11 второй 12 и третий 13 сдвигающие регистры предназначены для генерирования кодовых эквивалентов весов разрядов кода Фибоначчи. При этом первый сдвигающий регистр 11 предназначен для формирования старших (n - k) разрядов кодовых эквивалентов, а второй 12 и третий 13 сдвигающие регистры - для формирования остальных k младших разрядов кодовых эквивалентов, причем второй сдвигающий регистр 12 формирует младшие разряды кодовых эквивалентов с четными порядковыми номерами, а третий сдвигающий регистр 13 - с нечетными номерами. Коммутатор 14 предназначен для подключения на каждом такте преобразования выходов соответствующего сдвигающего регистра 11 или 13 - в зависимости от четности порядкового номера формируемого кодового эквивалента.

Сдвигающие регистры 2, 11-13 и коммутатор 14 могут быть реализованы на стандартных микросхемах.

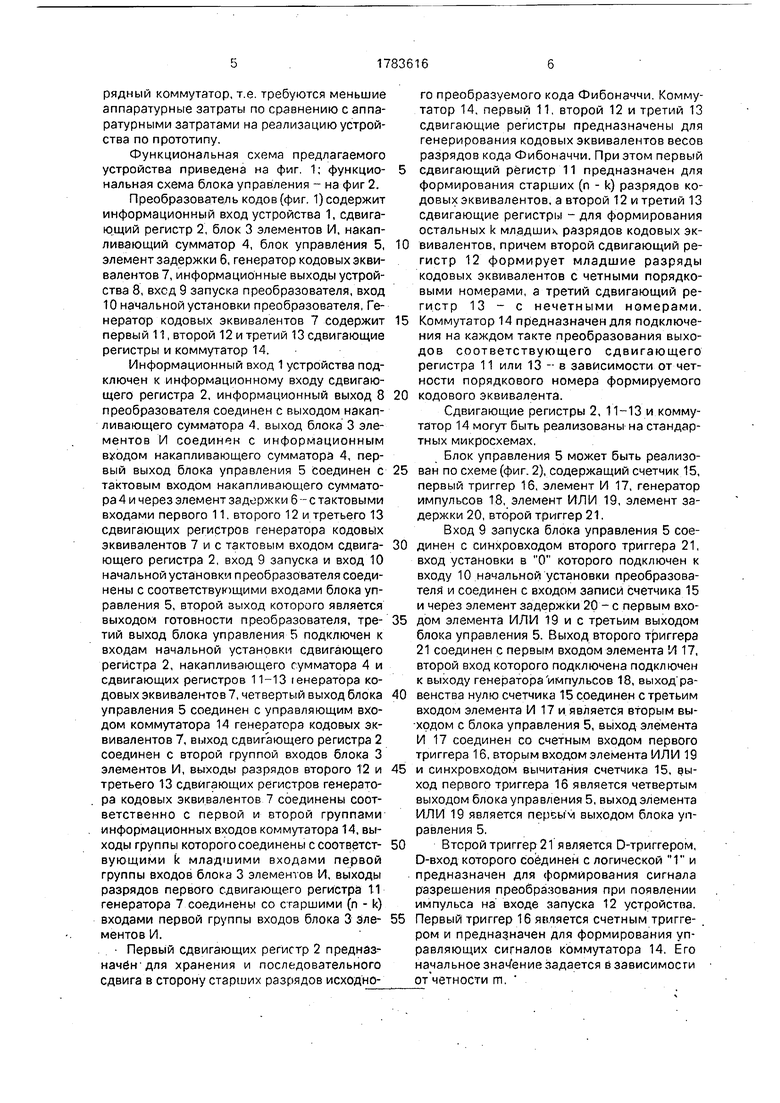

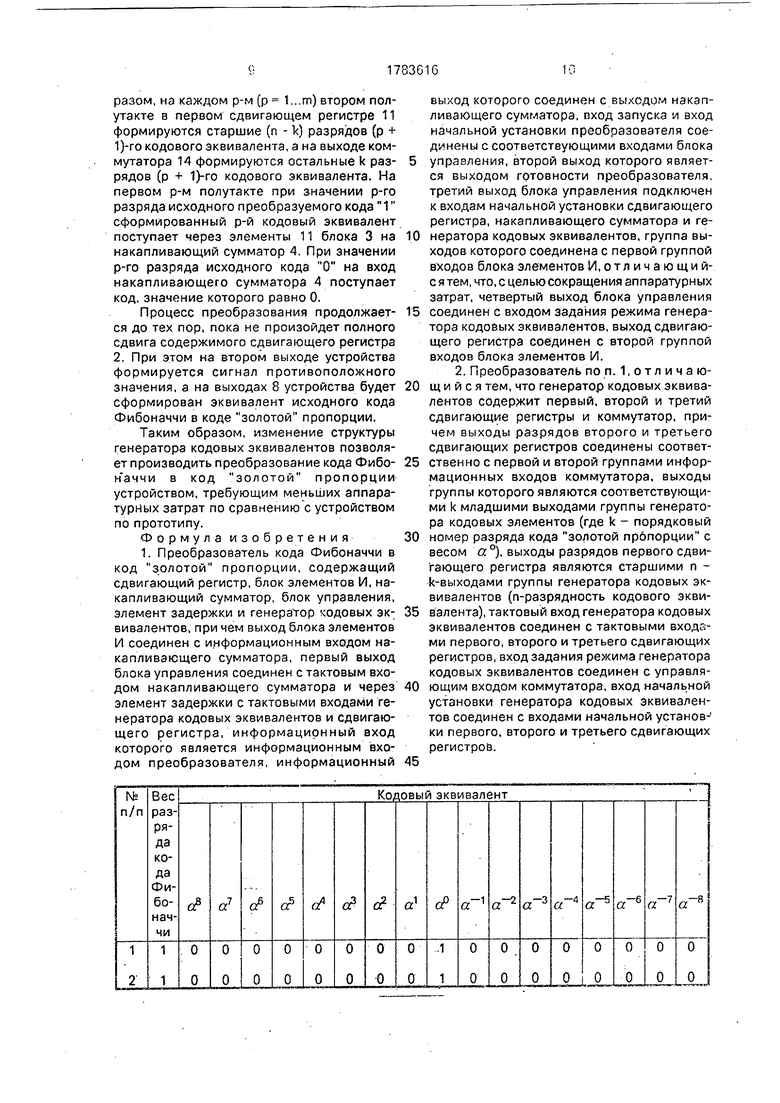

Блок управления 5 может быть реализован по схеме (фиг. 2), содержащий счетчик 15, первый триггер 16, элемент И 17, генератор импульсов 18, элемент ИЛИ 19, элемент задержки 20, второй триггер 21.

Вход 9 запуска блока управления 5 соединен с синхровходом второго триггера 21, вход установки в О которого подключен к входу 10 начальной установки преобразователя и соединен с входом записи счетчика 15 и через элемент задержки 20 - с первым входом элемента ИЛИ 19 и с третьим выходом блока управления 5. Выход второго триггера 21 соединен с первым входом элемента И 17, второй вход которого подключена подключен к выходу генератора импульсов 18, выход равенства нулю счетчика 15 соединен с третьим входом элемента И 17 и является вторым выходом с блока управления 5, выход элемента И 17 соединен со счетным входом первого триггера 16, вторым входом элемента ИЛИ 19 и синхровходом вычитания счетчика 15, выход первого триггера 16 является четвертым выходом блока управления 5, выход элемента ИЛИ 19 является персыvi выходом блока управления 5.

Второй триггер 21 является D-триггером, D-вход которого соединен с логической 1 и предназначен для формирования сигнала разрешения преобразования при появлении импульса на входе запуска 12 устройства Первый триггер 16 явпяется счетным триггером и предназначен для формирования управляющих сигналов коммутатора 14. Его начальное значение задается в зависимости отчетности m

Счетчик 15 предназначен для формирования временного интервала, в период которого происходит преобразование исходного кода. Счетчик 15 работаете режиме вычитания, при этом начальное значение счетчика равно п в двоичном коде. Инверсный выход равенства нулю счетчика 15 позволяет блокировать с помощью элемента И 17 прохождение тактовых импульсов на узлы преобразователя кодов после окончания преобразования кода. Блокировка тактовых импульсов до начала преобразования осуществляется элементом И 17 при наличии нулевого сигнала на выходе второго триггера 21.

Элемент ИЛ И 19 предназначен для формирования синхросигналов сдвига и начальной установки всех регистров устройства преобразования. Элемент задержки 20 может быть выполнен с помощью RC-цепочки и предназначен для задержки синхросигнала по отношению к сигналу начальной установки на входе 13 устройства.

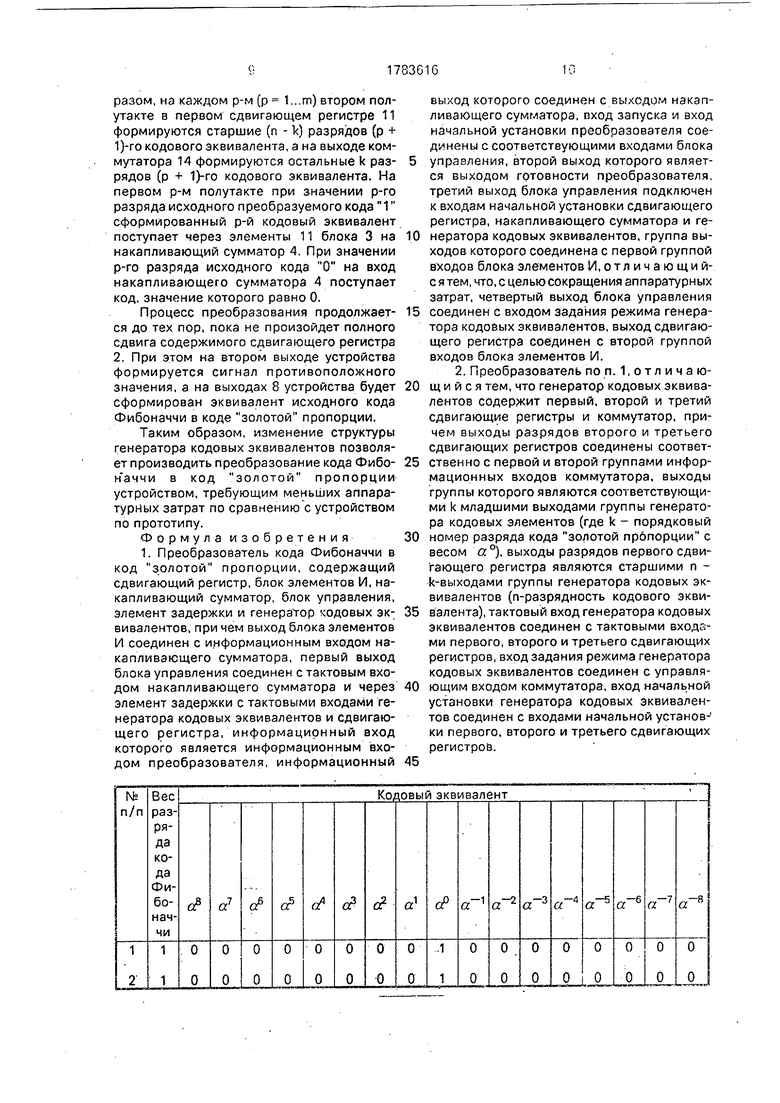

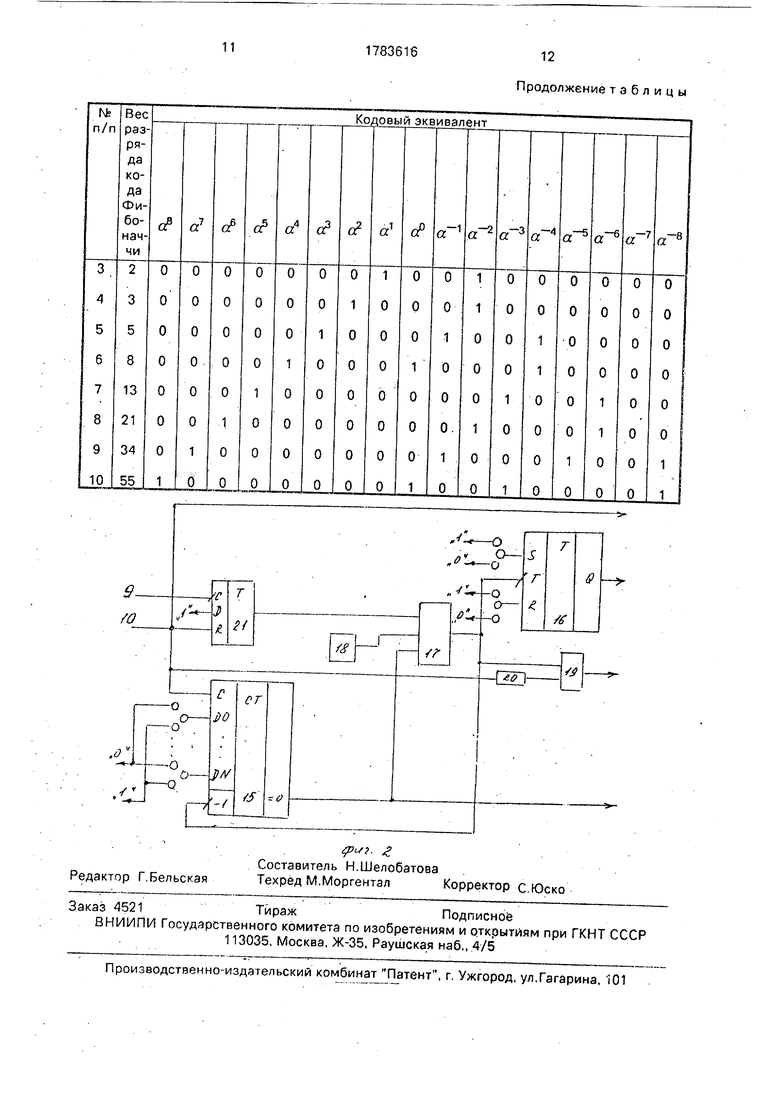

Генерация кодовых эквивалентов технически реализована исходя из закономер- ностей между соседними кодовыми эквивалентами весов разрядов кода Фибоначчи в коде золотой пропорции. Как видно из таблицы, (n - k) старших разрядов двух соседних кодовых эквивалентов равны между собой при сдвиге кодового эквивалента разряда с большим весом в сторону младших разрядов на 1 бит.

Младшие k разрядов двух соседних кодовых эквивалентов с четными порядковыми номерами равны при сдвиге кодового эквивалента с большим весом в сторону старших разрядов на 2 бита. Аналогично кодовым эквивалентам с четными номерами формируются соседние кодовые эквиваленты с нечетными номерами (см. таблицу).

Устройство работает следующим образом. При поступлении единичного сигнала на вход 10 начальной установки устройства преобразователь кодов устанавливается в исходное состояние: код, подлежащий преобразованию, записывается в сдвигающий регистр 2, а в первый сдвигающий регистр 11 генератора кодовых эквивалентов 7 заносятся старшие (n - k) разрядов кодового эквивалента, соответствующего весу т-го старшего разряда преобразуемого кода. При m нечетном в третий сдвигающий регистр 13 записываются k младших разрядов т-го кодового эквивалента, а во второй сдвигающий регистр 12 заносятся k младших разрядов (т - 1)-го кодового эквивалента, сдвинутого в сторону младших разрядов на 1 бит. При m четном запись производится наоборот: в третий сдвигающий регистр 13

записываются k младших разрядов (т - 1)-го кодового эквивалента, сдвинутых на 1 бит в сторону младших разрядов, а во второй сдвигающий регистр 12 - k младших разрядов т-го кодового эквивалента. При этом,

так как младшие значащие разряды т-го и (т - 1)-го кодовых эквивалентов при m четном имеют одинаковый вес, для сохранения информации при сдвиге на 1 бит (т - 1)-го кодового эквивалента разрядность третьего

0 сдвигающего регистра 13 должна быть равна k + 1 разрядам, тогда как для второго сдвигающего регистра 12 достаточно разрядности k. К коммутатору 14 в этом случае должны быть подключены только старшие

5 k-разряды третьего сдвигающего регистра 13. При m нечетной разрядности регистров 12, 13 равны k.

В исходном состоянии накапливающий сумматор 4 и второй триггер 21 блока управ0 ления 5 обнуляются, а в счетчик 15 заносится двоичный код, соответствующий значению т, а первый триггер 16 блбка управления 5 устанавливается в состояние, значение которого зависит от четности по5 рядкового номера старшего кодового эквивалента. При m четном значение сигнала на четвертом выходе блока управления 5 должно быть таким, чтобы коммутатор 14 подключал к своим выходам выходы второго

0 сдвигающего регистра 12, при m нечетном - выходы третьего сдвигающего регистра 13. Преобразование начинается при поступлении на вход 9 устройства сигнала запуска.

5 Каждый такт преобразования состоит из двух полутактов. Синхросигналы первого полутакта формируются на первом выходе блока управления 5, синхросигналы второго полутакта - на выходе элемента задержки б.

0 Длительность задержки сигналов элементов задержки 6 должна быть больше времени, необходимого для суммирования двух кодовых слов на накапливающем сумматоре 4.

5 .На первом полутакте происходит сложение содержимого накапливающего сумматора 4 и значения на выходе блока 3 элементов И.

На втором полутакте происходит сдвиг

0 на 1 бит сдвигающего регистра 2 и сдвигающих регистров 12, 13 генератора кодовых эквивалентов 7 в сторону старших разрядов, а также сдвиг на 1 бит в сторону младших разрядов первого сдвигающего

5 регистра 11 генератора кодовых эквивалентов 7. При этом на каждом втором полутакте на четвертом выходе блока управления 5 формируется сигнал, значение которого противоположно предыдущему. Таким образом, на каждом р-м (р 1 . т) втором полутакте в первом сдвигающем регистре 11 формируются старшие (п -1) разрядов (р + 1)-го кодового эквивалента, а на выходе коммутатора 14 формируются остальные k раз- рядов (р + 1)-го кодового эквивалента. На первом р-м полутакте при значении р-го разряда исходного преобразуемого кода 1 сформированный р-й кодовый эквивалент поступает через элементы 11 блока 3 на накапливающий сумматор 4. При значении р-го разряда исходного кода О на вход накапливающего сумматора 4 поступает код. значение которого равно 0.

Процесс преобразования продолжает- ся до тех пор, пока не произойдет полного сдвига содержимого сдвигающего регистра 2. При этом на втором выходе устройства формируется сигнал противоположного значения, а на выходах 8 устройства будет сформирован эквивалент исходного кода Фибоначчи в коде золотой пропорции.

Таким образом, изменение структуры генератора кодовых эквивалентов позволяет производить преобразование кода Фибо- наччи в код золотой пропорции устройством, требующим меньших аппаратурных затрат по сравнению с устройством по прототипу.

Формулаизобретения

1. Преобразователь кода Фибоначчи в код золотой пропорции, содержащий сдвигающий регистр, блок элементов И, накапливающий сумматор, блок управления, элемент задержки и генератор кодовых эк- вивалентов, при чем выход блока элементов И соединен с информационным входом накапливающего сумматора, первый выход блока управления соединен с тактовым входом накапливающего сумматора и через элемент задержки с тактовыми входами генератора кодовых эквивалентов и сдвигающего регистра, информационный вход которого является информационным входом преобразователя, информационный

выход которого соединен с выходом накапливающего сумматора, вход запуска и вход начальной установки преобразователя соединены с соответствующими входами блока управления, второй выход которого является выходом готовности преобразователя третий выход блока управления подключен к входам начальной установки сдвигающего регистра, накапливающего сумматора и генератора кодовых эквивалентов, группа выходов которого соединена с первой группой входов блока элементов И, отличающий- с я тем, что, с целью сокращения аппаратурных затрат, четвертый выход блока управления соединен с входом задания режима генератора кодовых эквивалентов, выход сдвигающего регистра соединен с второй группой входов блока элементов И.

2. Преобразователь по п. 1, о т л и ч a tout и и с я тем, что генератор кодовых эквивалентов содержит первый, второй и третий сдвигающие регистры и коммутатор, причем выходы разрядов второго и третьего сдвигающих регистров соединены соответственно с первой и второй группами информационных входов коммутатора, выходы группы которого являются соот ветствующи- ми k младшими выходами группы генератора кодовых элементов (где k - порядковый номер разряда кода золотой прбпорции с весом а°), выходы разрядов первого сдвигающего регистра являются старшими п - k-выходами группы генератора кодовых эквивалентов (n-разрядность кодового эквивалента), тактовый вход генератора кодовых эквивалентов соединен с тактовыми входами первого, второго и третьего сдвигающих регистров, вход задания режима генератора кодовых эквивалентов соединен с управляющим входом коммутатора, вход начальной установки генератора кодовых эквивалентов соединен с входами начальной установ- ки первого, второго и третьего сдвигающих регистров.

Продолжение таблицы

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кодов | 1976 |

|

SU662933A1 |

| Преобразователь р-кода фибоначчи в двоичный код | 1976 |

|

SU662932A1 |

| Преобразователь кодов | 1988 |

|

SU1552380A1 |

| Устройство для деления | 1988 |

|

SU1552174A1 |

| Преобразователь кодов | 1986 |

|

SU1438008A1 |

| Преобразователь аналогичных величинВ КОд фибОНАччи | 1977 |

|

SU809552A1 |

| Преобразователь кода Фибоначчи в двоичный код | 1986 |

|

SU1432789A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Преобразователь двоичного кода в непозиционный код Фибоначчи | 1988 |

|

SU1767700A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1005300A1 |

Изобретение относится к вычислительной технике. Целью изобретения является сокращение аппаратурных затрат. Преобразователь содержит сдвигающий регистр 2, блок 3 элементов И, накапливающий сумматор 4, блок 5 управления, элемент 6 задержки и генератор 7 кодовых эвивалентов. 1 з.п. ф-лы, 2 ил., 1 табл.

| Преобразователь кодов | 1976 |

|

SU662933A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь кодов | 1988 |

|

SU1552380A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-12-23—Публикация

1990-02-28—Подача