фиг 1

Изобретение относится к вычислительной технике и может быть использовано для получения равновесной формы кодов Фибоначчи с иррациональными отрицательными основаниями (ШО), обладающей высокими спектральными и самосинхронизируюцимнся параметрами.

Цель изобретения - повышение помехоустойчивости кода путем формирования равновесной формы.

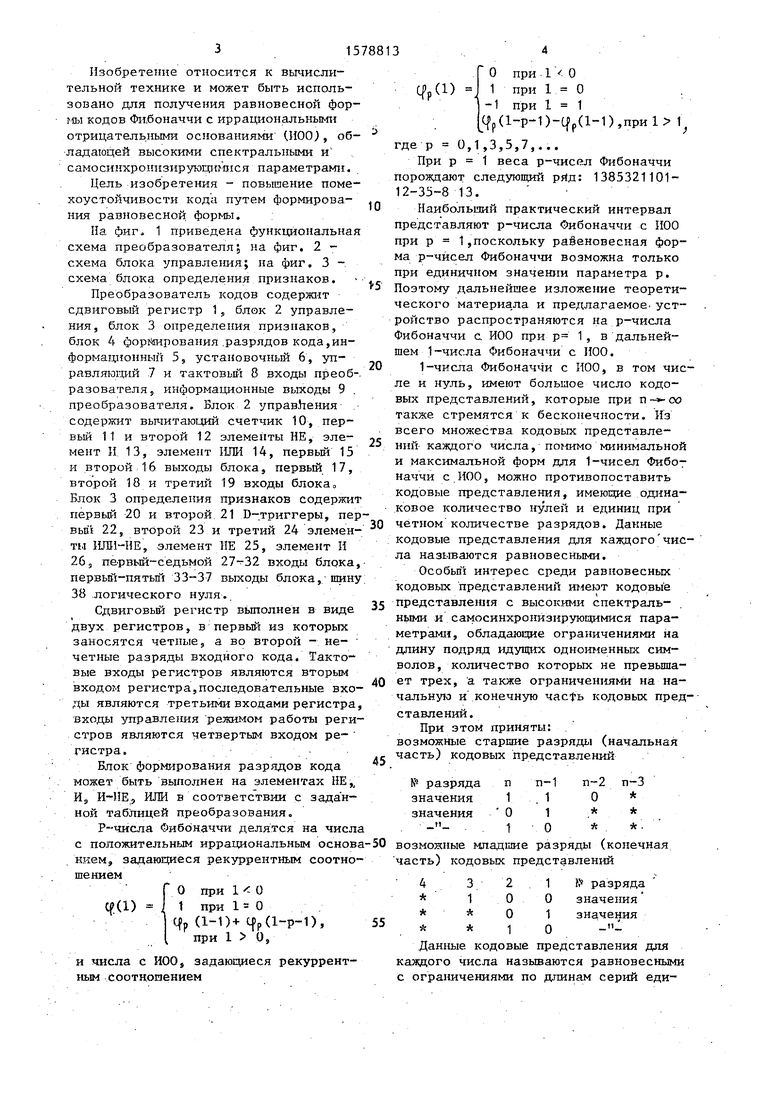

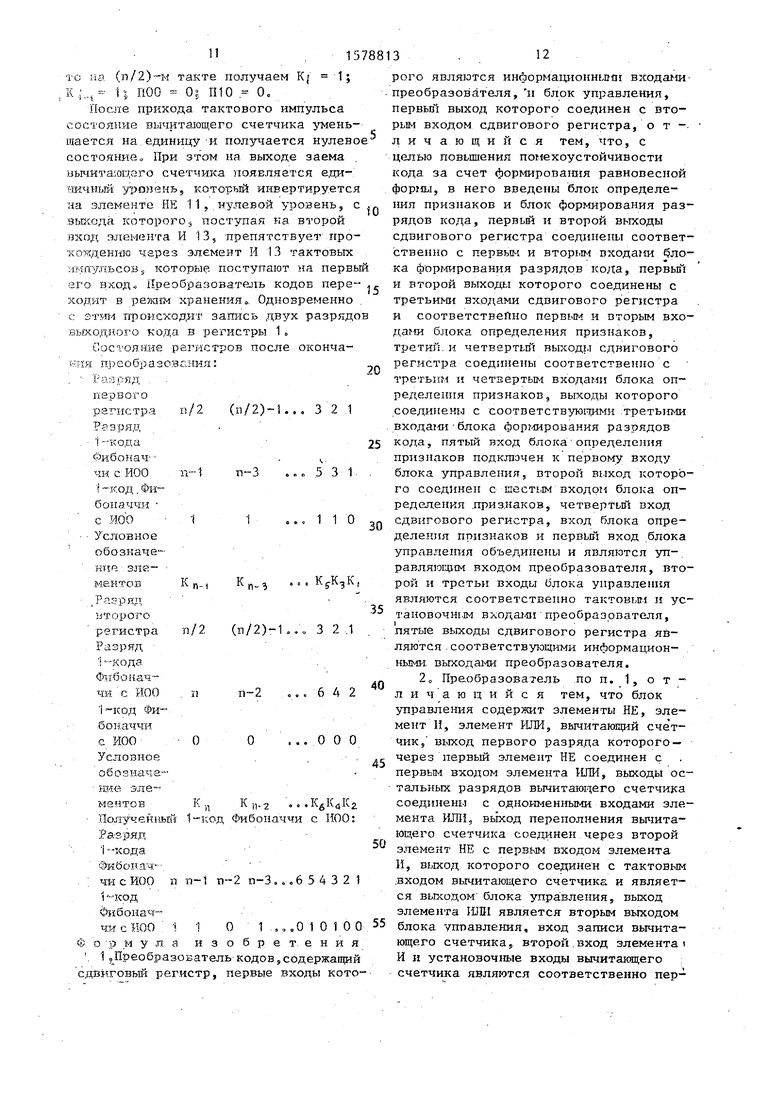

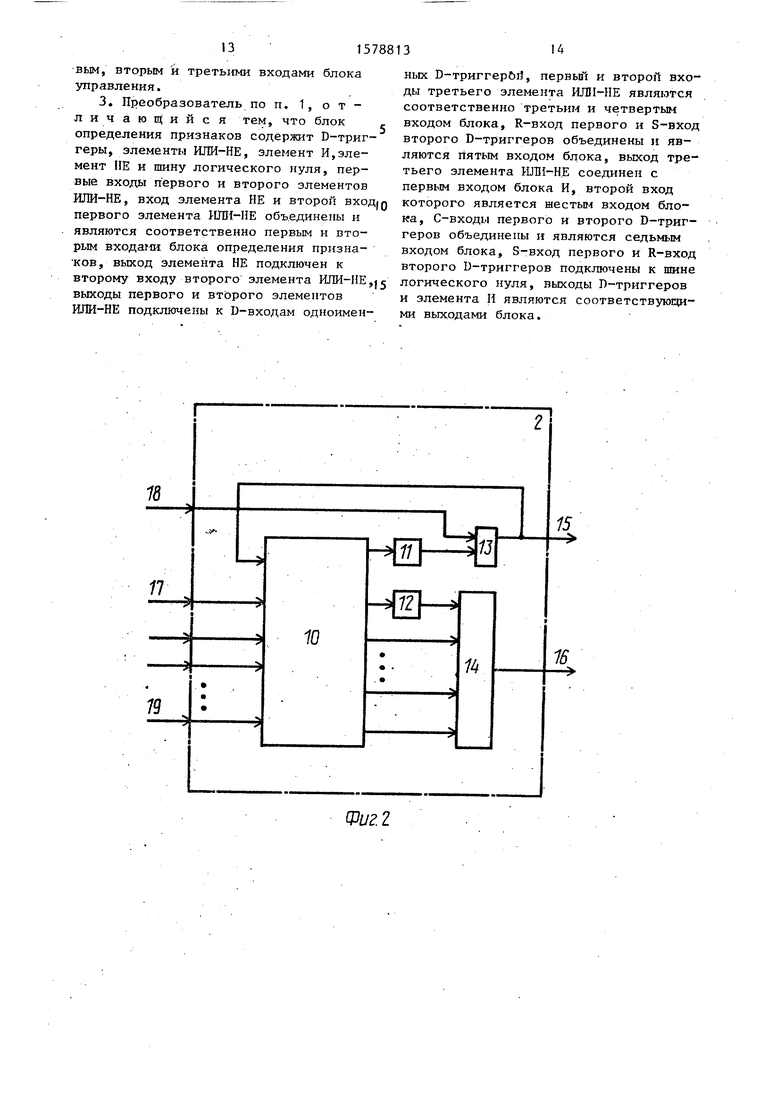

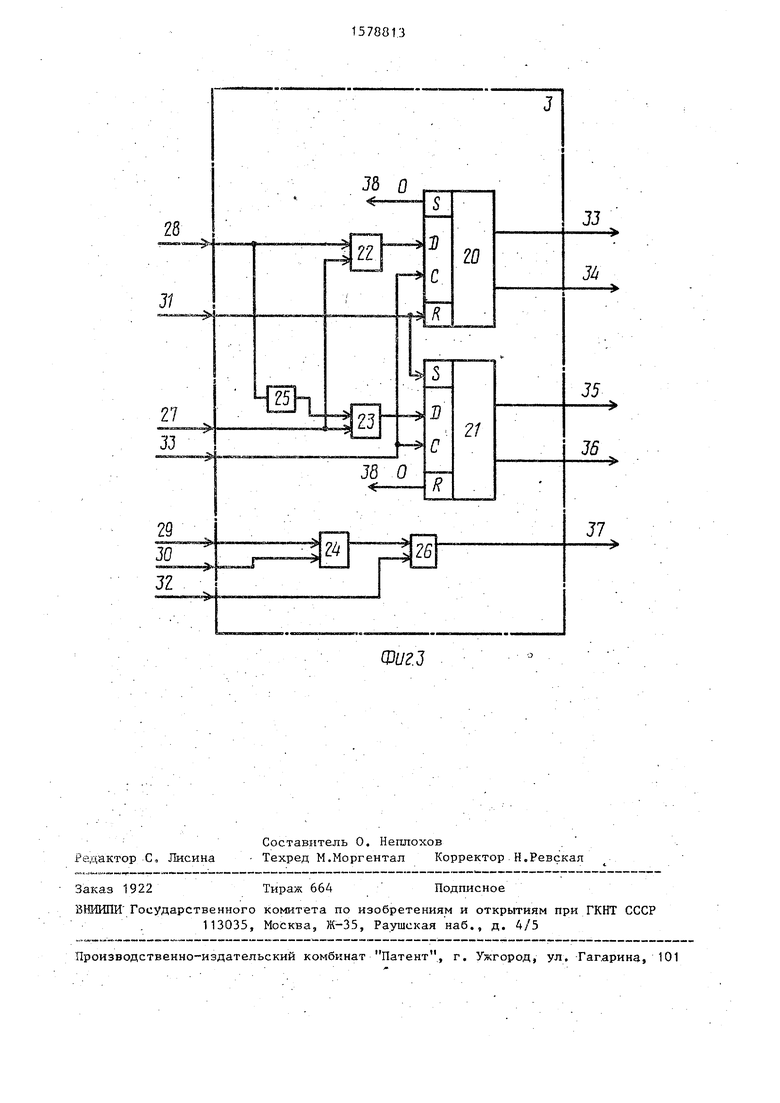

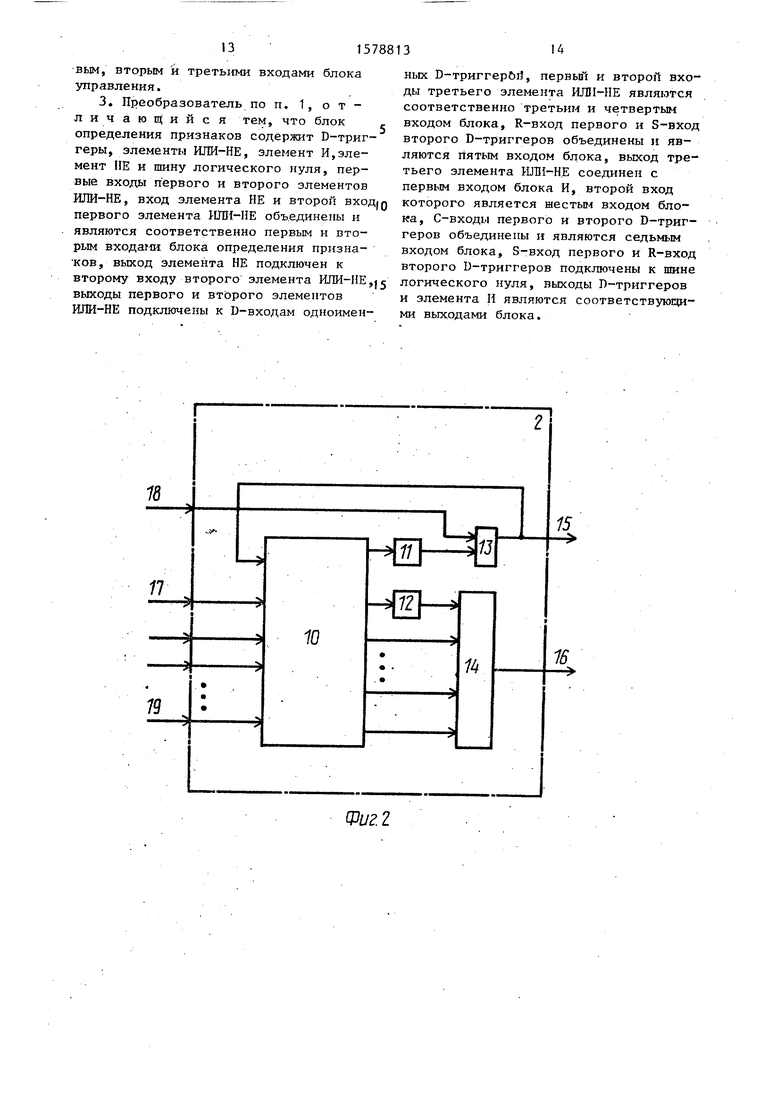

На фиг 1 приведена функциональная схема преобразователя; на фиг. 2 - схема блока управления; на фиг. 3 - схема блока определения признаков. Преобразователь кодов содержит сдвиговый регистр 1s блок 2 управления, блок 3 определения признаков, блок 4 форматирования разрядов кода,информационный 5, установочный 6, управляющий 7 и тактовый 8 входы преобразователя, информационные выходы 9 преобразователя. Блок 2 управления содержит вьгчитаюций счетчик 10, первый 11 и второй 12 элементы НЕ, элемент И 13, элемент ИЛИ 14, первый 15 и второй 16 выходы блока, первый 17, второй 18 и третий 19 входы блока„ Блок 3 определения признаков содержит первый 20 и второй 21 D-триггеры, первый 22, второй 23 и третий 24 элементы ИЛИ-НЕ, элемент НЕ 25, элемент И 26 s первый-седъмой 27-32 входы блока, первый-пятый 33-37 выходы блока, шину 38 логического нуля.

Сдвиговый регистр выполнен в виде двух регистров, в первый из которых заносятся четные, а во второй - нечетные разряды входного кода. Тактовые входы регистров являются вторым входом регистра,последовательные входы являются третьими входами регистра, входы управления режимом работы регистров являются четвертым входом регистра.

Блок формирования разрядов кода может быть выполнен на элементах НЕ,, йэ И-НЕ, ИЛИ в соответствии с заданной таблицей преобразования.

Р-числа Фибоначчи делятся на числа с положительным иррациональным основа1 нием, задающиеся рекуррентным соотношением

0

5

0

5

5

Cfpd)

0

0 при 1 О 1 при -1 при 1 1 С|р(1-р-1)-С|р(1-1),при1 }

где р 0,1,3,5,7,...

При р 1 веса р-чисел Фибоначчи порождают следующий рйд: 1385321101- 12-ЗЬ-8 13.

Наибольший практический интервал представляют р-числа Фибоначчи с ИОО при р 1,поскольку раёеновесная форма р-чисел Фибоначчи возможна только при единичном значении параметра р. Поэтому дальнейшее изложение теоретического материала и предлагаемое устройство распространяются на р-числа Фибоначчи а ИОО при р 1 , в дальнейшем 1-числа Фибоначчи с ИОО.

1-числа Фибоначчи с ИОО, в том числе и нуль, имеют болылое число кодовых представлений, которые при п со также стремятся к бесконечности. Из всего множества кодовых представлений каждого числа, помимо минимальной и максимальной форм для 1-чисел Фибоначчи с ИОО, можно противопоставить кодовые представления, имеющие одинаковое количество нулей и единиц при четном количестве разрядов. Данные кодовые представления для каждого числа называются равновесными.

Особый интерес среди равновесных кодовых представлений имеют кодовые представления с высокими спектральными и самосинхронизируюцимися параметрами, обладающие ограничениями на длину подряд идущих одноименных символов, количество которых не превышает трех, а также ограничениями на начальную и конечную 4acfb кодовых представлений.

При этом приняты:

возможные старшие разряды (начальная часть) кодовых представлений

1

-50

возможные младшие разряды (конечная часть) кодовых представлений

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода Фибоначчи в двоичный код | 1986 |

|

SU1432789A1 |

| Преобразователь кодов | 1987 |

|

SU1450112A1 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Преобразователь кода | 1987 |

|

SU1557685A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| Генератор псевдослучайных последовательностей | 1988 |

|

SU1626345A2 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В СИМВОЛЬНОМ КОДЕ | 1991 |

|

RU2021644C1 |

| Преобразователь двоичного кода в непозиционный код Фибоначчи | 1988 |

|

SU1767700A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU960792A1 |

Изобретение относится к вычислительной технике и может быть использовано для получения равновесной формы кодов Фибоначчи с иррациональными отрицательными основаниями, обладающей высокими спектральными и самосинхронизирующимися параметрами. Цель изобретения - повышение помехоустойчивости кода за счет формирования равновесной формы. Преобразователь содержит сдвиговый регистр 1, блок 2 управления, блок 3 определения признаков, блок 4 формирования разрядов кода, информационные 5, установочные 6, управляющий 7 и тактовый 8 входы преобразователя, информационные выходы 9 преобразователя. 2 з.п. ф-лы, 3 ил., 1 табл.

О при 1 О t при

cfp (i-i)+ ifpU-p-i),

при 1 О,

и числа с HOOS задающиеся рекуррентным соотношением

Данные кодовые представления для каждого числа называются равновесными с ограничениями по длинам серий еди

ниц и нулей, применение которых в системах связи позволяет решать задачи кодовой защиты и кодовой оптимизации информации, а также самосинхронизации информационного потока

Покажем работу преобразователя кодов на примере преобразования п-раз- рядной кодовой комбинации числа 1, представляемого 1-кодом Фибоначчи с ИОО в виде

Разряд п п-1 п-2 п-3. ..65432 1 1-код Фибоначчи с ИОО О О О О 000010

Перед началом преобразования необходимо подать на информационные входы преобразователя n-разрядную кодовую комбинацию, а на установочные входы подать двоичное число равное (п/2). Для начала преобразования на вход 7 преобразователя кодов подается единичный сигнал, который поступая в блок 3 определения признаков на R-вход D-триг герра 20, устанавливает его в нулевое состояние П00 0-П00 1, и поступая на S-вход D-триггера 21 , устанавливает его в единичное состояние; поступая в блок 2 управления на вход разрешения записи информации вычитающего счетчика 10, приводит к записи в него двоичного числа п/2, которое подано на установочные входы 19 блока 2 управления, при этом на выходе заема вычитающего счетчика 10 устанавливается нулевой уровень, который, проходя через элемент НЕ 11, инвертируется и поступает на второй вход элемента И 13, на выходе которого появляются тактовые сигналы, поступающие на его первый, вход, который соединен с входом 18 блока 2 управления; поступая в сдвиговый регистр 1, устанавливает его сдвиговые регистры в режим параллельной записи. :

По приходе тактового импульса происходит запись в регистры 1 соответственно нечетных и четных разрядов входного кода.

В первом регистре находится следующая информация:

Разряд первого

регистра п/2 (п/2)-1.. 3 2 1 Разряд

1-кода Фибоначчи с ИОО п-1 п-3 ... 5 3 1

0

о

5

5

Q

5

0

5

0

п/2 (п/2)-1... 3 21

642

О 0 1

абафа.

1-код Фибоначчи с ИОО 0 0 ... О О О Условное обозначениеэлементов ап, а п, а5 а з а 1

(а,)(ам)

Во втором регистре находится следующая информация: Разряд второго регистра Разряд 1-кода Фибоначчи с ИОО п п-2 1-код Фибоначчи с ИОО О О Условное обозначение элементов ап а

С третьего и четвертого выходов сдвигового регистра 1 нулевые значения четного а1+2и нечетного a,f| разрядов входного кода поступают соответственно на вторые входы блока 3 определения признаков. В результате на выходе элемента ИЛИ-НЕ 2 устанавливается единичный уровень, который через элемент И 26 проходит на выход 37 блока 3 определения признаков (признак ).

Действительноs при состояниях вычитающего счетчика 10, двоичный вес которых больше единицы, на второй, третий,..., 1-й входи элемента ИЛИ 14 поступает хотя бы один единичный уровень, что приводит к сокращению на выходе элемента ИЛИ 14. Путевые уровни с выходов блока 4 (К.; и KJ() поступают соответственно на третьи входы сдвигового регистра 1 и входы 27 и 28 блока 3 определения признаков. С входа 2 блока 4 определения признаков нулевой уровень поступает на первый вход элемента ИЛИ-НЕ 22, на второй вход которого поступает нулевой уровень (К,,) с входа 27 блока 14 определения признаков. Следовательно, на выход элемента ИЛИ-НЕ 28 устанавливается едшшч- ный уровень, который поступает на D-вход D-триггера 20. Нулевой уровень с входа 28 блока 14 определения приз-

наков поступает, кроме того, на вход элемента НЕ 25, на выходе которого устанавливается инвертированный (единичный) уровень, который поступает на первый вход элемента ИЛИ-НЕ 23 на выходе которого устанавливается нулевой уровень, который поступает на D-вход D-триггера 21.

Тактовый импульс, поступающий .на вход 18 блока 2 управления проходит на элемент И 13, а так как на выходе заема вычитающего счетчика 10 нулевой уровень, который, инвертируясь на элементе НЕ 11 в единичный поступает на второй вход элемента И 13, то на выходе этого элемента формируется тактовый импульс, который поступает на счетный вход вычитающего счетчика 10, что ведет к уменьшению двоичного веса его состояния ла единицу, а также поступает на выход 15 блока 2 управления

Тактовый импульс, поступающий с выхода 15 блока 2 управления на вход 3 блока 3 определения признаков, кото рый соединен с С-входами D-триггеров 20 и 21, ведет к записи в них сигналов, установленных на D-входах, т.е„ D-триггер 20 принимает единичное состояние (признак ПОО-И ), а D-триггер 21 принимает нулевое состояние (признак , ).

Тактовый импульс, поступающий с выхода 15 блока 2 управления на второй вход сдвигового регистра 1, ведет к одновременным; сдвигу информации в регистрах право на один разряд,что эквивалентно сдвигу входного кода на 2 разряда за один такт, а также записи в младшие разряды сдвиговых регистров информации, установленной на входах последовательной записи, которые соединены с третьими входами сдвигового регистра 1. Первый такт преобразования окончен.

Состояние сдвиговых регистров еле дующее:

,-

п/2 (п/2)-1...3 2 1

п-1

...7 5 3

...О О О

0

5

Ю

5

чение элементов

К

4 а ti-i 3

;. Ч,

Разряд ,

второго

регистра п/2 (п/2)-1... 3 2 1

Разряд

1-кода Фиббначчи

2 п

с ИОО 1-код Фибоначчис ИОО Условное обозначение элементов

...864

...000

К2 а й

... абаба.4

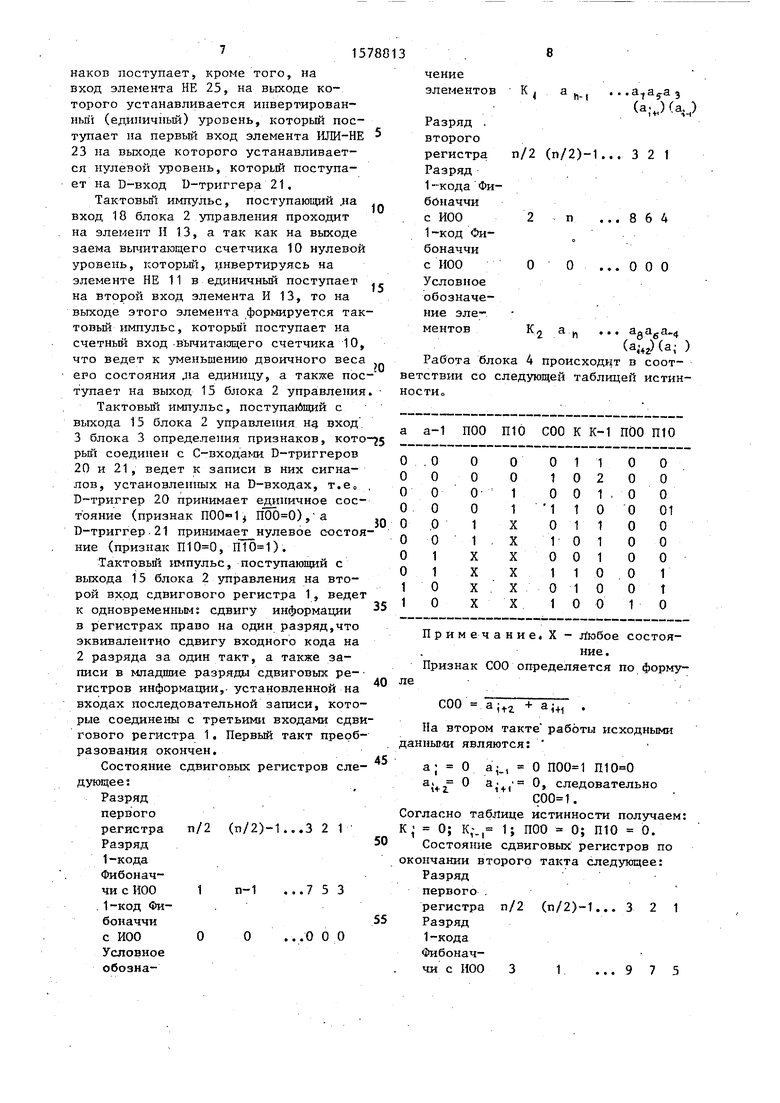

aj42Ha; Работа блока 4 происходит в соответствии со следующей таблицей истинности

Примечание. X - любое состояние. Признак СОО определяется по форму40 ле

COO ajtz + ai+1 .

На втором такте работы исходными данными являются:

45

50

55

а; О

«м- °

1 + 1

О О, следовательно .

Согласно таблице истинности получаем: К; 0; К;., 1; ПОО 0; П10 0.

Состояние сдвиговых регистров по окончании второго такта следующее: Разряд первого

регистра п/2 (п/2)-1... 3 2 1 Разряд 1-кода Фибоначчи с ИОО 3 1 ... 9 7 5

000

К,

К,

,) ю

Разряд второго

регистра п/2 (п/2)-1... 3 2 1 Разряд

1-кодаj5

Фибоначчи с ИОО 4 2 ... 10 8 6 1-код Фибоначчис ИОО 0 0 ... О О О 20 Условное обозначение элементов К К 2 ... а10 aft au

(а,-+2)(а;) 25

На третьем такте работы исходными анными являются:

а; 0; а-., 0; ПОО 0; П10 О а; 0; а(- {в 0, следовательно С00

Согласно таблице истинности полуаем: К; 0; К;., 1; ПОО О, П10 0

Состояние сдвиговых регистров по кончании третьего такта:

Разряд

первого

регистра

Разряд

1-кода

Фибоначчи с И60

1-код Фибоначчи

с ИОО

Условное

п/2 (п/2)-1

1

1

3 2 1

1197

000

К,

а„а9 а7

, Ч,

п/2 (п/2)-1

3 2 1

12 10 8

000

Условное обозначениеэлементов K К ... а„а,0а8

(а,чг) (а;) Четвертый, пятый,„..,(п/2)-1 такты

аботы происходят аналогично третьему. Состояние сдвиговых регистров по

кончании (п/2)-1 такта: Разряд первого регистра Разряд 1-кода Фибоначчи с ИОО 1-код Фибоначчи

с ИОО 1 1 Условное обознаи/2 (п/2)-1.

n-З п-5

3 2 1

32-1

1 О О

20

25

30

35

40

45

50

5

чение элементов

Разряд второго регистра Разряд 1-кода Фибоначчис ИОО 1-код Фибоначчис ИОО Условное обозначениеэлементов

К п- з К ц,

п/2 (п/2)-1

п-2 п-4

О

К,К,ай. (а н ;

3 2 1

4 2

000

К

п-г

к п-

.. К 4 К2 аи (а;)

При работе преобразователя кодов на (п/2)-и такте в вычитающем счетчике хранится двоичное число 1. С первого выхода вычитающего счетчика 10 единичный уровень поступает на вход элемента НЕ 11, инвертируется и нулевой уровень поступает на первый вход элемента ИЛИ 14, на второй, третий,... ,1-й входы которого поступают нулевые уровни. Следовательно, на выходе элемента ИЛИ 14 устанавливается нулевой уровень (признак ), который, поступая на второй вход элемента 26, ведет к появлению на его выходе нулевого уровня, т.е. признак , а так как а; 0; а,-., 0; ПОО О П10 О,

Н15

ю i.ct (п/2)-м такте получаем Kj 1; к | , - I; 1100 QI П10 О,

После прихода тактового импульса состояние вычитающего счетчика уменьшается на единицу и получается нулево состояние При этом на выходе эаема иычита.оцсго счетчика появляется еди- -шчный уровень, который инвертируется на элементе НЕ 11, нулевой уровень, с выхода которогоj поступая на второй вход элемента И 13, препятствует про- -лохденнкз чарез элемент И 13 тактовых

1 гпулъсов, которые поступают на первы

зго вход., Преобразователь кодов пере- ходит в режим хранения Одновременно

i стим происходит запись двух разрядо

«ыходього коца в регистры 1.

Сэс1оянйе регистров после окончаs ч преобразования:

- 1ГЯД

первого

рагиг.тр -i и/2 (п/2)-1... 3 2 1 Разряд

- кода

оибочач. ч

чигИОО п-1 n-З .„о 5 3 1 -код Фибоначчи

с ИОО 1 1 ..«110 Условное обозначение элементе о К П-1 П-Э Р-1C-ряд второго

регистра и/2 (п/2)-1... 3 2 1 Разряд i -кода ФтЛЗонач

642

40

О

О

000

45

чи с ИОО

I-код Фи

боьаччи

с ИОО

Условное

обозначение элементов К л К ц. 2 . ..

Полученный 1-код Фибоначчи с ИОО:

Разряд

I -хода

оибииз. ИОО п п-1 п-3...6 5 4 3 2 1

г-код

Фибона ™

ИОО 1 0 1 .,.0 1 0 1 00 55 оомула изобретения 1 Преобразователь кодов,содержащий двиговый регистр, первые входы кото50

3 ,,

5

0

30

35

40

45

55

50

312

рого являются информационными входами преобразователя, и блок управления, первый выход которого соединен с вторым входом сдвигового регистра, отличающийся тем, что, с целью повышения помехоустойчивости кода за счет формирования равновесной формы, в него введены блок определения признаков и блок формирования разрядов кода, первый и второй выходы сдвигового регистра соединены соответственно с первым и вторым входами §ло- ка формирования разрядов кода, первый и второй выходы которого соединены с третьими входами сдвигового регистра и соответственно первым и вторым входами блока определения признаков, третий и четвертый выходы сдвигового регистра соединены соответственно с третьим и четвертым входами блока определения признаков, выходы которого соединены с соответствующими третьими входами блока формирования разрядов кода, пятый вход блока определения признаков подключен к первому входу блока управления, второй выход которого соединен с шестым входом блока определения признаков, четвертый вход сдвигового регистра, вход блока определения признаков и первЬи вход блока управления объединены и являются управляющим входом преобразователя, второй и третьи входы блока управления являются соответственно тактовым и установочным входами преобразователя, пятые выходы сдвигового регистра являются соответствующими информационными выходами преобразователя.

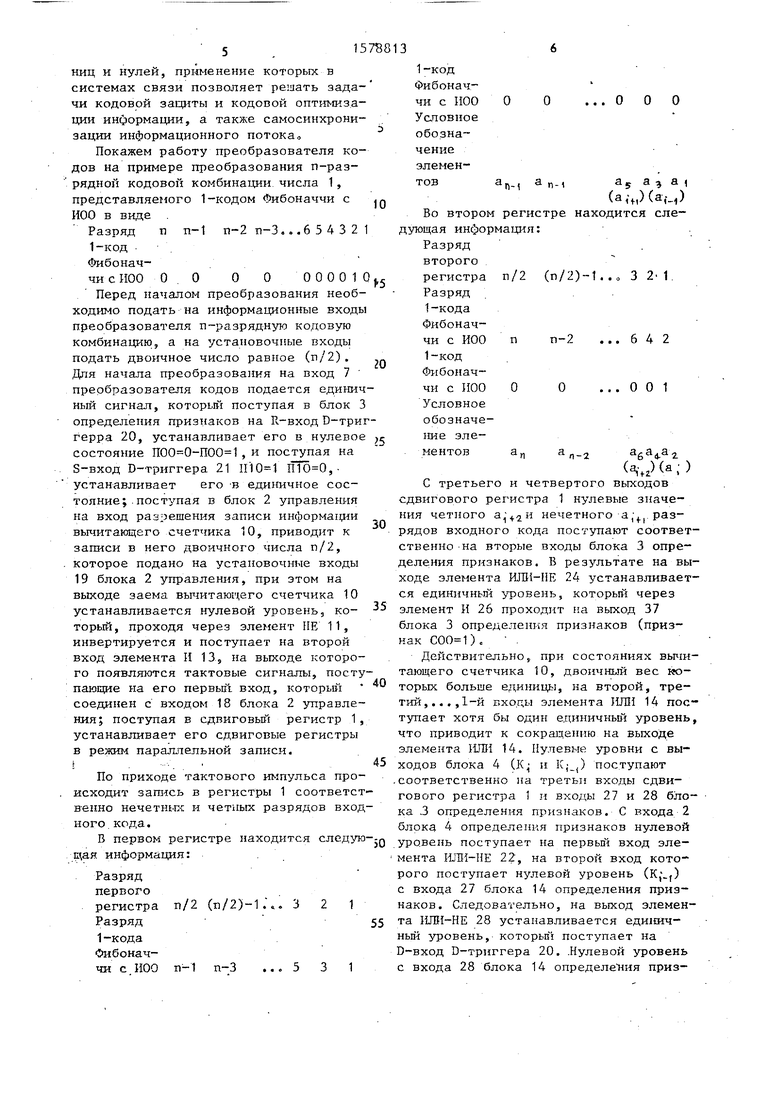

20 Преобразователь по п. отличающийся тем, что блок управления содержит элементы НЕ, элемент И, элемент ИЛИ, вычитающий сче т- чик, выход первого разряда которого- через первый элемент НЕ соединен с первым входом элемента ИЛИ, выходы остальных разрядов вычитающего счетчика соединены с одноименными входами элемента ИЛИ, выход переполнения вычитающего счетчика соединен через второй элемент НЕ с первым входом элемента И, выход которого соединен с тактовым входом вычитающего счетчика и является выходом блока управления, выход элемента ШШ является вторым выходом блока управления, вход записи вычитающего счетчика, второй вход элемента И и установочные входы вычитающего счетчика являются соответственно пер-

вым, вторым и третьими входами блока управления.

Фиг 2

редактор С, Лисина

Составитель О. Неплохов

Техред М.Моргентал Корректор Н.Ревскал

Заказ 1922

Тираж 664

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

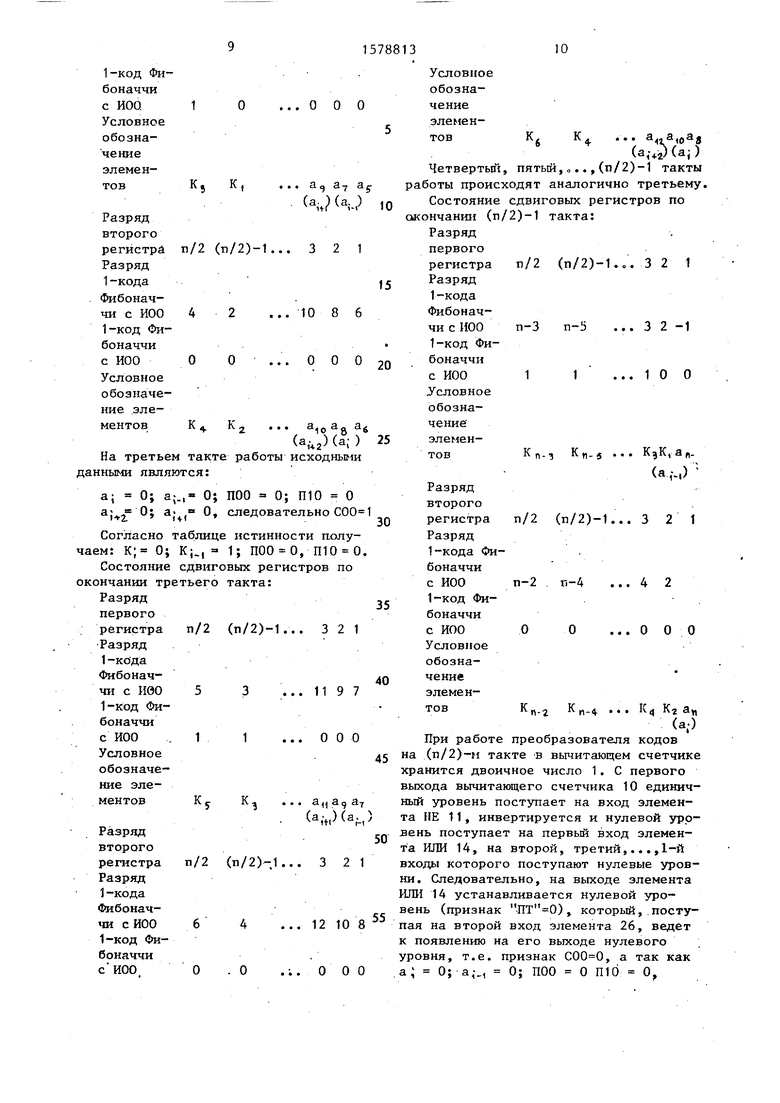

ФигЗ

Подписное

| Преобразователь кодов | 1976 |

|

SU662933A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-07-15—Публикация

1986-12-17—Подача