оо ас

ел

со

ND

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных систем с микропрограммным управлением.

Цель изобретения заключается в повышении производительности и увеличении точности вычислений.

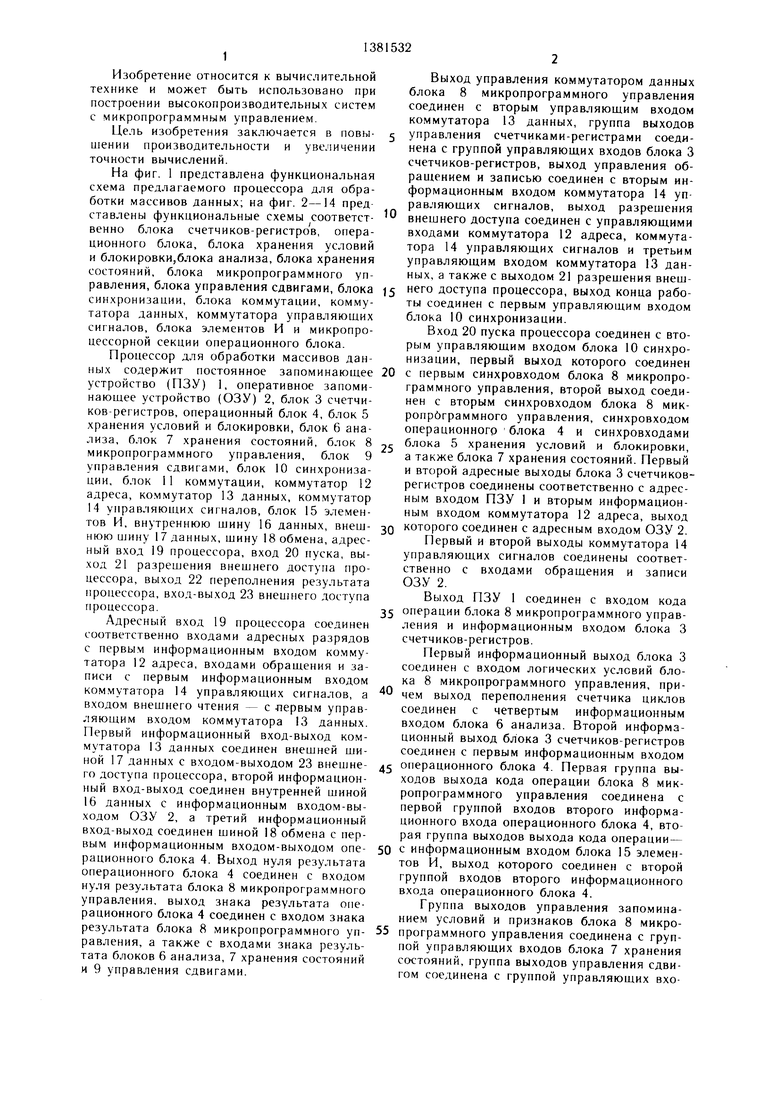

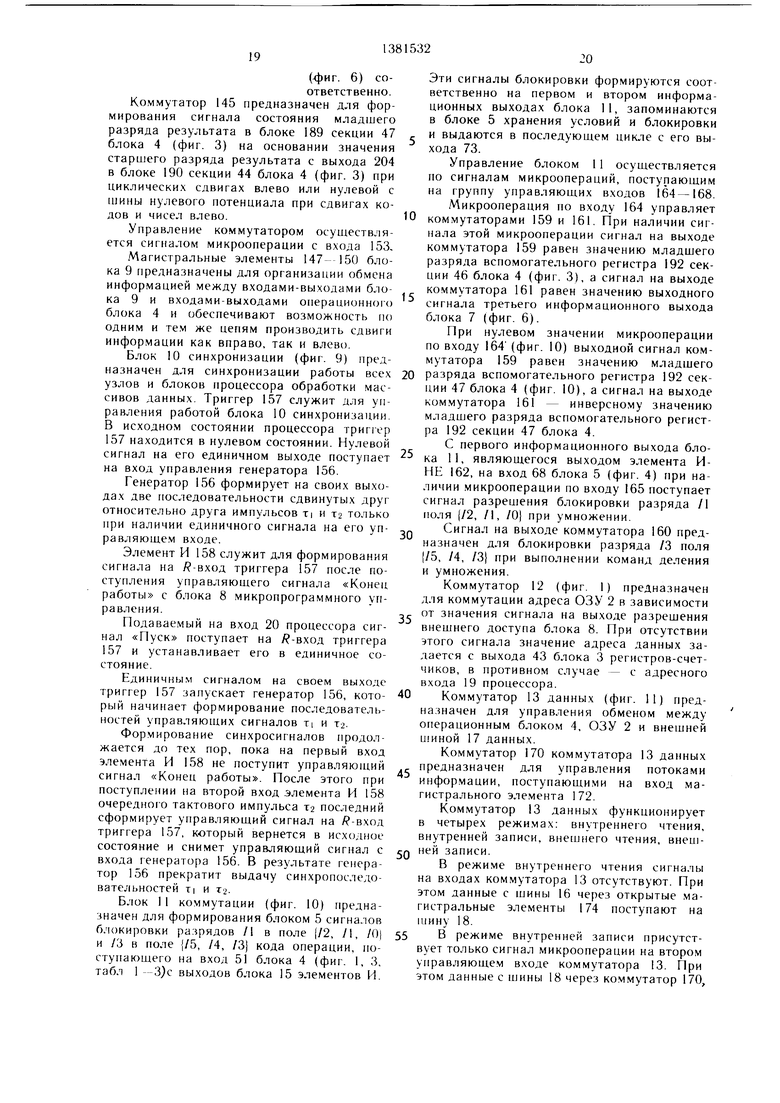

На фиг. 1 представлена функциональная схема предлагаемого процессора для обработки массивов данных; на фиг. 2-14 представлены функциональные схемы соответственно блока счетчиков-регистров, операционного блока, блока хранения условий и блокировки,блока анализа, блока хранения состояний, блока микропрограммного уп10

Выход управления коммутатором данных блока 8 микропрограммного управления соединен с вторым управляющим входом коммутатора 13 данных, группа выходов управления счетчиками-регистрами соединена с группой управляющих входов блока 3 счетчиков-регистров, выход управления обращением и записью соединен с вторым информационным входом коммутатора 14 управляющих сигналов, выход разрешения внешнего доступа соединен с управляющими входами коммутатора 12 адреса, коммутатора 14 управляющих сигналов и третьим управляющим входом коммутатора 13 данных, а также с выходом 21 разрешения внешравления, блока управления сдвигами, блока 15 Доступа процессора, выход конца рабосинхронизации, блока коммутации, коммутатора данных, коммутатора управляющих сигналов, блока элементов И и микропроцессорной секции операционного блока. Процессор для обработки массивов данты соединен с первым управляющим входом блока 10 синхронизации.

Вход 20 пуска процессора соединен с вторым управляющим входом блока 10 синхронизации, первый выход которого соединен

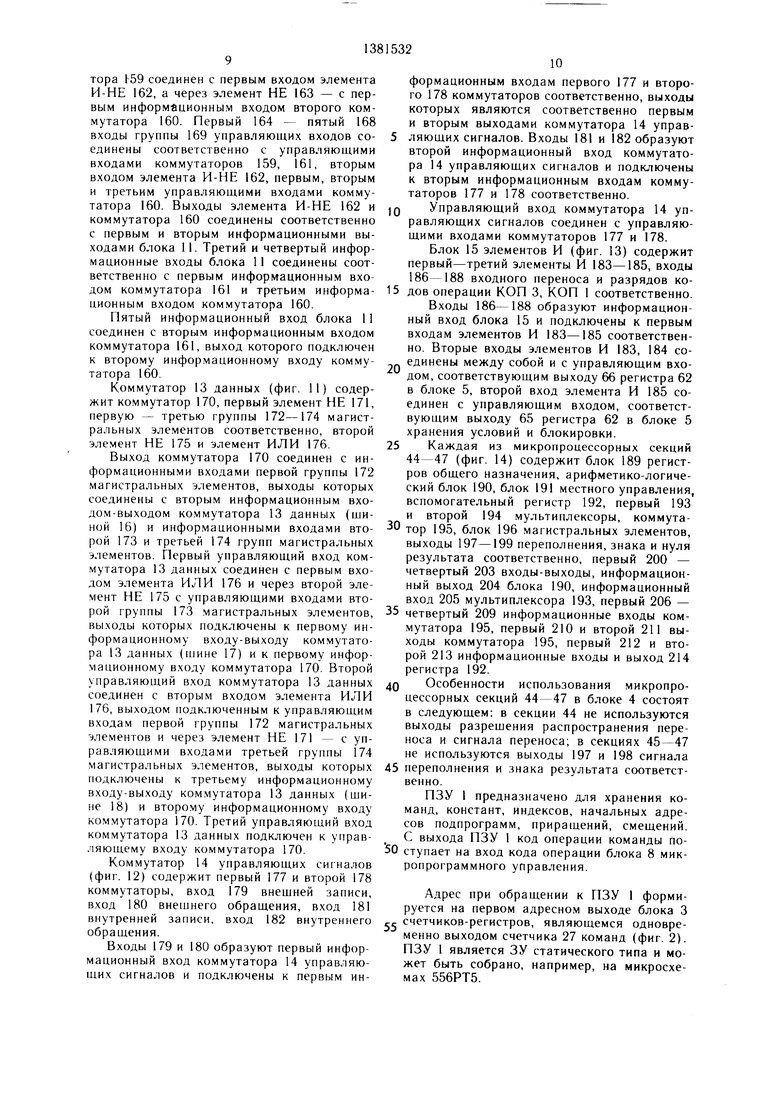

ных содержит постоянное запоминающее 20 с первым синхровходом блока 8 микропроустройство (ПЗУ) 1, оперативное запоминающее устройство (ОЗУ) 2, блок 3 счетчиков-регистров, операционный блок 4, блок 5 хранения условий и блокировки, блок 6 анализа, блок 7 хранения состояний, блок 8 микропрограммного управления, блок 9 управления сдвигами, блок 10 синхронизации, блок 11 коммутации, коммутатор 12 адреса, коммутатор 13 данных, коммутатор 14 управляющих сигналов, блок 15 элемен25

граммного управления, второй выход соединен с вторым синхровходом блока 8 мик- ропрбграммного управления, синхровходом операционного блока 4 и синхровходами блока 5 хранения условий и блокировки, а также блока 7 хранения состояний. Первый и второй адресные выходы блока 3 счетчиков- регистров соединены соответственно с адресным входом ПЗУ 1 и вторым информационным входом коммутатора 12 адреса, выход

тов И, внутреннюю шину 16 данных, внеш- зо которого соединен с адресным входом ОЗУ 2. нюю шину 17 данных, шину 18 обмена, адрес-Первый и второй выходы коммутатора 14

ный вход 19 процессора, вход 20 нуска, выход 21 разрешения внешнего доступа процессора, выход 22 переполнения результата процессора, вход-выход 23 внешнего доступа процессора.

Адресный вход 19 процессора соединен соответственно входами адресных разрядов с первым информационным входом ко.мму- татора 12 адреса, входами обрашения и записи с первым информационным входом коммутатора 14 управляющих сигналов, а входом внещнего чтения - с лервым управляющим входом коммутатора 13 данных. Первый информационный вход-выход коммутатора 13 данных соединен внешней шиной 17 данных с входом-выходом 23 внешне- д операционного блока 4. Первая группа вы- го доступа процессора, второй информацион- ходов выхода кода операции блока 8 микропрограммного управления соединена с первой группой входов второго информационного входа операционного блока 4, вторая группа выходов выхода кода операции

управляющих сигналов соединены соответственно с входами обращения и записи ОЗУ 2.

Выход ПЗУ 1 соединен с входом кода 35 операции блока 8 микропрограммного управления и информационным входом блока 3 счетчиков-регистров.

Первый информационный выход блока 3 соединен с входом логических условий блока 8 микропрограммного управления, причем выход переполнения счетчика циклов соединен с четвертым информационным входом блока 6 анализа. Второй информационный выход блока 3 счетчиков-регистров соединен с первым информационным входом

40

ныи вход-выход соединен внутренней шиной 16 данных с информационным входом-выходом ОЗУ 2, а третий информационный вход-выход соединен шиной 18 обмена с первым информационным входом-выходом one- 50 с информационным входом блока 15 элеменрационного блока 4. Выход нуля результата операционного блока 4 соединен с входом нуля результата блока 8 микропрограммного управления, выход знака результата операционного блока 4 соединен с входом знака результата блока 8 микропрограммного управления, а также с входами знака результата блоков 6 анализа, 7 хранения состояний и 9 управления сдвигами.

55

тов и, выход которого соединен с второй группой входов второго информационного входа операционного блока 4.

Группа выходов управления запоминанием условий и признаков блока 8 микропрограммного управления соединена с группой управляющих входов блока 7 хранения состояний, группа выходов управления сдвигом соединена с группой управляющих вхо

Выход управления коммутатором данных блока 8 микропрограммного управления соединен с вторым управляющим входом коммутатора 13 данных, группа выходов управления счетчиками-регистрами соединена с группой управляющих входов блока 3 счетчиков-регистров, выход управления обращением и записью соединен с вторым информационным входом коммутатора 14 управляющих сигналов, выход разрешения внешнего доступа соединен с управляющими входами коммутатора 12 адреса, коммутатора 14 управляющих сигналов и третьим управляющим входом коммутатора 13 данных, а также с выходом 21 разрешения внешты соединен с первым управляющим входом блока 10 синхронизации.

Вход 20 пуска процессора соединен с вторым управляющим входом блока 10 синхронизации, первый выход которого соединен

граммного управления, второй выход соединен с вторым синхровходом блока 8 мик- ропрбграммного управления, синхровходом операционного блока 4 и синхровходами блока 5 хранения условий и блокировки, а также блока 7 хранения состояний. Первый и второй адресные выходы блока 3 счетчиков- регистров соединены соответственно с адресным входом ПЗУ 1 и вторым информационным входом коммутатора 12 адреса, выход

которого соединен с адресным входом ОЗУ 2. Первый и второй выходы коммутатора 14

операционного блока 4. Первая группа вы- ходов выхода кода операции блока 8 микропрограммного управления соединена с первой группой входов второго информационного входа операционного блока 4, вторая группа выходов выхода кода операции

управляющих сигналов соединены соответственно с входами обращения и записи ОЗУ 2.

Выход ПЗУ 1 соединен с входом кода 5 операции блока 8 микропрограммного управления и информационным входом блока 3 счетчиков-регистров.

Первый информационный выход блока 3 соединен с входом логических условий блока 8 микропрограммного управления, причем выход переполнения счетчика циклов соединен с четвертым информационным входом блока 6 анализа. Второй информационный выход блока 3 счетчиков-регистров соединен с первым информационным входом

0

50 с информационным входом блока 15 элемен55

тов и, выход которого соединен с второй группой входов второго информационного входа операционного блока 4.

Группа выходов управления запоминанием условий и признаков блока 8 микропрограммного управления соединена с группой управляющих входов блока 7 хранения состояний, группа выходов управления сдвигом соединена с группой управляющих входов блока 9 управления сдвигами, группа выходов управления коммутацией соединена с группой управляющих входов блока 1 коммутации, выход управления мультиплексором соединен с управляющим входом блока 6 анализа.

Информационный выход операционного блока 4 соединен с первым информационным входом блока 11 коммутации, выход переполнения соединен с первым информационным входом блока б анализа, второй информационный вход-выход соединен с первым входом-выходом блока 9 управления сдвигами и первым информационным входом блока 7 хранения состояний, третий и четПервая группа входов входа 39 соединена с информационным входом первого буферного регистра 24, а вторая группа - с информационным входом второго буферного 5 регистра 25. Выходы первого буферного регистра 24 соединены с первыми информационными входами коммутаторов 29, 30, выходы регистра 25 соединены с аторыми информационными входами коммутаторов 29, 30, выходы которых образуют второй информационный выход 40 блока 3. Выход счетчика 27 команд соединен с первым адресным выходом 41 блока 3. Выходы счетчиков 28.1-28.л циклов образуют первый информационный выход 42 блока 3, а выход

вертый информационные входы-выходы со- 15 счетчика 26 адреса соединен с его вторым

адресным выходом 43.

единены соответственно с вторым и третьим входами-выходами блока 9 управления сдвигами, пятый информационный вход-выход соединен с четвертым входом-выходом блока 9 управления сдвигами, с первым информационным входом блока 5 хранения условий и блокировки и вторым информационным входом блока II коммутации.

Первый и второй информационные выходы блока 11 коммутации соединены соответственно с вторым и третьим информационными входами блока 5 хранения условий и блокировки. Первый и второй информационные выходы блока 6 анализа соединены соответственно с первым информационным входом блока 9 управления сдвигами и четвертым информационным входом блока 5 хранения и блокировки, управляющий, первый и второй информационные выходы которого соединены соответственно с управляющим входом блока 15 элементов И, третьим информационным входом блока 11

адресным выходом 43.

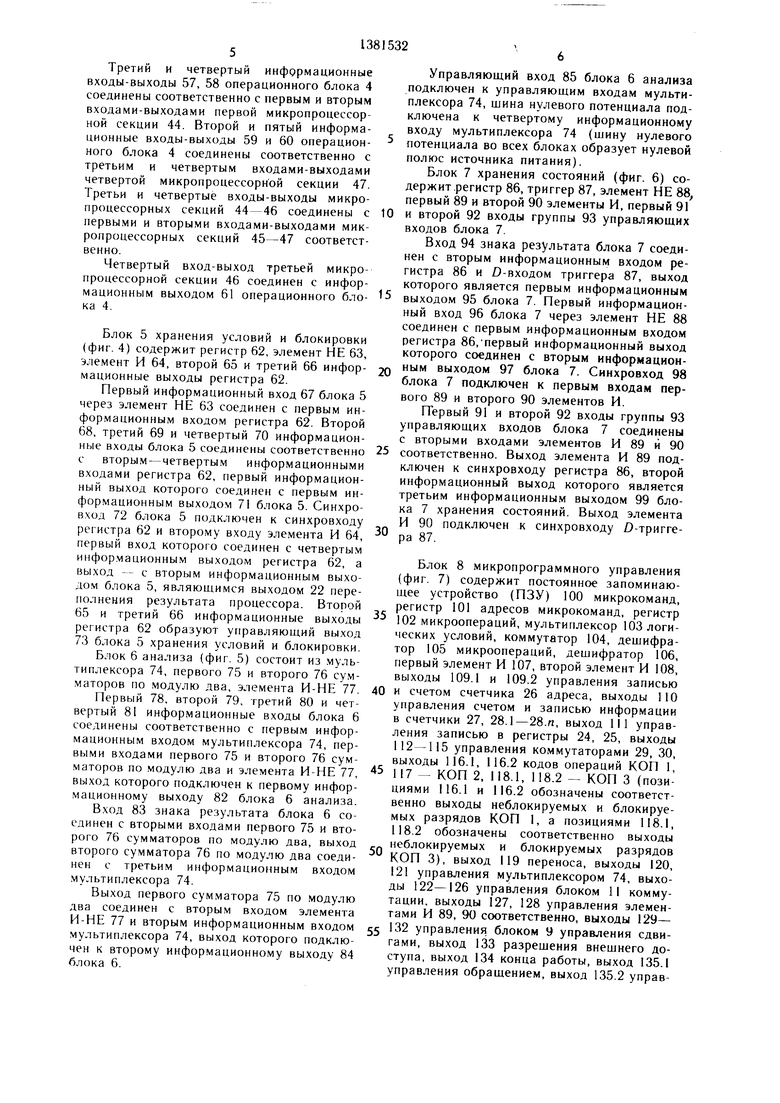

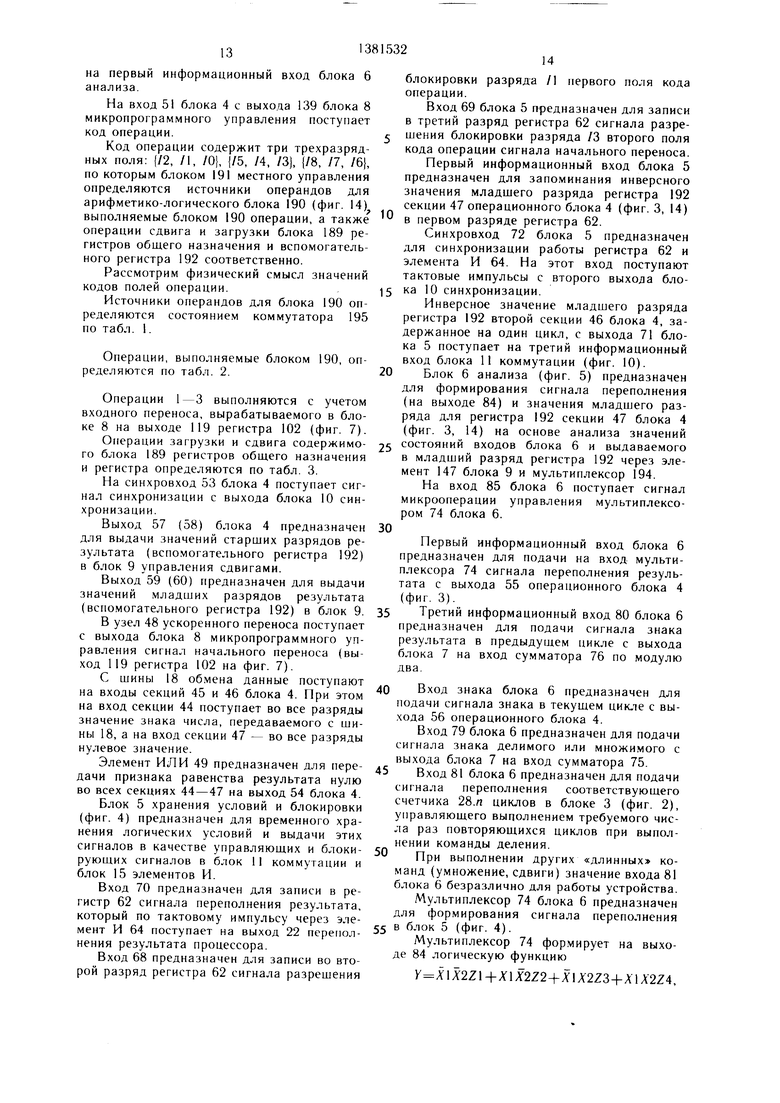

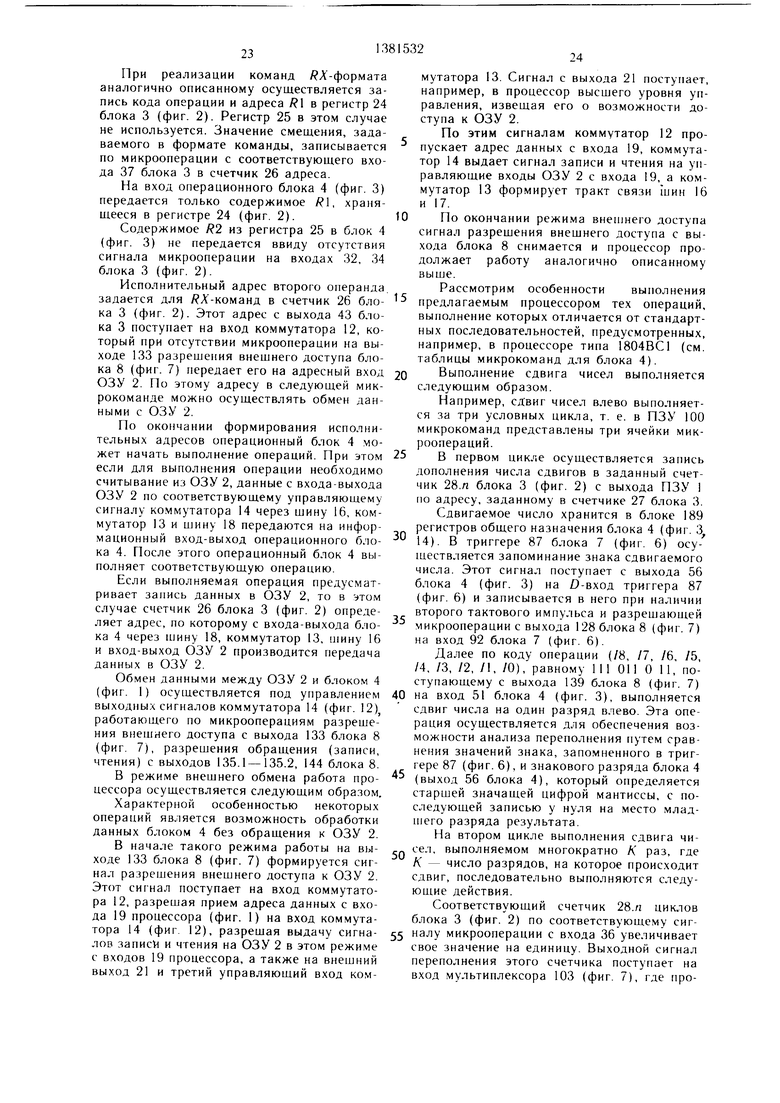

Операционный блок 4 (фиг. 3) содержит первую - четвертую микропроцессорные секции 44-47 соответственно, узел 48 уско20 ренного переноса, элемент ИЛИ 49.

Первый информационный вход-выход операционного блока 4, используемый для подключения этого блока к шине 18 обмена, соединен с входами-выходами данных вто25 рой и третьей микропроцессорных секций 45, 46, а знаковый разряд шины 18 обмена соединен с входом данных первой микропроцессорной секции 44. Вход данных четвертой микропроцессорной секцни 47 подключен к щине нулевого потенциала. Первый инфор30 мационный вход 50 (вход адресации операндов) подключен к адресным входам микропроцессорных секций 44-47. Второй информационный вход 51 (вход кода операции) подключен к входам кодов операции секций 44-47. Вход 52 входного переноса, вхокоммутации и выходом 22 переполнения ре- 35 дящий в состав второго информационного

входа 51, подключен к входу переноса секции 47 и к входу начального переноса узла 48 ускоренного переноса.

зультата процессора.

Первый информационный вход блока 7 хранения состояний соединен с вторым информационным входом блока 9 управления сдвигами и вторым информационным входом блока 6 анализа, второй информационный выход - с четвертым информационным входом блока 11 коммутации и третьим информационным входом блока 6 анализа.

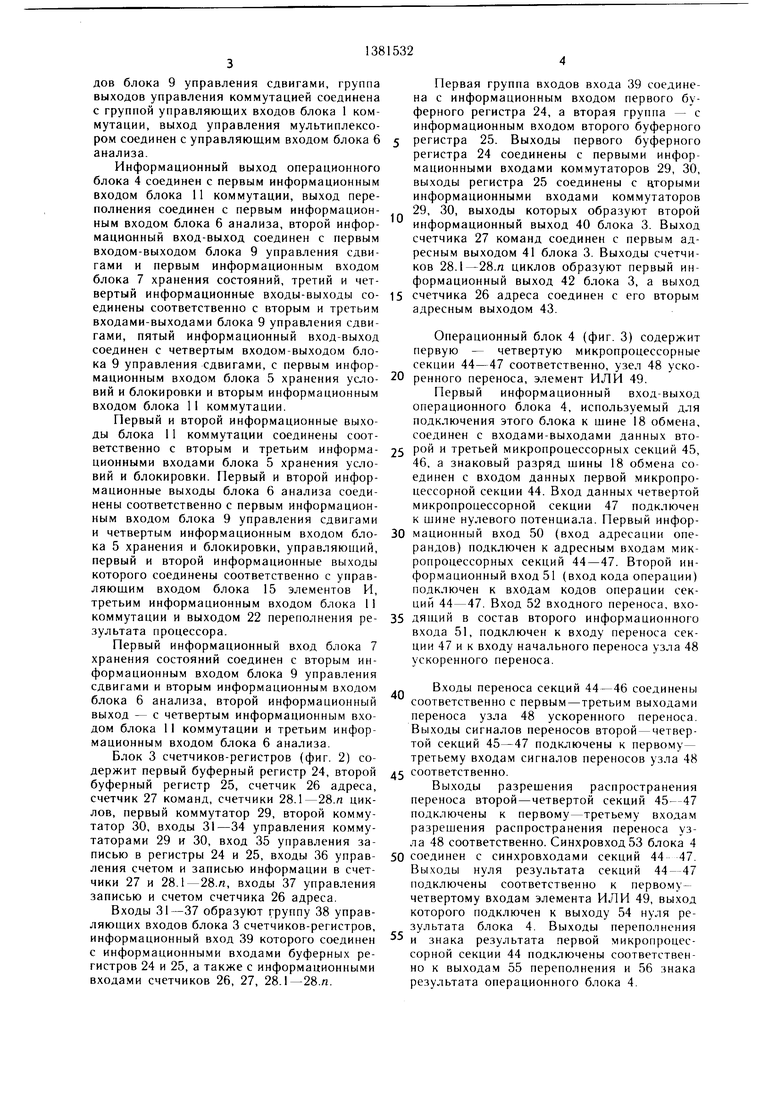

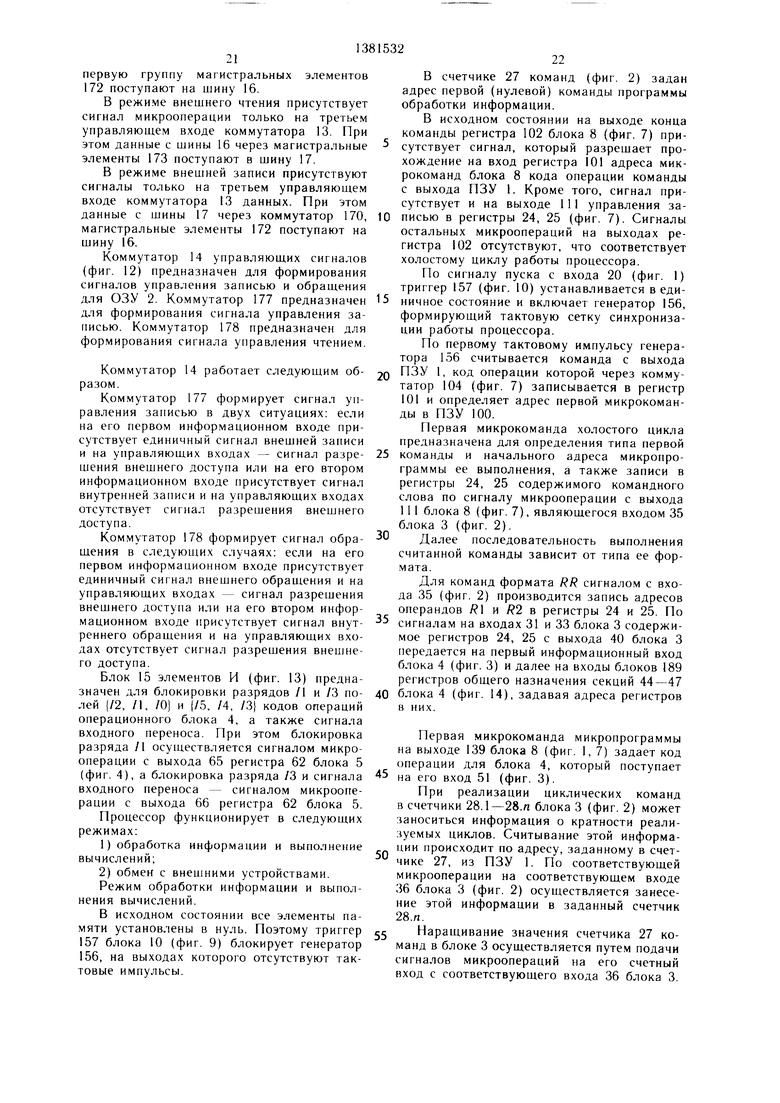

Блок 3 счетчиков-регистров (фиг. 2) содержит первый буферный регистр 24, второй буферный регистр 25, счетчик 26 адреса, счетчик 27 команд, счетчики 28.1-28.п циклов, первый коммутатор 29, второй коммутатор 30, входы 31-34 управления коммутаторами 29 и 30, вход 35 управления записью в регистры 24 и 25, входы 36 управления счетом и записью информации в счетчики 27 и 28.1-28.п, входы 37 управления записью и счетом счетчика 26 адреса.

Входы 31-37 образуют группу 38 управляющих входов блока 3 счетчиков-регистров, информационный вход 39 которого соединен с информационными входами буферных регистров 24 и 25, а также с информационными входами счетчиков 26, 27, 28.1-28.л.

Первая группа входов входа 39 соединена с информационным входом первого буферного регистра 24, а вторая группа - с информационным входом второго буферного регистра 25. Выходы первого буферного регистра 24 соединены с первыми информационными входами коммутаторов 29, 30, выходы регистра 25 соединены с аторыми информационными входами коммутаторов 29, 30, выходы которых образуют второй информационный выход 40 блока 3. Выход счетчика 27 команд соединен с первым адресным выходом 41 блока 3. Выходы счетчиков 28.1-28.л циклов образуют первый информационный выход 42 блока 3, а выход

счетчика 26 адреса соединен с его вторым

адресным выходом 43.

Операционный блок 4 (фиг. 3) содержит первую - четвертую микропроцессорные секции 44-47 соответственно, узел 48 ускоренного переноса, элемент ИЛИ 49.

Первый информационный вход-выход операционного блока 4, используемый для подключения этого блока к шине 18 обмена, соединен с входами-выходами данных второй и третьей микропроцессорных секций 45, 46, а знаковый разряд шины 18 обмена соединен с входом данных первой микропроцессорной секции 44. Вход данных четвертой микропроцессорной секцни 47 подключен к щине нулевого потенциала. Первый информационный вход 50 (вход адресации операндов) подключен к адресным входам микропроцессорных секций 44-47. Второй информационный вход 51 (вход кода операции) подключен к входам кодов операции секций 44-47. Вход 52 входного переноса, вхо 35 дящий в состав второго информационного

40

входа 51, подключен к входу переноса секции 47 и к входу начального переноса узла 48 ускоренного переноса.

Входы переноса секций 44 - 46 соединены соответственно с первым-третьим выходами переноса узла 48 ускоренного переноса. Выходы сигналов переносов второй - четвертой секций 45-47 подключены к первому- третьему входам сигналов переносов узла 48

д5 соответственно.

Выходы разрещения распространения переноса второй - четвертой секций 45-47 подключены к первому-третьему входам разрешения распространения переноса узла 48 соответственно. Синхровход53 блока 4

50 соединен с синхровходами секций 44 47. Выходы нуля результата секций 44-47 подключены соответственно к первому- четвертому входам элемента ИЛИ 49, выход которого подключен к выходу 54 нуля результата блока 4. Выходы переполнения и знака результата первой микропроцессорной секции 44 подключены соответственно к выходам 55 переполнения и 56 знака результата операционного блока 4.

55

Третий и четвертый информационные входы-выходы 57, 58 операционного блока 4 соединены соответственно с первым и вторым входами-выходами первой микропроцессорной секции 44. Второй и пятый информационные входы-выходы 59 и 60 операцион- ного блока 4 соединены соответственно с третьим и четвертым входами-выходами четвертой микропроцессорной секции 47. Третьи и четвертые входы-выходы микропроцессорных секций 44-46 соединены с первыми и вторыми входами-выходами микропроцессорных секций 45-47 соответственно.

Четвертый вход-выход третьей микропроцессорной секции 46 соединен с информационным выходом 61 операционного бло- ка 4.

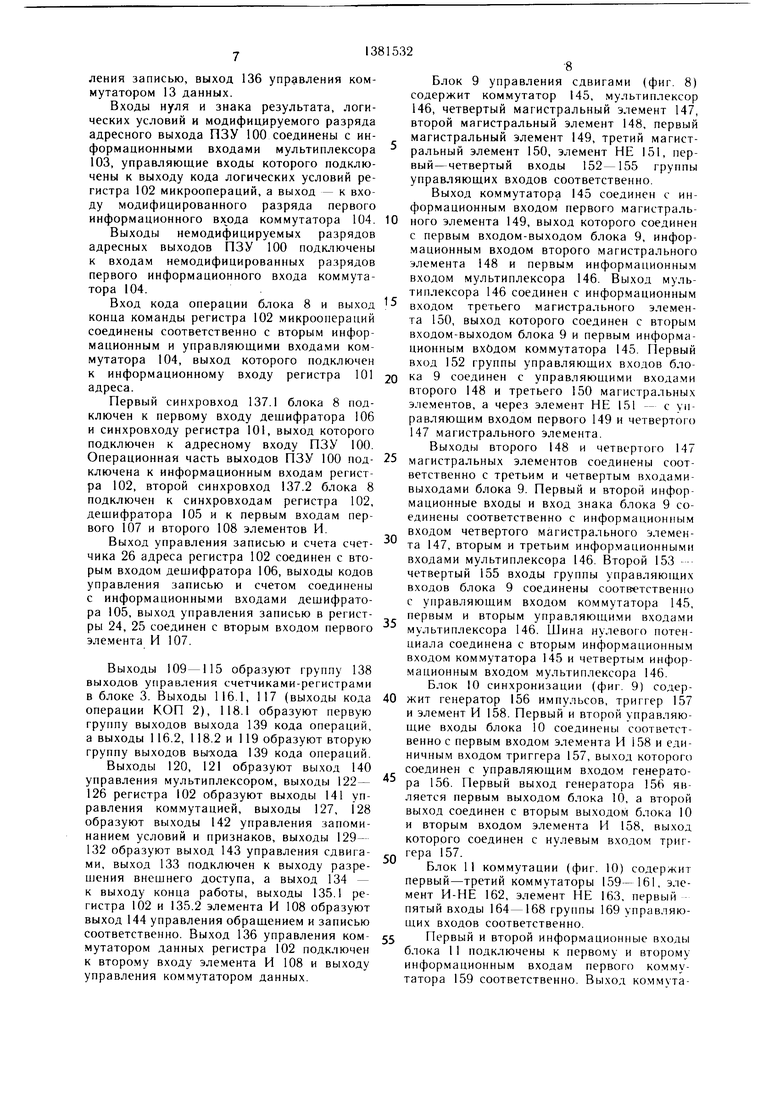

Блок 5 хранения условий и блокировки (фиг. 4) содержит регистр 62, элемент НЕ 63, элемент И 64, второй 65 и третий 66 инфор- мационные выходы регистра 62.

Первый информационный вход 67 блока 5 через элемент НЕ 63 соединен с первым информационным входом регистра 62. Второй 68, третий 69 и четвертый 70 информационные входы блока 5 соединены соответственно с вторым-четвертым информационными входами регистра 62, первый информационный выход которого соединен с первым информационным выходом 71 блока 5. Синхро- вход 72 блока 5 подключен к синхровходу регистра 62 и второму входу элемента И 64, первый вход которого соединен с четвертым информационным выходом регистра 62, а выход - с вторым информационным выходом блока 5, являющимся выходом 22 переполнения результата процессора. Второй 65 и третий 66 информационные выходы регистра 62 образуют управляющий выход 73 блока 5 хранения условий и блокировки.

Блок 6 анализа (фиг. 5) состоит из мультиплексора 74, первого 75 и второго 76 су.м- маторов по модулю два, э-темента И-НЕ 77.

Первый 78, второй 79, третий 80 и четвертый 81 информационные входы блока 6 соединены соответственно с первым информационным входом мультиплексора 74, первыми входами первого 75 и второго 76 сумматоров по модулю два и элемента И-НЕ 77, выход которого подключен к первому информационному выходу 82 блока 6 анализа.

Вход 83 знака результата блока 6 соединен с вторыми входами первого 75 и второго 76 сумматоров по модулю два, выход второго сумматора 76 по модулю два соеди- нен с третьим информационным входом .мультиплексора 74.

Выход первого сумматора 75 по модулю два соединен с вторым входом элемента И-НЕ 77 и вторым информационным входом мультиплексора 74, выход которого подключен к второму информационному выходу 84 блока 6.

Управляющий вход 85 блока 6 анализа подключен к управляющим входам мультиплексора 74, щина нулевого потенциала подключена к четвертому информационному входу мультиплексора 74 (шину нулевого потенциала во всех блоках образует нулевой полюс источника питания).

Блок 7 хранения состояний (фиг. 6) содержит .регистр 86, триггер 87, элемент НЕ 88, первый 89 и второй 90 элементы И, первый 91 и второй 92 входы группы 93 управляющих входов блока 7.

Вход 94 знака результата блока 7 соединен с вторым информационным входом регистра 86 и D-входом триггера 87, выход которого является первым информационным выходом 95 блока 7. Первый информационный вход 96 блока 7 через элемент НЕ 88 соединен с первым информационным входом регистра 86, первый информационный выход которого соединен с вторым информационным выходом 97 блока 7. Сиихровход 98 блока 7 подключен к первым входам первого 89 и второго 90 элементов И.

Первый 91 и второй 92 входы группы 93 управляющих входов блока 7 соединены с вторыми входами элементов И 89 и 90 соответственно. Выход элемента И 89 подключен к синхровходу регистра 86, второй информационный выход которого является третьим информационным выходом 99 блока 7 хранения состояний. Выход элемента И 90 подключен к синхровходу )-тригге- ра 87.

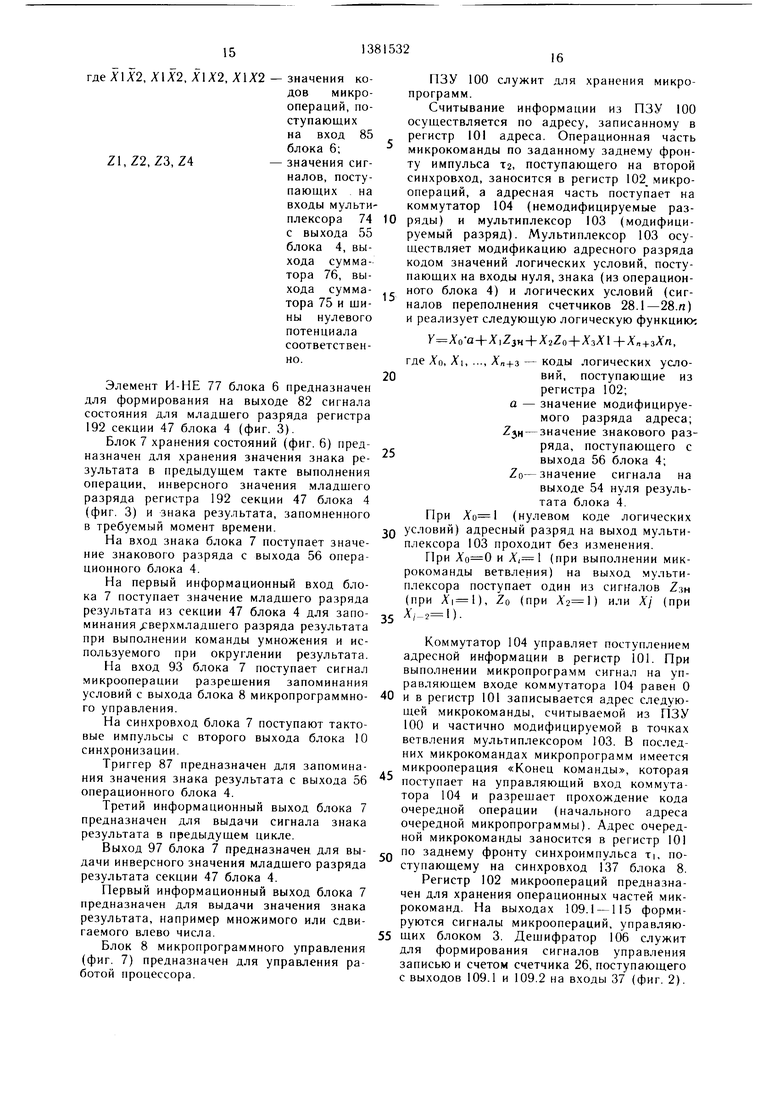

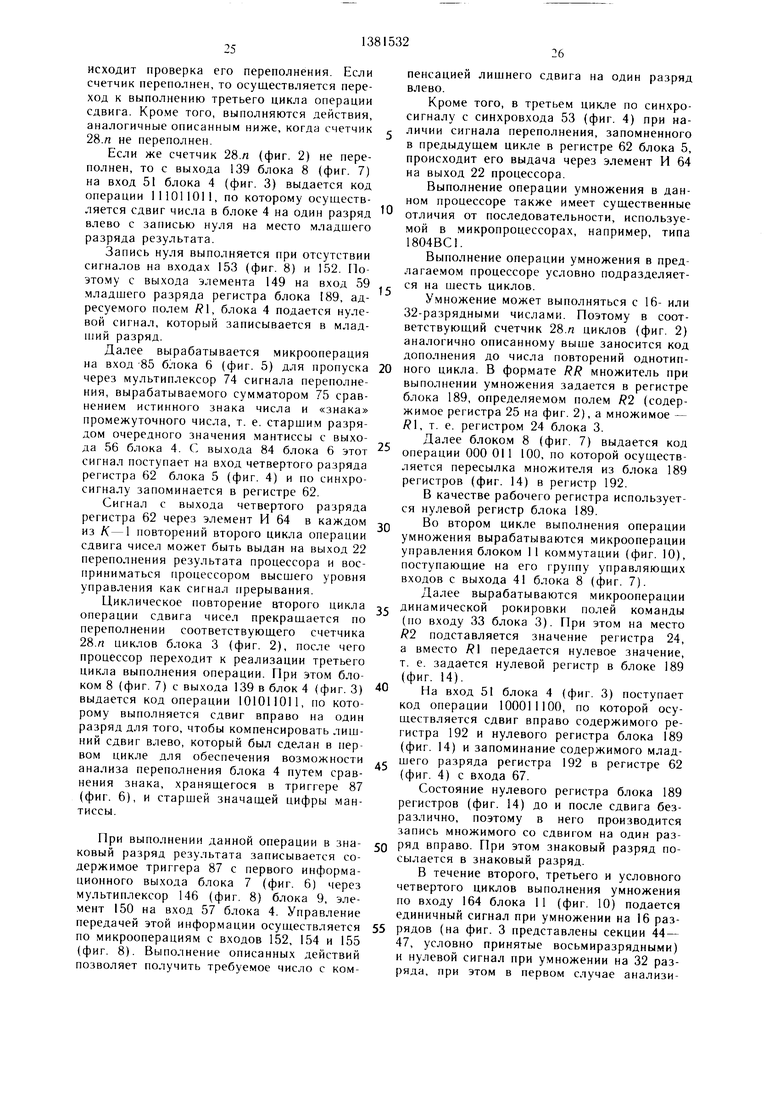

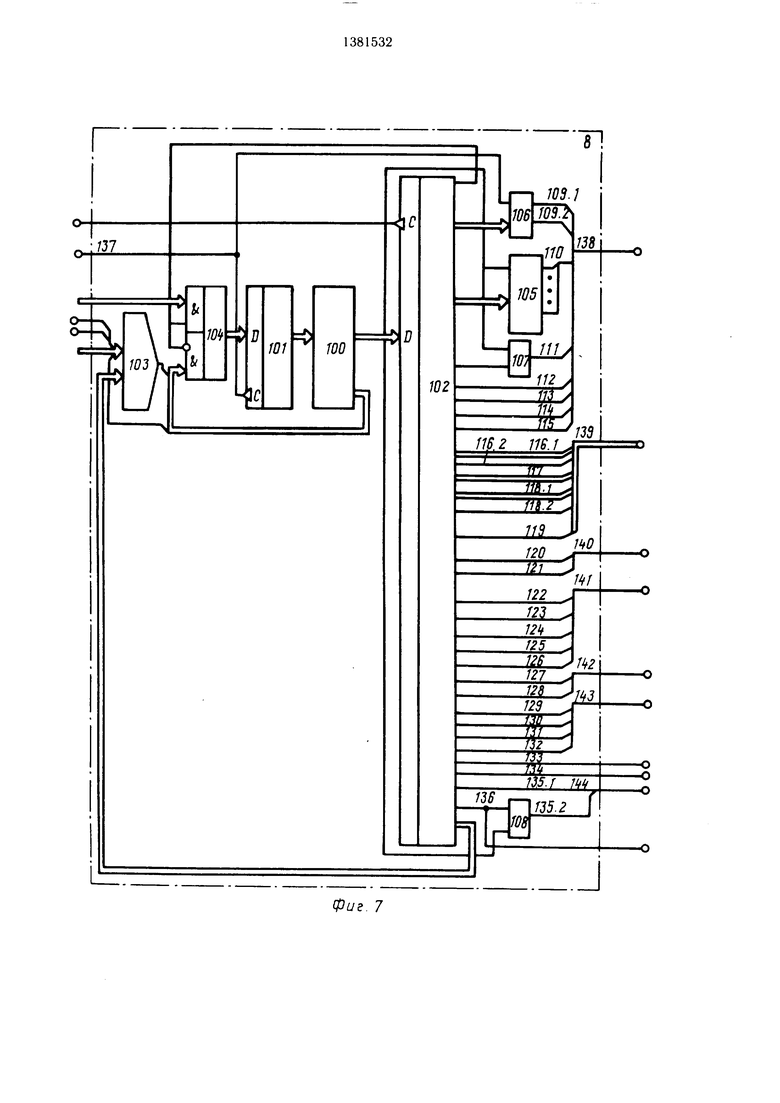

Блок 8 микропрограммного управления (фиг. 7) содержит постоянное запоминающее устройство (ПЗУ) 100 микрокоманд, регистр 101 адресов микрокоманд, регистр 102 микроопераций, мультиплексор 103 логических условий, коммутатор 104, дешифратор 105 микроопераций, дешифратор 106, первый элемент И 107, второй элемент И 108, выходы 109.1 и 109.2 управления записью и счетом счетчика 26 адреса, выходы 110 управления счетом и записью информации в счетчики 27, 28.1-28.и, выход 111 управления записью в регистры 24, 25, выходы 112-115 управления коммутаторами 29, 30, выходы 116.1, 116.2 кодов операций КОП 1, 117 - КОП 2, 118.1, 118.2 - КОП 3 (позициями 116.1 и 116.2 обозначены соответственно выходы неблокируемых и блокируемых разрядов КОП 1, а позициями 118.1, 118.2 обозначены соответственно выходы неблокируемых и блокируемых разрядов КОП 3), выход 119 переноса, выходы 120, 121 управления мультиплексором 74, выходы 122-126 управления блоком II коммутации, выходы 127, 128 управления элементами И 89, 90 соответствеино, выходы 129- 132 управления блоком 9 управления сдвигами, выход 133 разрешения внешнего доступа, выход 134 конца работы, выход 135.1 управления обращением, выход 135.2 управления записью, выход 136 управления коммутатором 13 данных.

Входы нуля и знака результата, логических условий и модифицируемого разряда адресного выхода ПЗУ 100 соединены с информационными входами мультиплексора 103, управляющие входы которого подключены к выходу кода логических условий регистра 102 микроопераций, а выход - к входу модифицированного разряда первого информационного коммутатора 104.

Выходы немодифицируемых разрядов адресных выходов ПЗУ 100 подключены к входам немодифицированных разрядов первого информационного входа коммутатора 104.

Вход кода операции блока 8 и выход конца команды регистра 102 микроопераций соединены соответственно с вторым информационным и управляющими входами коммутатора 104, выход которого подключен к информационному входу регистра 101 адреса.

Первый синхровход 137.1 блока 8 подключен к первому входу дешифратора 106 и синхровходу регистра 101, выход которого подключен к адресному входу ПЗУ 100. Операционная часть выходов ПЗУ 100 под- ключена к информационным входам регистра 102, второй синхровход 137.2 блока 8 подключен к синхровходам регистра 102, дешифратора 105 и к первым входам первого 107 и второго 108 элементов И.

Выход управления записью и счета счетчика 26 адреса регистра 102 соединен с вторым входом дешифратора 106, выходы кодов управления записью и счетом соединены с информационными входами дешифратора 105, выход управления записью в регистры 24, 25 соединен с вторым входом первого элемента И 107.

Выходы 109-115 образуют группу 138 выходов управления счетчиками-регистрами в блоке 3. Выходы 116.1, 117 (выходы кода операции КОП 2), 118.1 образуют первую группу выходов выхода 139 кода операций, а выходы 116.2, 118.2 и 119 образуют вторую группу выходов вы-хода 139 кода операций.

Выходы 120, 121 образуют выход 140 управления мультиплексором, выходы 122- 126 регистра 102 образуют выходы 141 управления коммутацией, выходы 127, 128 образуют выходы 142 управления запоминанием условий и признаков, выходы 129- 132 образуют выход 143 управления сдвигами, выход 133 подключен к выходу разре- внешнего доступа, а выход 134 - к выходу конца работы, выходы 135.1 регистра 102 и 135.2 элемента И 108 образуют выход 144 управления обращением и записью соответственно. Выход 136 управления ком- мутатором данных регистра 102 подключен к второму входу элемента И 108 и выходу управления коммутатором данных.

0

5 0

5

5

0

5

0

5

0

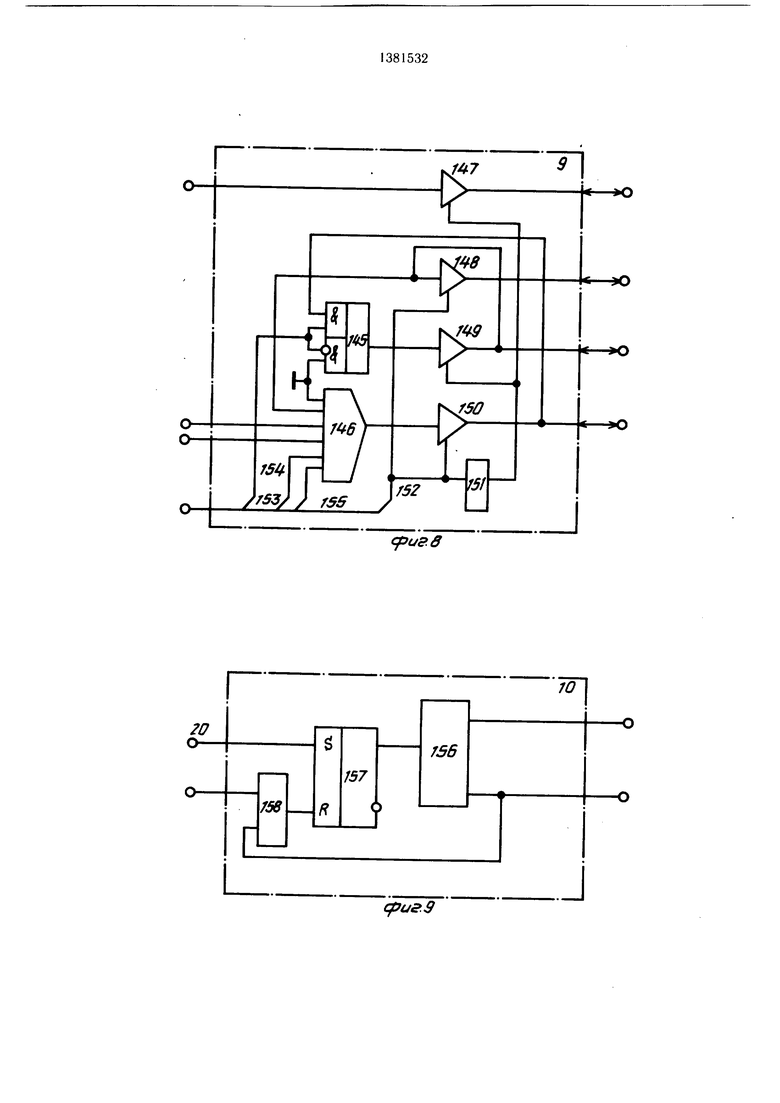

Блок 9 управления сдвигами (фиг. 8) содержит коммутатор 145, мультиплексор 146, четвертый магистральный элемент 147, второй магистральный элемент 148, первый магистральный элемент 149, третий магистральный элемент 150, элемент НЕ 151, первый- четвертый входы 152-155 группы управляющих входов соответственно.

Выход коммутатора 145 соединен с информационным входом первого магистрального элемента 149, выход которого соединен с первым входом-выходом блока 9, информационным входом второго магистрального элемента 148 и первым информационны.м входом мультиплексора 146. Выход мультиплексора 146 соединен с информационным входом третьего магистрального элемента 150, выход которого соединен с вторым входом-выходом блока 9 и первым информационным входом коммутатора 145. Первый вход 152 группы управляющих входов блока 9 соединен с управляющими входами второго 148 и третьего 150 магистральных элементов, а через элемент НЕ 151 - с управляющим входом первого 149 и четвертого 147 магистрального элемента.

Выходы второго 148 и четвертого 147 магистральных элементов соединены соответственно с третьим и четвертым входами- выходами блока 9. Первый и второй информационные входы и вход знака блока 9 соединены соответственно с информационным входом четвертого магистрального элемента 147, вторым и третьим информационными входами мультиплексора 146. Второй 153 четвертый 155 входы группы управляющих входов блока 9 соединены соответственно с управляющим входом коммутатора 145, первым и вторым управляющими входами мультиплексора 146. Шина нулевого потенциала соединена с вторым информационным входом коммутатора 145 и четвертым информационным входом мультиплексора 146.

Блок 10 синхронизации (фиг. 9) содержит генератор 156 импульсов, триггер 157 и элемент И 158. Первый и второй управляющие входы блока 10 соединены соответственно с первым входом элемента И 158 и единичным входом триггера 157, выход которого соединен с управляющим входом генератора 156. Первый выход генератора 156 является первым выходом блока 10, а второй выход соединен с вторым выходом блока 10 и вторым входом элемента И 158, выход которого соединен с нулевым входом триггера 157.

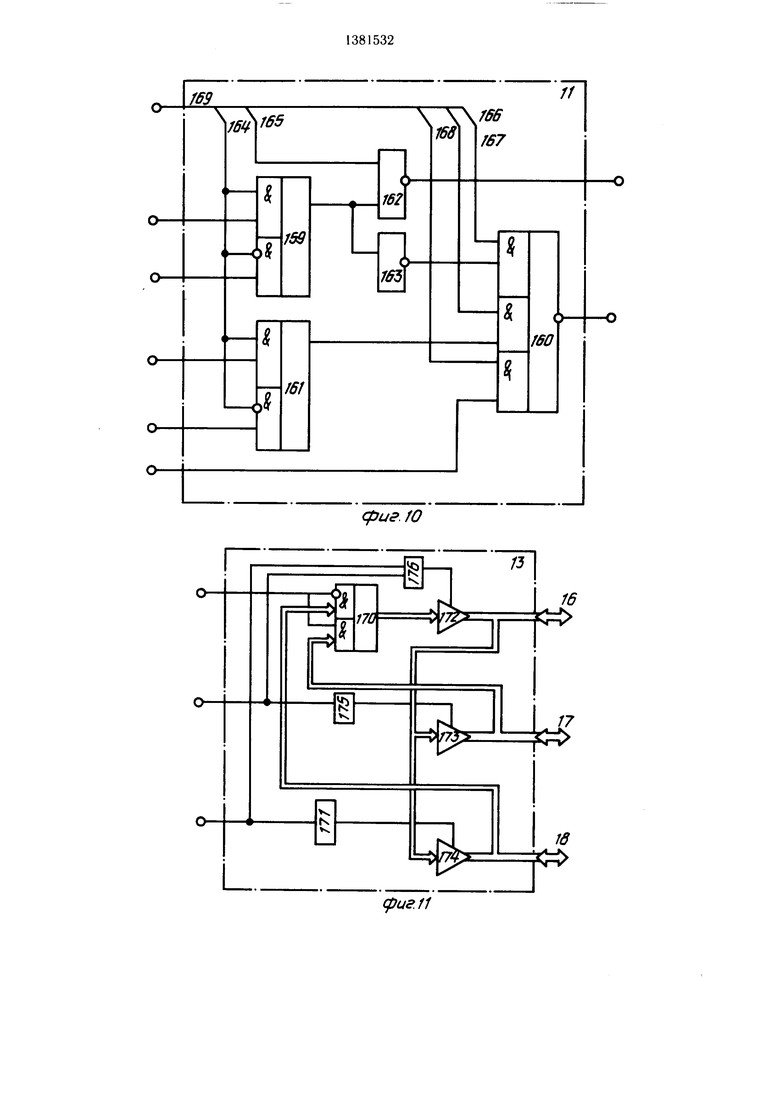

Блок 11 коммутации (фиг. 10) содержит первый-третий коммутаторы 159-161, элемент И-НЕ 162, элемент НЕ 163, первый пятый входы 164-168 группы 169 управляющих входов соответственно.

Первый и второй информационные входы блока 11 подключены к первому и второму информационным входам первого коммутатора 159 соответственно. Выход коммутатора 159 соединен с первым входом элемента И-НЕ 162, а через элемент НЕ 163 - с первым информационным входом второго коммутатора 160. Первый 164 - пятый 168 входы группы 169 управляющих входов соединены соответственно с управляющими входами коммутаторов 159, 161, вторым входом элемента И-НЕ 162, первым, вторым и третьим управляющими входами коммутатора 160. Выходы элемента И-НЕ 162 и коммутатора 160 соединены соответственно с первым и вторым информационными выходами блока 11. Третий и четвертый информационные входы блока 11 соединены соответственно с первым информационным входом коммутатора 161 и третьим информационным входом коммутатора 160.

Пятый информационный вход блока 11 соединен с вторым информационным входом коммутатора 161, выход которого подключен к второму информационному входу коммутатора 160.

Коммутатор 13 данных (фиг. 11) содержит коммутатор 170, первый элемент НЕ 171, первую - третью группы 172-174 магистральных элементов соответственно, второй элемент НЕ 175 и элемент ИЛИ 176.

Выход коммутатора 170 соединен с информационными входами первой группы 172 магистральных элементов, выходы которых соединены с вторым информационным входом-выходом коммутатора 13 данных (щи- ной 16) и информационными входами второй 173 и третьей 174 групп магистральных элементов. Первый управляющий вход коммутатора 13 данных соединен с первым входом элемента ИЛИ 176 и через второй элемент НЕ 175 с управляющими входами второй группы I7i3 магистральных элементов, выходы которых подключены к первому информационному входу-выходу коммутатора 13 данных (HJHHe 17) и к первому информационному входу коммутатора 170. Второй управляющий вход коммутатора 13 данных соединен с вторым входом элемента ИЛИ 176, выходом подключенным к управляющим входам первой группы 172 магистральных элементов и через элемент НЕ 171 - с управляющими входами третьей группы 174 магистральных элементов, выходы которых подключены к третьему информационному входу-выходу коммутатора 13 данных (щи- не 18) и второму информационному входу коммутатора 170. Третий управляющий вход коммутатора 13 данных подключен к управляющему входу коммутатора 170.

Коммутатор 14 управляющих сигналов (фиг. 12) содержит первый 177 и второй 178 коммутаторы, вход 179 внещней записи, вход 180 внещнего обращения, вход 181 внутренней записи, вход 182 внутреннего обращения.

Входы 179 и 180 образуют первый информационный вход коммутатора 14 управляющих сигналов и подключены к первым информационным входам первого 177 и второго 178 коммутаторов соответственно, выходы которых являются соответственно первым и вторым выходами коммутатора 14 управляющих сигналов. Входы 181 и 182 образуют второй информационный вход коммутатора 14 управляющих сигналов и подключены к вторым информационным входам коммутаторов 177 и 178 соответственно.

Управляющий вход коммутатора 14 управляющих сигналов соединен с управляющими входами коммутаторов 177 и 178.

Блок 15 элементов И (фиг. 13) содержит первый-третий элементы И 183-185, входы 186-188 входного переноса и разрядов ко5 дов операции КОП 3, КОП 1 соответственно. Входы 186-188 образуют информационный вход блока 15 и подключены к первым входам элементов И 183-185 соответственно. Вторые входы элементов И 183, 184 со- единены между собой и с управляющим входом, соответствующим выходу 66 регистра 62 в блоке 5, второй вход элемента И 185 соединен с управляющим входом, соответствующим выходу 65 регистра 62 в блоке 5 хранения условий и блокировки.

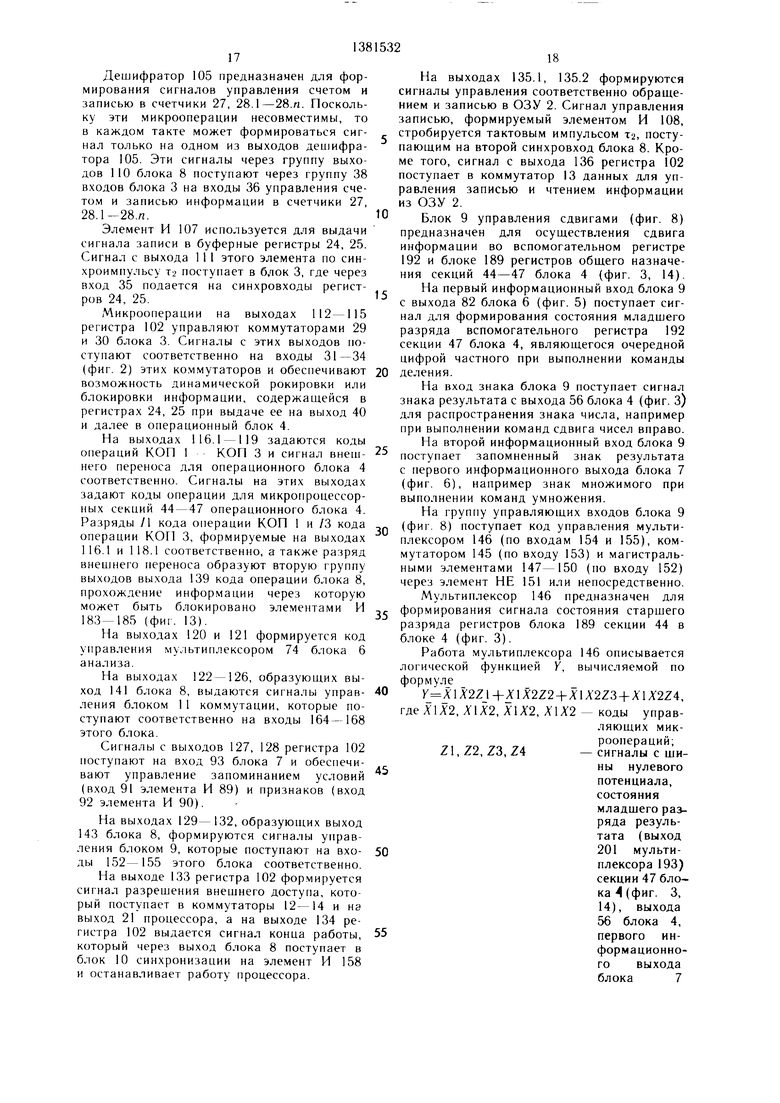

5 Каждая из микропроцессорных секций 44-47 (фиг. 14) содержит блок 189 регистров общего назначения, арифметико-логический блок 190, блок 191 местного управления, вспомогательный регистр 192, первый 193 и второй 194 мультиплексоры, коммута0 тор 195, блок 196 магистральных элементов, выходы 197-199 переполнения, знака и нуля результата соответственно, первый 200 - четвертый 203 входы-выходы, информационный выход 204 блока 190, информационный вход 205 мультиплексора 193, первый 206 -

5 четвертый 209 информационные входы коммутатора 195, первый 210 и второй 211 выходы коммутатора 195, первый 212 и второй 213 информационные входы и выход 214 регистра 192.

0 Особенности использования микропроцессорных секций 44-47 в блоке 4 состоят в следующем: в секции 44 не используются выходы разрещения распространения переноса и сигнала переноса; в секциях 45-47 не используются выходы 197 и 198 сигнала

5 переполнения и знака результата соответственно.

ПЗУ 1 предназначено для хранения команд, констант, индексов, начальных адресов подпрограмм, приращений, смещений. С выхода ПЗУ 1 код операции команды по0 ступает на вход кода операции блока 8 микропрограммного управления.

Адрес при обращении к ПЗУ 1 формируется на первом адресном выходе блока 3 С счетчиков-регистров, являющемся одновременно выходом счетчика 27 команд (фиг. 2). ПЗУ 1 является ЗУ статического типа и может быть собрано, например, на микросхемах 556РТ5.

ОЗУ 2 предназначено для временного хранення данных в процессе выполнения вычислений. Доступ к ОЗУ 2 может осуществляться через коммутатор 12 как по адресу, задаваемому в счетчике 26 адреса блока 3 счетчиков-регистров (фнг. 2) с целью обработки их операционным блоком 4, так и с адресного входа 19 в случаях разрешения внешнего доступа.

ОЗУ 2 может быть выполнено по типовой схеме ОЗУ, например марки 541 РУ 1.

Команды процессора используются в формате регистр-регистр () и регистр- память (RX).

В формате RR-команд, содержатся поля кода операции, адреса первого (/ 1) и вто- рого (R 2) операндов.

Формат / А -команд подразделяется на поля кода операции, адреса первого операнда (R 1) и смещения (D),

В обоих форматах команд адрес R (R 2} задает номер регистра общего назначения в блоке 189 регистров общего назначения микропроцессорной секции 44 (фиг. 14). Смещение задает адрес первого числа в режимах прямой адресации (адресации с автоиндексацией) .

Принцип формирования- исполнительных адресов в процессоре состоит в следующем.

Код команды считывается с выхода ПЗУ 1. При этом код операции поступает на вход кода операции блока 8 микропрограммного управления, адресная часть кода команды поступает на вход блока 3 регистров-счетчиков (фиг. 2).

При выполнении команд формата RR адреса первого (/ 1) и второго (R 2) операндов поступают с выходов буферных регистров 24 и 25 первого и второго операндов через коммутаторы 29 и 30 блока 3 на выход 40 блока 3 и далее на первый информационный вход операционного блока 4 (фиг. 3).

При выполнении команд форматов RX адрес первого операнда R 1 аналогично описанному для RR-KOMatia поступает на вход блока 4. Адрес второго операнда может задаваться смещением D в формате команды. Этот адрес поступает с входа 39 блока 3 в счетчик 26 адреса и далее через выход 43 блока 3 на вход коммутатора 12 адреса, связанного с адресным входом ОЗУ 2. В ОЗУ 2 по заданному адресу может осуществляться запись или считывание данных в зависимости от управляющих сигналов, формируемых коммутатором 14 управляющих сигналов.

Коммутаторы 29 и 30 (фиг. 2) предназначены для маскирования и динамической рокировки адресных полей (/ 1 и / 2) в процессе выполнения микропрограмм длинных команд. Это позволяет, например, выполнять обнуление регистров общего назначения в операционном блоке 4 в процессе или при 3aBepujeHHH выполнения таких команд.

0

5

не прибегая к программным средствам, а используя только аппаратно-микронрограм- мные средства процессора.

Счетчик 27 команд предназначен для задания адреса информации, считываемой из ПЗУ 1, по адресу, формируемому на выходе 41 блока 3.

Счетчики 28.1-28.п циклов предназначены для хранения значений счетчиков циклов при выполнении вычислений. Информация в эти счетчики записывается с выхода ПЗУ 1.

Операционный блок 4 (фиг. 3) предназначен для выполнения обработки данных и может быть построен по типовой схеме, например на микропроцессорном комплекте 1804 ВС1.

Через первый информационный вход- выход блока 4 осуществляется обмен данными с щиной 18 обмена.

Разрядность исходного представления чисел в ОЗУ 2 соответствует суммарной раз- 0 рядности секций 45 и 46. Секции 44 и 47 блока 4 предназначены для обеспечения возможности выполнения вычислений с разрядностью, превышающей исходное представление. При этом в секции 44 блока 4 осуществляется накопление старщей части результатов - разрядов переполнения результата в секции 45 или при сдвигах влево при обработке больщих массивов данных, а в секции 47 - накопление младшей части результатов для команд умножения и сдвигов вправо, кроме того, при наличии данных в секциях 44 и 47 после умножений, сдвигов и других команд, в которых появляются переполнения, они обрабатываются в обычном порядке как данные с увеличенной разрядностью.

Узел 48 предназначен для выполнения ускоренного переноса между секциями и может быть выполнен по типовой схеме, например 133ИП4.

Выход 56 блока 4 предназначен для выдачи сигнала знака результата на соответст- 0 вующий вход блока 8 микропрограммного управления, на третий информационный вход блока 9 управления сдвигами и на входы знаков результата блока 6 анализа и блока 7 хранения состояния.

Выход 54 блока 4 предназначен для выдачи сигнала нулевого результата секций 44-47 блока 4. Этот сигнал поступает на соответствующий вход блока 8 и используется для организации ветвлений в микропрограмме.

Выход 61 блока 4 является выходом младшего разряда вспомогательного регистра 192 секции 46 (фиг. 3 и 14) операционного блока 4. С выхода 61 сигнал состояния этого разряда поступает на первый информационный вход блока 11 коммутации.

0

5

5

0

55

Выход 55 блока 4 предназначен для подачи сигнала истинного переполнения результата (ф) с выхода секции 44 блока 4

на первый информационный вход блока 6 анализа.

На вход 51 блока 4 с выхода 139 блока 8 микронрограммного управления поступает код операции.

Код операции содержит три трехразрядных поля: (/2, /1, /0}, J/5, /4, /3), {/8, /7, /6), по которым блоком 191 местного управления определяются источники операндов для арифметико-логического блока 190 (фиг. 14) выполняемые блоком 190 операции, а также операции сдвига и загрузки блока 189 регистров общего назначения и вспомогательного регистра 192 соответственно.

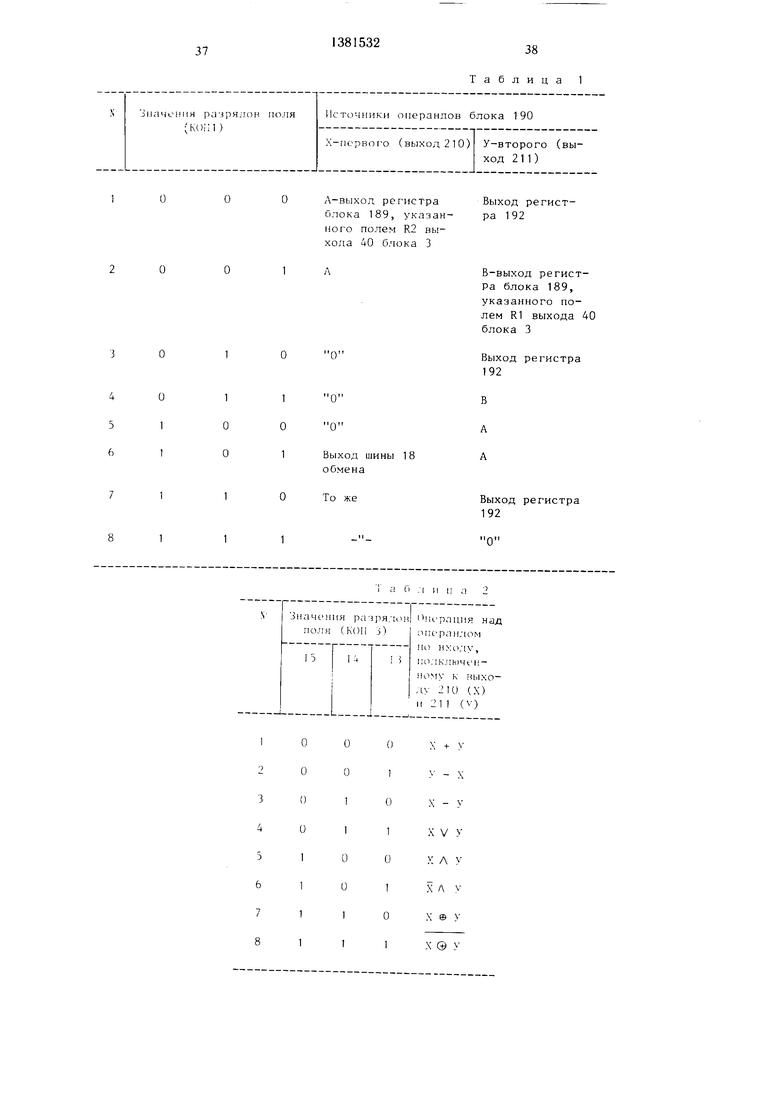

Рассмотрим физический смысл значений кодов полей операции.

Источники операндов для блока 190 определяются состоянием коммутатора 195 по табл. 1.

Операции, выполняемые блоком 190, определяются по табл. 2.

Операции 1-3 выполняются с учетом входного переноса, вырабатываемого в блоке 8 на выходе 119 регистра 102 (фиг. 7).

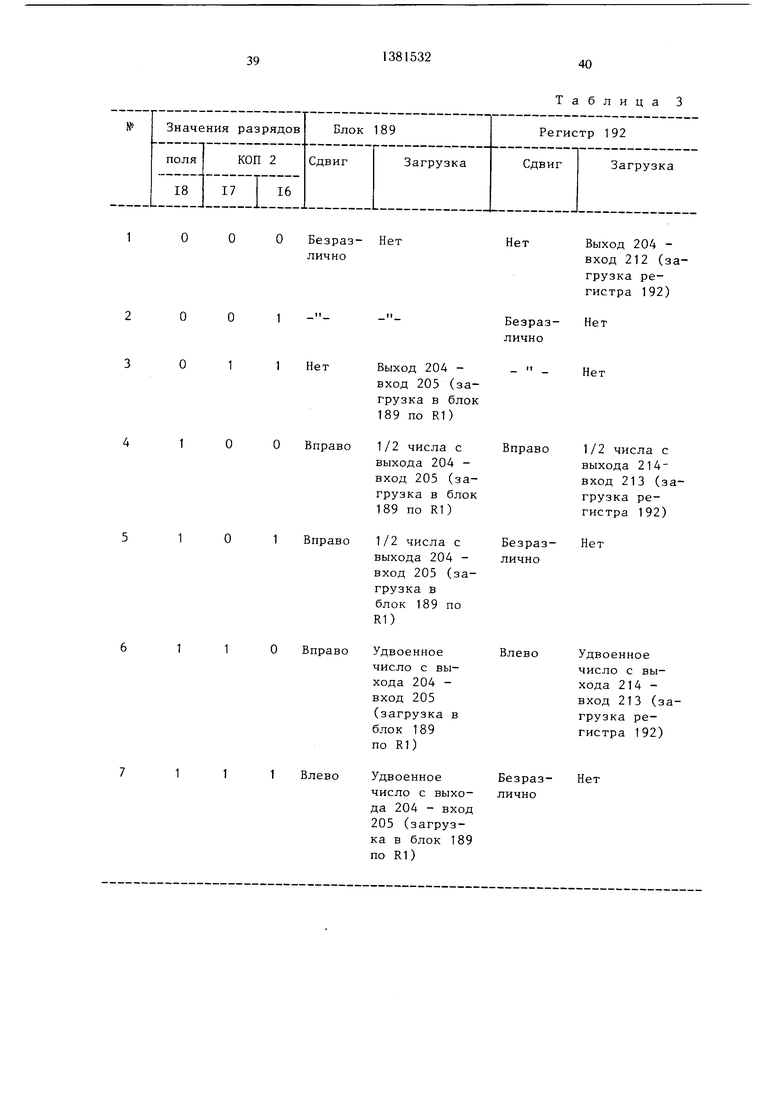

Операции загрузки и сдвига содержимого блока 189 регистров общего назначения и регистра определяются по табл. 3.

На синхровход 53 блока 4 поступает сигнал синхронизации с выхода блока 10 синхронизации.

Выход 57 (58) блока 4 предназначен для выдачи значений старших разрядов результата (вспомогательного регистра 192) в блок 9 управления сдвигами.

Выход 59 (60) предназначен для выдачи значений младших разрядов результата (вспомогательного регистра 192) в блок 9.

В узел 48 ускоренного переноса поступает с выхода блока 8 микропрограммного управления сигнал начального переноса (выход 119 регистра 102 на фиг. 7).

С шины 18 обмена данные поступают на входы секций 45 и 46 блока 4. При этом на вход секции 44 поступает во все разряды значение знака числа, передаваемого с шины 18, а на вход секции 47 - во все разряды нулевое значение.

Элемент ИЛИ 49 предназначен для передачи признака равенства результата нулю во всех секциях 44-47 на выход 54 блока 4.

Блок 5 хранения условий и блокировки (фиг. 4) предназначен для временного хранения логических условий и выдачи этих сигналов в качестве управляющих и блокирующих сигналов в блок 1I коммутации и блок 15 элементов И.

Вход 70 предназначен для записи в регистр 62 сигнала переполнения результата.

10

20

25

блокировки разряда /1 первого поля кода операции.

Вход 69 блока 5 предназначен для записи в третий разряд регистра 62 сигнала разрешения блокировки разряда /3 второго поля кода операции сигнала начального переноса.

Первый информационный вход блока 5 предназначен для запоминания инверсного значения младшего разряда регистра 192 секции 47 операционного блока 4 (фиг. 3, 14) в первом разряде регистра 62.

Синхровход 72 блока 5 предназначен

для синхронизации работы регистра 62 и

элемента И 64. На этот вход поступают

тактовые импульсы с второго выхода бло15 ка 10 синхронизации.

Инверсное значение младшего разряда регистра 192 второй секции 46 блока 4, задержанное на один цикл, с выхода 71 блока 5 поступает на третий информационный вход блока 11 коммутации (фиг. 10).

Блок 6 анализа (фиг. 5) предназначен для формирования сигнала переполнения (на выходе 84) и значения младшего разряда для регистра 192 секции 47 блока 4 (фиг. 3, 14) на основе анализа значений состояний входов блока 6 и выдаваемого в младший разряд регистра 192 через элемент 147 блока 9 и мультиплексор 194.

На вход 85 блока 6 поступает сигнал микрооперации управления мультиплексором 74 блока 6.

30

Первый информационный вход блока 6 предназначен для подачи на вход мультиплексора 74 сигнала переполнения результата с выхода 55 операционного блока 4 (фиг. 3).

35 Третий информационный вход 80 блока 6 предназначен для подачи сигнала знака результата в предыдущем цикле с выхода блока 7 на вход сумматора 76 по модулю два.

40 Вход знака блока 6 предназначен для подачи сигнала знака в текущем цикле с выхода 56 операционного блока 4.

Вход 79 блока 6 предназначен для подачи сигнала знака делимого или множимого с выхода блока 7 на вход сумматора 75.

Вход 81 блока 6 предназначен для подачи сигнала переполнения соответствующего счетчика 28.п циклов в блоке 3 (фиг. 2), управляющего выполнением требуемого числа раз повторяющихся циклов при выполнении команды деления.

При выполнении других «длинных команд (умножение, сдвиги) значение входа 81 блока 6 безразлично для работы устройства.

Мультиплексор 74 блока 6 предназначен

45

50

для формирования сигнала переполнения

который по тактовому импульсу через эле- J 5 (фиг. 4).

мент И 64 поступает на выход 22 перепол-- ... -гл

нения результата процессора.Мультиплексор 74 формирует на выхоп со F кде 84 логическую функцию

Вход 68 предназначен для записи во вто- .

рой разряд регистра 62 сигнала разрешенияY X X2Z +X X2Z2+X X2Z3+X X2Z4,

0

5

блокировки разряда /1 первого поля кода операции.

Вход 69 блока 5 предназначен для записи в третий разряд регистра 62 сигнала разрешения блокировки разряда /3 второго поля кода операции сигнала начального переноса.

Первый информационный вход блока 5 предназначен для запоминания инверсного значения младшего разряда регистра 192 секции 47 операционного блока 4 (фиг. 3, 14) в первом разряде регистра 62.

Синхровход 72 блока 5 предназначен

для синхронизации работы регистра 62 и

элемента И 64. На этот вход поступают

тактовые импульсы с второго выхода блока 10 синхронизации.

Инверсное значение младшего разряда регистра 192 второй секции 46 блока 4, задержанное на один цикл, с выхода 71 блока 5 поступает на третий информационный вход блока 11 коммутации (фиг. 10).

Блок 6 анализа (фиг. 5) предназначен для формирования сигнала переполнения (на выходе 84) и значения младшего разряда для регистра 192 секции 47 блока 4 (фиг. 3, 14) на основе анализа значений состояний входов блока 6 и выдаваемого в младший разряд регистра 192 через элемент 147 блока 9 и мультиплексор 194.

На вход 85 блока 6 поступает сигнал микрооперации управления мультиплексором 74 блока 6.

0

Первый информационный вход блока 6 предназначен для подачи на вход мультиплексора 74 сигнала переполнения результата с выхода 55 операционного блока 4 (фиг. 3).

5 Третий информационный вход 80 блока 6 предназначен для подачи сигнала знака результата в предыдущем цикле с выхода блока 7 на вход сумматора 76 по модулю два.

0 Вход знака блока 6 предназначен для подачи сигнала знака в текущем цикле с выхода 56 операционного блока 4.

Вход 79 блока 6 предназначен для подачи сигнала знака делимого или множимого с выхода блока 7 на вход сумматора 75.

Вход 81 блока 6 предназначен для подачи сигнала переполнения соответствующего счетчика 28.п циклов в блоке 3 (фиг. 2), управляющего выполнением требуемого числа раз повторяющихся циклов при выполнении команды деления.

При выполнении других «длинных команд (умножение, сдвиги) значение входа 81 блока 6 безразлично для работы устройства.

Мультиплексор 74 блока 6 предназначен

5

0

для формирования сигнала переполнения

Z1,Z2, Z3, Z4

где A 1A 2, 2, A IA 2, - значения кодов микроопераций, поступающихна вход 85 блока б;

- значения сигналов, поступающих на входы мультиплексора 74 с выхода 55 блока 4, выхода сумматора 76, выхода сумматора 75 и щи- ны нулевого потенциала соответственно.

Элемент И-НЕ 77 блока 6 предназначен для формирования на выходе 82 сигнала состояния для младщего разряда регистра 192 секции 47 блока 4 (фиг. 3).

Блок 7 хранения состояний (фиг. 6) предназначен для хранения значения знака результата в предыдущем такте выполнения операции, инверсного значения младщего разряда регистра 192 секции 47 блока 4 (фиг. 3) и знака результата, запомненного в требуемый момент времени.

На вход знака блока 7 поступает значение знакового разряда с выхода 56 операционного блока 4.

На первый информационный вход блока 7 поступает значение младщего разряда результата из секции 47 блока 4 для запоминания верхмладщего разряда результата при выполнении команды умножения и используемого при округлении результата.

На вход 93 блока 7 поступает сигнал микрооперации разрещения запоминания условий с выхода блока 8 микропрограммно- го управления.

На синхровход блока 7 поступают тактовые импульсы с второго выхода блока 10 синхронизации.

Триггер 87 предназначен для запоминания значения знака результата с выхода 56 операционного блока 4.

Третий информационный выход блока 7 предназначен для выдачи сигнала знака результата в предыдущем цикле.

Выход 97 блока 7 предназначен для выдачи инверсного значения младщего разряда результата секции 47 блока 4.

Первый информационный выход блока 7 предназначен для выдачи значения знака результата, например множимого или сдвигаемого влево числа.

Блок 8 микропрограммного управления (фиг. 7) предназначен для управления работой процессора.

5

0

п

0

5

5

5

0

ПЗУ 100 служит для хранения микропрограмм.

Считывание информации из ПЗУ 100 осуществляется по адресу, записанному в регистр 101 адреса. Операционная часть микрокоманды по заданному заднему фронту импульса Т2, поступающего на второй синхровход, заносится в регистр 102 микроопераций, а адресная часть поступает на коммутатор 104 (немодифицируемые разряды) и мультиплексор 103 (модифицируемый разряд). Мультиплексор 103 осуществляет модификацию адресного разряда кодом значений логических условий, поступающих на входы нуля, знака (из операцион- ното блока 4) и логических условий (сигналов переполнения счетчиков 28.1-28.«) и реализует следующую логическую функцию

Y Xo-a+X ZiH + + X Xl+Xn+ Xn,

где Л о, А |, ..., Л „+з - коды логических условий, поступающие из регистра 102;

а - значение модифицируемого разряда адреса; ZjH - значение знакового разряда, поступающего с выхода 56 блока 4; Zo-значение сигнала на выходе 54 нуля результата блока 4.

При А о I (нулевом коде логических условий) адресный разряд на выход мультиплексора 103 проходит без изменения.

При и А , 1 (при выполнении микрокоманды ветвления) на выход мультиплексора поступает один из сигналов Z.m (при ), Zo (при ) или А / (при ).

Коммутатор 104 управляет поступлением адресной информации в регистр 101. При выполнении микропрограмм сигнал на управляющем входе коммутатора 104 равен О и в регистр 101 записывается адрес следующей микрокоманды, считываемой из ПЗУ 100 и частично модифицируемой в точках ветвления мультиплексором 103. В последних микрокомандах микропрограмм имеется микрооперация «Конец команды, которая поступает на управляющий вход коммутатора 104 и разрещает прохождение кода очередной операции (начального адреса очередной микропрограммы). Адрес очередной микрокоманды заносится в регистр 101 по заднему фронту синхроимпульса Т|, поступающему на синхровход 137 блока 8.

Регистр 102 мнкроопераций предназначен для хранения операционных частей микрокоманд. На выходах 109.1 -115 формируются сигналы микроопераций, управляющих блоком 3. Дещифратор 106 служит для формирования сигналов управления записью и счетом счетчика 26, поступающего с выходов 109.1 и 109.2 на входы 37 (фиг. 2).

Дешифратор 105 предназначен для формирования сигналов управления счетом и записью в счетчики 27, 28.1-28.и. Поскольку эти микрооперации несовместимы, то в каждом такте может формироваться сигнал только на одном из выходов дешифратора 105. Эти сигналы через группу выходов 110 блока 8 поступают через группу 38 входов блока 3 на входы 36 управления счетом и записью информации в счетчики 27, 28.1-28.П.

Элемент И 107 используется для выдачи сигнала записи в буферные регистры 24, 25. Сигнал с выхода 1 I 1 этого элемента по синхроимпульсу Т2 поступает в блок 3, где через вход 35 подается на синхровходы регистров 24, 25.

Микрооперации на выходах 112-115 регистра 102 управляют коммутаторами 29 и 30 блока 3. Сигналы с этих выходов поступают соответственно на входы 31-34 (фиг. 2) этих ко.ммутаторов и обеспечивают возможность динамической рокировки или блокировки информации, содержащейся в регистрах 24, 25 при выдаче ее на выход 40 и далее в операционный блок 4.

На выходах 116.1 -119 задаются коды операций КОП 1 КОП 3 и сигнал внешнего переноса для операционного блока 4 соответственно. Сигналы на этих выходах задают коды операции для микропроцессорных секций 44-47 операционного блока 4. Разряды /1 кода операции КОП 1 и /3 кода операции КОП 3, формируемые на выходах 1 16.1 и 118.1 соответственно, а также разряд внешнего переноса образуют вторую группу выходов выхода 139 кода операции блока 8, прохождение информации через которую может быть блокировано элементами И 183-185 (фиг. 13).

На выходах 120 и 121 формируется код управления мультиплексором 74 блока 6 анализа.

На выходах 122-126, образующих выход 141 блока 8, выдаются сигналы управления блоком 11 коммутации, которые поступают соответственно на входы 164-168 этого блока.

Сигналы с выходов 127, 128 регистра 102 поступают на вход 93 блока 7 и обеспечивают управление запоминанием условий (вход 91 элемента И 89) и признаков (вход 92 элемента И 90).

На выходах 129-132, образующих выход 143 блока 8, формируются сигналы управления блоком 9, которые поступают на входы 152-155 этого блока соответственно.

На выходе 133 регистра 102 формируется сигнал разрешения внещнего доступа, который поступает в коммутаторы 12-14 и на выход 21 процессора, а на выходе 134 регистра 102 выдается сигнал конца работы, который через выход блока 8 поступает в блок 10 синхронизации на элемент И 158 и останавливает работу процессора.

0

0

На выходах 135.1, 135.2 формируются сигналы управления соответственно обращением и записью в ОЗУ 2. Сигнал управления записью, формируемый элементом И 108, стробируется тактовым импульсом Т2, поступающим на второй синхровход блока 8. Кроме того, сигнал с выхода 136 регистра 102 поступает в коммутатор 13 данных для управления записью и чтением информации из ОЗУ 2.

Блок 9 управления сдвигами (фиг. 8) предназначен для осуществления сдвига информации во вспомогательном регистре 192 и блоке 189 регистров общего назначения секций 44-47 блока 4 (фиг. 3, 14).

На первый информационный вход блока 9 с выхода 82 блока 6 (фиг. 5) поступает сигнал для формирования состояния младшего разряда вспомогательного регистра 192 секции 47 блока 4, являющегося очередной цифрой частного при выполнении команды деления.

На вход знака блока 9 поступает сигнал знака результата с выхода 56 блока 4 (фиг. З) для распространения знака числа, например при выполнении команд сдвига чисел вправо.

На второй информационный вход блока 9 поступает запомненный знак результата с первого информационного выхода блока 7 (фиг. 6), например знак множимого при выполнении команд умножения.

На группу управляющих входов блока 9 (фиг. 8) поступает код управления мультиплексором 146 (по входам 154 и 155), коммутатором 145 (по входу 153) и магистральными элементами 147-150 (по входу 152) через элемент НЕ 151 или непосредственно.

Мультиплексор 146 предназначен для r формирования сигнала состояния старшего разряда регистров блока 189 секции 44 в блоке 4 (фиг. 3).

Работа мультиплексора 146 описывается логической функцией Y, вычисляемой по формул е

K A 1A 2ZJ-|-A 1X2Z2 + A 1A 2Z3 + A 1A 2Z4, где А 1А2, А 1А2, А1А 2, А1А:2 - коды управляющих мик5

0

0

5

Z1,Z2, Z3, Z4

5

0

роопераций; - сигналы с шины нулевого потенциала, состояния младшего разряда результата (выход 201 мультиплексора 193) секции 47 блока А (фиг. 3, 14), выхода 56 блока 4, первого информационного выхода блока7

(4)иг. 6) соответственно.

Коммутатор 145 предназначен для формирования сигнала состояния младшего разряда результата в блоке 189 секции 47 блока 4 (фиг. 3) на основании значения старшего разряда результата с выхода 204 в блоке 190 секции 44 блока 4 (фиг. 3) при циклически.х сдвигах влево или нулевой с шины нулевого потенциала при сдвигах кодов и чисел влево.

Управление ко.ммутатором осуществляется сигналом микрооперации с входа 153,

Магистральные элементы 147--150 блока 9 предназначены для организации обмена информацией между входами-выходами блока 9 и входами-выходами операционного блока 4 и обеспечивают возможность по одним и тем же цепям производить сдвиги информации как вправо, так и влево.

Блок 10 синхронизации (фиг. 9) предназначен для синхронизации работы всех узлов и блоков процессора обработки массивов данных. Триггер 157 служит для управления работой блока 10 синхронизации. В исходном состоянии процессора триггер 157 находится в нулевом состоянии. Нулевой сигнал на его единичном выходе поступает на вход управления генератора 156.

Генератор 156 формирует на своих выходах две последовательности сдвинутых друг относительно друга импульсов TI и Т2 только при наличии единичного сигнала на его управляющем входе.

Элемент И 158 служит для формирования сигнала на / -вход триггера 157 после поступления управляющего сигнала «Конец работы с блока 8 микропрограммного управления.

Подаваемый на вход 20 процессора сигнал «Пуск поступает на У -вход триггера 157 и устанавливает его в единичное состояние.

Единичным сигналом на своем выходе триггер 157 запускает генератор 156, который начинает формирование последовательностей управляющ,их сигналов TI и Т2.

Формирование синхросигналов продолжается до тех пор, пока на первый вход элемента И 158 не поступит управляющий сигнал «Конец работы. После этого при поступлении на второй вход элемента И 158 очередного тактового импульса Т2 последний сформирует управляющий сигнал на R-BKOH триггера 157, который вернется в исходное состояние и снимет управляющий сигнал с входа генератора 156. В результате генератор 156 прекратит выдачу синхропоследо- вательностей TI и Т2Блок 1 I коммутации (фиг. 10) предназначен для формирования блоком 5 сигналов блокировки разрядов /1 в поле /2, /1, /0) и /3 в поле {/5, /4, /3) кода операции, поступающего на вход 51 блока 4 (фиг. 1, 3. табл 1 --3)с выходов блока 15 элементов И.

0

5

0

5

0

5

0

5

0

5

Эти сигналы блокировки формируются соответственно на первом и втором информационных выходах блока 11, запоминаются в блоке 5 хранения условий и блокировки и выдаются в последующем цикле с его выхода 73.

Управление блоком 11 осуществляется по сигналам микроопераций, постуг1ающим на группу управляющих входов 164-168.

Микрооперация по входу 164 управляет коммутаторами 159 и 161. При наличии сигнала этой микрооперации сигнал на выходе коммутатора 159 равен значению младщего разряда вспомогательного регистра 192 секции 46 блока 4 (фиг. 3), а сигнал на выходе коммутатора 161 равен значению выходного сигнала третьего информационного выхода блока 7 (фиг. 6).

При нулевом значении микрооперации по входу 164 (фиг. 10) выходной сигнал коммутатора 159 равен значению младшего разряда вспомогательного регистра 192 секции 47 блока 4 (фиг. 10), а сигнал на выходе коммутатора 161 - инверсному значению младщего разряда вспомогательного регистра 192 секции 47 блока 4.

С первого информационного выхода блока 11, являющегося выходом элемента PI- HE 162, на вход 68 блока 5 (фиг. 4) при наличии микрооперации по входу 165 поступает сигнал разрешения блокировки разряда /1 поля 1/2, /I, /0) при умножении.

Сигнал на выходе коммутатора 160 предназначен для блокировки разряда /3 поля 1/5, /4, /3) при выполнении команд деления и умножения.

Коммутатор 12 (фиг. 1) предназначен для коммутации адреса ОЗУ 2 в зависимости от значения сигнала на выходе разрешения внешнего доступа блока 8. При отсутствии этого сигнала значение адреса данных задается с выхода 43 блока 3 регистров-счетчиков, в противном случае - с адресного входа 19 процессора.

Коммутатор 13 данных (фиг. 11) предназначен для управления обменом между операционным блоком 4, ОЗУ 2 и внещней 17 данных.

Коммутатор 170 коммутатора 13 данных предназначен для управления потоками ипформации, поступающими на вход магистрального элемента 172.

Коммутатор 13 данных функционирует в четырех режимах: внутреннего чтения, внутренней записи, внешнего чтения, внешней записи.

В режиме внутреннего чтения сигналы на входах коммутатора 13 отсутствуют. При этом данные с шины 16 через открытые магистральные элементы 174 поступают на шину 18.

В режиме внутренней записи присутствует только сигнал микрооперации на втором управляющем входе коммутатора 13. При этом данные с 18 через коммутатор 170,

элементов

первую группу магистральных 172 поступают на шину 16.

В режиме внешнего чтения присутствует сигнал микрооперации только на третьем управляюшем входе коммутатора 13. При этом данные с шины 16 через магистральные элементы 173 поступают в шину 17.

В режиме внешней записи присутствуют сигналы только на третьем управляюшем входе коммутатора 13 данных. При этом данные с шины 17 через коммутатор 170, магистральные элементы 172 поступают на шину 16.

Коммутатор 14 управляюплих сигналов (фиг. 12) предназначен для формирования сигналов управления записью и обрашения

10

В счетчике 27 команд (фиг. 2) задан адрес первой (нулевой) команды программы обработки информации.

В исходном состоянии на выходе конца команды регистра 102 блока 8 (фиг. 7) присутствует сигнал, который разрешает прохождение на вход регистра 101 адреса микрокоманд блока 8 кода операции команды с выхода ПЗУ 1. Кроме того, сигнал присутствует и на выходе 111 управления записью в регистры 24, 25 (фиг. 7). Сигналы остальных микроопераций на выходах регистра 102 отсутствуют, что соответствует холостому циклу работы процессора.

По сигналу пуска с входа 20 (фиг. 1) триггер 157 (фиг. 10) устанавливается в едиписью. Коммутатор 178 предназначен для формирования сигнала управления чтением.

для ОЗУ 2. Коммутатор 177 предназначен 15 ничное состояние и включает генератор 156, для формирования сигнала управления за-формирующий тактовую сетку синхронизации работы процессора.

По первому тактовому импульсу генератора 156 считывается команда с выхода 2Q ПЗУ 1, код операции которой через коммутатор 104 (фиг. 7) записывается в регистр 101 и определяет адрес первой микрокоманды в ПЗУ 100.

Первая микрокоманда холостого цикла предназначена для определения типа первой 25 команды и начального адреса микропрограммы ее выполнения, а также записи в регистры 24, 25 содержимого командного слова по сигналу микрооперации с выхода 111 блока 8 (фиг. 7), являюшегося входом 35 блока 3 (фиг. 2).

Далее последовательность выполнения считанной команды зависит от типа ее формата.

Для команд формата RR сигналом с входа 35 (фиг. 2) производится запись адресов операндов и в регистры 24 и 25. По сигналам на входах 31 и 33 блока 3 содержимое регистров 24, 25 с выхода 40 блока 3 передается на первый информационный вход блока 4 (фиг. 3) и далее на входы блоков 189 регистров общего назначения секций 44-47 40 блока 4 (фиг. 14), задавая адреса регистров в них.

Коммутатор 14 работает следуюшим образом.

Коммутатор 177 формирует сигнал управления записью в двух ситуациях: если на его первом информационном входе присутствует единичный сигнал внешней записи и на управляюш,их входах - сигнал разрешения внешнего доступа или на его втором информационном входе присутствует сигнал внутренней записи и на управляющих входах отсутствует сигнал разрешения внешнего доступа.

Коммутатор 178 формирует сигнал обрашения в следующих случаях: если на его первом информационном входе присутствует единичный сигнал внешнего обращения и на управляюших входах - сигнал разрешения внешнего доступа или на его втором информационном входе присутствует сигнал внутреннего обращения и на управляющих входах отсутствует сигнал разрешения вне1ине- го доступа.

Блок 15 элементов И (фиг. 13) предназначен для блокировки разрядов /1 и /3 полей {/2, /1, /0) и (/5, 14, /3| кодов операций операционного блока 4, а также сигнала входного переноса. При этом блокировка разряда /I осуществляется сигналом микрооперации с выхода 65 регистра 62 блока 5

30

35

Первая микрокоманда микропрограммы на выходе 139 блока 8 (фиг. 1, 7) задает код операции для блока 4, который поступает

(фиг. 4), а блокировка разряда /3 и сигнала 45 д вход 51 (фиг. 3).

входного переноса - сигналом микрооперации с выхода 66 регистра 62 блока 5. Процессор функционирует в следующих режимах:

1)обработка информации и выполнение вычислений;

2)обмен с внешними устройствами. Режим обработки информации и выполнения вычислений.

В исходном состоянии все элементы памяти установлены в нуль. Поэтому триггер 157 блока 10 (фиг. 9) блокирует генератор 156, на выходах которого отсутствуют тактовые импульсы.

0

В счетчике 27 команд (фиг. 2) задан адрес первой (нулевой) команды программы обработки информации.

В исходном состоянии на выходе конца команды регистра 102 блока 8 (фиг. 7) присутствует сигнал, который разрешает прохождение на вход регистра 101 адреса микрокоманд блока 8 кода операции команды с выхода ПЗУ 1. Кроме того, сигнал присутствует и на выходе 111 управления записью в регистры 24, 25 (фиг. 7). Сигналы остальных микроопераций на выходах регистра 102 отсутствуют, что соответствует холостому циклу работы процессора.

По сигналу пуска с входа 20 (фиг. 1) триггер 157 (фиг. 10) устанавливается в еди5 ничное состояние и включает генератор 156, формирующий тактовую сетку синхронизаПервая микрокоманда микропрограммы на выходе 139 блока 8 (фиг. 1, 7) задает код операции для блока 4, который поступает

д вход 51 (фиг. 3).

0

5

При реализации циклических команд в счетчики 28.1-28.« блока 3 (фиг. 2) может заноситься информация о кратности реализуемых циклов. Считывание этой информации происходит по адресу, заданному в счетчике 27, из ПЗУ 1. По соответствующей микрооперации на соответствующем входе 36 блока 3 (фиг. 2) осуществляется занесение этой информации в заданный счетчик 28.П.

Наращивание значения счетчика 27 команд в блоке 3 осуществляется путем подачи сигналов микроопераций на его счетный вход с соответствующего входа 36 блока 3.

При реализации команд / А-формата аналогично описанному осуществляется запись кода операции и адреса в регистр 24 блока 3 (фиг. 2). Регистр 25 в этом случае не используется. Значение смещения, задаваемого в формате команды, записывается по микрооперации с соответствующего входа 37 блока 3 в счетчик 26 адреса.

На вход операционного блока 4 (фиг. 3) передается только содержимое R, хранящееся в регистре 24 (фиг. 2).

Содержимое R2 из регистра 25 в блок 4 (фиг. 3) не передается ввиду отсутствия сигнала микрооперации на входах 32, 34 блока 3 (фиг. 2).

Исполнительный адрес второго операнда задается для / А-команд в счетчик 26 блока 3 (фиг. 2). Этот адрес с выхода 43 блока 3 поступает на вход коммутатора 12, который при отсутствии микрооперации на выходе 133 разрешения внещнего доступа блока 8 (фиг. 7) передает его на адресный вход ОЗУ 2. По этому адресу в следующей микрокоманде можно осуществлять обмен данными с ОЗУ 2.

По окончании формирования исполнительных адресов операционный блок 4 может начать выполнение операций. При этом если для выполнения операции необходимо считывание из ОЗУ 2, данные с входа-выхода ОЗУ 2 по соответствующему управляющему сигналу коммутатора 14 через шину 16, коммутатор 13 и щину 18 передаются на информационный вход-выход операционного блока 4. После этого операционный блок 4 выполняет соответствующую операцию.

Если выполняемая операция предусматривает запись данных в ОЗУ 2, то в этом случае счетчик 26 блока 3 (фиг. 2) определяет адрес, по которому с входа-выхода блока 4 через Ц1ину 18, коммутатор 13, шину 16 и вход-выход ОЗУ 2 производится передача данных в ОЗУ 2.

Обмен данными между ОЗУ 2 и блоком 4 (фиг. 1) осуществляется под управлением выходных сигналов коммутатора 14 (фиг. 12) работающего по микрооперациям разрешения внешнего доступа с выхода 133 блока 8 (фиг. 7), разрешения обращения (записи, чтения) с выходов 135.1-135.2, 144 блока 8.

В режиме внешнего обмена работа процессора осуществляется следующим образом.

Характерной особенностью некоторых операций является возможность обработки данных блоком 4 без обращения к ОЗУ 2.

В начале такого режима работы на выходе 133 блока 8 (фиг. 7) формируется сигнал разрешения внешнего доступа к ОЗУ 2. Этот сигнал поступает на вход коммутатора 12, разрешая прием адреса данных с входа 19 процессора (фиг. 1) на вход коммутатора 14 (фиг. 12), разрещая выдачу сигналов 3anHcVi и чтения на ОЗУ 2 в этом режиме с входов 19 процессора, а также на внешний выход 21 и третий управляющий вход ком5

мутатора 13. Сигнал с выхода 21 поступает, например, в процессор высщего уровня управления, извещая его о возможности доступа к ОЗУ 2.

По этим сигналам коммутатор 12 про- пускает адрес данных с входа 19, коммутатор 14 выдает сигнал записи и чтения на управляющие входы ОЗУ 2 с входа 19, а коммутатор 13 формирует тракт связи шин 16 и 17.

0По окончании режима внешнего доступа

сигнал разрешения внещнего доступа с выхода блока 8 снимается и процессор продолжает работу аналогично описанному выше.

Рассмотрим особенности выполнения предлагаемым процессором тех операций, выполнение которых отличается от стандартных последовательностей, предусмотренных, например, в процессоре типа 1804ВС1 (см. таблицы микрокоманд для блока 4). 0 Выполнение сдвига чисел выполняется следующим образом.

Например, сд виг чисел влево выполняется за три условных цикла, т. е. в ПЗУ 100 микрокоманд представлены три ячейки микроопераций.

5 В первом цикле осуществляется запись дополнения числа сдвигов в заданный счетчик 28.гг блока 3 (фиг. 2) с выхода ПЗУ 1 по адресу, заданному в счетчике 27 блока 3.

Сдвигаемое число хранится в блоке 189 регистров общего назначения блока 4 (фиг. 3 14). В триггере 87 блока 7 (фиг. 6) осуществляется запоминание знака сдвигаемого числа. Этот сигнал поступает с выхода 56 блока 4 (фиг. 3) на D-вход триггера 87 (фиг. 6) и записывается в него при наличии второго тактового импульса и разрешающей микрооперации с выхода 128 блока 8 (фиг. 7) на вход 92 блока 7 (фиг. 6).

Далее по коду операции (/8, 17, 16, /5, /4, /3, 12, /1, /0), равному 111 011 О 11, поступающему с выхода 139 блока 8 (фиг. 7) на вход 51 блока 4 (фиг. 3), выполняется сдвиг числа на один разряд влево. Эта операция осуществляется для обеспечения возможности анализа переполнения путем сравнения значений знака, запомненного в триггере 87 (фиг. 6), и знакового разряда блока 4 (выход 56 блока 4), который определяется старшей значащей цифрой мантиссы, с последующей записью у нуля на место млад- inero разряда результата.

На втором цикле выполнения сдвига чисел, выполняемом многократно Л раз, где К - число разрядов, на которое происходит сдвиг, последовательно выполняются следующие действия.

Соответствующий счетчик 28.л циклов блока 3 (фиг. 2) по соответствующему сиг- 5 налу микрооперации с входа 36 увеличивает свое значение на единицу. Выходной сигнал переполнения этого счетчика поступает на вход мультиплексора 103 (фиг. 7), где про0

5

0

5

0

исходит проверка его переполнения. Если счетчик переполнен, то осуществляется переход к выполнению третьего цикла операции сдвига. Кроме того, выполияются действия, аналогичные описанным ниже, когда счетчик 28.п не переполнен.

Если же счетчик 28.л (фиг. 2) не переполнен, то с выхода 139 блока 8 (фиг. 7) на вход 51 блока 4 (фиг. 3) выдается код операции 111011011, по которому осуществляется сдвиг числа в блоке 4 на один разряд влево с записью нуля на место младщего разряда результата.

Запись нуля выполняется при отсутствии сигналов на входах 153 (фиг. 8) и 152. Поэтому с выхода элемента 149 на вход 59 младщего разряда регистра блока 189, адресуемого полем R, блока 4 подается нулевой сигнал, который записывается в млад- Н1ИЙ разряд.

Далее вырабатывается микрооперация на вход 85 блока 6 (фиг. 5) для пропуска через мультиплексор 74 сигнала переполнения, вырабатываемого сумматором 75 сравнением истинного знака числа и «знака промежуточного числа, т. е. старшим разрядом очередного значения мантиссы с выхода 56 блока 4. С выхода 84 блока 6 этот сигнал поступает на вход четвертого разряда регистра 62 блока 5 (фиг. 4) и по синхросигналу запоминается в регистре 62.

Сигнал с выхода четвертого разряда регистра 62 через элемент И 64 в каждом из К-1 повторений второго цикла операции сдвига чисел может быть выдан на выход 22 переполнения результата процессора и восприниматься процессором высшего уровня управления как сигнал прерывания.

Циклическое повторение второго цикла операции сдвига чисел прекращается но переполнении соответствующего счетчика 28.п циклов блока 3 (фиг. 2), после чего процессор переходит к реализации третьего цикла выполнения операции. При этом блоком 8 (фиг. 7) с выхода 139 в блок 4 (фиг. 3) выдается код операции 101011011, по которому выполняется сдвиг вправо на один разряд для того, чтобы компенсировать лищ- ний сдвиг влево, который был сделан в нервом цикле для обеспечения возможности анализа переполнения блока 4 путем сравнения знака, хранящегося в триггере 87 (фиг. 6), и старщей значащей цифры мантиссы.

При выполнении данной операции в знаковый разряд результата записывается содержимое триггера 87 с первого информационного выхода блока 7 (фиг. 6) через мультиплексор 146 (фиг. 8) блока 9, элемент 150 на вход 57 блока 4. Управление передачей этой информации осуществляется по микрооперациям с входов 152, 154 и 155 (фиг. 8). Выполнение описанных действий позволяет получить требуемое число с компенсацией лишнего сдвига на один разряд влево.

Кроме того, в третьем цикле по синхросигналу с синхровхода 53 (фиг. 4) при на- личии сигнала переполнения, запомненного в предыдущем цикле в регистре 62 блока 5, происходит его выдача через элемент И 64 на выход 22 процессора.

Выполнение операции умножения в данном процессоре также имеет существенные отличия от последовательности, используемой в микропроцессорах, например, типа 1804ВС1.

Выполнение операции умножения в предлагаемом процессоре условно подразделяет- ся на шесть циклов.

Умножение может выполняться с 16- или 32-разрядными числами. Поэтому в соответствующий счетчик 28.я циклов (фиг. 2) аналогично описанному выще заносится код дополнения до числа повторений однотип- 0 ного цикла. В формате RR множитель при выполнении умножения задается в регистре блока 189, определяемом полем R2 (содержимое регистра 25 на фиг. 2), а множимое - , т. е. регистром 24 блока 3.

Далее блоком 8 (фиг. 7) выдается код операции 000 011 100, по которой осуществляется пересылка множителя из блока 189 регистров (фиг. 14) в регистр 192.

В качестве рабочего регистра используется нулевой регистр блока 189.

Во втором цикле выполнения операции умножения вырабатываются микрооперации управления блоком 11 коммутации (фиг. 10), поступающие на его гругщу управляющих входов с выхода 41 блока 8 (фиг. 7).

Далее вырабатываются микрооперации c динамической рокировки полей команды (по входу 33 блока 3). При этом на место R2 подставляется значение регистра 24, а вместо R передается нулевое значение, т. е. задается нулевой регистр в блоке 189 (фиг. 14).

0На вход 51 блока 4 (фиг. 3) поступает

код операции 100011100, по которой осуществляется сдвиг вправо содержимого регистра 192 и нулевого регистра блока 189 (фиг. 14) и запоминание содержимого млад- с шего разряда регистра 192 в регистре 62 (фиг. 4) с входа 67.

Состояние нулевого регистра блока 189 регистров (фиг. 14) до и после сдвига безразлично, поэтому в него производится запись множимого со сдвигом на один раз- 0 ряд вправо. При этом знаковый разряд посылается в знаковый разряд.

В течение второго, третьего и условного четвертого циклов выполнения умножения по входу 164 блока 11 (фиг. 10) подается единичный сигнал при умножении на 16 раз- 5 рядов (на фиг. 3 представлены секции 44 - 47, условно принятые восьмиразрядными) и нулевой сигнал при умножении на 32 разряда, при этом в первом случае анализи0

руется младший разряд множителя с выхода секции 46 (выход 61 блока 4), а в другом - с выхода секции 47 (выход 60 блока 4).

Знак множимого, поступающий на вход знака результата блока 7 (фиг. 6), запоминается в триггере 87 (фиг. 5) по сигналу микрооперации на входе 92 блока 7 (фиг. 6). Далее рассматривается случай умножения на 16 разрядов, что соответствует анализу младшего разряда секции 46, т. е. 23-го разряда.

Вырабатывается микрооперация по входу 166 блока II (фиг. 10) и входу 164. При единичном значении 23-го разряда регистра 192 (фиг. 14), выходной сигнал которого поступает на первый информационный вход блока 11 (фиг. 10) с выхода 61 блока 4, коммутатор 160 срабатывает и сигнал с второго информационного выхода (фиг. 10) записывается в третий разряд регистра 62 (фиг. 4) для блокировки разряда /3 кода операции в следующем такте.

В третьем цикле аналогично вырабатываются коммутирующие микрооперации для коммутаторов 29 и 30 блока 3 (фиг. 2).

Затем блок 8 (фиг. 7) выдает код операции 100101100, по которому производится запись множимого со сдвигом на один разряд вправо. При этом значение знака множимого из триггера 87 (фиг. 6) записывается на место знакового разряда нулевого регистра блока 189 (фиг. 14), выполняющего роль рабочего регистра. Запись знака множимого происходит с первого информационного выхода блока 7 (фиг. 6) через мультиплексор 146, элемент 149 на вход 57 блока 4 (фиг. 3) под управлением микроопераций по входам 154, 155 и 153 в блоке 9 (фиг. 8).

Если значение младшего разряда множителя было равно О, то, следовательно, по сигналу с входа 69 (фиг. 4) соответствующий разряд регистра 62 был установлен в единицу. Поэтому в данном цикле сигналом с выхода 66 регистра 62 (фиг. 4) через выход 73 блока 5 (фиг. 4) осуществляется блокировка разряда /3 кода операции и, следовательно, производится запись нулей в нулевой регистр блока 189 (фиг. 14), выполняющий роль рабочего регистра.

По сигналу микрооперации на входе 36 (фиг. 2) значение соответствующего счетчика 28.п циклов увеличивается на единицу.

Вырабатывается микрооперация по входу 165 (фиг. 10), которая разрешает в следующем цикле блокировку разряда /1 кода операции при единичном значении выдвигаемого на выход 60 (фиг. 3) разряда числа. Если блокировка разрешена, то в регистр 62 (фиг. 4) по входу 68 записывается единица.

В четвертом цикле выполнения умножения, который выполняется k-2 раза, аналогично описанному выше, вырабатываются коммутирующие микрооперации для блока 3 (k - разрядность множителя).

Значение заданного счетчика 28.п циклов (фиг. 2) увеличивается на единицу по микрооперации на входе 36 в блоке 3, и блоком 8 (фиг. 7) осуществляется проверка счетчика 28.п на переполнение. Если счет- чик 28.п переполнен, то процессор по окончании данного цикла 1ереходит к гттому циклу выполнения операции умпожения, в противном случае продолжается выполнение операции четвертого цикла, в котором 0 на вход операционного блока 4 (фиг. 3) поступает код операции 100000011, если разряд /1 не блокируется, или код 100000001, когда на выходе 65 регистра 62 (фиг. 4) присутствует единичный сигнал.

По коду операции 100000011 в блоке 4 5 к частичному произведению прибавляется множимое (см. таблицы операций блока 4), результат сдвигается на один разряд вправо с записью знака множимого с выхода триггера 87 (фиг. 6) в знаковый разряд резуль- Q тата по цепи: 1ервый информационный выход блока 7 (фиг. 6), второй информационный вход блока 9 (фиг. 8), мультиплексор 146, магистральный элемент 150, выход блока 9, вход 57 блока 4 (фиг. 3). Управление передачей осуществляют микроопера 1.ии 5 по входам 152, 154, 155 (фиг. 8).

По коду операции 100000001 выполняются аналогичные действия, но к частичному произведению прибавляется нуль, а не множимое.

Далее значение выдвигаемого сверх- 0 младшего тридцать второго разряда результата инвертируется на элемент НЕ 88 и записывается во второй разряд регистра 86 (фиг. 6) с входа 96 (выход 59 блока 4).

Аналогично описанному в третьем цикле может вырабатываться сигнал блокировки 5 разряда /1 кода операции, после чего операции четвертого цикла повторяются снова.

В пятом цикле осуществляется коррекция результата при отрицательном множителе, при этом может быть выработан сигнал 0 переполнения результата, который с выхода 55 блока 4 через мультиплексор 74 запоминается в четвертом разряде регистра 62 для выдачи его в следующем цикле через элемент И 64 на выход 22 процессора.

Аналогично описанно.му вып1е выпол- 5 няется коммутация регистров 24, 25 в блоке 3 (фиг. 2).

На вход 51 кода операции блока 4 (фиг. 3) поступает код операции 010001011, если в последнем повторении четвертого цикла не была разрешена блокнровка раз- ряда /1, и 010001001, если блокировка была разрешена.

По микрооперациям на входе 85 блока 6

(фиг. 5) формируется цепь передачи сигнала

переполнения результата блока 4 (фиг. 3)

-г с выхода 55 через мультиплексор 74, вход 70

блока 5 в регистр 62 (фиг. 4).

В заключение пятого цикла осуществляется подготовка к округлению чис.:1а в njecтом цикле в зависимости от значения третьего разряда регистра 62 (выход 66). Для этого вырабатывается микрооперация по входу 168 блока 11 (фиг. 10).

В ujecTOM цикле выполняются ко.ммути- рующие операции в блоке 3 (фиг. 2), при которых содержимое регистра 24 передается в поле , а поле , после чего на вход 51 блока 4 (фиг. 3) с выхода блока 8 (фиг. 7) подается код операции 010000100 и подается входной перенос. По этому коду выполняется операция сложения результата выполнения операции умножения с единицей младшего разряда, если значение входного переноса не заблокировано (сверхмладший разряд результата равен единице). В противном случае результат пе изменяется.

Сигна.ч входного переноса блокируется аналогично микрооперации /3 при том же состоянии условий. Отличие состоит лишь в том, что сигнал на вход 69 блока 5 поступает по цепи: выход 97 блока 7 (фиг. 6), четвертый информационный вход блока 11 (фиг. 10), коммутатор 160, второй информационный выход блока 11, вход 69 блока 5 (фиг. 4).

Сигнал переполнения по очередному тактовому импульсу на синхровходе блока 5 (фиг. 4) может быть выдан через элемент И 64 на выходе 22 процессора и использоваться аналогично описанному выше.

На этом выполнение операции умножения заканчивается. С выхода конца команды регистра 102 (фиг. 7) выдается соответствующая микрооперация, по которой коммутатор 104 настраивается на пропуск кода операции команды, считываемой с выхода ПЗУ 1.

Выполнение деления в процессоре условно подразделяется на четыре цикла.

В первом цикле деления соответствующий счетчик 28.п циклов, аналогично опи санному выше, настраивается на нужное число циклов.

Блоком 8 выдается код операции 001110001 в операционный блок 4. При этом знаковый разряд результата, равный сумме по модулю два знаков операндов, с выхода 56 блока 4 поступает на соответствующий вход регистра 86 (фиг. 6) и запоминается в нем, так как вырабатывается микрооперация на входе 91 элемента И 89.

Во втором цикле осуществляется передача делителя на выход блока 190 (фиг. 14) для запоминания знака делителя в триггере 87 (фиг. 6). Знак делителя поступает в триггер 87 через вход знака результата блока 7 (фиг. 6). Кроме того, вырабатывается .микрооперация по входу 167 (фиг. 10) для разрешения блокировки разряда /3 кода операций в следующем цикле деления при единичном значении третьего информационного выхода блока 7 (фиг. 6), т. е. при не равенстве знаков делителя и делимого.

0

0

Третий цикл деления выполняется К. раз до переполнения счетчика 28.л блока 3 (фиг. 2).

Последовательность действий, выполняемых процессором, следующая.

Значение счетчика 28.п циклов увеличивается на единицу и проверяется на переполнение аналогично описанному выше. Далее получается очередная цифра частного, которая записывается в младший разряд регистра 192 со сдвигом влево. Инверсное значение этой цифры по входу 69 блока 5 (фиг. 4) записывается в соответствующий разряд регистра 62 для последующей блокировки разряда /3 кода операции. Очередная цифра частного равна единице при равенстве знаков делителя (выход D-триг- гера 87) и знака результата выполняемой операции (выход 56 блока 4). Для этого значение пербполнения счетчика 28.п на вход элемента И-НЕ 77 подается в инверсном виде, т. е. только при переполнении счетчика 28.л на первый вход элемента И-НЕ 77 поступит низкий потенциал, поэтому очередная Цифра частного равна инверсному значению сигнала на выходе сумматора 75 (фиг. 5) (К-1) раз выполнения третьего 5 цикла и всегда равна «1 при К-м выполнении третьего цикла.

Блокируется разряд /3 кода операции в третьем цикле. При выполнении первого раза третьего цикла условием блокировки является равенство единице суммы по модулю два сигналов знаков операндов, запомненное в регистре 86 и выдаваемое с третьего информационного выхода блока 7 (фиг. 6), т. е. при неравенстве знаков делителя и делимого.

При последующих повторениях третьего цикла (до /(-го) условием блокировки является нулевое состояние выхода 71 регистра 62 (фиг. 4).

Если разряд /3 не блокирован, то на вход 51 блока 4 поступает код операции 110001001, в противном случае - 110000001.

Если /3 не блокируется, то выполняется операция вычитания со сдвигом влево иа один разряд (см. таблицу кодов операций). При этом сигнал входного переноса равен единице.

В случае, когда разряд /3 блокируется, вместе с ним блокируется (устанавливается в нуль) и сигнал входного переноса. Поэтому в данном случае выполняется операция сложения со сдвигом на один разряд влево.