Изобретение относится к вычислительной технике и может быть использовано при проектировании устройства ввода-вывода, аппаратуры сопряжения, памяти таймеров и др.

Целью изобретения является повышение быстродействия устройства и расширение области его применения.

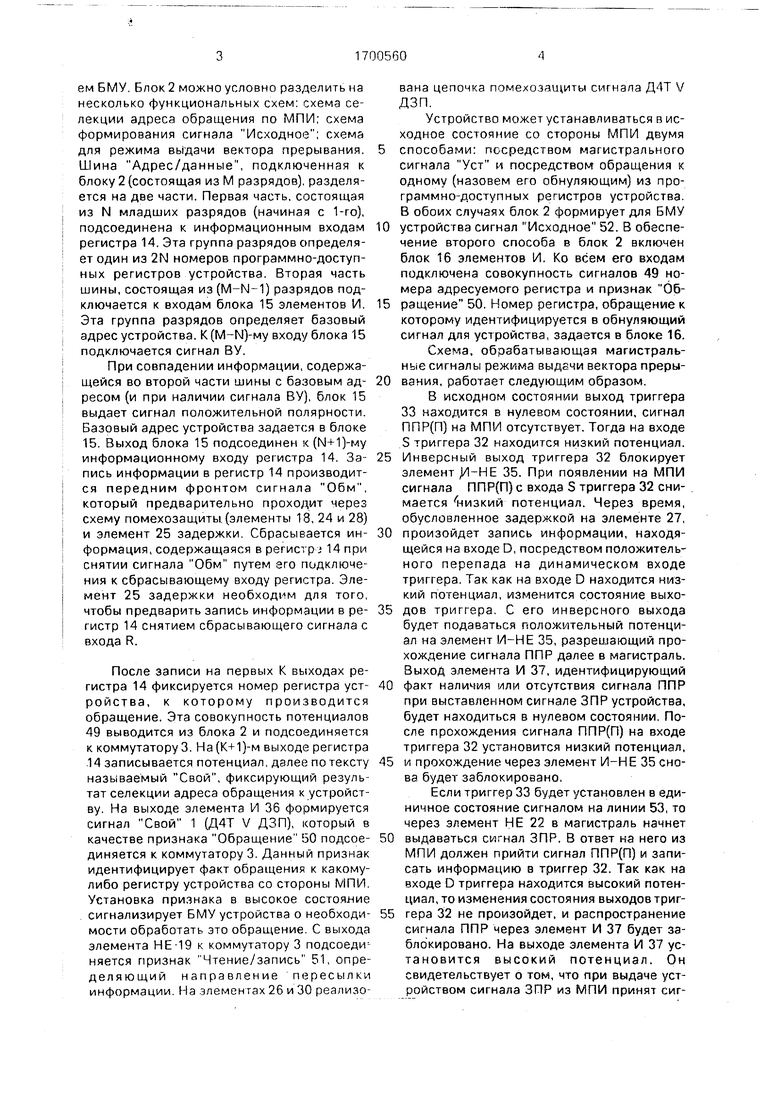

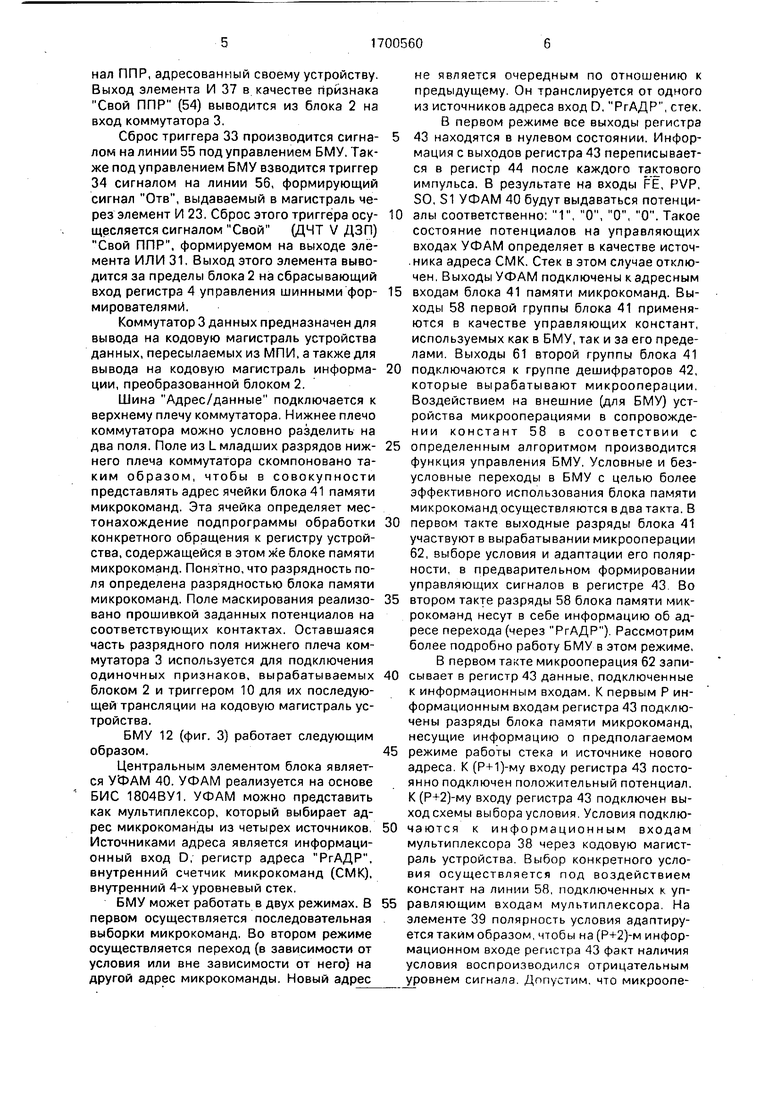

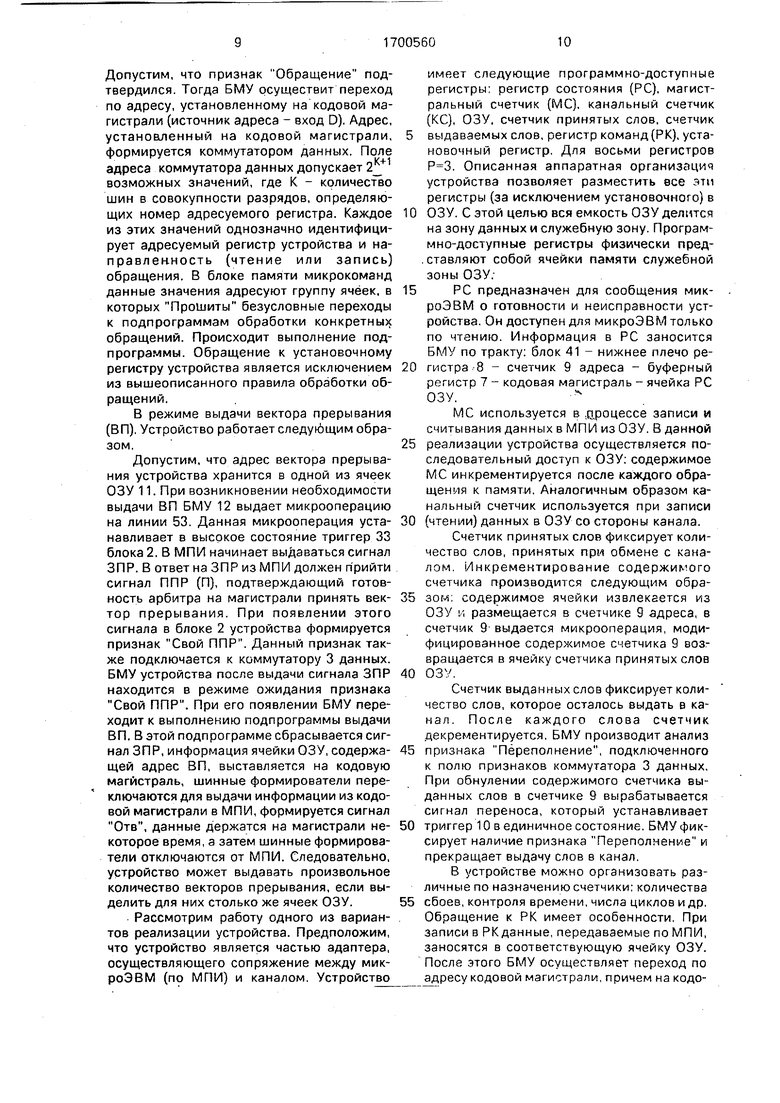

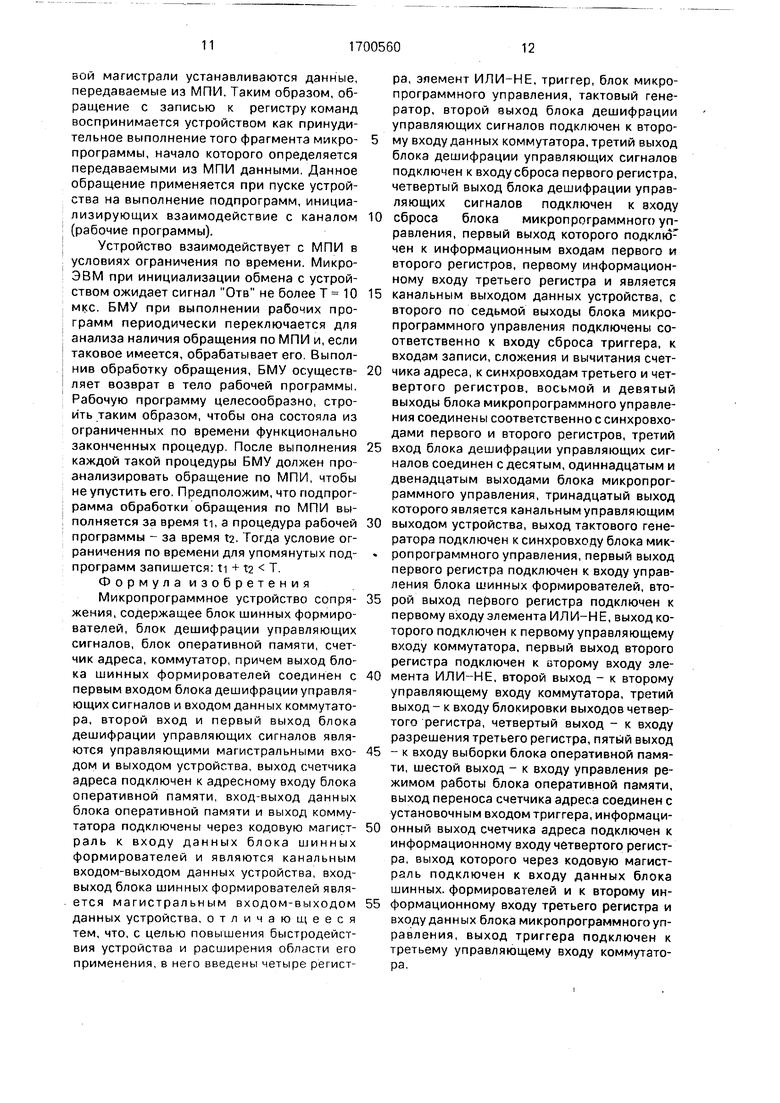

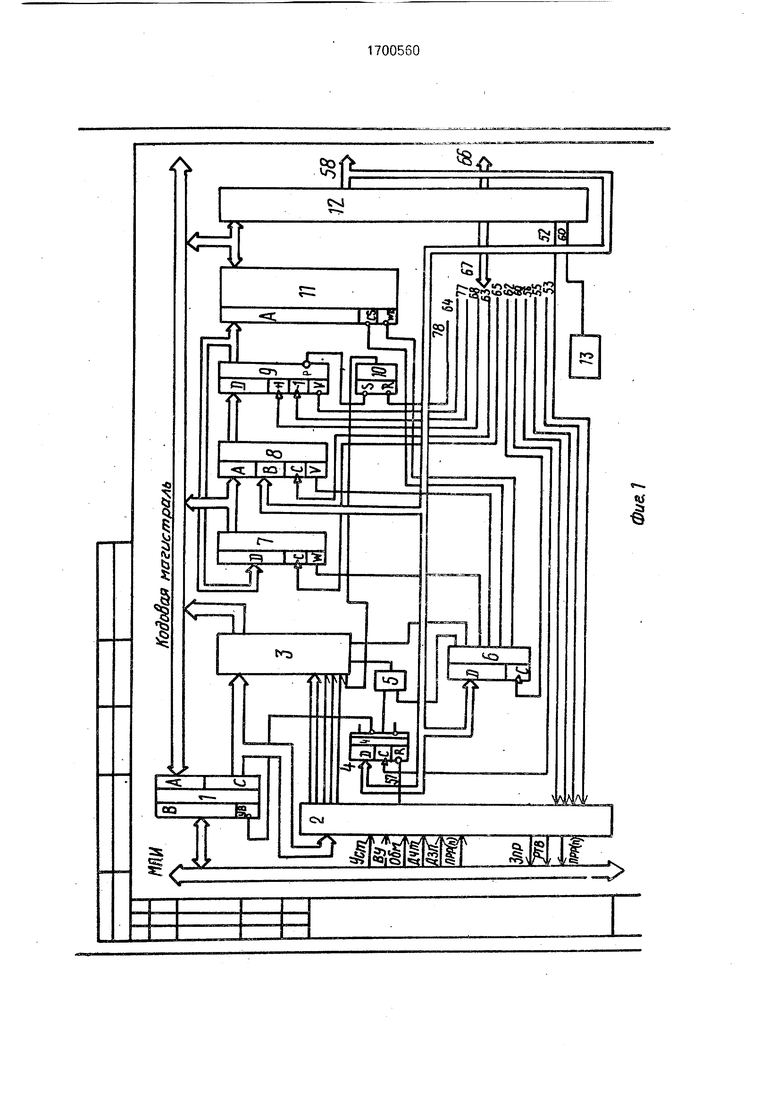

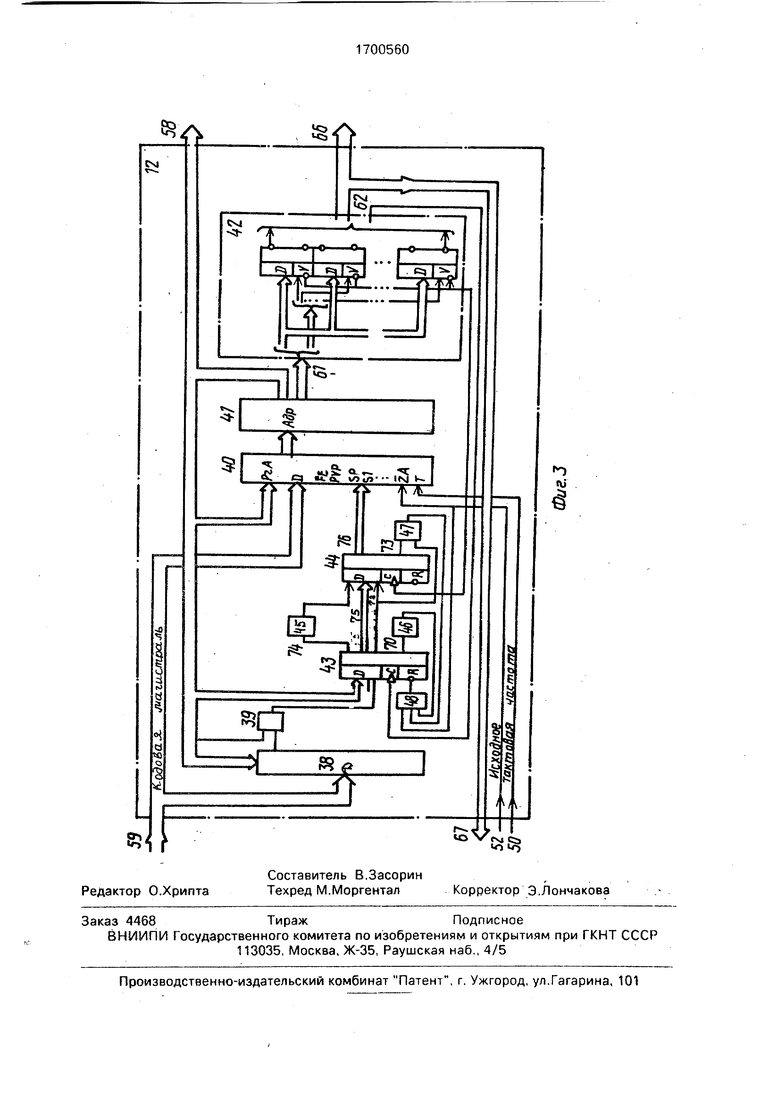

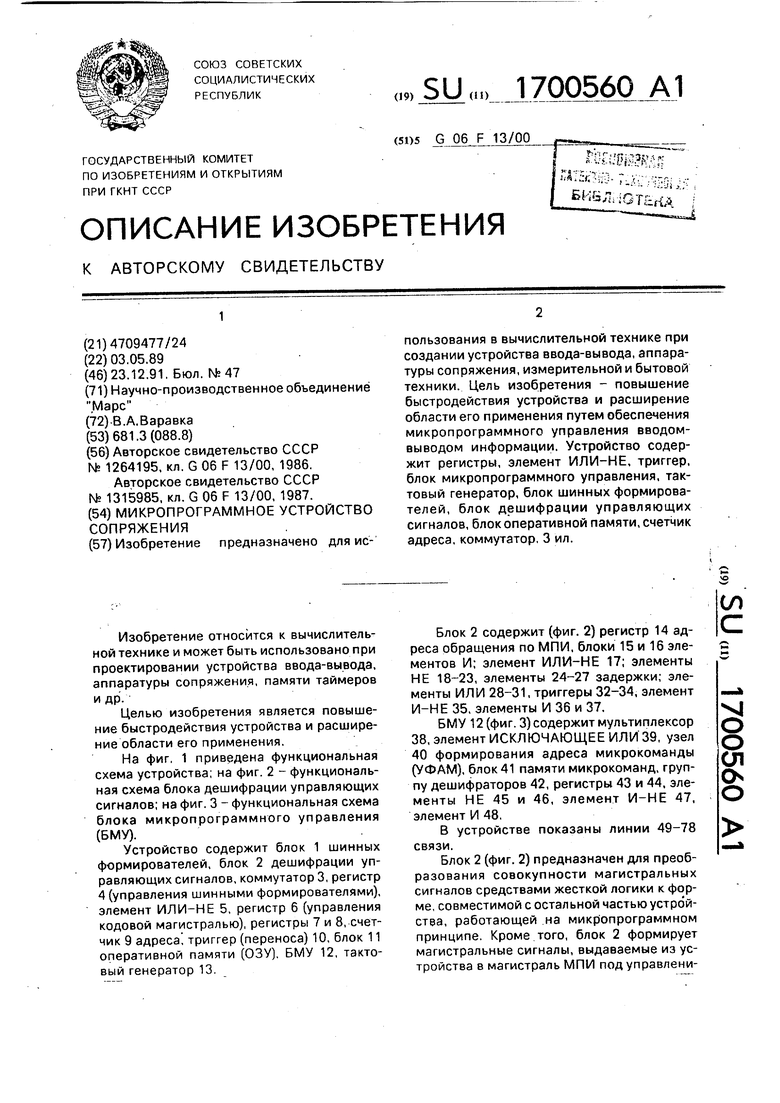

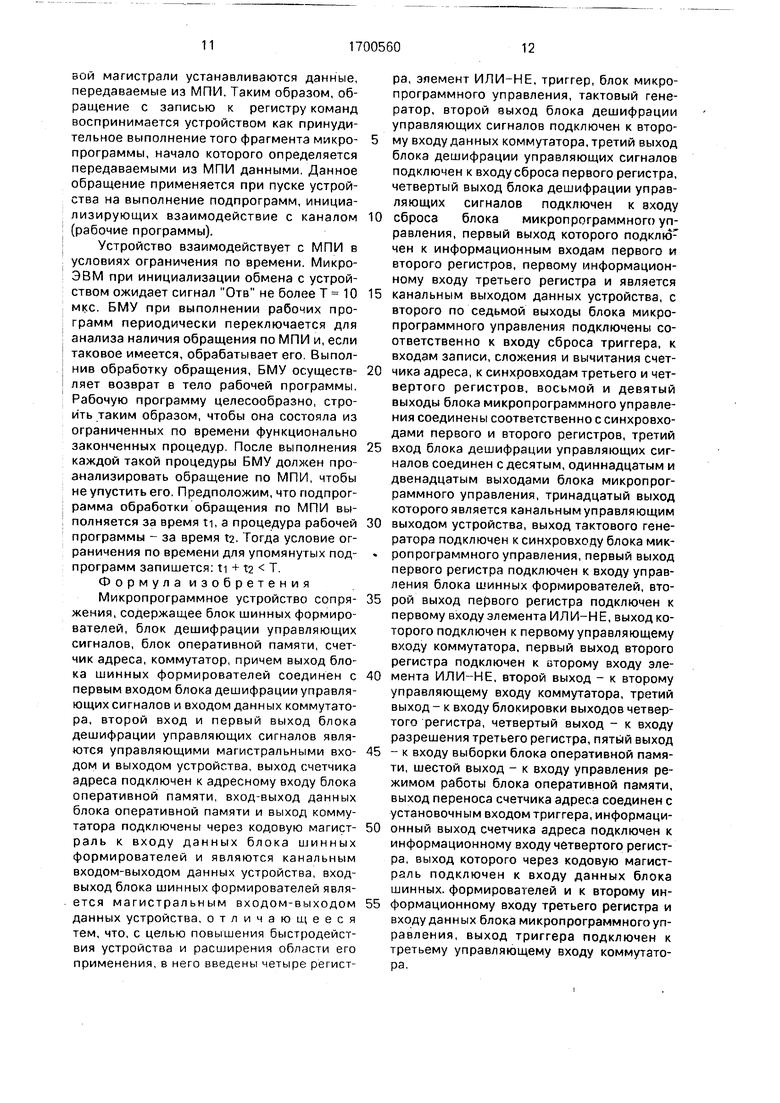

На фиг, 1 приведена функциональная схема устройства; на фиг. 2 - функциональная схема блока дешифрации управляющих сигналов; на фиг. 3 - функциональная схема блока микропрограммного управления (БМУ).

Устройство содержит блок 1 шинных формирователей, блок 2 дешифрации управляющих сигналов, коммутатор 3, регистр 4 (управления шинными формирователями), элемент ИЛИ-НЕ 5, регистр 6 (управления кодовой магистралью), регистры 7 и 8, счетчик 9 адреса , триггер (переноса) 10, блок 11 оперативной памяти (ОЗУ), БМУ 12, тактовый генератор 13.

Блок 2 содержит (фиг. 2) регистр 14 адреса обращения по МПИ, блоки 15 и 16 элементов И; элемент ИЛИ-НЕ 17; элементы НЕ 18-23, элементы 24-27 задержки; элементы ИЛИ 28-31, триггеры 32-34, элемент И-НЕ 35, элементы И 36 и 37.

БМУ 12 (фиг. 3) содержит мультиплексор 38, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 39. узел 40 формирования адреса микрокоманды (УФAM), блок 41 памяти микрокоманд, группу дешифраторов 42, регистры 43 и 44, элементы НЕ 45 и 46, элемент И-НЕ 47, элемент И 48.

В устройстве показаны линии 49-78 связи.

Блок 2 (фиг. 2) предназначен для преобразования совокупности магистральных сигналов средствами жесткой логики к форме, совместимой с остальной частью устройства, работающей на микропрограммном принципе. Кроме того, блок 2 формирует магистральные сигналы, выдаваемые из устройства в магистраль МПИ под управлени(/1

С

3 8

О О

ем БМУ. Блок 2 можно условно разделить на несколько функциональных схем: схема селекции адреса обращения по МПИ; схема формирования сигнала Исходное ; схема для режима выдачи вектора прерывания. Шина Адрес/данные, подключенная к блоку 2 (состоящая из М разрядов), разделяется на две части. Первая часть, состоящая из N младших разрядов (начиная с 1-го), подсоединена к информационным входам регистра 14. Эта группа разрядов определяет один из 2N номеров программно-доступных регистров устройства. Вторая часть шины, состоящая из (M-N-1) разрядов подключается к входам блока 15 элементов И. Эта группа разрядов определяет базовый адрес устройства. К(М-М)-му входу блока 15 подключается сигнал ВУ.

При совпадении информации, содержащейся во второй части шины с базовым адресом (и при наличии сигнала ВУ), блок 15 выдает сигнал положительной полярности. Базовый адрес устройства задается в блоке 15. Выход блока 15 подсоединен к (Ы+1)-му информационному входу регистра 14. Запись информации в регистр 14 производится передним фронтом сигнала Обм, который предварительно проходит через схему помехозащиты (элементы 18, 24 и 28) и элемент 25 задержки. Сбрасывается информация, содержащаяся в регистр j 14 при снятии сигнала Обм путем эго подключения к сбрасывающему входу регистра. Элемент 25 задержки необходим для того, чтобы предварить запись информации в регистр 14 снятием сбрасывающего сигнала с входа R.

После записи на первых К выходах регистра 14 фиксируется номер регистра устройства, к которому производится обращение. Эта совокупность потенциалов 49 выводится из блока 2 и подсоединяется к коммутатору 3. На (К+1)-м выходе регистра 14 записывается потенциал, далее по тексту называемый Свой, фиксирующий результат селекции адреса обращения к устройству. На выходе элемента И 36 формируется сигнал Свой 1 (Д4Т V ДЗП), который в качестве признака Обращение 50 подсоединяется к коммутатору 3. Данный признак идентифицирует факт обращений к какому- либо регистру устройства со стороны МПИ. Установка признака в высокое состояние сигнализирует БМУ устройства о необходимости обработать это обращение. С выхода элемента НЕ-19 к коммутатору 3 подсоеди няется признак Чтение/запись 51, определяющий направление пересылки информации. На элементах 26 и 30 реализована цепочка помехозащиты сигнала Д4Т V ДЗП.

Устройство может устанавливаться в исходное состояние со стороны МПИ двумя

способами: посредством магистрального сигнала Уст и посредством обращения к одному (назовем его обнуляющим) из программно-доступных регистров устройства. В обоих случаях блок 2 формирует для БМУ

0 устройства сигнал Исходное 52. В обеспечение второго способа в блок 2 включен блок 16 элементов И. Ко всем его входам подключена совокупность сигналов 49 номера адресуемого регистра и признак 065 ращение 50. Номер регистра, обращение к которому идентифицируется в обнуляющий сигнал для устройства, задается в блоке 16. Схема, обрабатывающая магистральные сигналы режима выдачи вектора преры0 вания, работает следующим образом.

В исходном состоянии выход триггера 33 находится в нулевом состоянии, сигнал ППР(П) на МПИ отсутствует. Тогда на входе S триггера 32 находится низкий потенциал.

5 Инверсный выход триггера 32 блокирует элемент yi-HE 35. При появлении на МПИ сигнала ППР(П) с входа S триггера 32 снимается низкий потенциал. Через время, обусловленное задержкой на элементе 27,

0 произойдет запись информации, находящейся на входе D, посредством положительного перепада на динамическом входе триггера. Так как на входе D находится низкий потенциал, изменится состояние выхо5 дов триггера. С его инверсного выхода будет подаваться положительный потенциал на элемент И-НЕ 35, разрешающий прохождение сигнала ППР далее в магистраль. Выход элемента И 37, идентифицирующий

0 факт наличия или отсутствия сигнала ППР при выставленном сигнале ЗПР устройства, будет находиться в нулевом состоянии. После прохождения сигнала ППР(П) на входе триггера 32 установится низкий потенциал,

5 и прохождение через элемент И-НЕ 35 снова будет заблокировано,

Если триггер 33 будет установлен в единичное состояние сигналом на линии 53, то через элемент НЕ 22 в магистраль начнет

0 выдаваться сигнал ЗПР, В ответ на него из МПИ должен прийти сигнал ППР(П) и записать информацию в триггер 32. Так как на входе D триггера находится высокий потенциал, то изменения состояния выходов триг5 гера 32 не произойдет, и распространение сигнала ППР через элемент И 37 будет заблокировано. На выходе элемента И 37 ус- тановится высокий потенциал. Он свидетельствует о том, что при выдаче устройством сигнала ЗПР из МПИ принят сигнал ППР, адресованный своему устройству. Выход элемента И 37 в качестве признака Свой ППР (54) выводится из блока 2 на вход коммутатора 3.

Сброс триггера 33 производится сигналом на линии 55 под управлением БМУ. Также под управлением БМУ взводится триггер 34 сигналом на линии 56, формирующий сигнал Отв, выдаваемый в магистраль через элемент И 23. Сброс этого триггера осу- щесляется сигналом Свой (ДЧТ V ДЗП) Свой ППР, формируемом на выходе элемента ИЛИ 31, Выход этого элемента выводится за пределы блока 2 на сбрасывающий вход регистра 4 управления шинными формирователями.

Коммутатор 3 данных предназначен для вывода на кодовую магистраль устройства данных, пересылаемых из МПИ, а также для вывода на кодовую магистраль информации, преобразованной блоком 2.

Шина Адрес/данные подключается к верхнему плечу коммутатора. Нижнее плечо коммутатора можно условно разделить на два поля. Поле из L младших разрядов нижнего плеча коммутатора скомпоновано таким образом, чтобы в совокупности представлять адрес ячейки блока 41 памяти микрокоманд. Эта ячейка определяет местонахождение подпрограммы обработки конкретного обращения к регистру устройства, содержащейся в этом же блоке памяти микрокоманд. Понятно, что разрядность поля определена разрядностью блока памяти микрокоманд. Поле маскирования реализовано прошивкой заданных потенциалов на соответствующих контактах. Оставшаяся часть разрядного поля нижнего плеча коммутатора 3 используется для подключения одиночных признаков, вырабатываемых блоком 2 и триггером 10 для их последующей трансляции на кодовую магистраль устройства.

БМУ 12 (фиг. 3) работает следующим образом.

Центральным элементом блока является У ФАМ 40. УФАМ реализуется на основе БИС 1804ВУ1. УФАМ можно представить как мультиплексор, который выбирает адрес микрокоманды из четырех источников, Источниками адреса является информационный вход D, регистр адреса РгАДР, внутренний счетчик микрокоманд (СМК), внутренний 4-х уровневый стек,

БМУ может работать в двух режимах. В первом осуществляется последовательная выборки микрокоманд, Во втором режиме осуществляется переход (в зависимости от условия или вне зависимости от него) на другой адрес микрокоманды. Новый адрес

не является очередным по отношению к предыдущему. Он транслируется от одного из источников адреса вход D, РгАДР, стек. В первом режиме все выходы регистра 5 43 находятся в нулевом состоянии. Информация с выходов регистра 43 переписывается в регистр 44 после каждого тактового импульса. В результате на входы FE, PVP, SO, S1 УФАМ 40 будут выдаваться потенци- 0 алы соответственно: 1, О, О, О. Такое состояние потенциалов на управляющих входах УФАМ определяет в качестве источ- .ника адреса СМК, Стек в этом случае отключен, Выходы УФАМ подключены к адресным

5 входам блока 41 памяти микрокоманд. Выходы 58 первой группы блока 41 применяются в качестве управляющих констант, используемых как в БМУ, так и за его пределами. Выходы 61 второй группы блока 41

0 подключаются к группе дешифраторов 42, которые вырабатывают микрооперации, Воздействием на внешние (для БМУ) устройства микрооперациями в сопровождении констант 58 в соответствии с

5 определенным алгоритмом производится функция управления БМУ. Условные и безусловные переходы в БМУ с целью более эффективного использования блока памяти микрокоманд осуществляются едва такта. В

0 первом такте выходные разряды блока 41 участвуют в вырабатывании микрооперации 62, выборе условия и адаптации его полярности, в предварительном формировании управляющих сигналов в регистре 43 Во

5 втором такте разряды 58 блока памяти микрокоманд несут в себе информацию об адресе перехода (через РгАДР). Рассмотрим более подробно работу БМУ в этом режиме, В первом такте микрооперация 62 запи0 сывает в регистр 43 данные, подключенные к информационным входам. К первым Р информационным входам регистра 43 подключены разряды блока памяти микрокоманд, несущие информацию о предполагаемом

5 режиме работы стека и источнике нового адреса. К (Р+1)-му входу регистра 43 постоянно подключен положительный потенциал. К (Р+2)-му входу регистра 43 подключен выход схемы выбора условия. Условия подклю0 чаются к информационным входам мультиплексора 38 через кодовую магистраль устройства. Выбор конкретного условия осуществляется под воздействием констант на линии 58, подключенных к уп5 равляющим входам мультиплексора. На элементе 39 полярность условия адаптируется таким образом, чтобы на (Р+2)-м информационном входе регистра 43 факт наличия условия воспроизводился отрицательным уровнем сигнала. Допустим, что микрооперация записала в регистр 43 по входу (Р+2) положительный потенциал (условие отсутствует). Тогда и на (Р+2)-м выходе регистра 43 появится положительный потенциал, который, пройдя через элементы 46 и 48, преобразуется в отрицательный и установится на входе сброса регистра 43. Регистр 43 обнулится. Обнулится и информация на первых Р его выходах, которая предварительно (вместо с условием) туда записалась. Во втором такте информация с выходов регистра 43 перепишется в регистр D положиТель- ным перепадом тактовой частоты, но никаких изменений на выходе регистра 44 не произойдет. Источником адреса по-прежнему будет СМК, Таким образом, условный переход не состоялся, так как не подтвердилось условие.

Допустим, что микрооперация записала в регистр 43 по входу (Р+2) отрицательный потенциал (условие присутствует). Тогда на (Р+2)-м выходе регистра появится отрицательный потенциал, и обнуление регистра 43 по цепи обратной связи (элемент 46 и 48, вход сброса регистра 43) не произойдет. Сохранится и информация, записанная в регистр 43 одновременно с условием. Управляющие константы на линии 58 к началу следующего такта устанавливают на входах РгАДР УФАМ адрес перехода. После второго такта на выходе регистра 44 установятся измененные управляющие потенциалы для входов FE, PVP, SO, S1 УФАМ, В регистре адреса УФАМ зафиксируется адрес перехода. Таким образом, осуществился переход на неочередной адрес. Если переход предполагается по входам D УФАМ, то ЕМУ предварительно подключает к этим входам .соответствующую информацию, Схема БМУ должна работать таким образом, чтобы после перехода на неочередной адрес последующие считываемые адреса микрокоманд из УФАМ были уже очередными. Поэтому, после второго такта состоя ще- гося перехода, регистр 43 обнуляется: на входах элемента И-НЕ 47 устанавливаются положительные потенциалы, и сигнал отрицательной полярности с выхода элемента И-НЕ 47, транслируясь через элемент И 48, подается на вход сброса регистра 43.

Процесс осуществления безусловного перехода на неочередной адрес аналогичен условному переходу по подтвержденному условию. В этом случае подтвержденное условие формируется путем блокировки выхода мультиплексора 38 воздействием на его управляющие входы.

Схема БМУ предусматривает принудительное обнуление выходов УФАМ. регистра 43 внешним сигналом на линии 42 из устройства.

Особенностью работы БМУ является то, что при анализе условий происходит их синхронизация в регистре 43. Данное свойство БМУ избавляет от необходимости синхронизировать совокупность условий (признаков) за пределами БМУ.

Устройство работает следующим обра0 зом.

При включении устройства вместе со всеми другими устройствами, подключенными к магистрали, из МПИ выдается сигнал Уст. Этот сигнал преобразуется в

5 блоке 2 в сигнал Исходное на линии 52 и поступает в БМУ 12. После этого БМУ 12 считывает микрокоманды последовательно, начиная с нулевого адреса. В начале адресного пространства блока памяти микроко0 манд обычно размещают подпрограмму исходной подготовки устройства к работе, которая и будет выполняться. В этой подпрограмме целесообразно обнулить триггер 33, формирующий сигнал ЗПР, так как после

5 включения он может находиться в произвольном состоянии. Необходимо также отключить от кодовой магистрали все регистры, имеющие на нее выход, чтобы не допустить их встречного включения. Для

0 этого в регистр 6 записывается соответствующий код.

Устройство может приводиться в исходное состояние нетолько посредством сигнала Уст, но и путем обращения из МПИ к его

5 установочному регистру. При таком обращении также вырабатывается сигнал Исходное на линии 52 в блоке 2. В этом случае БМУ 12 должен сформировать в магистраль сигнал Отв, чтобы не нарушить временную

0 диаграмму обмена в МПИ. С этой целью в нулевой ячейке блока памяти микрокоманд содержится микрокоманда, вырабатывающая микрооперацию на линии 56. Эта микрооперация устанавливает в высокое

5 состояние триггер 34 (блок 2), формирующий сигнал Отв. Если устройство устанавливается в исходное состояние сигналом Уст, то аналогичным образом БМУ на нулевом адресе выдает микрооперацию на ли0 нии 56. Однако в этом случае сигнал Отв не сформируется, так как триггер 34 зажат noR входу (нет сигнала (), При обработке обращений по МПИ устройство работает следующим образом.

5 Записывая в регистр б определенный код, БМУ 12 подключает к кодовой магистрали устройства нижнее плечо коммутатора 3 данных. Далее БМУ 12 анализирует признак Обращение, так как кодовая магистраль подключена к мультиплексору 38.

Допустим, что признак Обращение подтвердился. Тогда ЕМУ осуществит переход по адресу, установленному на кодовой магистрали (источник адреса - вход D). Адрес, установленный на кодовой магистрали, формируется коммутатором данных. Поле адреса коммутатора данных допускает возможных значений, где К - количество шин в совокупности разрядов, определяющих номер адресуемого регистра. Каждое из этих значений однозначно идентифицирует адресуемый регистр устройства и направленность (чтение или запись) обращения. В блоке памяти микрокоманд данные значения адресуют группу ячеек, в которых Прошиты безусловные переходы к подпрограммам обработки конкретных обращений. Происходит выполнение подпрограммы. Обращение к установочному регистру устройства является исключением из вышеописанного правила обработки обращений.

В режиме выдачи вектора прерывания (ВП). Устройство работает следующим образом,

Допустим, что адрес вектора прерывания устройства хранится в одной из ячеек ОЗУ 11. При возникновении необходимости выдачи ВП БМУ 12 выдает микрооперацию на линии 53. Данная микрооперация уста- навливает в высокое состояние триггер 33 блока 2. В МПИ начинает выдаваться сигнал ЗПР. В ответ на ЗПР из МПИ должен прийти сигнал ППР (П), подтверждающий готовность арбитра на магистрали принять век- тор прерывания. При появлении этого сигнала в блоке 2 устройства формируется признак Свой ППР. Данный признак также подключается к коммутатору 3 данных. БМУ устройства после выдачи сигнала ЗПР находится в режиме ожидания признака Свой ППР. При его появлении БМУ переходит к выполнению подпрограммы выдачи ВП. В этой подпрограмме сбрасывается сигнал ЗПР, информация ячейки ОЗУ, содержа- щей адрес ВП, выставляется на кодовую магистраль, шинные формирователи переключаются для выдачи информации из кодовой магистрали в МПИ, формируется сигнал Отв, данные держатся на магистрали не- которое время, а затем шинные формирователи отключаются от МПИ. Следовательно, устройство может выдавать произвольное количество векторов прерывания, если выделить для них столько же ячеек ОЗУ.

Рассмотрим работу одного из вариантов реализации устройства. Предположим, что устройство является частью адаптера, осуществляющего сопряжение между мик- роЭВМ (по МПИ) и каналом. Устройство

имеет следующие программно-доступные регистры; регистр состояния (PC), магистральный счетчик (МС), канальный счетчик (КС), ОЗУ, счетчик принятых слов, счетчик выдаваемых слов, регистр команд (РК), установочный регистр. Для восьми регистров . Описанная аппаратная организация устройства позволяет разместить все эти регистры (за исключением установочного) в ОЗУ. С этой целью вся емкость ОЗУ делится на зону данных и служебную зону. Программно-доступные регистры физически представляют собой ячейки памяти служебной зоны ОЗУ/

PC предназначен для сообщения мик- роЭВМ о готовности и неисправности устройства. Он доступен для микроЭВМ только по чтению. Информация в PC заносится БМУ по тракту: блок 41 - нижнее плечо регистра 8 - счетчик 9 адреса - буферный регистр 7 - кодовая магистраль - ячейка PC ОЗУ.

МС используется в процессе записи и считывания данных в МПИ из ОЗУ. В данной реализации устройства осуществляется последовательный доступ к ОЗУ: содержимое МС инкрементируется после каждого обращения к памяти. Аналогичным образом канальный счетчик используется при записи (чтении) данных в ОЗУ со стороны канала.

Счетчик принятых слов фиксирует количество слов, принятых при обмене с каналом. Инкрементирование содержимого счетчика производится следующим образом, содержимое ячейки извлекается из ОЗУ г, размещается в счетчике 9 адреса, в счетчик 9 выдается микрооперация, модифицированное содержимое счетчика 9 возвращается в ячейку счетчика принятых слов 03V.

Счетчик выданных слов фиксирует количество слов, которое осталось выдать в канал. После каждого слова счетчик декрементируется. БМУ производит анализ признака Переполнение, подключенного к полю признаков коммутатора 3 данных. При обнулении содержимого счетчика выданных слое в счетчике 9 вырабатывается сигнал переноса, который устанавливает триггер 10 в единичное состояние. БМУ фиксирует наличие признака Переполнение и прекращает выдачу слов в канал.

В устройстве можно организовать различные по назначению счетчики: количества сбоев, контроля времени, числа циклов и др. Обращение к РК имеет особенности. При записи в РКданные, передаваемые по МПИ, заносятся в соответствующую ячейку ОЗУ. После этого БМУ осуществляет переход по адресу кодовой магистрали, причем на кодовой магистрали устанавливаются данные, передаваемые из МПИ. Таким образом, обращение с записью к регистру команд воспринимается устройством как принудительное выполнение того фрагмента микропрограммы, начало которого определяется передаваемыми из МПИ данными. Данное обращение применяется при пуске устройства на выполнение подпрограмм, инициализирующих взаимодействие с каналом (рабочие программы).

Устройство взаимодействует с МПИ в условиях ограничения по времени. Микро- ЭВМ при инициализации обмена с устройством ожидает сигнал Отв не более Т 10 мкс. БМУ при выполнении рабочих программ периодически переключается для анализа наличия обращения по МПИ и, если таковое имеется, обрабатывает его Выполнив обработку обращения, БМУ осуществляет возврат в тело рабочей программы. Рабочую программу целесообразно, строить таким образом, чтобы она состояла из ограниченных по времени функционально законченных процедур После выполнения каждой такой процедуры БМУ должен проанализировать обращение по МПИ, чтобы не упустить его. Предположим, что подпрограмма обработки обращения по МПИ выполняется за время ti, а процедура рабочей программы - за время ta. Тогда условие ограничения по времени для упомянутых подпрограмм запишется: ti + tz Т

Формула изобретения Микропрограммное устройство сопряжения, содержащее блок шинных формирователей, блок дешифрации управляющих сигналов, блок оперативной памяти, счетчик адреса, коммутатор, причем выход блока шинных формирователей соединен с первым входом блока дешифрации управляющих сигналов и входом данных коммутатора, второй вход и первый выход блока дешифрации управляющих сигналов являются управляющими магистральными входом и выходом устройства, выход счетчика адреса подключен к адресному входу блока оперативной памяти, вход-выход данных блока оперативной памяти и выход коммутатора подключены через кодовую магистраль к входу данных блока шинных формирователей и являются канальным входом-выходом данных устройства, вход- выход блока шинных формирователей является магистральным входом-выходом данных устройства, отличающееся тем, что, с целью повышения быстродействия устройства и расширения области его применения, в него введены четыре регистра, элемент ИЛИ-НЕ, триггер, блок микропрограммного управления, тактовый генератор, второй выход блока дешифрации управляющих сигналов подключен к второму входу данных коммутатора, третий выход блока дешифрации управляющих сигналов подключен к входу сброса первого регистра, четвертый выход блока дешифрации управляющих сигналов подключен к входу

сброса блока микропрограммного управления, первый выход которого подклюг чен к информационным входам первого и второго регистров, первому информационному входу третьего регистра и является

канальным выходом данных устройства, с второго по седьмой выходы блока микропрограммного управления подключены соответственно к входу сброса триггера, к входам записи, сложения и вычитания счетчика адреса, к синхровходам третьего и четвертого регистров, восьмой и девятый выходы блока микропрограммного управления соединены соответственно с синхровхо- дами первого и второго регистров, третий

вход блока дешифрации управляющих сигналов соединен с десятым, одиннадцатым и двенадцатым выходами блока микропрограммного управления, тринадцатый выход которого является канальным управляющим

выходом устройства, выход тактового генератора подключен к синхровходу блока мик- ропрограммного управления, первый выход первого регистра подключен к входу управления блока шинных формирователей, второй выход первого регистра подключен к первому входу элемента ИЛИ-НЕ, выход которого подключен к первому управляющему входу коммутатора, первый выход второго регистра подключен к второму входу элемента ИЛИ-НЕ, второй выход - к второму управляющему входу коммутатора, третий выход - к входу блокировки выходов четвертого регистра, четвертый выход - к входу разрешения третьего регистра, пятый выход

- к входу выборки блока оперативной памяти, шестой выход - к входу управления режимом работы блока оперативной памяти, выход переноса счетчика адреса соединен с установочным входом триггера, информаци0 онный выход счетчика адреса подключен к информационному входу четвертого регистра, выход которого через кодовую магистраль подключен к входу данных блока шинных, формирователей и к второму ин5 формационному входу третьего регистра и входу данных блока микропрограммного управления, выход триггера подключен к третьему управляющему входу коммутатора.

51 50 &

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Многоканальное микропрограммное устройство ввода-вывода | 1983 |

|

SU1104500A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Устройство для управления и обмена данными | 1986 |

|

SU1319042A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

Изобретение предназначено для использования в вычислительной технике при создании устройства ввода-вывода, аппаратуры сопряжения, измерительной и бытовой техники. Цель изобретения - повышение быстродействия устройства и расширение области его применения путем обеспечения микропрограммного управления вводом- выводом информации. Устройство содержит регистры, элемент ИЛИ-НЕ, триггер, блок микропрограммного управления, тактовый генератор, блок шинных формирователей, блок дешифрации управляющих сигналов, блок оперативной памяти, счетчик адреса, коммутатор, 3 ил.

56 55 53

52

| Устройство для сопряжения ЭВМ и абонента | 1985 |

|

SU1264195A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| Устройство для сопряжения | 1985 |

|

SU1315985A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-12-23—Публикация

1989-05-03—Подача