Изобретение относится к устройствам ввода и обработки измерительной информации, получаемой при натурных испытаниях сложных технических систем, и может быть использовано для связи источников непрерывных потоков информации с ЭВМ различной архитектуры, например персональными ЭВМ, миниЭВМ и др.

Известна система ввода-вывода информации [1] , обеспечивающая связь основного процессора с измерительным устройством, генерирующим поток информации, и содержащая микропроцессор, выполняющий набор специальных команд, поступающих от основного процессора, и сверхоперативную память. Микропроцессор распределяет сверхоперативную память между блоками поступающей информации в соответствии с командами основного процессора, каждая из которых содержит переменный признак блока, определяющий структуру сверхоперативной памяти, и адрес блока в ней.

Недостатком известной системы является отсутствие возможности одновременного ввода цифровых потоков информации от нескольких различных источников в несколько различных приемников, поскольку в однопроцессорной системе нет средств ввода и организации распределенной обработки нескольких потоков данных.

Наиболее близкой к заявляемой по технической сущности является система для связи модулей распределенной мультипроцессорной системы [2] , содержащая магистраль, объединяющую несколько процессорных модулей, каждый из которых содержит блок магистрального обмена, вырабатывающий временной интервал, соответствующий данному модулю, в течение которого происходит передача информации от этого модуля. Передающий модуль принимает запрос на передачу сообщения, который поступает от центрального процессора, выбирает соответствующий временной интервал и передает в течение этого интервала признак сообщения, который содержит адрес принимающего модуля и код приоритета. Принимающий модуль содержит блоки, которые обеспечивают контроль за состоянием магистрали, обнаруживая при этом сигналы подтверждения приема признака сообщения, и поддерживают возможность передачи передающим модулем признака сообщения в течение ряда временных интервалов до тех пор, пока принимающий модуль не подтвердит прием.

Известная система позволяет вводить и обрабатывать информацию от нескольких источников, в данном случае процессорных модулей, однако при передаче непрерывных потоков данных, поступающих одновременно, быстродействие системы (количество информации, обрабатываемой в единицу времени) ограничено, поскольку каждое слово принимается и передается по прерыванию, на обработку которого необходимы дополнительные ресурсы процессорного модуля. Кроме того, если в данный процессорный модуль поступает сообщение от другого модуля, то на выделение сообщения из потока информации (на обработку адресов) также требуется дополнительное время. В известной системе все источники информации жестко подключаются к блоку ввода-вывода конкретного процессорного модуля, поэтому программная коммутация источников невозможна. Таким образом, недостатком системы является низкое быстродействие при вводе и обработке информации от нескольких источников, поступающей одновременно и непрерывно.

Анализ патентных и литературных данных показал, что совокупность указанных признаков нигде ранее не описана и не известна, а именно данная совокупность обеспечивает функциональную полноту, законченность заявленного технического решения и достижение цели.

Цель изобретения - повышение быстродействия мультипроцессорной системы ввода и предварительной обработки данных для непрерывных потоков информации, поступающих одновременно от нескольких источников.

Цель достигается тем, что в мультипроцессорную систему ввода и предварительной обработки информации, содержащую процессорные модули, входы-выходы которых подключены к межпроцессорной магистрали, введены коммутатор источников, информационная магистраль, блоки связи с источниками, формирователь адресов и приоритетов источника и дополнительные процессорные модули, входы-выходы которых подключены к межпроцессорной магистрали, входы подключены к информационной магистрали, к которой подключены входы-выходы блоков связи с источниками, при этом первый выход формирователя адреса и приоритета источника через межпроцессорную магистраль подключен к входу коммутатора источников, вход-выход которого подключен к информационной магистрали, второй выход формирователя адреса и приоритета источника подключен к информационной магистрали.

Введение информационной магистрали для приема и передачи информации от источников обеспечивает распределение информационных потоков, разгрузку межпроцессорной магистрали и повышение быстродействия системы. Введение дополнительных процессорных модулей с дополнительными запоминающими устройствами в их составе, которые связаны непосредственно с информационной магистралью, обеспечивает ввод информации без затрат времени процессора на обработку прерываний. Введение коммутатора источников для управляемого распределения одного или нескольких потоков в один или несколько процессорных модулей дает возможность программного управления связями источников информации. Введение формирователя адресов и приоритетов источников обеспечивает управление коммутатором и порядком приема-передачи информации процессорными модулями по информационной и межпроцессорной магистралям.

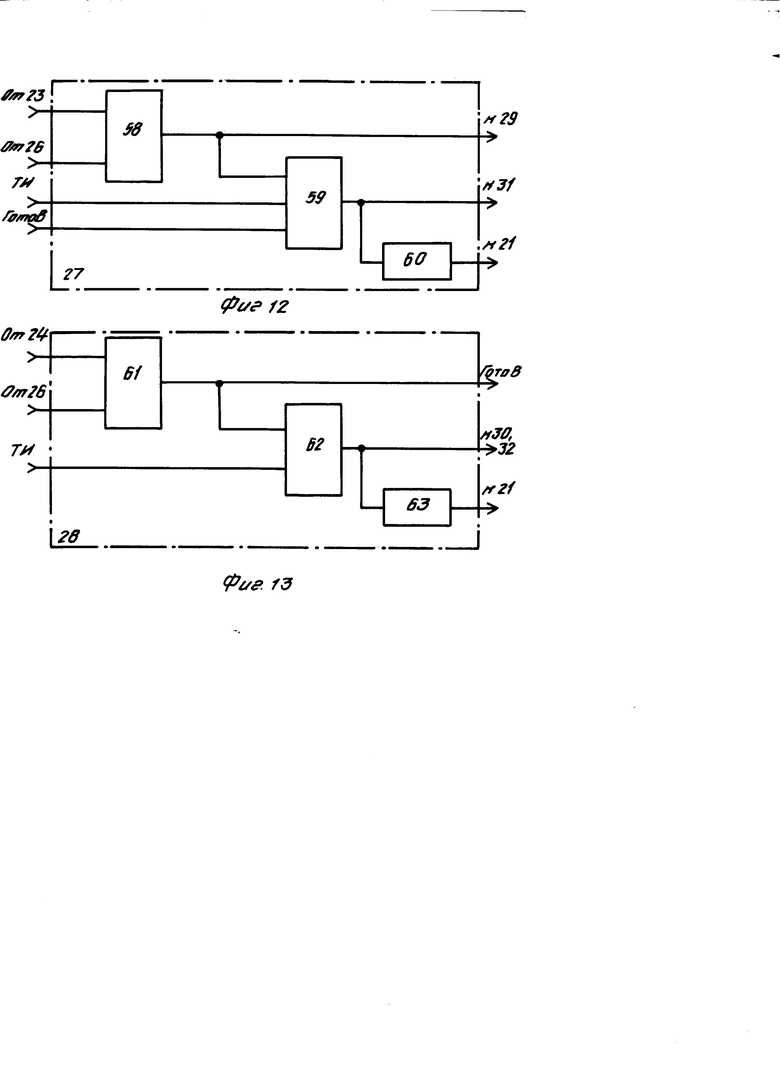

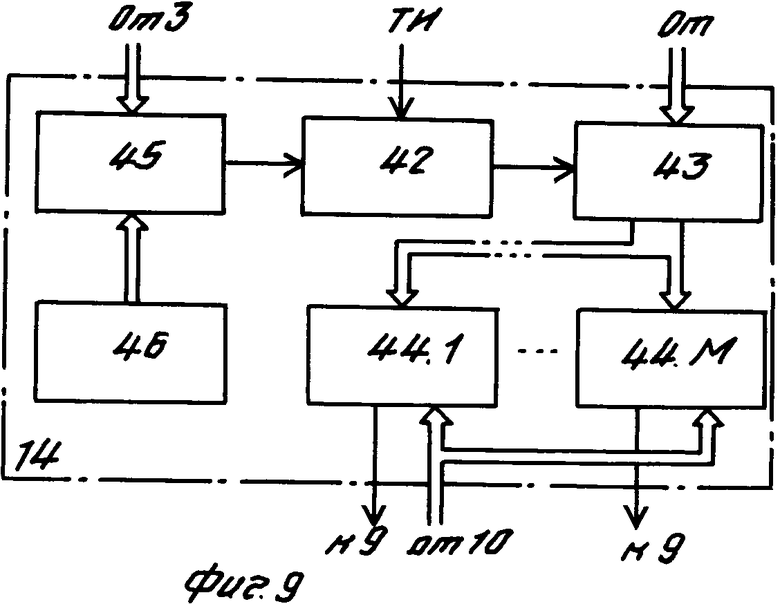

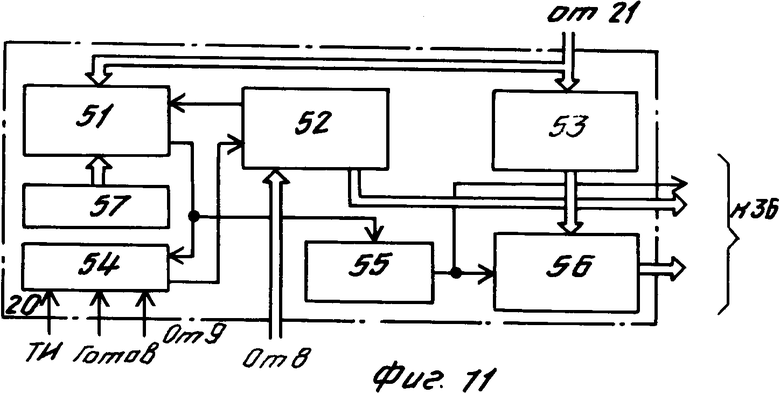

На фиг. 1 представлена структурная схема системы-прототипа; на фиг. 2 - структурная схема процессорного модуля системы-прототипа; на фиг. 3 - блок-схема системы-прототипа; на фиг. 4 - структурная схема заявляемой системы; на фиг. 5 - структурная схема процессорного модуля заявляемой системы; на фиг. 6 и 7 - блок-схема заявляемой системы; на фиг. 8 - блок-схема формирователя адреса и приоритета источников; на фиг. 9 - блок-схема коммутатора источников; на фиг. 10 - блок-схема блока связи с источником; на фиг. 11 - блок-схема блока управления доступом к запоминающему устройству (ЗУ); на фиг. 12 - блок-схема блока управления передачей; на фиг. 13 - блок-схема блока управления приемом.

В системе-прототипе межпроцессорная магистраль 1 объединяет N процессорных модулей 2 (фиг. 1). Каждый процессорный модуль содержит внутрипроцессорную магистраль 3, объединяющую центральный процессор 4, блок 5 ввода-вывода, ЗУ 6, и блок 7 магистрального обмена (фиг. 2), который связывает процессорный модуль с межпроцессорной магистралью.

Блок-схема системы-прототипа содержит (фиг. 3) межпроцессорную магистраль 1, внутрипроцессорную магистраль 2, причем магистраль 1 включает шину 8 данных, шину 9 адреса приемника, шину 10 тактовых импульсов и шину 11 готовности, ЗУ 6, блок 5 ввода-вывода, центральный процессор 4, блок 7 магистрального обмена, который включает в себя регистр 12 адреса модуля передачи, регистр 13 данных, регистр 14 адреса модуля приема, счетчик 15, регистр 16 адреса модуля CNR, блок 17 управления передачей, блок 18 управления приемом, компаратор 19 передачи, компаратор 20 приема, порт 21 данных, порт 22 адреса, порт 23 управления, порт 24 CNR, и регистр 25 данных модуля передачи.

Система-прототип работает следующим образом.

По внутрипроцессорной магистрали 3 через порт 24 в регистр 16 загружается адрес модуля, который может работать в двух режимах: приема и передачи.

Режим передачи. По внутрипроцессорной магистрали 3 через порт 22 в регистр 14 происходит запись адреса модуля, принимающего данные. Запись слова данных осуществляется через порт 21 в регистр 25 по управляющему сигналу от порта 23 управления, этот же сигнал поступает на первый вход блока 17 управления.

С шины 10 тактовые импульсы поступают на вход счетчика 15, выходной код которого изменяется с каждым импульсом на единицу и поступает на первый вход компаратора 19 для сравнения с адресом модуля от регистра 16, выход которого подключен к второму входу компаратора 19.

При совпадении кодов компаратор 19 формирует управляющий сигнал, подаваемый на второй вход блока 17 управления, третий и четвертый входы которого подключены соответственно к шине 10 тактовых импульсов и шине 11 готовности. При активных уровнях сигналов на четырех входах блок 17 управления вырабатывает три выходных сигнала: сигнал прерывания работы центрального процессора 4, передаваемый на магистраль 3, и сигналы разрешения выдачи адреса приема и данных соответственно на шины 9 и 8 магистрали 1, поступающие на входы управления третьим состоянием соответственно регистров 14 и 25. В результате на магистраль 1 передаются адрес, заданный регистром 14 на шине 9, и данные, заданные регистром 25 на шине 8.

Для передачи последующих слов данных из порта 21 через регистр 25 по одному и тому же адресу указанный выше порядок передачи повторяется. При этом в регистре 14 сохраняется прежний адрес модуля приема, а данные в регистре 25 могут обновляться.

Режим приема. Компаратор 20 сравнивает адрес модуля из регистра 16 с адресом приемника от шины 9 межпроцессорной магистрали 1. При совпадении адресов активный уровень поступает на первый вход блока 18 управления приемом, на второй и третий входы которого подаются сигналы соответственно с выхода порта 23 управления и от шины 10 тактовых импульсов.

При наличии активных уровней входных сигналов на первом выходе блока 18 формируется сигнал готовности к приему, передаваемый на шину 11, на втором выходе блока 18 формируется сигнал прерывания, передаваемый центральному процессору 4 через внутрипроцессорную магистраль 3, на третьем выходе блока 18 формируется строб, по которому происходит запись адреса передающего модуля из счетчика 15 в регистр 12 и слова данных от шины 8 в регистр 13. Адрес и данные через соответственно порт 22 и порт 21 поступают на внутрипроцессорную магистраль 3 и далее через нее в центральный процессор 4, который обеспечивает чтение и запись адресов, слов данных и управления через блок 5 ввода-вывода в порты 21, 22, 23 и 24, а также хранение данных в ЗУ 6.

Заявляемая система (фиг. 6 и 7) содержит межпроцессорную магистраль 1, включающую шину 2 данных, шину 3 адреса приемника, шину 4 адреса источника, шину 5 тактовых импульсов и шину 6 готовности, информационную магистраль 7, включающую шину 8 данных, шину 9 адреса приемника, шину 10 адреса источника, шину 11 тактовых импульсов и шину 12 готовности, формирователь 13 адреса и приоритета источников, коммутатор 14, блоки 15.1, . . . , 15. L связи с источником, процессорные модули 16.1, . . . , 16. N, включающие центральный процессор 17, блок 18 ввода-вывода, ЗУ 19, блок 20 управления доступом к ЗУ, внутрипроцессорную магистраль 21 и блок 22 магистрального обмена, включающий компаратор 23 передачи, компаратор 24 приема, регистр 25 адреса модуля, порт 26 управления, блок 27 управления передачей, блок 28 управления приемом, регистр 29 адреса модуля приема, регистр 30 адреса модуля передачи, регистр 31 данных модуля передачи, регистр 32 данных модуля приема, порт 33 данных, порт 34 адреса и порт 35 адреса модуля, и ЗУ 36.

Формирователь 13 адреса и приоритета источников (фиг. 8) включает счетчики 37, 38, преобразователи 39, 40 кодов, генератор 41 тактовых импульсов. Коммутатор 14 (фиг. 9) включает элемент И 42, регистр 43 адресов источников, компараторы 44.1, . . . , 44. М, 45, задатчик 46 адреса. Блок 15 связи с источником (фиг. 10) включает компаратор 47, задатчик 48 адреса, элемент И 49, регистр 50 данных. Блок 20 управления доступом к ЗУ (фиг. 11) включает компаратор 51, регистр 52 данных источника, порт 53 адреса ЗУ, элемент И 54, одновибратор 55, счетчик 56 адреса ЗУ, задатчик 57 кода. Блок 27 управления передачей (фиг. 12) включает элементы И 58, 59, одновибратор 60. Блок 28 управления приемом (фиг. 13) включает элементы И 61, 62 и одновибратор 63.

В каждом процессорном модуле 16.1, . . . , 16. N внутрипроцессорная магистраль 21 подключена к входам-выходам центрального процессора 17, блока 18 ввода-вывода, ЗУ 19, портов 33, 34 ввода-вывода, а также к входам портов 26, 35 вывода, первый и второй выходы блока 27 управления передачей подключены к входам управления соответственно регистров 29, 31, выход порта 35 вывода через регистр 25 подключен к первым входам компараторов 23, 24, выходы которых подключены к первым входам соответственно блока 27 управления передачей и блока 28 управления приемом. К вторым входам последних подключены соответственно первый и второй выходы порта 26 вывода, первый выход которого подключен к входу записи регистра 31. Первый выход блока 28 управления приемом подключен к входам управления регистров 30, 32, выходы которых подключены к входам соответственно портов 34, 33 ввода-вывода, выходы которых подключены к входам данных соответственно регистров 29, 31. Второй выход блока 28 управления приемом и третий выход блока 27 управления передачей подключены к внутрипроцессорной магистрали 21, выход регистра 29 через шину 3 адреса приемника подключен к второму входу компаратора 24, выход регистра 31 через шину 2 данных подключен к входу данных регистра 32, шина 5 тактовых импульсов подключена к третьим входам блока 28 управления приемом и блока 27 управления передачей. Третий выход блока 28 управления приемом через шину 6 сигнала готовности подключен к четвертому входу блока 27 управления передачей. Первый и второй выходы формирователя 13 адреса и приоритета источников через соответственно шины 4, 10 адреса источников подключены соответственно к второму входу компаратора 23 и первому входу коммутатора 14, 1,2, . . . , М-й выходы которого подключены соответственно к 1,2, . . . , М-й линии шины 9 адреса приемника. Шина 2 данных, шина 3 адреса приемника и шина 5 тактовых импульсов подключены соответственно к второму, третьему и четвертому входам коммутатора 14. Третий выход формирователя 13 адреса и приоритета источников подключен к шине 5 тактовых импульсов, шина 4 адреса источника подключена к входу регистра 30. Первый и второй выходы блоков 15.1, . . . , 15. L связи с источниками подключены соответственно к дополнительной шине 8 данных и дополнительной шине 12 сигнала готовности, шина 10 адреса источников и шина 11 тактовых импульсов подключены соответственно к первому и второму входам блоков 15.1, . . . , 15. L связи с источниками. В каждом из М процессорных модулей 16.1, . . . , 16. М внутрипроцессорная магистраль 21 подключена к первому входу блока 20 управления доступом к ЗУ и входу-выходу двухпортового ЗУ 36, к первому, второму и третьему входам которого подключены соответственно первый, второй и третий выходы блока 20 управления доступом к ЗУ, к второму, третьему и четвертому входам которого подключены соответственно дополнительная шина 8 данных, дополнительная шина 12 сигнала готовности и шина 11 тактовых импульсов. 1,2, . . . , М-я линии шины 9 адреса приемника подключены к пятым входам блоков 20 управления доступом к ЗУ соответственно 1,2, . . . , М-го процессорного модуля.

Заявляемая система работает следующим образом.

Формирователь 13 обеспечивает формирование тактовых импульсов, а также последовательности адресов источников на магистралях 1, 7, при этом адреса распределены с учетом приоритетов, установленных в соответствии с информативностью источников (фиг. 4).

Процессорный модуль 16. k, на который от магистрали 7 должен поступать непрерывный поток информации, загружает по магистрали 1 в коммутатор 14 слово, обеспечивающее коммутацию источника с i-м адресом через блок 15. i на данный модуль (1≅k≅M, 1≅<N>i≅L), и при необходимости пересылает это слово другим процессорным модулям или одному из них (управляющему) для того, чтобы учесть при загрузке коммутацию других источников. Поток информации через блок 15. i и магистраль 7 поступает в процессорный модуль 16. k, который ведет обработку непрерывного потока информации. Результаты обработки по магистрали 1 могут быть переданы другим процессорным модулям 16.

При соответствующей загрузке коммутатора 14 возможна передача непрерывного потока информации от одного источника к нескольким процессорным модулям 16 или от нескольких источников к одному или нескольким процессорным модулям. Таким образом, процессорные модули 16.1, . . . , 16. М могут быть использованы для предварительной обработки информации и передачи результатов обработки в модули 16.1, . . . , 16. N. Процессорные модули 16. М+1, . . . , 16. N, связанные только с межпроцессорной магистралью 1, могут выполнять как предварительную, так и основную обработку информации, ее графическое отображение и документирование.

Процессорные модули 16.1, . . . , 16. М по сравнению с процессорными модулями 16. М+1, . . . , 16. N, совпадающими с использованными в составе системы-прототипа, дополнены (фиг. 5) двухпортовым ЗУ 36 и блоком 20 управления доступом к ЗУ, которые обеспечивают прием и временное хранение слов данных от информационной магистрали 7 в течение времени, пока центральный процессор 17 занят обработкой информации и обслуживанием прерываний, не связанных с обращением к ЗУ 36. Связь центрального процессора 17 с другими процессорными модулями обеспечивают блок 18 ввода-вывода и блок 22 магистрального обмена. ЗУ 19 и 36 служат для хранения программ и данных.

Формирователь 13 адреса и приоритета источников (фиг. 6 и 7) формирует последовательность тактовых импульсов на шинах 5 и 11, а также последовательности адресов источников на шинах 4 и 10 магистралей 1 и 7 соответственно. Для магистрали 7 источниками являются и блоки 15.1, . . . , 15. L, а для магистрали 1 - процессорные модули 16.1, . . . , 16. N. Тактовые импульсы поступают с выхода генератора 41 (фиг. 8), а адреса источников формируются путем пересчета тактовых импульсов счетчиками 37, 38 и преобразования их выходных кодов с учетом требуемых приоритетов преобразователями 39, 40 соответственно. Высшему приоритету соответствует большее количество одинаковых адресов в цикле соответствующего счетчика.

Обмен информацией между модулями 16.1, . . . , 16. N по магистрали 1 происходит следующим образом.

По внутрипроцессорной магистрали 21 через порт 35 в регистр 25 загружается адрес процессорного модуля, который может работать в двух режимах: приема и передачи.

Режим передачи. По внутрипроцессорной магистрали 21 через порт 34 в регистр 29 происходит запись адреса модуля, принимающего данные. Запись слова данных осуществляется через порт 33 в регистр 31 по управляющему сигналу от порта 26 управления, этот же сигнал поступает на первый вход блока 27 управления, на второй и третий входы которого поступают соответственно сигнал с шины 6 готовности и тактовые импульсы с шины 5.

С шины 4 адреса источников поступают на первый вход компаратора 23 для сравнения с адресом модуля от регистра 25, выход которого подключен к второму входу компаратора 23. При совпадении кодов компаратор 23 формирует управляющий сигнал, подаваемый на четвертый вход блока 27 управления. При активных уровнях сигналов на четырех входах блок 27 управления вырабатывает три выходных сигнала: сигнал прерывания работы центрального процессора 17, передаваемый на магистраль 21, и сигналы разрешения выдачи адреса модуля приема и данных соответственно на шины 3 и 2 магистрали 1, поступающие на входы управления третьим состоянием регистров 29 и 31. В результате на магистраль 1 передается адрес, заданный регистром 29 на шине 3, и данные, заданные регистром 31 на шине 2.

Для передачи последующих слов данных через порт 33 из регистра 31 по одному и тому же адресу указанный выше порядок передачи повторяется в очередном цикле изменения выходного кода формирователя 13. При этом в регистре 29 сохраняется прежний адрес модуля приема, а данные в регистре 31 обновляются, что проверяет блок 27 управления по сигналу с выхода порта 26 управления.

Режим приема. Компаратор 24 сравнивает адрес модуля из регистра 25 с адресом приемника от шины 3 межпроцессорной магистрали 1. При совпадении адресов активный уровень поступает на первый вход блока 28 управления приемом, на второй и третий входы которого подаются сигналы соответственно с выхода порта 26 управления и от шины 5 тактовых импульсов.

При наличии активных уровней входных сигналов на первом выходе блока 28 формируется сигнал готовности, поступающий на шину 6, на втором выходе блока 28 формируется сигнал прерывания, передаваемый центральному процессору 17 через внутрипроцессорную магистраль 21, на третьем выходе блока 28 формируется сигнал, по которому происходит запись адреса передающего модуля с шины 4 в регистр 30 и слова данных от шины 2 в регистр 32. Адрес и данные через соответственно порт 34 и порт 33 поступают на внутрипроцессорную магистраль 21 и далее через нее в центральный процессор 17, который обеспечивает чтение и запись адресов, слов данных и управления через блок 18 ввода-вывода в порты 34, 35, 33 и 26 и хранение данных в ЗУ 19.

Перед началом обработки непрерывного потока информации от блока 15. i через магистраль 7 процессорный модуль 16. k устанавливает через порт 35 в регистр 25 адрес модуля 16. k, через порт 34 в регистр 29 адрес компаратора 14, а также через порт 33 в регистр 31 слово управления, содержащее информацию о коммутации блока 15. i и при необходимости о уже скоммутированных источниках. Затем через порт 26 в блок 27 управления поступает сигнал управления передачей.

При формировании на шине 4 адреса модуля 16. k на выходе компаратора 23 появляется активный уровень, по совпадению которого с сигналом управления от порта 26 и тактовым импульсом с шины 5 блок 27 формирует сигнал разрешения передачи адреса коммутатора 14 из регистра 29 и слова управления из регистра 31 на шины соответственно 3 и 2. Компаратор 45 коммутатора 14 сравнивает адрес на шине 3 с кодом задатчика 46 адреса и при их совпадении формирует на своем выходе активный уровень, который при совпадении с тактовым импульсом и активным уровнем сигнала готовности на входах элемента И 42 управляет записью слова управления в регистр 43 (фиг. 9).

Слово управления состоит из М поразрядных групп, каждая из которых определяет адрес источника для одного из модулей 16.1, . . . , 16. М, поэтому для коммутации источника 15. i с процессорным модулем 16. k необходимо в k-ю группу слова управления записать адрес i-го источника. Например, при 16-разрядной шине 2 данных возможна коммутация восьми источников на пять процессорных модулей (L = 8, M = 5), а слово управления содержит в этом случае пять поразрядных групп по три разряда в каждой (один разряд избыточный), или коммутация шестнадцати источников на четыре процессорных модуля (L = 16, M = 4), при этом слово управления содержит четыре группы по четыре разряда в каждой.

Соответствующие группы кодов слова управления поступают на первые входы компараторов 44.1, . . . , 44. М, на вторые входы которых поступает код адреса источника с шины 10. При совпадении кодов компаратор 44. k формирует на k-й линии шины 9 строб записи данных.

Стробируемые данные от источника информации поступают в блок 15. i связи с источником и заносятся в регистр 50 (фиг. 10), после чего на управляющем выходе регистра 50 формируется сигнал наличия данных. Компаратор 47 сравнивает код от задатчика 48 с кодом адреса на шине 10 и при совпадении кодов выдает активный уровень на первый вход элемента И 49, на второй и третий входы которого поступают соответственно тактовые импульсы и сигнал наличия данных от регистра 50. Сигнал готовности с выхода элемента И 49 разрешает выдачу данных из регистра 50 на шину 8 и поступает на шину 12 готовности.

Таким образом, на входах блока 20 управления доступом к ЗУ модуля 16. k в течение рассматриваемого тактового импульса формируются данные, поступающие от блока 15. i через шину 8, строб записи данных с k-й линии шины 9, тактовый импульс с шины 11 и сигнал готовности с шины 12.

По активным уровням сигналов на шинах 9, 11 и 12 элемент И 54 (фиг. 11) формирует строб записи данных с шины 8 в регистр 52, сигнал подтверждения записи с его управляющего выхода разрешает работу компаратора 51, который сравнивает код, образуемый на магистрали 21 управляющими сигналами в каждом такте работы центрального процессора 17, с кодом задатчика 57, соответствующим отсутствию управляющих сигналов обращения центрального процессора 17 к ЗУ 36. При совпадении кодов компаратор 51 запускает одновибратор 55, который формирует строб записи в ЗУ 36 данных из регистра 52 и одновременно увеличивает на единицу содержимое счетчика 56, выходной код которого соответствует адресу записываемых данных.

Для управления буферизацией данных в ЗУ 36 предназначен порт 53, через который центральный процессор 17 из блока 18 ввода-вывода записывает адрес буфера в счетчик 56 адресов.

Центральный процессор 17 через блок 18 ввода-вывода может обращаться к ЗУ 36 по внутрипроцессорной магистрали 21 для чтения слов и выполнять предварительную обработку и/или пересылку данных другим процессорным модулям по магистрали 1, как это рассмотрено выше. (56) 1. Патент США N 4485439, кл. G 06 F 3/00, опублик. 1984.

2. Патент США N 4223380, кл. G 06 F 15/16, опублик. 1980.

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Устройство для запоминания трассы функционирования многопроцессорных систем | 1990 |

|

SU1737454A1 |

| МНОГОПРОЦЕССОРНАЯ СИСТЕМА ОБРАБОТКИ ДАННЫХ | 1997 |

|

RU2139566C1 |

| Устройство формирования заданного спектра вибрации | 1988 |

|

SU1649342A1 |

| ТРЕХКАНАЛЬНАЯ УПРАВЛЯЮЩАЯ СИСТЕМА | 2007 |

|

RU2333529C1 |

| Система сбора и обработки информации | 1987 |

|

SU1424024A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Автопрокладчик пути судна на карте | 1989 |

|

SU1716554A1 |

| Устройство для сопряжения двух процессоров | 1990 |

|

SU1762309A1 |

| Микропроцессорная вычислительная система | 1975 |

|

SU674025A1 |

Изобретение относится к устройствам ввода и обработки измерительной информации, получаемой при натурных испытаниях сложных технических систем, и может быть использовано для связи источников непрерывных потоков информации с ЭВМ различной архитектуры, например персональными ЭВМ, миниЭВМ и др. С целью повышения быстродействия при обработке непрерывных потоков информации, поступающих от нескольких источников, в систему, содержащую процессорные модули, объединенные межпроцессорной магистралью, введены коммутатор источников, информационная магистраль, блоки связи с источниками, формирователь адреса и приоритета источников и дополнительные процессорные модули. Формирователь адреса и приоритета источников обеспечивает формирование тактовых импульсов, а также последовательности адресов источников на межпроцессорной и информационной магистралях. Процессорный модуль, на который от информационной магистрали должен поступать непрерывный поток информации, загружает по межпроцессорной магистрали в коммутатор источников слово, обеспечивающее коммутацию источника через блок связи с источником на данный модуль, и при необходимости пересылает это слово другим процессорным модулям или одному из них для того, чтобы учесть при загрузке коммутацию других источников. 6 з. п. ф-лы, 13 ил.

Авторы

Даты

1994-01-30—Публикация

1991-03-11—Подача