Изобретение относится к вычислительной технике к может быть использовано ) системах согласованной фильтпации связи, спектроана- лизаторах гидре-акустике и радиолокации.

Цель изобретения - п вычение точности масштабирования.

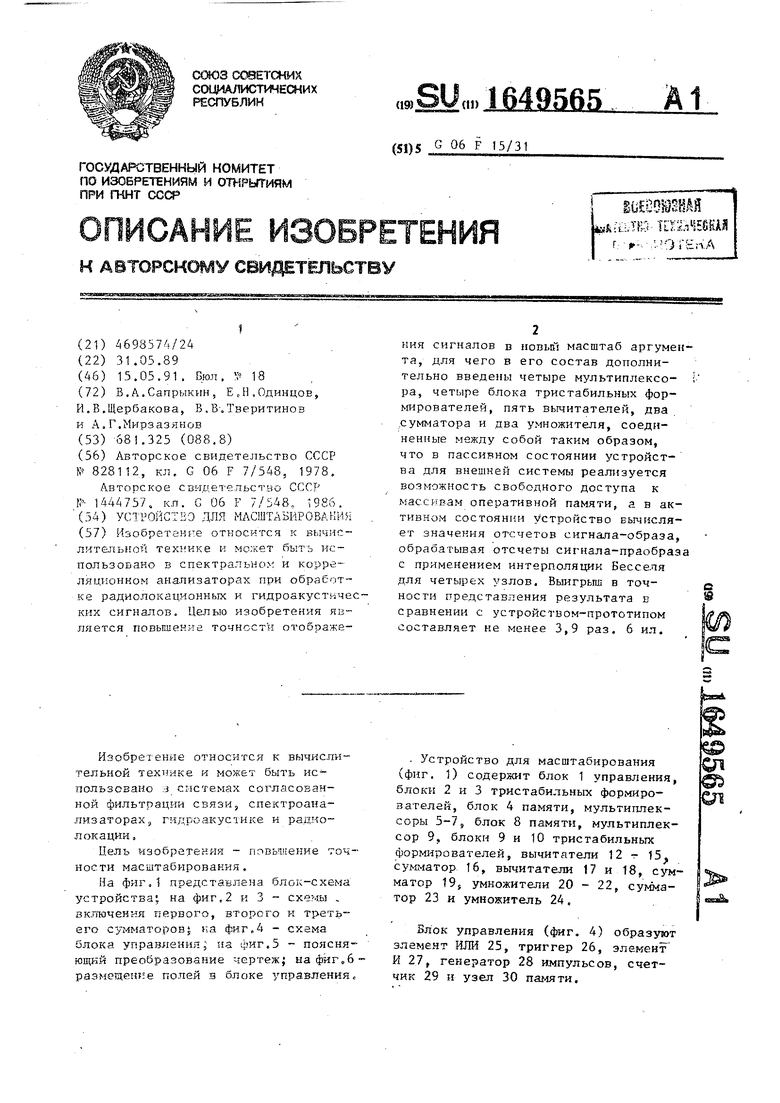

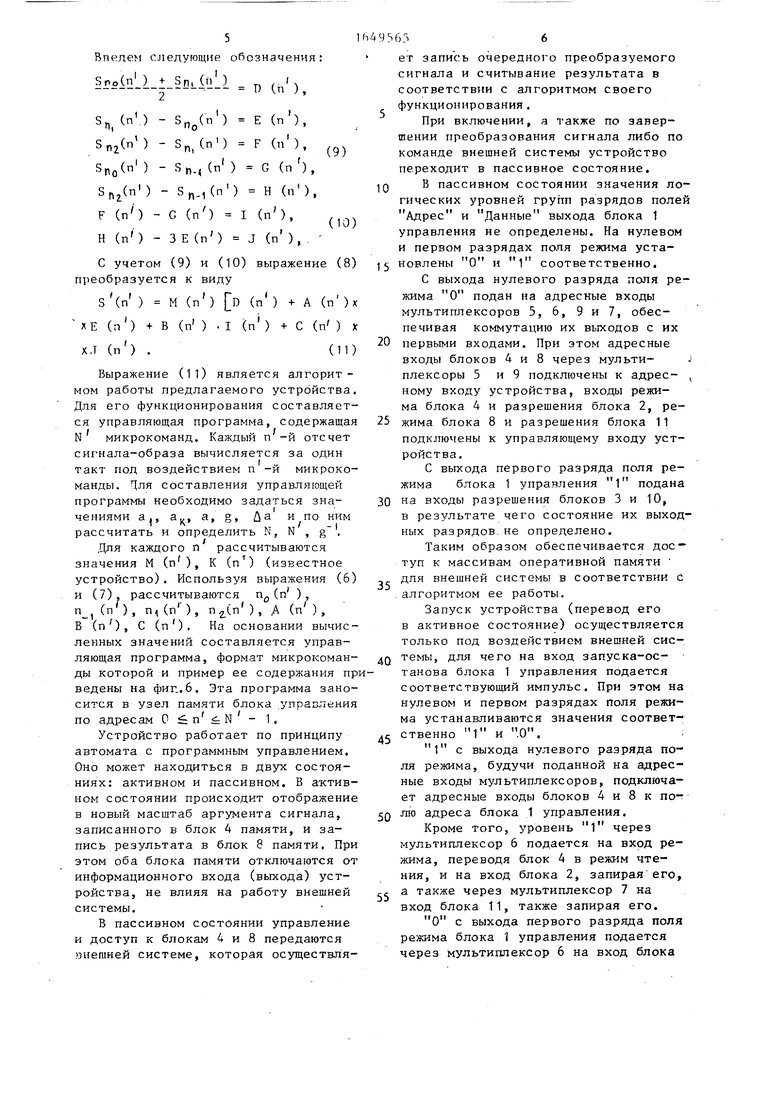

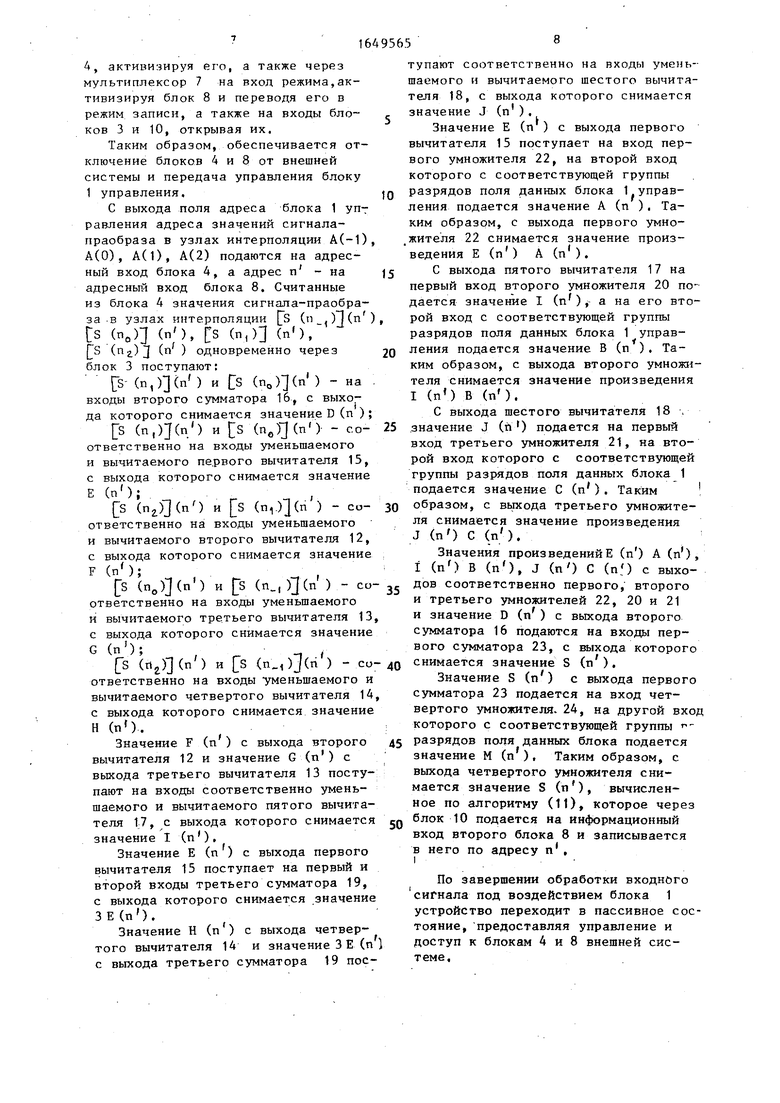

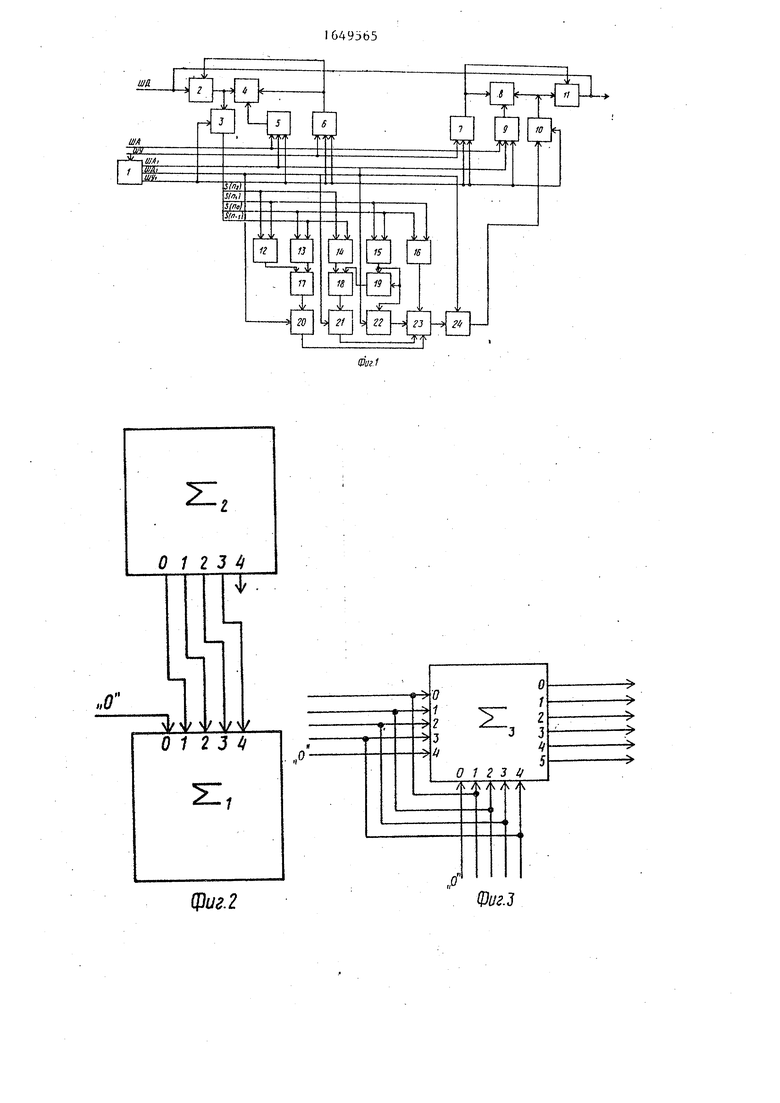

На фиг.1 лредстаьлена блок-схема устройства; на фиг,2 и 3 - схемы , включения первого, второго и третьего сумматоровj ьа фиг.4 - схема блока управления, на (,иг„5 - поясняющий преобразование чертеж; нафиг.,6- размецение полей з блоке управления.

. Устройство для масштабирования (фиг. 1) содержит блок 1 управления, блоки 2 и 3 тристабильных формирователей, блок 4 памяти, мультиплексоры 5-7, блок 8 памяти, мультиплексор 9, блоки 9 и 10 тристабильных формирователей, вычитатели 12 - 15, сумматор 16, вычитатели 17 и 18, сумматор 19, умножители 20 - 22, сумматор 23 и умножитель 24.

Блок управления (фиг. 4) образуют элемент ИЛИ 25, триггер 26, элемент И 27, генератор 28 импульсов, счетчик 29 и узел 30 памяти.

J16495654

Принцип действия известного уст- лки . л v . л с-,-

U У У t+1 U У. , Ч-5У

роиства основан на том, что отсчеты

результата масштабирования (сигнала- причем

образа) S (п ) вычисляются по алго- , h „ v .

э п - х х -,

ритму, (4)

S (п ) М (п( ) S (п ), .t

где М (п ) - функция уравнивания

энергии,jo Фиг.5 поясняет значения символов

О . da

2fUtT alX 1 Х° Xlt Хг С h

М (п ) ---«---- ;Применительно к дискретному представлению сигналов установим следующие соответствия между номерами отS (п ) - значение сигнала-праоб- 15 счетов сигнала-праобраза п и номе- раза, соответствующеерами узлов интерполяции i при выn -му отсчету сигнала-числении п -го отсчета сигнала-обра-образца, вычисляемое по-эа посредством интерполяции Бесселя:

средством линейной ин-„. „ . /

л - II ll J t

терполяции20(

S (n )K(n )sn((n ) -У ,(П) (5)

, -t ,t К (n ). - ) + Sno (n1),

Очевидно, что h Да. Тогда ок

где п (п ) 25зываются справедливыми соотношения

и п° (п1) - номера отсчетов сиг-Гг -i (a + „ а )-}

нала-праобраза соответ-n 0 vn - 11 г-М

йа

ственно в нулевом и

первом узлах интерпо- п-( (п ) п 0 (п ) - 1,

(6)

ляции по Лагранжу. 3Qn , (п1) п0 (п ) + 1, В устройстве S (п ) вычисляется

как интерполяционный многочлен Бессе-n2(n)nQ(n)+2s

ля для четырех узлов интерполяции. .

Он описывается выражениемгДе ({) оператор вычисления

целой части.

Р (х + ht) +Введем следующие обозначения:

п , ,(t - 0,5) К (п ) - 0,5 А(п ),

(t - 0.5) . t(t - 1) ( .l , J

+ + --- х (1)t( Kf((n) в (п,}

, (Лгу «+йгуо) Д32 -t(t-1)(t-0±5) 40

кi r i -+-Ј-L.,t() ()

6

ГД6 , у о l°.:f- 5(nl)lK(nl).z Oi5lCK(

гУ1 Уг. У , (2) 456

Ув Уг 2У| + С (п1). (7)

ЛгУ( У , - 2у0 + у.,,

Д3 у., у г - Зу t -y i+3y0,Поскольку Р (х + ht) S (n1 ), то с

y(i) f(x-) - значение функцииучетом (1), (2), (5) и (7) имеем

в i-м узле интер-. . Гч /п %+с „ (п ч

поляции S (п1 ) М (п ) - +

Л,Л ,Л - конечные разности/г t ,

соответственно+ А (п ) (п ) - 8„о(п )J +

первого, второго+ в (nf} . (n } g (ni j-|

и третьего поряд-r u 2 n J

55 Sn/п1) - S.Cn ) +

Соотношения (2) получены из общего+ с (п ) . (п1 ) - S, (n1 )1 - 3 , - Sn0(

соотношения

г-

- 1,

йа

+ 1,

5

Впедем следующие обозначения;

Sp0(n ) + Sn, (ч )

2

D (п ),

п,

(п ) W

I,

n2v

i(n )

nz

- sn.(n )

(n ), I

E

F (n ), f.

(9)

S(n )

(10)

Sn. (n1 ) G (n ), Sn.n ) H (n1), F (n ) - G (n ) I (n ), H (n ) - 3E(n ) J (n ),

С учетом (9) и (10) выражение (8) реобразуется к виду

s (n ) М (n ) D (n ) + А (п )х

(п ) + (п ) .

В (п1 ) - I (п1 )

+ С (п ) X

(11)

Выражение (11) является алгоритмом работы предлагаемого устройства. Для его функционирования составляется управляющая программа, содержащая

N

микрокоманд.

Каждый п -и отсчет

сигнала-образа вычисляется за один

г „

такт под воздействием n -и микрокоманды. Для составления управляющей

программы необходимо задаться зна. i чениями а., а„, a, g, Да и по ним

рассчитать и определить N, N , .

Для каждого n рассчитываются значения М (п ), К (пт) (известное устройство). Используя выражения (6) и (7), рассчитываются n0 (n ), n, (n )t n, (r/), nz(n ), А (п ) , В (п ), С (п(). На основании вычисленных значений составляется управляющая программа, формат микрокоманды которой и пример ее содержания прведены на фиг..6. Эта программа заносится в узел памяти блока управления по адресам 0 : п N - 1 .

Устройство работает по принципу автомата с программным управлением. Оно может находиться в двух состояниях: активном и пассивном. В активном состоянии происходит отображение в новый масштаб аргумента сигнала, записанного в блок 4 памяти, и запись результата в блок 8 памяти. При этом оба блока памяти отключаются от информационного входа (выхода) устройства, не влияя на работу внешней системы.

В пассивном состоянии управление и доступ к блокам 4 и 8 передаются внешней системе, которая осуществля49Sb36

ег запись очередного преобразуемого сигнала и считывание результата в соответствии с алгоритмом своего функционирования.

При включении, а также по завершении преобразования сигнала либо по команде внешней системы устройство переходит в пассивное состояние. 1Q В пассивном состоянии значения логических уровней групп разрядов полей Адрес и Данные выхода блока 1 управления не определены. На нулевом

и первом разрядах поля режима уста- 0

ft It

0

5 новлены и и 1 соответственно.

С выхода нулевого разряда поля режима О подан на адресные входы мультиплексоров 5, 6, 9 и 7, обеспечивая коммутацию их выходов с их

0 первыми входами. При этом адресные входы блоков 4 и 8 через мультиплексоры 5 и 9 подключены к адрес- ( ному входу устройства, входы режима блока 4 и разрешения блока 2, ре5 жима блока 8 и разрешения блока 11 подключены к управляющему входу устройства.

С выхода первого разряда поля режима блока 1 управления 1 подана на входы разрешения блоков 3 и 10, в результате чего состояние их выходных разрядов не определено.

Таким образом обеспечивается доступ к массивам оперативной памяти для внешней системы в соответствии с алгоритмом ее работы.

Запуск устройства (перевод его в активное состояние) осуществляется только под воздействием внешней системы, для чего на вход запуска-останова блока 1 управления подается соответствующий импульс. При этом на нулевом и первом разрядах поля режима устанавливаются значения соответственно 1 и О.

1 с выхода нулевого разряда поля режима, будучи поданной на адресные входы мультиплексоров, подключает адресные входы блоков 4 и 8 к полю адреса блока 1 управления.

Кроме того, уровень 1 через мультиплексор 6 подается на вход режима, переводя блок 4 в режим чтения, и на вход блока 2, запирая его, а также через мультиплексор 7 на вход блока 11, также запирая его.

О с выхода первого разряда поля режима блока 1 управления подается через мультиплексор 6 на вход блока

5

0

5

0

5

4, активизируя его, а также через мультиплексор 7 на вход режима,активизируя блок 8 и переводя его в режим записи, а также на входы блоков 3 и 10, открывая их.

Таким образом, обеспечивается отключение блоков 4 и 8 от внешней системы и передача управления блоку 1 управления.

С выхода поля адреса блока 1 управления адреса значений сигнала- праобраза в узлах интерполяции А(-1), А(0), А(1), А(2) подаются на адресный вход блока 4, а адрес п - на адресный вход блока 8. Считанные из блока 4 значения сигнала-праобра- за в узлах интерполяции р5 (п . )|(п ), fS Ю (n ), S (n() (n ), ЈS (пг)Д (n ) одновременно через блок 3 поступают:

S (n,)(n ) и ЈS (n0)(n) - на входы второго сумматора 16, с выхода которого снимается значение D(п ) ;

S (n,)J(n() и S (neTJ(n() - со- ответственно на входы уменьшаемого и вычитаемого первого вычитателя 15, с выхода которого снимается значение Е Сп );,

S (пг)(п ) и S (n,)(n ) - со- ответственно на входы уменьшаемого и вычитаемого второго вычитателя 12, с выхода которого снимается значение F (п )5 .. .

тупают соответственно на входы уменьшаемого и вычитаемого шестого вычитателя 18, с выхода которого снимается значение J (п1 ).

Значение Е (п ) с выхода первого вычитателя 15 поступает на вход первого умножителя 22, на второй вход которого с соответствующей группы

JQ разрядов поля данных блока 1 управления подается значение А (п ). Таким образом, с выхода первого умно- жителя 22 снимается значение произведения Е (п ) А (п().

15 С выхода пятого вычитателя 17 на первый вход второго умножителя 20 подается значение I (п ), а на его второй вход с соответствующей группы разрядов поля данных блока 1 управления подается значение В (п ). Таким образом, с выхода второго умножителя снимается значение произведения I (п ) В (nf).

С выхода шестого вычитателя 18 , значение J (ft ) подается на первый вход третьего умножителя 21, на второй вход которого с соответствующей группы разрядов поля данных блока 1 подается значение С (п ) . Таким

30 образом, с выхода третьего умножителя снимается значение произведения J (п ) С (п ).

Значения произ ведений Е (п ) А (п(), I (nf) В (n ), J (n ) С () с выхо20

25

Јs (n0)J(n() и jj3 (п,Г|(п ) - со- 35 Дов соответственно первого, второго

и третьего умножителей 22, 20 и 21 и значение D (п ) с выхода второго сумматора 16 подаются на входы первого сумматора 23, с выхода которого снимается значение S (n ).

ответственно на входы уменьшаемого и вычитаемого третьего вычитателя 13, с выхода которого снимается значение G (п1);

S (rtej(n ) и S (n,)J(n ) - соответственно на входы уменьшаемого и вычитаемого четвертого вычитателя 14, с выхода которого снимается значение Н (пг).

Значение F (п ) с выхода второго вычитателя 12 и значение G (п) с выхода третьего вычитателя 13 поступают на входы соответственно уменьшаемого и вычитаемого пятого вычитателя 17, с выхода которого снимается значение I (п ).

Значение Е (п ) с выхода первого вычитателя 15 поступает на первый и второй входы третьего сумматора 19, с выхода которого снимается значение ЗЕ(п ).

Значение Н (п ) с выхода четвертого вычитателя 14 и значение 3Е (п ) с выхода третьего сумматора 19 пос40

45

50

Значение S (п ) с выхода первого сумматора 23 подается на вход четвертого умножителя. 24, на другой вход которого с соответствующей группы - разрядов поля данных блока подается значение М (п ), Таким образом, с выхода четвертого умножителя снимается значение S (nf), вычисленное по алгоритму (11), которое через блок 10 подается на информационный вход второго блока 8 и записывается в него по адресу п .

По завершении обработки входного сигнала под воздействием блока 1 устройство переходит в пассивное состояние, предоставляя управление и доступ к блокам 4 и 8 внешней системе.

тупают соответственно на входы уменьшаемого и вычитаемого шестого вычитателя 18, с выхода которого снимается значение J (п1 ).

Значение Е (п ) с выхода первого вычитателя 15 поступает на вход первого умножителя 22, на второй вход которого с соответствующей группы

Q разрядов поля данных блока 1 управления подается значение А (п ). Таким образом, с выхода первого умно- жителя 22 снимается значение произведения Е (п ) А (п().

5 С выхода пятого вычитателя 17 на первый вход второго умножителя 20 подается значение I (п ), а на его второй вход с соответствующей группы разрядов поля данных блока 1 управления подается значение В (п ). Таким образом, с выхода второго умножителя снимается значение произведения I (п ) В (nf).

С выхода шестого вычитателя 18 , значение J (ft ) подается на первый вход третьего умножителя 21, на второй вход которого с соответствующей группы разрядов поля данных блока 1 подается значение С (п ) . Таким

30 образом, с выхода третьего умножителя снимается значение произведения J (п ) С (п ).

Значения произ ведений Е (п ) А (п(), I (nf) В (n ), J (n ) С () с выхо0

5

35 Дов соответственно первого, второго

и третьего умножителей 22, 20 и 21 и значение D (п ) с выхода второго сумматора 16 подаются на входы первого сумматора 23, с выхода которого снимается значение S (n ).

0

5

0

Значение S (п ) с выхода первого сумматора 23 подается на вход четвертого умножителя. 24, на другой вход которого с соответствующей группы - разрядов поля данных блока подается значение М (п ), Таким образом, с выхода четвертого умножителя снимается значение S (nf), вычисленное по алгоритму (11), которое через блок 10 подается на информационный вход второго блока 8 и записывается в него по адресу п .

По завершении обработки входного сигнала под воздействием блока 1 устройство переходит в пассивное состояние, предоставляя управление и доступ к блокам 4 и 8 внешней системе.

Ф о р м у 1 а и т о б р е т е н и я

Устройство для масштабирования, содержащее два блока памяти, дна умножителя, первый сумматор, блок управления и первый вычитатель, причем выход первого вычитателя соединен с входом первого сомножителя первого умножителя, выход которого соединен с входом первого слагаемого первого сумматора, вход второго слагаемого которого соединен с выходом второго умножителя, вход первого сомножителя которого соединен с выходом поля данных блока управления и входом второго сомножителя первого умножителя, отличающееся тем, что, с целью повышения точности в него введены четыре мультиплексора, с второго по шестой вычитатели, третий и четвертый умножители,второй и третий сумматоры, четыре блока три стабильных формирователей, причем входы разрядов данных устройства соединены с информационными входами, первого блока тристабильных формирователей, выходы которого соединены с информационными входами второго блока тристабильных формирователей, информационными входами и информационными выходами соответствующих разрядов первого блока памяти, адресный вход которого соединен с выходом первого мультиплексора, вход выбора режима первого блока памяти соединен с входами разрешения выдачи первого блока тристабильных формирователей и выходом второго мульти плгксора, выходы третьего блока три- стабильных формирователей соединены с информационными входами четвертого блока тристабильных формирователей и информационными входами и информационными выходами соответствующих разрядов второго блока памяти, адресный вход которого соединен с выходом третьего мультиплексора, вход выбора режима второго блока памяти соединен с выходом четвертого мультиплексора и входами разрешения выдачи четвертого блока тристабильных формирователей, выходы которого соединены с информационными входами первого блок тристабильных формирователей и выходом устройства, входы уменьшаемого и вычитаемого второго вычитателя и входы уменьшаемого и вычитаемого

0

5

0

5

0

5

0

5

0

5

третьего вычитатечя соединены г выходами соответственно е первой по четвертую групп второго бпока тристабильных формирователей, входы уменьшаемого и вычитаемого четвертого вычитателя и входы уменьшаемого и вычитаемого первого вычитателя соединены соответственно с выходами первой, четвертой, третьей н второй групп второго блока тристабильных элементов, входы первого и второго слагаемых второго сумматора соединены соответственно с выходами третьей и второй групп второго блока тристабильных формирователей, выходы второго и третьего вычнтателей соединены с входами соответственно уменьшаемого и вычитаемого пятого вычитателя, выход которого соединен с входом второго сомножителя второго умножителя, выходы четвертого вычитателя и третьего сумматора соединены с входами соответственно уменьшаемого и вычитаемого шестого вычитателя, выход которого соединен с входом первого сомножителя третьего умножителя, выход которого соединен с входом третьего слагаемого первого сумматора, вход четвертого слагаемого и выход которого соединены соответственно с выходом второго сумматора и входом первого сомножителя четвертого умножителя, выходы разрядов которого соединены с информационными входами третьего блока тристабильных формирователей, выход поля данных блока управления соединен с вхо- дами вторых сомножителей третьего и четвертого умножителей, выход поля адресов блока управления соединен с первыми информационными входами первого и третьего мультиплексоров, вторые информационные входы которых соединены с входом адресов устройства, вход управления которого соеди- . нен с входом запуска-останова блока управления и вторыми информационными входами второго и четвертого мультиплексоров, первые информационные входы которых соединены с выходом поля признаков режима блока управления, адресными входами с первс- го по четвертый мультиплексоров и входами разрешения выдачи второго и четвертого блоков тристабильных формирователей.

фиг. 2

te.j

Фаг. 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Устройство для быстрого преобразования Фурье | 1986 |

|

SU1392577A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1608740A1 |

| Преобразователь координат | 1990 |

|

SU1742816A2 |

| Устройство для преобразования декартовых координат | 1984 |

|

SU1206777A1 |

| Вычислительное устройство для поворота вектора | 1987 |

|

SU1520511A1 |

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1988 |

|

SU1541663A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Цифровой фазовый детектор | 1986 |

|

SU1467785A1 |

| Устройство обнаружения и определения координат объекта на изображении | 1990 |

|

SU1737755A1 |

Изобретайте относится к вычислительной технике и мс,кет быт о использовано в спектральном и корреляционном анализаторах при обраСот- ке радиолокационных и гидроакустических сигналов. Целью изобретения является повышение точности отображения сигналов в новый масштаб аргумента, для чего в его состав дополнительно введены четыре мультиплексо- i pa, четыре блока тристабильных формирователей, пять вьгчитателей, два сумматора и два умножителя, соединенные между собой таким образом, что в пассивном состоянии устройства для внешней системы реализуется возможность свободного доступа к маео вам оперативной памяти, а в активном состоянии устройство вычисляет значения отсчетов сигнала-образа, обрабатывая отсчеты сигнала-праобраэа с применением интерполяции Бессепя для четырех узлов. Выигрыш в точности предетавления результата в сравнении с устройством-прототипом составляет не менее 3,9 раз. 6 ил. /Г Чзяв

Составитель А.Зорин - Редактор А.Огар Техред М.Моргентал

Фиг. 6

Корректор Н.Король

| Дискретный фазометр | 1979 |

|

SU828112A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Авторское сви0е10льство CCCTJ № 144475/ | |||

| кп | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-05-15—Публикация

1989-05-31—Подача