Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых вычислительных системах

Цель изобретения - повышение достоверности шифратора,,

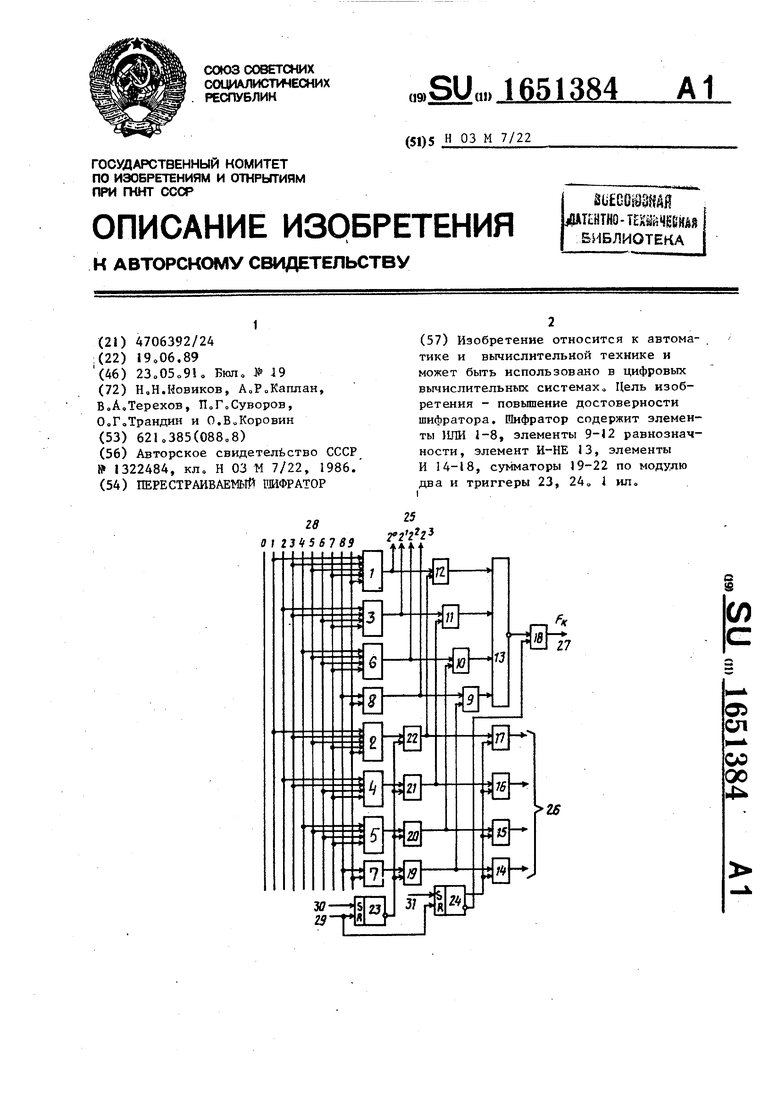

На чертеже изображена функциональная схема шифраторас

Перестраиваемый шифратор содержит элементы ИЛИ 4-8, элементы 9-12 равнозначности, элемент И-НЕ 13, элементы И 14-J8, сумматоры 19-22 по модулю два, триггеры 23 и 24, первую и вторую группы 25 и 26 информационных вы- ходов, контрольный выход 27, информационные и управляющие входы 28-34 о Шифратор работает следующим образом.

В зависимости от комбинации управ- ляющих сигналов на соответствующих входах шифратора возможны три режима работы; одноканальный5 двухканальный, тестовый (режим самопроверки). j Рассмотрим работу в одноканальном режиме. Сигналом управленияfэквивас лентным логической единице, по входу 29 триггеры 23 и 24 устанавливаются в исходное состояние о Затем сигналом управления, эквивалентным логической единице, по входу 30 триггер 23 переводится в единичное состояние,, Шифратор подготовлен для работы в первом режиме„

Пусть теперь, к примеру, на вход шифратора поступил сигнал, соответствующий двоичному коду 0004, в этом случае через элементы ИЛИ 4 и 2 на соответствующий выход в первой группе 25 информационных выходов, на вход элемента J 2 равнозначности и на вход сумматора 22 по модулю два поступит сигнал логической единицы,, На другой вход сумматора 22 поступает сигнал логического нуля с инверс- ного выхода триггера 23, находящегог ся в единичном состоянии, С выхода сумматора 22 по модулю два сигнал логической единицы поступает на соответствующий вход элемента 12 равнозначности и на один из входов элемента И 17, который закрыт по другому входу нулевым потенциалом с прямого выхода триггера 24. Так как на входах элемента 12 равнозначности присутствуют одинаковые сигналы, то на вход элемента И-НЕ 13 поступает сигнал логической единицы с выхода элемента 12 равнозначности. На дру

5

5

0

0

5

0

5

0

5

гие входы элемента И-НЕ 13 также поступают сигналы совпадения, экви- Iвалентные логической единице, с выходов элементов 9-11 равнозначности, так как на их входах сигналы отсутствуют с В этом случае с выхода элемента И-НЕ 13 снимается сигнал логичес кого нуля, который поступает на вход элемента И 18, предварительно подготовленный к открытию сигналом, снимаемым с инверсного выхода триггера 24. Таким образом, на выходах первой группы 25 формируется код 0001, выходы группы 26 отключены, а на выходе 27 сигнал отсутствует, что свидетельствует об отсутствии неисправности.

Если, например, возникает неисправность в элементах устройства, приводящая к тому, что на элементы 9-12 сравнения поступает различная информация , то с выхода элемента И-НЕ 13 снимается сигнал логической единицы. С выхода элемента И-НЕ 13 сигнал логической единицы проходит через подготовленный к открытию элемент И 4 8 на выход 27, что свидетельствует о наличии неисправности

При работе в двухканальном режиме код снимается как с выходов первой группы 25, так и с выходов второй группы 26о Для перестройки работы шифратора в двухканальный режим на вход 29 подается сигнал логической единицы и устанавливает триггеры 23 и 24 в исходное состояние, затем сигнал по входу 31 шифратора устанавливает в единичное состояние триггер 24, с его прямого выхода сигнал логической единицы поступает на соответствующие входы элементов И 14-17, подготавливая их к открытию. Своим инверсным выходом триггер 24 отключает контрольный выход 27„ Теперь при наличии сигнала на информационных входах 28. как на выходах первой группы 25, так и на выходах второй группы 26 формируется код 0010.

Работа шифратора в режиме самопроверки осуществляется по сигналу Сброс на входе 29 устройства: подготавливается к открытию элемент И 18, отключаются выходы второй группы 26 с инверсного выхода триггера 23, сигнал логической единицы поступает на соответствующие входы сумматоров 19-22 по модулю два Так как на входах 28 сигнал отсутствует, то с выходов сумматоров 19-22 по

516

модулю дяа ня входы элементов 9-12 равнозначности поступает сигнал, инверсный входному, т„е„ эквивалентный логической единице

В результате на выходе 27 ожидается сигнал логической единицы, который свидетельствует о исправной работе сумматоров 19-22 по модулю два, элементов 9-12 равнозначности, триггера 23.

Таким образом, по сравнению с прототипом обеспечивается повышение достоверности работы шифратора за счет увеличения кратности обнаруживаемых ошибок и сокращение времени обнаружения неисправности за счет работы в реальном масштабе времени

Формула изобретения

Перестраиваемый шифратор, содержащий первый элемент ИЛИ, первый вход которого соединен с первым входом второго элемента ИЛИ и является первым информационным входом шифратора, третий элемент ИЛИ, первый вход кото- iporo является вторым информационным входом шифратора, четвертый элемент ИЛИ, первый вход которого соединен с вторым входом второго элемента ИЛИ и является третьим информационным входом шифратора, пятый элемент ИЛИ, вход которого является четвертым информационным входом шиф- ратора, шестой элемент ИЛИ у первый вход которого соединен с-вторым входом первого элемента ИЛИ-и является пятым информационным входом шифратора, вторые входы третьего и шестого элементов ИЛИ объединены и являются шестым информационным входом шифра- тора, второй вход четвертого элемента ИЛИ и третий вход шестого элемента ИЛИ объединены и являются седьмым информационным входом шифратора, седьмой элемент ИЛИ, выход которого соединен с первым входом первого сумматора по модулю два и восьмой элемент ИЛИ, выход которого является первым выходом первой группы информационных выходов шифратора, отличающийся тем, что, с целью повышения достоверности шифратора, в него введены второй, третий и четвертый сумматоры по модулю два, триггеры, элементы равнозначности, элемент И-НЕ и элементы И, выходы пятого, четвертого и второго элемен-

3846

тов ИЛИ соединены с первыми входами соответственно второго, третьего и четвертого сумматоров по модулю два, инверсный выход первого триггера соединен с вторыми входами пеового-чет- вертого сумматоров по модулю два, выходы которых соединены с первыми входами одноименных элементов И и с

Q первыми входами одноименных элементов равнозначности, выходы которых соединены с соответствующими входами элемента И-НЕ, выход которого соединен с первым входом пятого элемента

5 И, выход которого является контрольным выходом шифратора, инверсный и прямой выходы второго триггера соединены соответственно с вторым входом пятого элемента И н с вторыми входа0 ми первог) - четвертого элементов И, выходы которых являются соответствующими выходами второй группы информационных выходов шифратора, второй вход первого элемента равнозначности

5 подключен к выходу восьмого элемента ИЛИ, выходы шестого, третьего и первого элементов ИЛИ соединены с вторыми входами соответственно второго, третьего и четвертого элементов рав0 нозначности и являются соответствующими вторыми выходами первой группы информационных выходов шифратора, первый вход седьмого элемента ИЛИ соединен с первым входом восьмого эле,. мента ИЛИ и является восьмым входом шифратора, вторые входы седьмого и восьмого элементов ИЛИ объединены с третьими входами первого и второго элементов ИЛИ и являются девятым вхо0 дом шифратора, четвертый вход первого элемента ИЛИ, третий вход третьего элемента ИЛИ, четвертый вход второго элемента ИЛИ, и второй вход пятого элемента ИЛИ подключены к третье5 МУ входу шестого элемента ИЛИ, пятый вход первого элемента ИЛИ и четвертый вход третьего элемента ИЛИ подключены к первому входу четвертого элемента ИЛИ, четвертый вход шестого

0 элемента ИЛИ подключен к первому входу пятого элемента ИЛИ, пятый вход второго элемента ИЛИ и третий вход пятого элемента ИЛИ подключены к первому входу шестого элемента ИЛИ, тре5 тий вход четвертого элемента ИЛИ подключен к первому входу третьего элемента ИЛИ, четвертые входы четвертого и пятого элементов ИЛИ подключены к второму входу шестого элемента ИЛИ,

716513848

R-рходы первого и второго триггеров первого и второго триггеров являются объединены и являются первым управ- соответственно вторым и третьим - ляющим входом шифратора, S-входы управляющими входами шифратора„

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство аналого-цифрового преобразования с самоконтролем | 1989 |

|

SU1695498A1 |

| Самодиагностируемый шифратор | 1986 |

|

SU1322484A1 |

| Устройство для обслуживания сообщений | 1983 |

|

SU1128256A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство для функционального контроля вычислительных машин | 1983 |

|

SU1134943A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для ввода информации с перфокарт | 1984 |

|

SU1246086A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Устройство для контроля средств числового программного управления | 1988 |

|

SU1675852A1 |

| Устройство для распознавания функциональной полноты систем логических функций | 1979 |

|

SU960795A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых вычислительных системах,, Цель изобретения - повышение достоверности шифратора. Шифратор содержит элементы ИЛИ 1-8, элементы 9-12 равнозначности, элемент И-НЕ 13, элементы И 14-18, сумматоры 19-22 по модулю два и триггеры 23, 24„ I ил (Л О5 СП со 00 4

| Самодиагностируемый шифратор | 1986 |

|

SU1322484A1 |

Авторы

Даты

1991-05-23—Публикация

1989-06-19—Подача