регистра соединены с первыми входами шестой группы элементов. И, выходы которых соединены со вторыми входами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параметров | 1984 |

|

SU1244677A1 |

| Устройство для контроля дискретных систем | 1983 |

|

SU1117640A1 |

| Устройство для контроля блоков управления | 1984 |

|

SU1242962A1 |

| Устройство для кодирования | 1985 |

|

SU1287294A1 |

| Устройство для контроля хода программ | 1988 |

|

SU1617442A1 |

| Устройство для обнаружения и исправления ошибок | 1985 |

|

SU1368995A1 |

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

| Устройство для реализации логических функций | 1981 |

|

SU1164724A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство для мажоритарного выбора сигналов | 1989 |

|

SU1656539A1 |

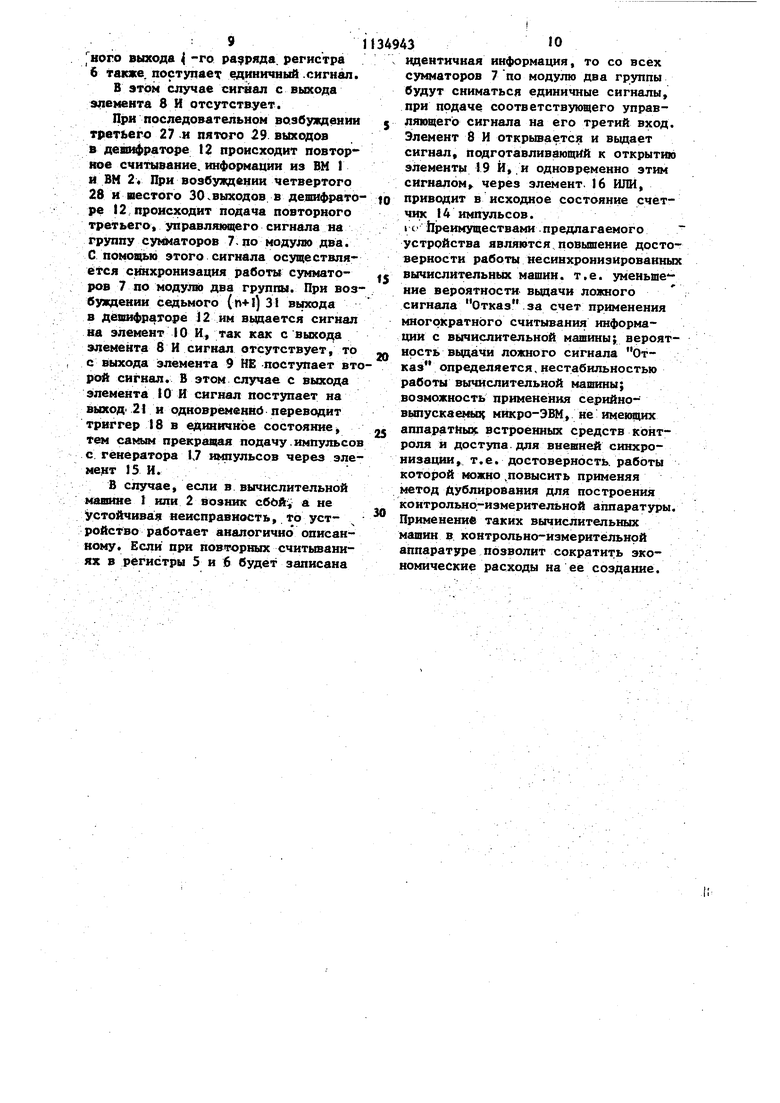

УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНОГО КОНТРОЛЯ ВЫЧИСЛИТЕЛЬНЫХ МАШИН, содержащее группу сумматоров по модулю два счетчик импульсов, генератор импульсов., триггер, п1вреключатель, отличающееся тем, ЧТО, с целью повьшения достоверности работы, оно дополнительно содержит : первую и вторую группы элементов И третий,, четвертый и пятый элементы И, шестую группу элементов И, элементы НЕ, первый,.второй и третий элементы ИЛИ, дешифратор, первый и второй регистры, причем информационные . выходы первой вычислительной машины подключены ко вторым входам первой группы элементов И, а информационные выходы второй вычислительной машины ко вторым входан второй группы элементов И, первые вхбды первой и второй групп .элементов И соединены с выходом первого элемента ИЛИ, выходы первой группы элементЬв И подключены к информационным, входам первого регистра, выходы вторсЛ группы элементов И соединены .с информационными входами второго регистра, управляющие входы первого и второго регистров соединены с выходом третьего элемента ИЛИ, прямые и инверсные, выходы первого регистра подключены к первым входам соответствующих сумматоров по модулю два, а прямые и инверсные выходы второго регистра - ко вторым входам группы сумматоров по модулю два,. третьи входы которых подключены к выходу второго элемента ИЛИ, выходы - ко входам третьего элемента И, выход которого подключен ко второму входу шестой группы элементов И, ко второму входу третьего элемента ИЛИ и к элементу НЕ, i выход которого соединен со вторым входом четвертого элемента И, первый вход которого подключен к (п +1) выходу дешифратора, выход четвертого элемента И Соединен с первым выходом устройства и с первым входом триггера, второй вход которого подключен к выходу переключателя, инверсный выход триггера соединен со вторым входом пятого элемента И, первый вход которого, соединён с выходом СО 4ib генератора импульсов, выход пятого элемента И подключен к информаСО 4 :А ционному входу счетчика импульсов, : управлякиций вход которого соединен с. выходом-третьего элемента ИЛИ, первый вход которого подключен к выходу переключателя., выходы счетчи ка импульсов соединены с соответствующими, йходами дешифратора все нечетные выходы которого, начиная с nepieoro до(п -l) , подключены . ко входам первого элемента ИЛИ, а все четные, начиная со второго, до П подключены- ко входа1)- второго элемента ИЛИ, прямые выходы первого

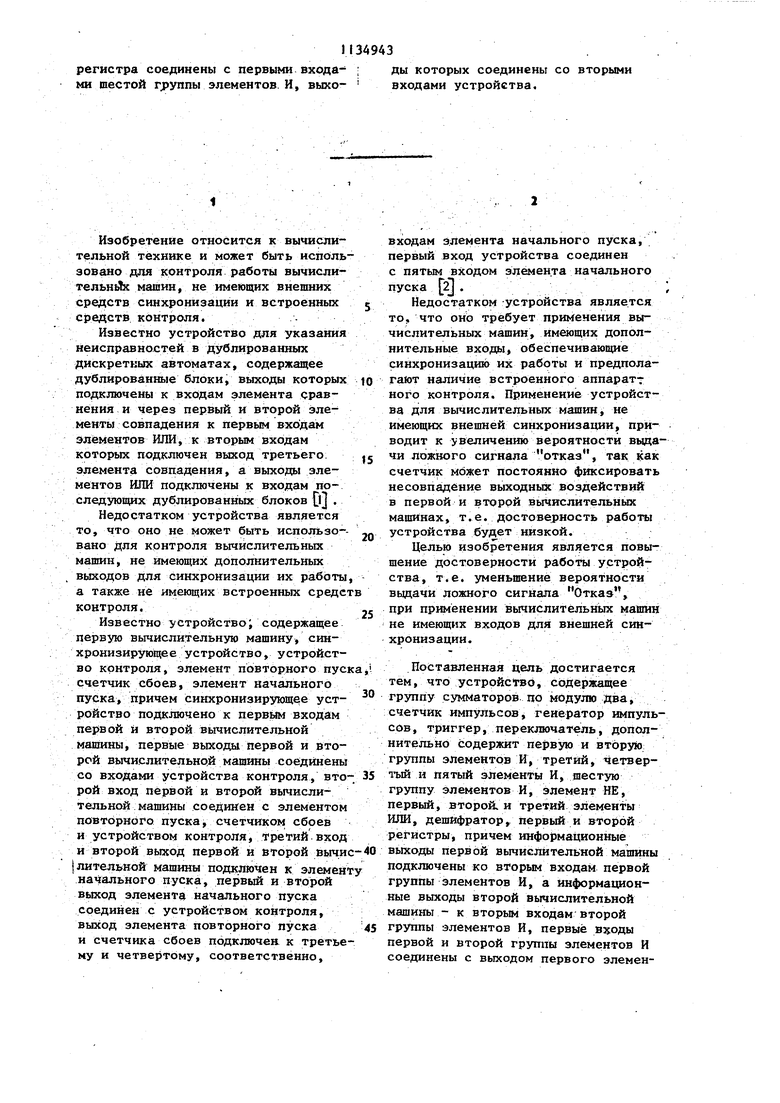

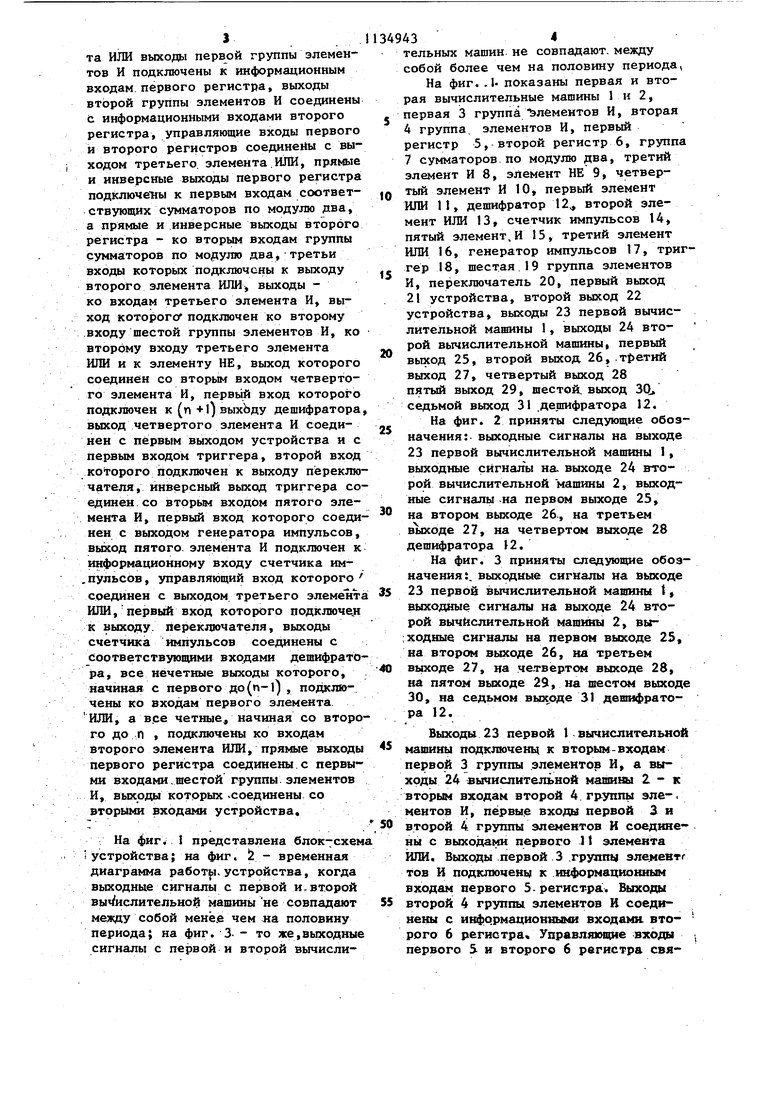

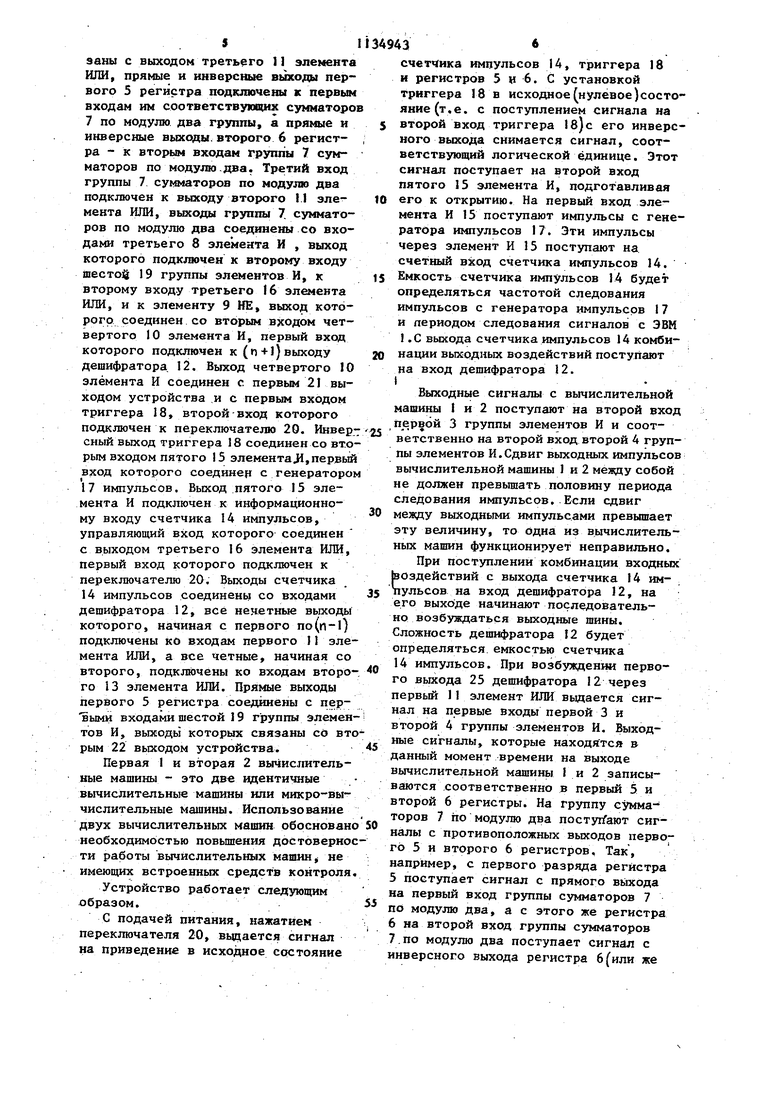

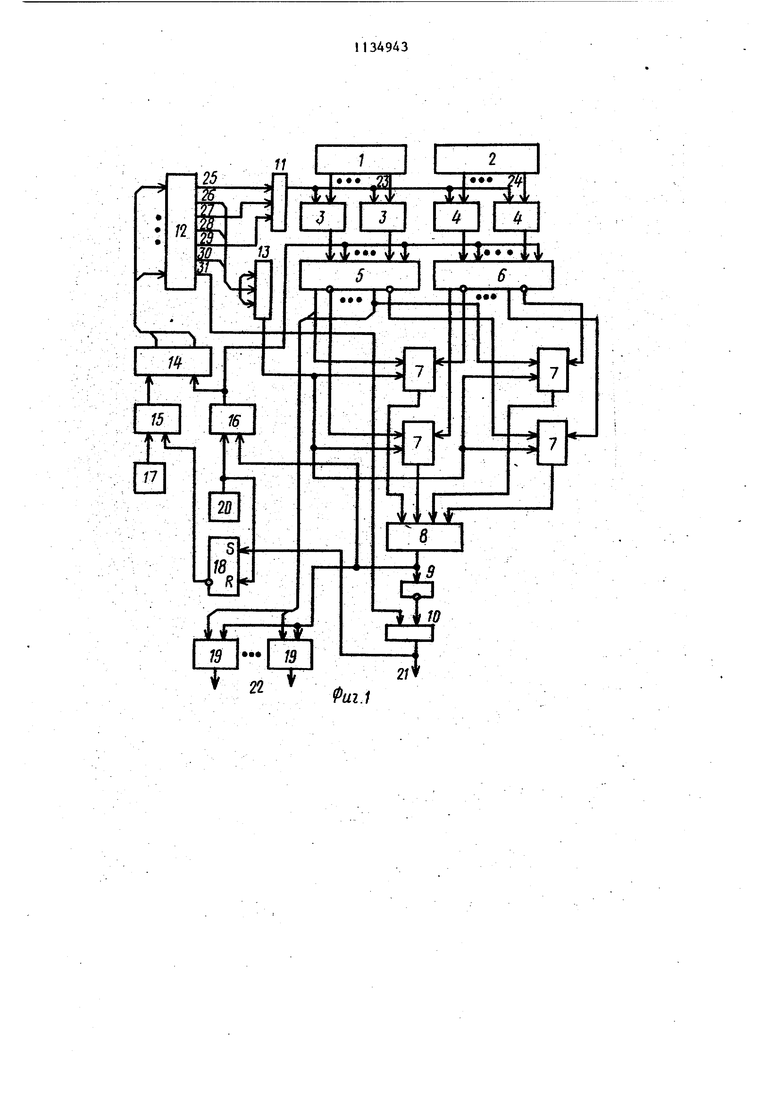

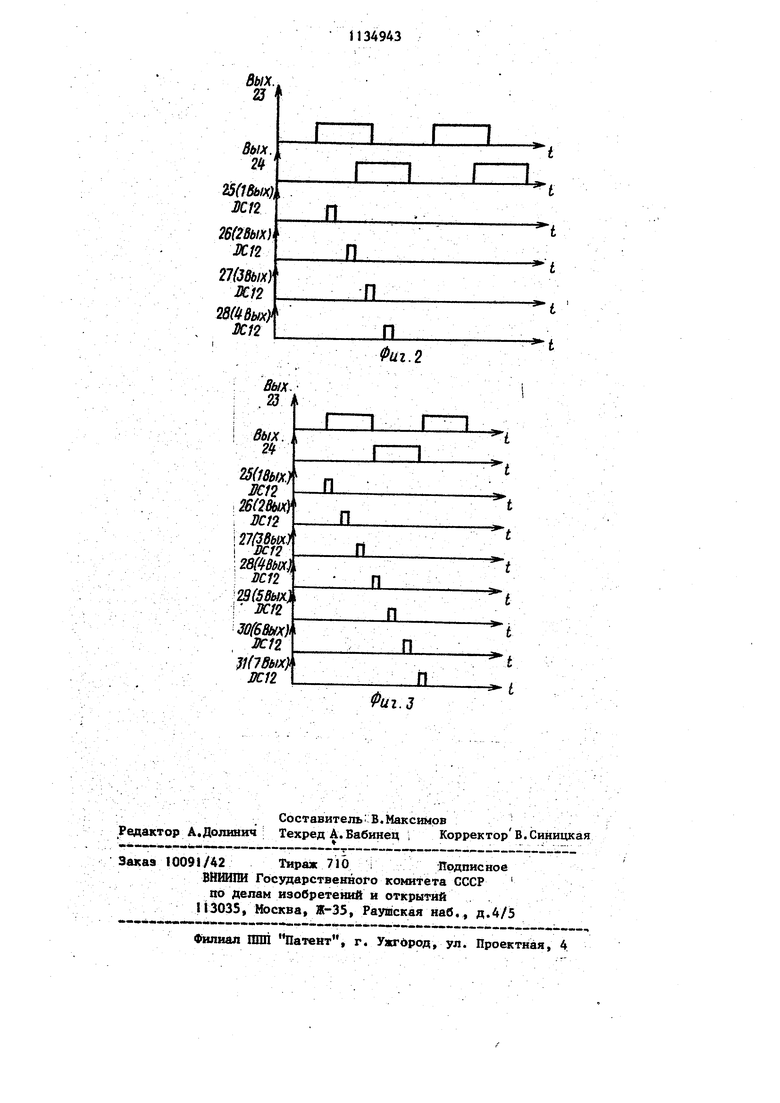

Изобретение относится к вычислительной технике и может быть исполь зовано для контроля работы вычислительн1 Ьс машин, не имеющих внешних средств синхронизации и встроенных средств контроля. Известно устройство для указания неисправностей в дублированных дискретных автоматах, содержащее дублированные блоки, выходы которых подключены к входам элемента сравнения и через первый и второй элементы совпадения к первым входам элементов ИЛИ, к вторым входам которых подключен выход третьего: элемента совпадения, а выходы элементов ИЛИ подключены к входам последующих дублированных блоков ij . Недостатком устройства является то, что оно не может быть использовано Для контроля вычислительных машин, не имеющих дополнительных выходов для синхронизации их работы а также не имеющих встроенных Средс контроля. Известно устройство; содержащее первую вычислительную машину, синхронизирующее устройство, устройство контроля, элемент повторного пус счетчик сбоев, элемент начального пуска, причем синхронизирующее устройство подключено к первым входам первой и второй вычислительной машины, первые выходы первой и второй вычислительной машины соединены со входами устройства контроля, вто рой вход первой и второй вычислительной машины соединен с элементом повторного пуска, счетчиком сбоев и устройством контроля, третий вход и второй выход первой и второй выч |лительвой машины подключен к элемен начального пуска, первый и второй выход элементу начального пуска соединен с устройством контроля, выход элемента повторного пуска и счетчика сбоев подключен к треть му и четвертому, соответственно. входам элемента начального пуска, первый вход устройства соединен с пятым входом элемента начального пуска 2 .) Недостатком устройства является то, что оно требует применения вычислительных машин, имеющих дополнительные входы, обеспечивающие синхронизацию их работы и предполагают наличие встроенного аппаратт ного контроля. Применение устройства для вычислительных машин, не имеющих внешней синхронизации, приводит к увеличению вероятности выдачи Ложного сигнала отказ, так как счетчик может постоянно фиксировать несовпадение выходных воздействий в первой и второй вычислительных машинах, т.е. достоверность работы устройства будет низкой. Целью изобретения является повышение достоверности работы устройства, т.е. уменьшение вероятности выдачи ложного сигнала Отказ, при пршченении вычислительных машин не имеющих входов для внешней синхронизации. Поставленная цель достигается тем, что устройство, содержащее грзшпу сумматоров до модулю Два, счетчик импульсовj генератор импульсов, триггер, переключатель, дополнительно содержит первую и вторую группы элементов И, третий, четвер1Ъ1й и пятый элементы И, шестую группу элементов И, элемент НЕ, первый, второйчи третий элементы ИЛИ, дешифратор, первый и второй регистры, причем информационные выходы первой вычислительной машины пoдкJПoчeны ко вторым входам первой группы элементов И, а информационные выходы второй вычислительной машины - к вторым входам второй группы элементов И, первые входы первой и второй группы элементов И соединены с выходом первого элемента ИЛИ выходы первой группы элементов И подключены к информационным входам первого регистра, выходы второй группы элементов И соединены с информационными входами второго регистра, управляющие входы первого и второго регистров соединены с выходом третьего, элемента.ИЛИ, прямые и инверсные выходы первого регистра подключены к первым входам соответствующих сумматоров по модулю два, а прямые и инверсные выходы второго регистра - ко вторым входам группы сумматоров по модулю два, третьи входы которых подключены к выходу второго элемента ИЛИ, выходы ко входам третьего элемента И, выход которого подключен ко второму входу шестой группы элементов И, ко второму входу третьего элемента ИЛИ и к элементу НЕ, выход которого соединён со вторым входом четвертого элемента И, первый вход которого подключен к{п+1)выхЬду дешифратора выход четвертого элемента И соединен с первым выходом устройства и с первым входом триггера, второй вход которого подключен к выходу переключателя, инверсный выход триггера соединен со вторым входом пятого элемента И, первый вход которого соединен с выходом генератора импульсов, выход пятого, элемента И подключен к информационному входу счетчика им,пульсов, управляющий вход которого соединен с вькодом третьего элеме11та ИЛИ, первый вход которого подключе.|с к выходу, переключателя, выходы счетчика импульсов соединены с соответствующими входами дешифратора, все нечетные выходы которого, начиная с первого до(n-l), подключены ко входам первого элемента. ИЛИ, а все четные начиная со второго до п , подключены ко входам второго элемента ИЛИ, прямые выходы первого регистра соединены.с первыми входами.шестой группы элементов И, выходы которых .соединены со вторыми входами устройства, .- На фиг. I представлена блок-схем i устройства; на фиг. 12 - временная диаграмма работу.устройства, когда выходные сигналы с первой и.второй вычислительной машины не совпадают между собой менее чем яа половину периода; на фиг. 3- - то же,выходные сигналы с первой и второй вычисли434тельных машин не совпадают, между собой более чем на половину периода, На фиг.-Ь показаны первая и вторая вычислительные машины 1 и 2, первая 3 группа Элементов И, вторая 4 группа, элементов И, первый регистр 5, второй регистр 6, группа 7 сумматоров по модулю два, третий элемент И 8, элемент НЕ 9, четвертый элемент И 10, первый элемент ИЛИ II, дешифратор 12 второй элемент ИЛИ 13, счетчик нмпульсов 14, пятый элемент, И 15, третий элемент ИЛИ 16, генератор импульсов 17, триггер 18, шестая 19 группа элементов И, переключатель 20, первый выход 21 устройства, второй выход 22 устройства выходы 23 первой вычислительной машины 1, выходы 24 второй вычислительной машины, первый выход 25, второй выход 26, . выход 27, четвертый выход 28 пятый выход 29, шестой, выход 3Q седьмой выход 31 .дешифратора 12. На фиг. 2 приняты следующие обозначения: выходные сигналы на выходе 23 первой вычислительной машины I, выходные сйгналы на выходе 24 второй вычислительной машины 2, выходные сигналы .на первом выходе 25, на втором выходе 26., на третьем выходе 27, на четвертом выходе 28 дешифратора 12. На фиг. 3 приняты следующие обозначения:, выходные сигналы на выходе 23 первой вычислительной машины t, выходные сигналы на выходе 24 второй вычислительной машшш 2, выходные сигналы на первом выходе 25, на втором выходе 26, на третьем вьрсоде 27, на четвертом выходе 28, на пятом выходе 29, на шестом выходе 30, на седьмом выходе 31 дешифратора 12. Выходы 23 первой 1 вычислительной машины подключен к вторым-входам первой 3 группы элементов И, а выходы 24 вычислительной машины Z - к вторым входам второй 4 гр.уппы зле-, ментов И, первые входы первой 3 и второй 4 группы элементов И соединены с выходами первого 11 элемента ИЛИ, Выходы первой .3 .группы злемевтг тов И подключены к информационным входам первого 5-регистра:. Выходы второй 4 группы элементов И соединены с инфо.рмациовными входами второго 6 регистра Управляющие входы , первого S и второго 6 регистра связевы с выходом третьего П элемента ИШ, прямые и инверсные вьЬсоды первого 5 регистра подключены к первым входам им соответствующих сумматоро 7 по модулю два группы, а прямые и инверсные выходы второго 6 регистра - к вторым входам группы 7 сумматоров по модулю.два. Третий вход группы 7 сумматоров по модулю два подключен к выходу второго 1.1 элемента ИЛИ, выходы группы 7 сумматоров по модулю два соединены со входами третьего 8 элемента И , выход которого подключен к второму входу шестой 19 группы элементов И, к второму входу третьего 16 элемента ИЛИ, и к элементу 9 НЕ, выход которого соединен со вторым входом четвертого 10 элемента И, первый вход которого подключен к (n+l) выходу дешифратора, 12. Выход четвертого 10 элемента И соединен с первым 21 выходом устройства и с первым входом триггера 18, второй вход которого подключен к переключателю 20. Инвер сный выход триггера 18 соединен со вто рым входом пятого 15 элемента J1, первый вход которого соединен с генераторо I7 импульсов, Выход пятого 15 элемента И подключен к информационному входу счетчика 14 импульсов, управляющий вход которого соединен с выходом третьего 16 элемента ИЛИ, первый вход которого подключен к переключателю 20. Выходы счетчика 14 импульсов соединены со входами дешифратора 12, всё ненетные выходы которого, начиная с первого по(п-1} подключены ко входам первого 11 эле мента ИЛИ, а все четные, начиная со второго, подключены ко входам второ го 13 элемента ИЛИ. Прямые выходы первого 5 регистра соединены с входами шестой 19 группы элемен тов И, выходы которых связаны со вт рым 22 выходом устройства. Первая I и вторая 2 вычислительные машины - это две вдентичные вычислительные машины нли микро-вычислительные машины. Использование двух вычислительных машин обоснован необходимостью повьшгения достоверно ти работы вычислительных маоин, не имеющих встроенных средств контроля Устройство работает следующим образом. С подачей питания, нажатием переключателя 20, вьщается сигнал на приведение в исходное состояние счетчика импульсов 14, триггера 18 и регистров 5 и 6. С установкой триггера 18 в исходное нулевое)состояние (т.е. с поступлением сигнала на второй вход триггера 18)с его инверсного выхода снимается сигнал, соответствующий логической единице. Этот сигнал поступает на второй вход пятого 15 элемента И, подготавливая его к открытию. На первый вход элемента И 15 поступают импульсы с генератора импульсов I7. Эти импульсы через элемент И 15 поступают на счетный вход счетчика импульсов 14. Емкость счетчика импульсов 14 будет определяться частотой следоваиия импульсов с генератора импульсов 17 и периодом следования сигналов с ЭВМ 1 .С выхода счетчика импульсов 14 комбинации выходных воздействий поступают на вход дешифратора 12, 1 Выходные сигналы с вычислительной машины t и 2 поступают на второй вход Первой 3 группы элементов И и соответственно на второй вход второй 4 группы элементов И.Сдвиг выходных импульсов вычислительной машины 1 и 2 между собой не должен превьшать половину периода следования импульсов. Если сдвиг мезкду выходными импульсами превышает эту величину, то одна из вычислительных машин функционирует неправильно. При поступлении комбинации входных воздействий с выхода счетчика 14 импульсов на вход дешифратора 12, на его выходе начинают последовательно возбуждаться выходные шины. Сложность дешифратора 12 будет определяться емкостью счетчика 14 импульсов. При возбуждении первого выхода 25 дешифратора 12 через первый 11 элемент ИЛИ выдается сигнал на первые входы первой 3 и второй 4 группы элементов И. Выходные сигналы, которые находятся в данный момент времени на выходе вычислительной машины I и 2 записываются соответственно в первый 5 и второй 6 регистры. На группу сумматоров 7 по модулю два постугГают сигналы с противоположных выходов первого 5 и второго 6 регистров. Так, например, с первого разряда регистра 5поступает сигнал с прямого выхода на первый вход группы сумматоров 7 по модулю два, а с этого же регистра 6на второй вход группы сумматоров 7.по модулю два поступает сигнал с инверсного выхода регистра 6(или же наоборот, b регистре 5 снимаются сигналы с инверсных выходов, а в регистре 6 - с прямыхJ. При возбуждении второго выхода 26 в дешифраторе 12 через элемент 1 ИЛИ вьщается сигнал на третий вход группы сумматоров 7 по модулю два. Если сигналы, поступающие не первый вход и второй вход.группы сумматоро 7 по модулю два, отличаются дЬуг от друга, ,1О с его выхода снимается сигнал, эквивалентный логической единице. Если с каждого сумматора 7 по модулю два группы, количество которых определяется, разрядностью регистров 5, 6, снимаются сигналы, эквивалентные логической единице, которые поступают на элемент 8 И, то в этом случае с его выхода ведается сигнал эквивалентный логической единице. Этот .сигнал поступает на второй вход элементов 19 И, разрешая выдачу информации на выход 22 записанной в первом 5 регистре. Одн временно с выхода элемента 8 И пост пает сигнал через элемент 16 ИЛИ на приведение счетчика 14 импульсов в исходное состояние, а также регистров 5 и 6. Если хотя-бы с одного сумматора 7 по модулю два группы сигнал, эквивалентный логической единице, то на выходе элемента 8 И сигнал, эквивалентньГй логической единице, тоже отсутствует, а на выходе элемента 9 НЕ возникает сигнал, который будет эквивалентен логической единице. Этот сигнал подготавливает к открытию элемент 10 И В этом случае, в соответствии с вре менной диаграммой,представленной на фиг.2,счетчик 14 импульсов продолжает дальше заполняться. На выходе дешифратора 12 возбуждается третий выход 27., обеспечивая через элемент 11 ИЛИ и элемент 3,4 И повторную запись информации в регистры 5 и 6. Сравнение, записанной информации в регистрах 5 и 6 происходит после того, как на дешифратор 12 поступает код, возбуждающий его четвертый выход 28. Далее процесс работы аналогичен описанному.Количество повторных считываний определяется периодом следования информаци / с вычислительной машины 1 (2) ,и частотой генератора 17.импульсоа за количество считываний примем как само считывание информации из 3 вычислительной машины. 1, так и ее сравнение). Если в результате проведения П го считывания на выходе элемента 8 И сигяал., эквивалентный ;логической единице, отсутствует, то при возбуждении()выхода 31 дешифратора 12, в соответствии с временной диаграммой, представленной на фиг. 3, поступает сигнал на первый вход элемента 10 И. С выхода элемента 10 И поступает сигнал отказ на первый 21 выход и на первый вход триггера 18, устанавливая его в единичное состояние. В этом случае на инверсном выходе триггера 18 устанавливается сигнал, эквивалентный логическому нулю, который закрывает элемент 15 И, т.е. счетчик 14 импульсов отключается от генератора I7 импульсов . Для продолжения работы необходимо нажать переключатель 20, т.е.. все устройства привести в исходное состояние. В случае, к примеру, наличия неисправности в вычислительной машине 1 (2)выходные последовательности сигналов с вычислительных машин 1 и 2 отличаются, друг от друга. Эти выходные, последовательности элементы 3 И при возбуждении первого выхода 25 в деш)1фраторе 11 записываются соответственно в регистр 5 и 6. Выходные сигналы с прямых и инверсных выходов регистра 5 и выходные сигналы с инверсных и прямых выходов.регистра 6 поступают на соответствующие сумматоры 7 по модулю два Группы. При возбуждении второго выходца 26 в дешифраторе 12 выходной сигнал через элементы 13 ИЛИ поступает на третий управлякнций вход сумматоров 7 по модулю два группы. Допустим, в f-м разряде выходные последовательности,сигналов с вычислительных машии 1 и 2 отличаются друг от друга, то в этом случае С выхода 1 -го сумматора 7 па модулю два. группы будет нулевой, сигнал. На группу сумматоров 7 по модулю два поступает, информация, с противоположш ас выходов регистра. 5 и б, т.е. если в i -и разряд регистра 5 записана единица, а в « -и разряд регистра 6 ноль, то на i -и сумматор 7 по модулю два группы с прямого выхода 1 -го разряда регистра 5 поступает единичный сигнал и с ииверс9

, выхода -го разряда, регистра 6 также, поступает единичный .сигнал.

В этом случае сигнал с выхода элемента 8 И отсутствует.

При последовательном возбуждении третьего 27 и пятого 29 выходов в дешифраторе 12 происходит повторное считывание, информации из ВМ I и ВМ 2« При возбуждении четвертого 28 и шестого ЗО.выходов в дешифраторе 12 происходит подача повторного третьего, управляющего сигнала на группу сумматоров 7. по модулю два. С помощью этого сигнала осуществляется синхронизация работы сумматоров 7 по модулю два группы. При возбуждении седьмого (n+l 31 выхода в Дешифраторе 12 им вьщается сигнал на элемент 10 И, так как с выхода элемента в И сигнал отсутствует, то с выхода элемента 9 НЕ -поступает вт рой сигнал. В этом случае с выхода элемента t О И сигнал поступает на ВЫХОД 21 и одноврю4енн() переводит триггер 18 в единичное состояние тем самым прекравцая подачу. импульсо с, генератора 17 иьшульсов через элемент 15 И.

В случае, если в вычислительной машине 1 или 2 Возник сббйу а ие Устойчивая неисправность. То устройство работает аналогично описанному. Если при повторных считываниях в регистры 5 и 1б будет записана

3494310

ч идентичная информация, то со всех сумматоров 7 по модулю два группы будут сниматься единичные сигналы, при подаче соответствующего управJ ляющего сигнала на его третий вход. Элемент 8 И открывается и вьщает сигнал, подготавливающий к открытию элементы 19 И, и одновременно этим сигналом, через элемент. 16 ИЛИ, приводит в исходное состояние счетчих 14 импульсов.

ГС Преимуществами .предлагаемого устройства являются повышение достоверности работы несинхрониэироваиных вычислительных машин, т.е. уменьшение вероятности выдачи ложного ; сигнала Отказ.за счет применения многократного считывания информации с вычислительной машины; вероятность водачи ложного сигнала Отказ определяется.нестабильностью работы вычислительной машины; возможность применения се.рийновыпускаемыз; микро-ЭВМ, не имеющих аппаратных встроенных средств контроля и доступа, для внешней синхронизации , т.е. достоверное ть. работы которой можно.повысить применяя метод Дублирования для построения контрольно-измерительной аппаратуры. Применение таких вычислительных машин в контрольно-измеритёльнрй аппаратуре позволит сократить экономические расходы на ее создание.

д О

Фиг.1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 0 |

|

SU283688A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Э ., ; 2 | |||

| Кузьмин И.В., Бурназян Р.Г., Ковергин А.А | |||

| Аппаратный контроль электронных цифровых вьтислительных машин | |||

| М., Энергия, 1974, с | |||

| Ступица для винтовых лопастей или крыльев вентиляторов, пропеллеров и т.п. | 1917 |

|

SU2122A1 |

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

1985-01-15—Публикация

1983-05-20—Подача