Ј

17

О

сл го ю со

00

Изобретение стносится к фазоизмери- тельной технике и может быть использовано для воспроизведения фазовых сдвигов с малым дискретом в широком диапазоне частот.

Цель изобретения - уменьшение дискрета задаваемого фазового сдвига.

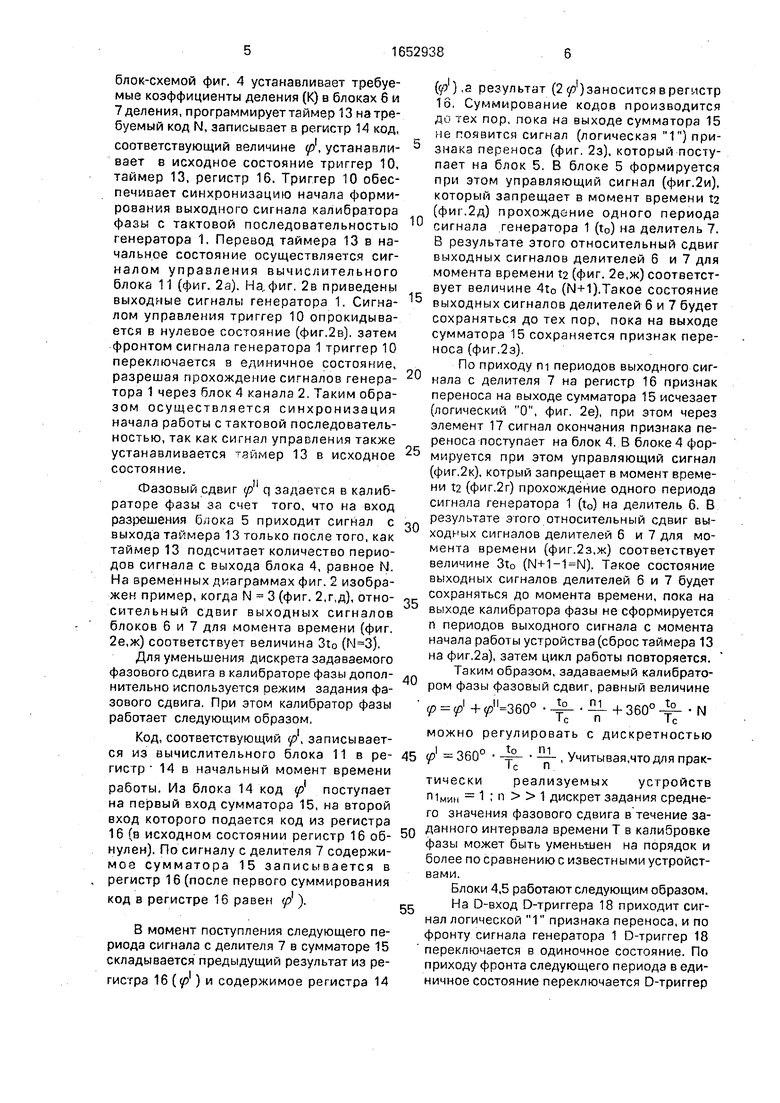

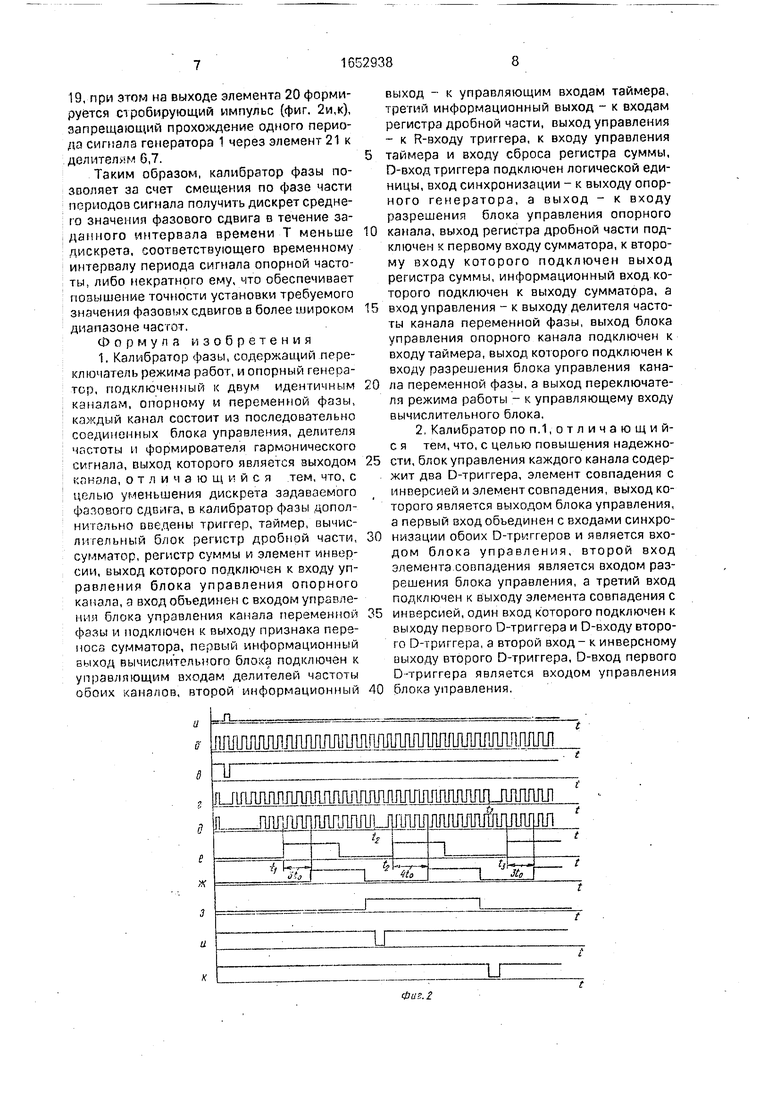

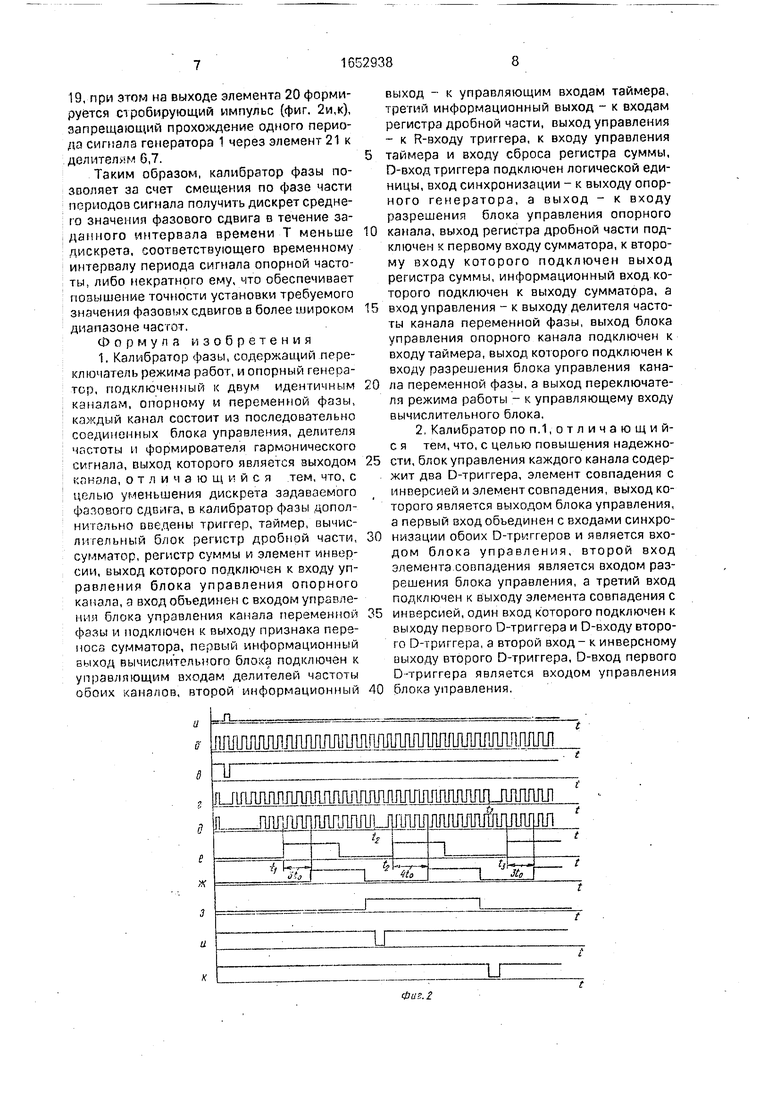

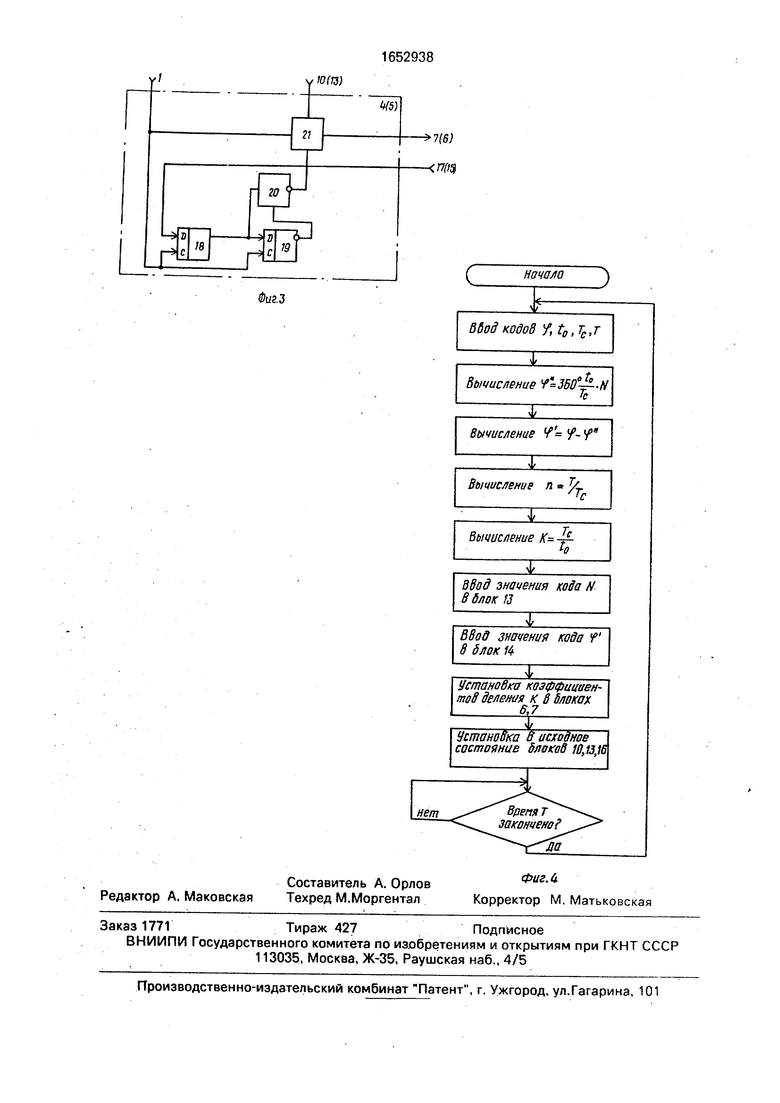

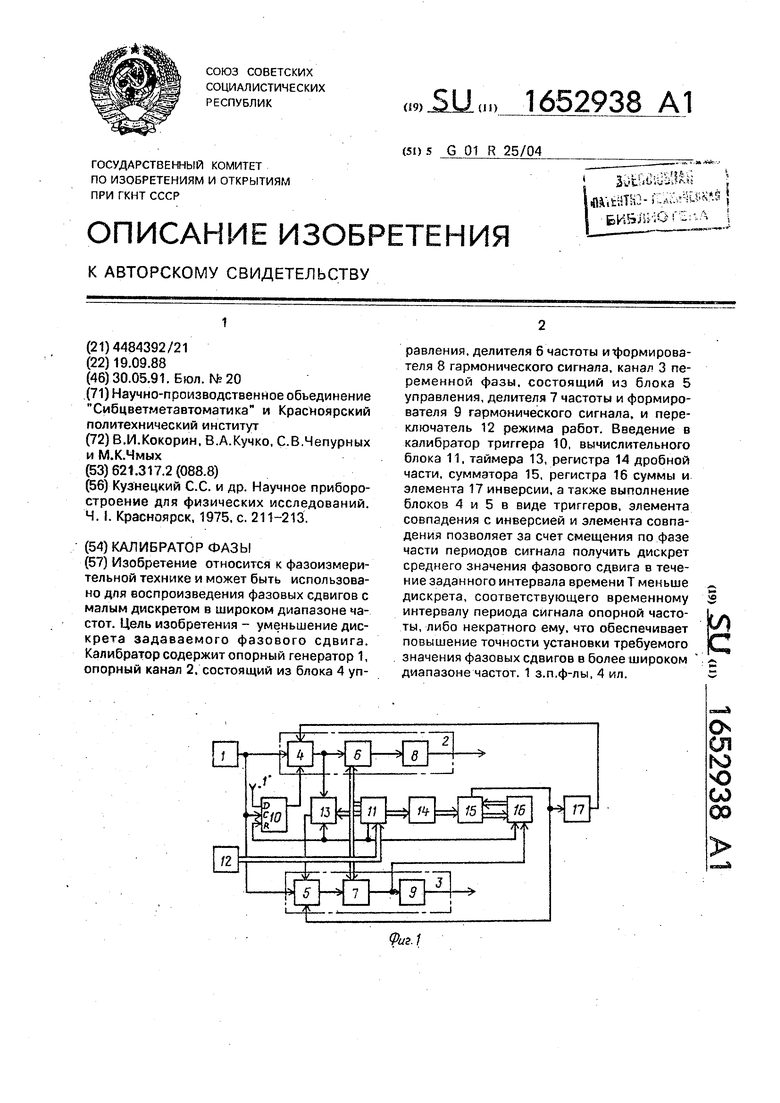

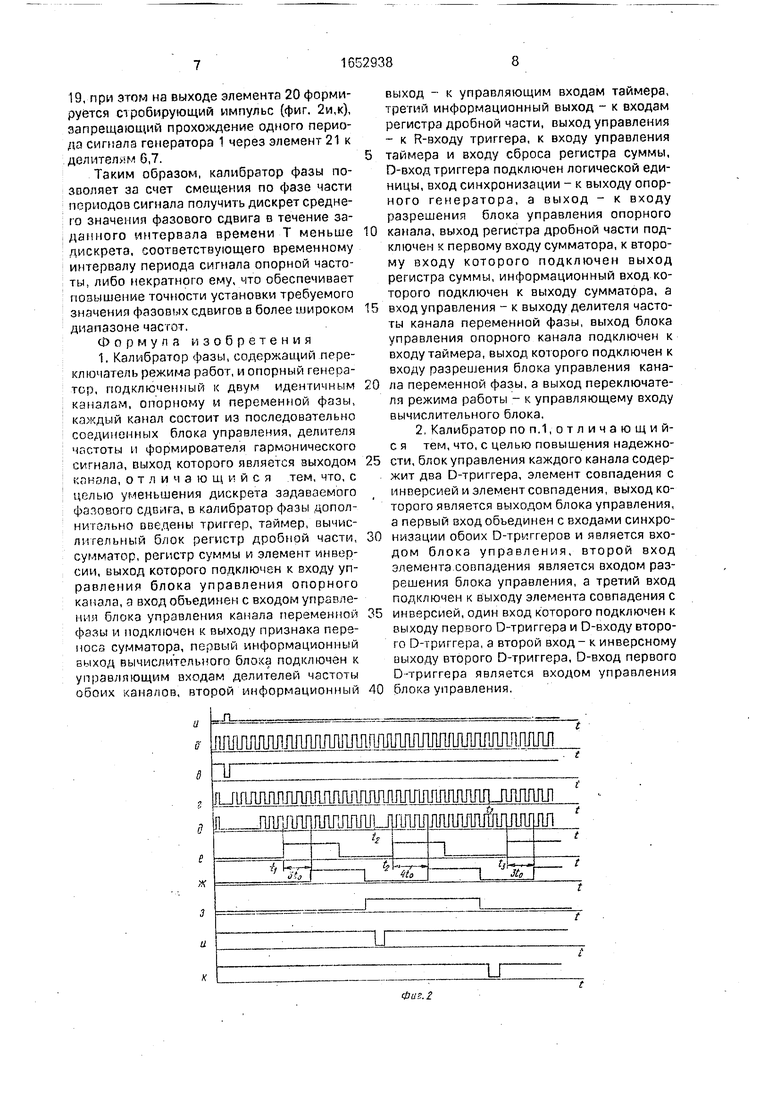

На фиг. 1 приведена структурная схема калибратора фазы; на фиг. 2 - эпюры, поясняющие принцип работы калибратора фазы; на фиг. 3 - схема блоков управления; на фиг. 4 - блок-схема алгоритма работы вычислительного блока.

Калибратор фазы (фиг.1) содержит опорный генератор 1, подключенный к двум идентичным каналам - опорному каналу 2 и каналу 3 переменной фазы, в составе каналов 2 и 3 имеются блоки 4 и 5 управления, делители 6 и частоты и формирователи 8 и 9 гармонического сигнала, причем в канале

2соединены последовательно блок 4, делитель б и формирователь 8, а в канале 3 - блок 5, делитель 7 и формирователь 9, а также триггер 10 пуска, вход синхронизации которого подключен к выходу опорного генератора 1, D-вход - к потенциалу логической единицы, э в.лход триггера 10 подключен к входу разрешения блока канала 2; вычислительный блок 11, выход управления которого подключен к R-входу триггера 10, первый информационный выход вычислительного блока 11 подключен к управляющим входам делителей 6,7, вход управления - к выходу переключателя 12 режима работ; таймер 13, к входу управления которого подключен выход вычислительного блока 11, а к информационному входу - второй информационный выход вычислительного блока 11, к счетному входу таймера 13 подключен выход блока 4, а выход таймера 13 подключен к входу разрешения блока 5; регистр 14 дробной части, вход которого подключен к третьему информационному выходу вычислительного блока 11; сумматор 15, к первому входу которого подключен выход регистра 14, а выход признака переноса подключен к входу управления блокл 5; регистр 16 суммы, информационный вход которого подключен к информационному выходу сумм-птора 15, информационный выход - к второму информационному входу сумматсрн 15, к входу сброса регистра 16 подклеен выход управления сычислительного блока 11,

3к входу управления записью - выход де- лителей 7, и элемент 17 инверсии, вход

которого подключен к выходу признака переноса сумматора 15, а выход - к входу управления блока 4.

Блоки 4 , 5 (фиг.З) содержат два D-триг гера 18, 19, элемент 20 совпадения с инвер сией и элемент 21 совпадения, выход которого является выходом блока 4 (5), первый вход элемента 21 соединен с синхров- ходами D-триггеров 18, 19 и является входом блока 4 (5), второй вход элемента 21 является входом разрешения блока 4 (5), третий вход соединен с выходом элемента

0 20, один выход которого соединен с инверсным выходом D-триггера 19, а другой - с D-входом D-триггера 19 и выходом D-триггера 18, D-вход которого является входом управления блока 4(5),

5Калибратор фазы работает следующим

образом.

Генератор 1 вырабатывает сигнал прямоугольной формы, поступающий на блоки 4 и 5, которые осуществляют исключение

0 необходимого количества импульсов, после чего в делителях 6 и 7 производится деление частоты сигналов генератора 1. Далее сигналы прямоугольной формы поступают на Формирователи 8 и 9, где производится вы5 деление первой гармоники и формирование выходного синусоидального сигнала.

Вычислительный блок 11 осуществляет управление блоками калибратора фазы и выполняет вычислительные операции с

0 целью задания Tpe6veMoro фазового сдвига п соответствии с алгоритмом, приведенным на фиг. 4.

Задаваемый устройство фазовый сдвиг р можно представить в виде формулы

5

0

5

/ + - Фазовый сдвиг

Л

у соответствует задержке повремени целого числа периодов сигнала генератора 1 (to), определяется

выражением / 360° -у1- N где Тс - период выходного сигнала калибратора фазы, N - код таймера 13 и может принимать значение N 0, 1, 2 ... до (To/to - 1); фазовый сдвиг у представляет собой среднее значение фазового сдвига за несколько периодов выходного сигнала калибратора фазы и определяется выражением

0

5

360° -f-

ъ Щ Тс п

где п - количество периодов выходного сигнала калибратора фазы Тс, в течение которых задается среднее значение фазового сдвига р(П Тс - Т ) m - количество периодов выходного сигнала калибратора фазы, в течение которых задается фазовый

сдвиг .

Перед началом работы калибратора фазы переключателем 12 в вычислительный блок 11 вводятся коды значений , Т. Вычислительный блок 11 в соответствии с

блок-схемой фиг. 4 устанавливает требуемые коэффициенты деления (К) в блоках 6 и 7 деления, программирует таймер 13 на требуемый код N, записывает в регистр 14 код,

соответствующий величине у, устанавливает в исходное состояние триггер 10, таймер 13, регистр 16. Триггер 10 обес- печипает синхронизацию начала формирования выходного сигнала калибратора фазы с тактовой последовательностью генератора 1. Перевод таймера 13 в начальное состояние осуществляется сигналом управления вычислительного блока 1 i (фиг. 2d). На фиг. 2в приведены выходные сигналы генератора 1. Сигма- лом управления триггер 10 опрокидывается в нулевое состояние (фиг,2г-). затем фронтом сигнала генератора 1 триггер 10 переключается в единичное состояние, разрешая прохождение сигналов генератора 1 через блок А канала 2. Таким образом осуществляется синхронизация начала работы с тактовой последовательностью, так как сигнал управления также устанавливается я.:мер 13 в исходное состояние.

Фазовый сдвиг р q задайся в капиб- раторе фазы ja счет того, что на вход разрешения С.юка 5 приходит сигнал с выхода таймера 13 только после того, как таймер 13 подсчитает количество периодов сигнала с выхода блока 4, равное N. На временных диаграммах фиг. 2 изображен пример, когда N 3 (фиг. 2,г,д). относительный сдвиг выходных сигналов блоков 6 и 7 для момента времени (фиг. 2е,ж) соответствует величина 3to ().

Для уменьшения дискрета задаваемого фазоього сдвига в калибраторе фазы дополнительно используется режим задания фазового сдвига. При этом калибратор фазы работает следующим образом.

Код, соответствующий . записывается из вычислительного блока 11 в регистр 14 в начальный момент времени

работы. Из блока 14 код ( поступает на первый вход сумматора 15, на второй вход которого подается код из регистра 16 (в исходном состоянии регистр 16 обнулен). По сигналу с делителя 7 содержимое сумматора 15 записывается в регистр 16 (после первого суммирования

код в регистре 16 равен )

В момент поступления следующего периода сигнала с делителя 7 в сумматоре 15 складывается предыдущий результат из регистра 16 () и содержимое регистра 14

0

5

0

5

0

5

0

5

0

5

(у }, а результат (2 заносится в регистр 16. Суммирование кодов производится д. тех пор. пока на выходе сумматора 15 ме появитсч сигнал (логическая 1) признака переноса (фиг. 2з), который поступает на блок 5. В блоке 5 формируется при этом управляющий сигнал (фиг.2и), который запрещает в момент времени t2 (фиг.2д) прохождение одного периода сигнала генератора 1 (t0) на делитель 7. В результате этого относительный сдвиг выходных сигналов делителей 6 и 7 для момента времени t2 (фиг. 2е,ж) соответствует величине 4t0 (N + 1).Такое состояние выходных сигналов делителей 6 и 7 будет сохраняться до тех пор, пока на выходе сумматора 15 сохраняется признак переноса (фиг.2з).

По приходу т периодов выходного сигнала с делителя 7 на регистр 16 признак переноса на выходе сумматора 15 исчезает (логический О, фиг. 2е), при этом через элемент 17 сигнал окончания признака переноса поступает на блок 4. В блоке 4 формируется при этом управляющий сигнал (фиг.2к), котрый запрещает в момент времени 12 (фиг.2г) прохождение одного периода сигнала генератора 1 (t0) на делитель б. В результате эюго относительный сдвиг выходных сигналов делителей 6 и 7 для момента времени (фиг.2з,ж) соответствует величине 3t0 (N+1-1 N). Такое состояние выходных сигналов делителей 6 и 7 будет сохраняться до момента времени, пока на выходе калибратора фазы не сформируется п периодов выходного сигнала с момента начала работы устройства (сброс таймера 13 на фиг.2а), затем цикл работы повторяется.

Таким образом, задаваемый калибратором фазы фазовый сдвиг, равный величине

Р 1Р +/ 360° - - -+360°- -N можно регулировать с дискретностью ft - 360° -у- - , Учитывая,что для практически реализуемых устройств П1мия 1 ; п 1 дискрет задания среднего значения фазового сдвига в течение заданного интервала времени Т в калибровке фазы может быть уменьшен на порядок и более по сравнению с известными устройствами.

Блоки 4,5 работают следующим образом.

На D-вход D-триггера 18 приходит сигнал логической 1 признака переноса, и по фронту сигнала генератора 1 D-триггер 18 переключается в одиночное состояние. По приходу фронта следующего периода в единичное состояние переключается D-триггер

19, при этом на выходе элемента 20 формируется (Пробирующий импульс (фиг. 2и,к), запрещающий прохождение одного периода сигнала генератора 1 через элемент 21 к делителем 6,7.

Таким образом, калибратор фазы позволяет за счет смещения по фазе части периодов сигнала получить дискрет среднего значения фазового сдвига в течение заданного интервала времени Т меньше дискрета, соответствующего временному интерпалу периода сигнала опорной частоты, либо некратного ему, что обеспечивает иозышение точности установки требуемого значения фазових сдвигов в более широком диапазоне частот.

Формула изобретения 1. Калибратор Фазы, содержащий переключатель режима работ, и опорный генгоа- тср, подключенный к двум идентичным копалам, опорному и переменной фазы, каждый канал состоит из последовательно соединенных блоки управления, делителя частоты и формирователя гармонического сигнала, выход которого является выходом |., отнимающийся тем, что, с цглью уменьшения дискрета задаваемого Фагового сдг.ига. в алибратор фазы дополни гйльно введены триггер, таймер вычислительный блок решстр дробной части, сумматор, регистр суммы и элемент инверсии, выход которого подключен к входу управления блока управления опорного канала, п вход объединен с входом упрапле- пия блока упртпления канала переменной фазы и подключен к выходу признака переноса сумматора, гирвыи информационный БМХОД вычислптел ного блока подключен к управляющим вхгдам делителей частоты обоих каналов н горой информационный

выход - к управляющим входам таймера, третий информационный выход - к входам регистра дробной части, выход управления - к R-входу триггера, к входу управления таймера и входу сброса регистра суммы, D-вход триггера подключен логической единицы, вход синхронизации - к выходу опорного генератора, а выход - к входу разрешения блока управления опорного канала, выход регистра дробной части подключен к первому входу сумматора, к второму входу которого подключен выход регистра суммы, информационный вход которого подключен к выходу сумматора, а вход управления - к выходу делителя частоты канала переменной фазы, выход блока управления опорного канала подключен к входу таймера, выход которого подключен к входу разрешения блока управления канала переменной фазы, а выход переключателя режима работы - к управляющему входу вычислительного блока,

2 Калибратор по п. 1, о т л и ч а ю щ и й- с я тем, что, с целью повышения надежности, блок управления клждого канала содержит два D-триггера, элемент совпадения с мнперсией и элемент совпадения, выход которого является выходом блока управления, а первый вход обьединен с входами синхронизации обоих D-rpiTfopoB и является входом блока управления, второй вход элемента совпадения является входом раз- ргшения блока управления, а третий вход подключен к выходу элемента совпадения с иноррсией, один вход которого подключен к выходу первого D-триггера и D-входу второго П-грипера, а второй вход- к инверсному выходу второго D-триггера, D-вход первого D-ipunepa является входом управления блока управления.

дагш

начало

}

| название | год | авторы | номер документа |

|---|---|---|---|

| Калибратор фазы | 1982 |

|

SU1048424A1 |

| Широкодиапазонный калибратор фазовых сдвигов | 1987 |

|

SU1525614A1 |

| Калибратор фазы | 1983 |

|

SU1138761A1 |

| Широкодиапазонный калибратор фазовых сигналов | 1984 |

|

SU1226339A1 |

| ПРИЕМОИНДИКАТОР СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1993 |

|

RU2067771C1 |

| Калибратор фазового сдвига | 1985 |

|

SU1352400A1 |

| Генератор-калибратор временных интервалов | 1985 |

|

SU1367139A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Дискретное фазосдвигающее устройство | 1990 |

|

SU1758582A1 |

| Устройство для измерения электромагнитных параметров объемных экранов | 1983 |

|

SU1228150A1 |

Изобретение относится к фазоизмери- тельной технике и может быть использовано для воспроизведения фазовых сдвигов с малым дискретом в широком диапазоне частот. Цель изобретения - уменьшение дискрета задаваемого фазового сдвига. Калибратор содержит опорный генератор 1, опорный канал 2, состоящий из блока 4 управления, делителя 6 частоты и формирователя 8 гармонического сигнала, канал 3 переменной фазы, состоящий из блока 5 управления, делителя 7 частоты и формирователя 9 гармонического сигнала, и переключатель 12 режима работ. Введение в калибратор триггера 10, вычислительного блока 11, таймера 13, регистра 14 дробной части, сумматора 15, регистра 16 суммы и элемента 17 инверсии, а также выполнение блоков 4 и 5 в виде триггеров, элемента совпадения с инверсией и элемента совпадения позволяет за счет смещения по фазе части периодов сигнала получить дискрет среднего значения фазового сдвига в течение заданного интервала времени Т меньше дискрета, соответствующего временному интервалу периода сигнала опорной частоты, либо некратного ему, что обеспечивает повышение точности установки требуемого значения фазовых сдвигов в более широком диапазоне частот. 1 з.п.ф-лы, 4 ил. в

ВВод кодод У, ta, тс,г

Вычисление ЗбО - -Н с

Вычисление Ч f- Т

Вычисление л /4

if

Вычисление К h

Ввод значения кода N 8 блок 13

Ввод значения кода f в блок П

У ста нов/са казффиааен- товделет/я К 6 блоках 6J

Установка В исходное состояние блокоВ fff,i3tt6

| Кузнецкий С.С | |||

| и др | |||

| Научное приборостроение для физических исследований | |||

| Ч | |||

| I | |||

| Красноярск | |||

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| с | |||

| Способ добывания бензина и иных продуктов из нефти, нефтяных остатков и пр. | 0 |

|

SU211A1 |

Авторы

Даты

1991-05-30—Публикация

1988-09-19—Подача