Изобретение относится к электросвязи и может использоваться в системах передачи данных.

Цель изобретения - повышение скорости анализа.

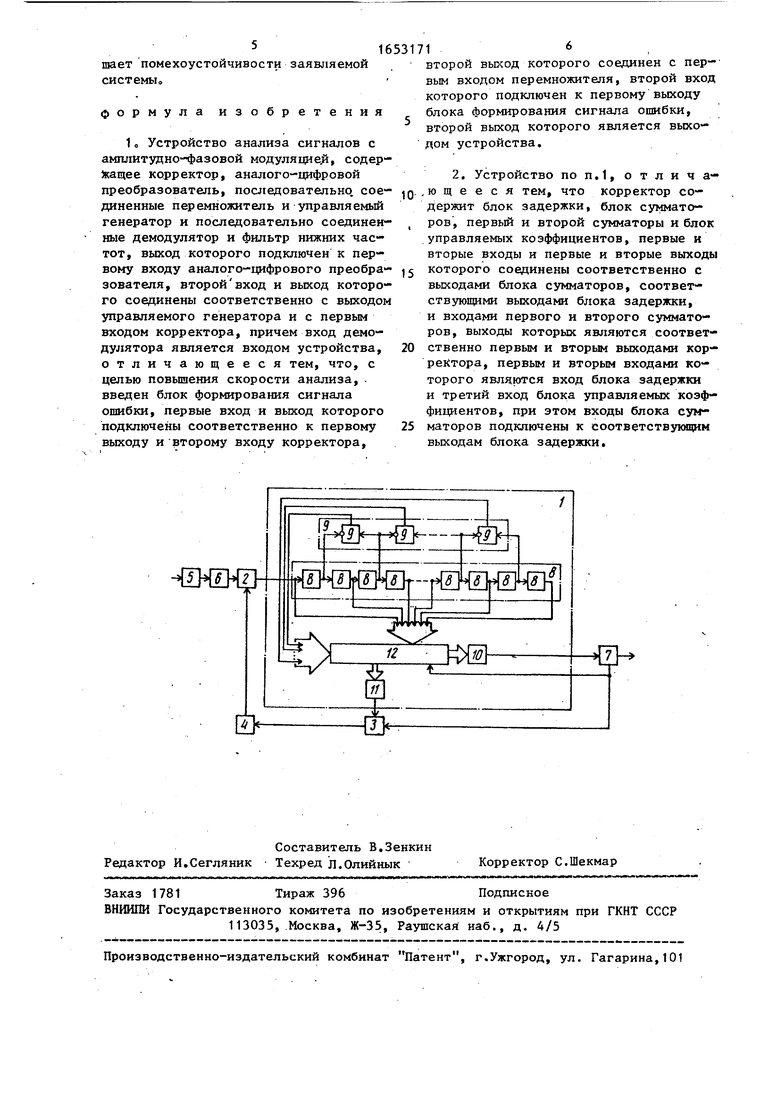

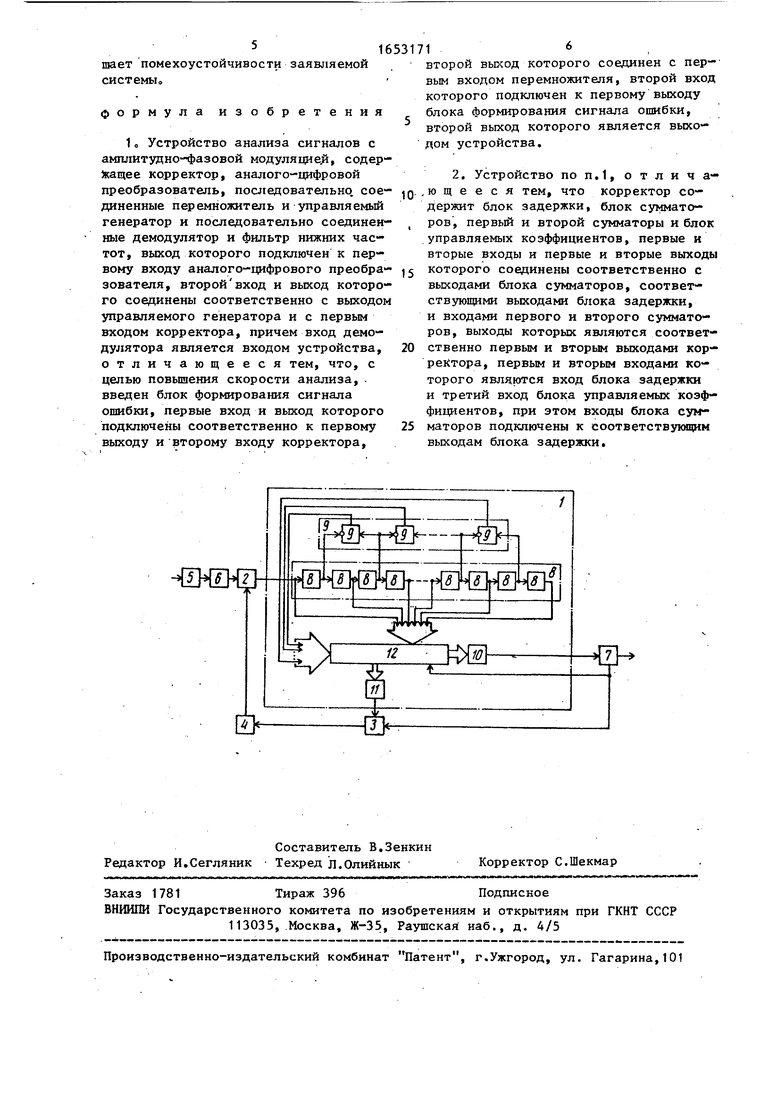

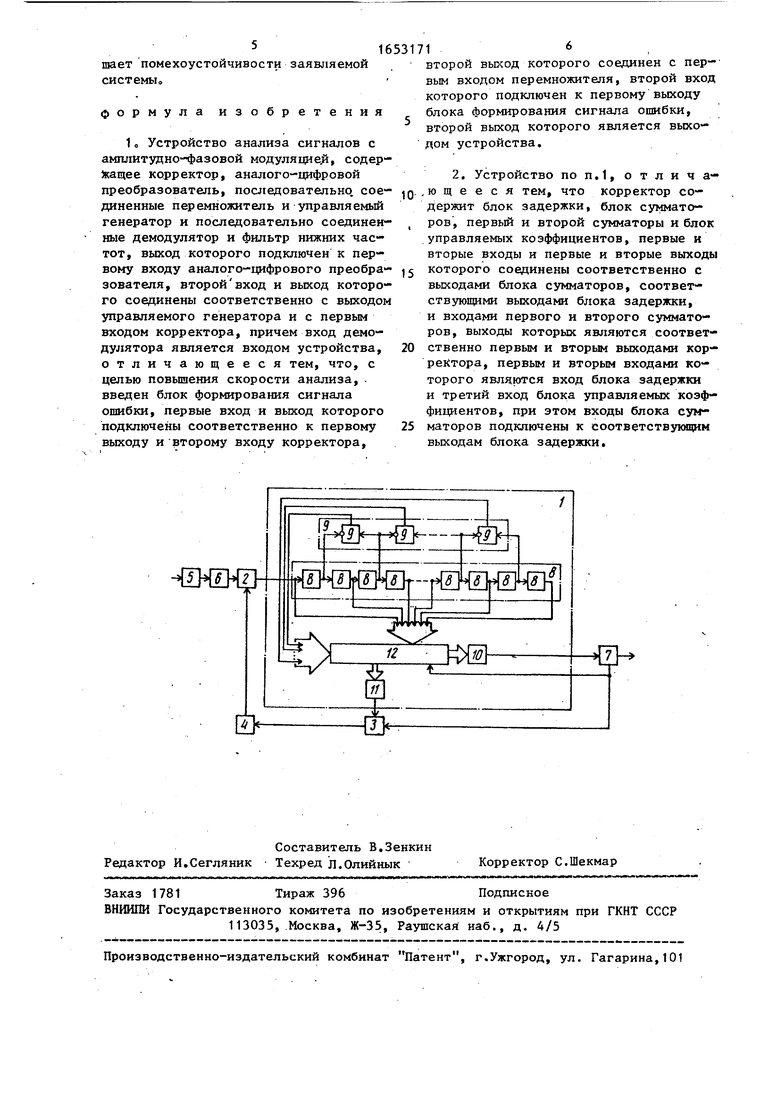

На чертеже представлена структурная электрическая схема устройства анализа сигналов с амплитудно-фазовой модуляцией.

Устройство анализа сигналов с амплитудно-фазовой модуляцией содержит корректор 1, аналого-цифровой преобразователь 2, перемножитель 3, управляемый генератор 4, демодулятор 5 и фильтр 6 нижних частот, а также блок 7 формирования сигнала ошибки. Корректор 1, входящий в состав устройства, содержит блок 8 задержки, блок 9 сумматоров, первый и второй сумматоры 10 и 11 и блок 12 управляемых коэффициентов,

Устройство анализа сигналов с амплитудно-фазовой модуляцией работает следующим образомо

Входной сигнал из канала связи поступает на демодулятор 5, затем на фильтр 6 нижних частот (ФНЧ) и далее на аналого-цифровой преобразователь 2 (АЦП) где он считывается в дискретные моменты времени через 1/2,

ск ел

G3

Здесь Т

1

2f,

2Ј„ - частота следоС

вания информационных символов) или - основная тактовая частота), a fc - полоса пропускания ФНЧ 6. С АЦП 2 дискретный сигнал поступает на корректор 1, а с его первого выхода - в блок 7 формирования сигнала ошибки и далее на выход устройства. Сигнал с первого выхода блока 7 формирования сигнала ошибки поступает на второй (управляющий) вход корректора 1 и на

второй вход перемножителя 3. Сигнал управления моментом считывания информации с выхода перемножителя 3 поступает на управляемый генератор А и за- тем на тактовый вход АЦП 2.

С выходов блока 8 задержки, блока 9 сумматоров, блока 12 управляемых коэффициентов, первого и второго сумматоров 10 и 11, перемножителя 3 и формирователя 7 сигнала ошибки сигналы поступают через промежуток времени Т, т.во через основной тактовый интервал.

Управляющий сигнал для определения момента считывания формируется на основе средне-квадратичного критерия качества принятого сигнала в приемнике:

Q M( Xt)e, (1) где М - символ математического ожидания;

7.1 - сигнал на входе блока 7 в момент времени t;

Xi - оценка переданного сигнала в

момент времени t0 Производная от критерия (1) по

такту т

Ё0 d€запишется в виде: о с- dZ

1 2Јt Z. - t ошибка,

где t,t

Сигнал Z, полученный на вректора 1, равен: иЧ

CJT

к1t-K

(3)

Ъ ЦшЛЛ| Л

где С k - управляемые коэффициенты корректора, чьи значения хранятся в блоке 12 управляемых коэффициентов;

Y . - значение сигналов на осно ных выходах блока 8 задержки, т.е. на входе первого и выходах всех четных отводов блока 8 задержки; к - номер основного выхода.

к 0,1,...n-i; 2п - количество отводов в блоке

8 задержки о

Сигналы на выходах двух соседних отводов в блоке 8 задержки сдви нуты на Т/2. Значение производной

-7v приближенно вычисляется как

величина, пропорциональная разности значений Z., взятых со сдвигом во времени относительно текущего момента времени на + Т/2

dZ-t 1 /7

dT T(

- Z

t-T/2

). (A)

dO 2 г dZt Тогда -.--- -

(5)

а момент считывания определяется как:

- -fEt- -VfEtf :,,.

t,,

х (Y + - Т/2 - К - Y.

+ Т/2 - К ),

5

0

5

0

5

0 5

0-

5

где у - коэффициент настройки. (6) Сигналы YЈ - Т/2 - К снимаются через тактовый интервал с дополнительных выходов блока 8 задержки, т0е. с выходов всех нечетных, отводов, кроме первого, и поступают на неинвертирующие входы блока 9 сумматоров. Сигналы Y Ј + Т/2 - К снимаются также через тактовый интервал Т со схода всех четных отводов, кроме последнего, и поступают на инвертирующие входы сумматоров 9„ Поэтому на все инвертирующие входы блока 9 сумматоров, кроме первого, поступают те же сигналы, что и на нейнвертирующие входы предыдущих сумматоров„

Группа сигналов (Y - Т/2 - К - - Y. + Т/2 - К), (К 1,2„..п-1) с выходов блока 9 сумматоров поступает через тактовые интервалы Т на первые входы блока 12 управляемых.коэффициентов. Со вторых выходов блока 12 управляемых коэффициентов снимаются сигналы - Т/2 - К - Y + + Т/2 - K)l также через тактовые интервалы Т„ Эти сигналы поступают на второй сумматор 11, на выходе, которого образуется сигнал х (Yt - Т/2 - К - Yt + Т/2 - К 5 „

Этот сигнал в перемножителе 3 умножается на сигнал ошибки с выхода блока 7 формирования сигнала ошибки. Таким образом, на выходе перемНожите«-1ля 3 образуется сигнал Ј .

х (Y4 - Т/2 - К - Y + Т/2 ). Управляемый генератор А, используя управляющий сигнал, регулирует момент считывания Ј петм воздействия на управляющий вход АЦП 3„

Управление моментом считывания 6 осуществляется на основании сигналов, снятых непосредственно с корректора 1 и пропорционально производной от критерия по такту, т.е. никакой дополнительной задержки в определение управляющего сигнала не вносится.По- этому время настройки момента считывания сокращается, что улучшает качество приема информации, т.е. повышает помехоустойчивости заявляемой системы.

формула изобретения

1„ Устройство анализа сигналов с амплитудно-фазовой модуляцией, содержащее корректор, аналого-цифровой преобразователь, последовательно, сое- диненные перемножитель и управляемый генератор и последовательно соединен- ные демодулятор и фильтр нижних частот, выход которого подключен к первому входу аналого-цифрового преобра- зователя, второй вход и выход которого соединены соответственно с выходом управляемого генератора и с первым входом корректора, причем вход демодулятора является входом устройства, отличающееся тем, что, с цепью повышения скорости анализа, введен блок формирования сигнала ошибки, первые вход и выход которого подключены соответственно к первому выходу и второму входу корректора,

Q , j 5 2025

31716

второй выход которого соединен с первым входом перемножителя, второй вход которого подключен к первому выходу блока формирования сигнала ошибки, 5 второй выход которого является выходом устройства.

2. Устройство поп.1,отлича- ю щ е е с я тем, что корректор соержит блок задержки, блок сумматоров, первый и второй сумматоры и блок управляемых коэффициентов, первые и вторые входы и первые и вторые выходы которого соединены соответственно с выходами блока сумматоров, соответствующими выходами блока задержки, и входами первого и второго сумматоров, выходы которых являются соответственно первым и вторым выходами корректора, первым и вторым входами которого являются вход блока задержки и третий вход блока управляемых коэффициентов, при этом входы блока сумматоров подключены к соответствующим выходам блока задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВРЕМЕННОЙ ДИСКРИМИНАТОР УСТРОЙСТВА ТАКТОВОЙ СИНХРОНИЗАЦИИ | 2006 |

|

RU2314646C1 |

| Адаптивный цифровой корректор | 1987 |

|

SU1506558A2 |

| Адаптивный цифровой корректор | 1979 |

|

SU794734A1 |

| Устройство адаптивного приема дискретных сигналов с амплитудно-фазовой модуляцией | 1986 |

|

SU1309319A1 |

| Адаптивный цифровой корректор | 1982 |

|

SU1083379A1 |

| Устройство для компенсации дрожания фазы сигнала в системах передачи данных | 1985 |

|

SU1243135A1 |

| Устройство для преобразования сигналов | 1984 |

|

SU1234991A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2009 |

|

RU2396721C1 |

| КВАЗИОПТИМАЛЬНЫЙ ПРИЕМНИК ДИСКРЕТНО-НЕПРЕРЫВНЫХ ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2004 |

|

RU2276459C1 |

| Адаптивное устройство для пространственно-временной обработки фазоманипулированных сигналов | 1984 |

|

SU1234981A1 |

Изобретение относится к электросвязи и может использоваться в системах передачи данных. Цель изобретения - повышение скорости анализа. Для достижения цели в устройство введен блок 7 формирования сигнала ошибки, а корректор 1 выполнен в виде соответствующим образом соединенных блока 8 задержки, блока 9 сумматоров, первого и второго сумматоров 10 и 11 и блока 12 управляемых коэффициентов. Управление моментом считывания информации осуществляется с помощью сигналов, снятых непосредственно с корректора 1 и пропорционально производной от критерия по такту, т„е. дополнительной задержки при определении управляющего сигнала не вносится. 1 з0л. ф-лы, 1 ил.

| Устройство обработки сигналов с амплитудно-фазовой модуляцией | 1978 |

|

SU720769A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-05-30—Публикация

1989-03-29—Подача