J/J

а

Вых. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| Устройство для исправления ошибокВ СиСТЕМЕ ОСТАТОчНыХ КлАССОВ | 1979 |

|

SU842820A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1989 |

|

SU1633497A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство кодирования | 1989 |

|

SU1762412A1 |

| Устройство кодирования-декодирования числовых последовательностей | 1990 |

|

SU1809541A1 |

| Устройство кодирования и декодирования информации | 1990 |

|

SU1783628A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1989 |

|

SU1649615A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

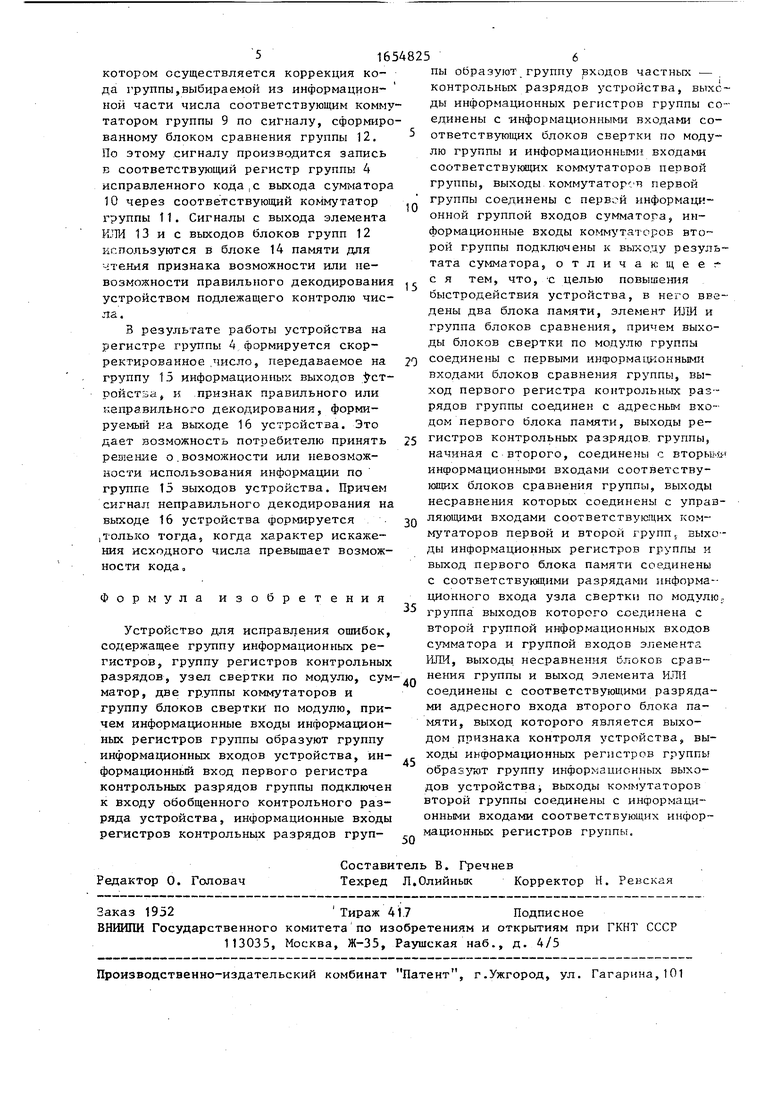

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах передачи данных. Цель изобретения - повышение быстродействия устройства. Устройство содержит группу 4 S-разрядных регистров, на которые записывается информационное слово, разбитое на п групп по S разрядов. Контрольные разряды контролируемого слова записываются на 4регистры группы 5, причем в первый ре гистр группы записывается контрольный 1код всего слова по модулю К 2 ь, а в остальные регистры - контрольные коды групп по модулю К К. Код, содержащийся в регистрах группы 4, сворачивается группой 8 блоков свертки по модулю и результат сравнивается на блоках сравнения группы 12. Узел 7 свертки по модулю формирует разность между принятым и вновь образованным обобщенным контрольным разрядом информационного слова. Выходы блоков сравнения группы 12 определяют номер регистра группы 4, где произошло искажение информации. С помощью коммутаторов группы 9 выбирается код с этого регистра и исправляется на сумматоре 10 путем сложения с результатом на выходе узла 7. Затем выход результата сумматора Ю с помощью коммутатора группы 11 записывается на регистр с S (Л 1 группы 4, где была искаженная информа- „ ция. 1 ил.

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах передачи данных ,,

Цель изобретения - повышение быстродействия устройства.

На чертеже дана функциональная схема устройства.

Устройство имеет группу 1 информа- 0 циониых входов устройства, вход 2 обобщенного контрольного разряда устройства, группу 3 входов частных контрольных разрядов устройства, группу 4 информационных регистров, группу 5 15 регистров контрольных разрядов.устройства, первый блок 6 памяти, узел 7 свертки по модулю, группу 8 блоков свертки по модулю, первую группу 9 коммутаторов, сумматор 10, вторую 20 группу 11 коммутаторов, группу 12 блоков сравнения, элемент ИЛИ 13, второй блок 14 памяти, группу 15 информационных выходов и выход 16 признака контроля.25

Информационное слово разбивается на п групп по S разрядов в каждой (S определяет максимальную кратность обнаруживаемых ошибок) и записывается 30 на группу 4 информационных регистров Контроль всего информационного слова осуществляется по модулю К 2 . Обобщенный контрольный разряд определяется по формуле35

г(А) - f ilrt .C-.U,

I J

ОДе ОС; код i-й S-разрядной группы, рассматриваемый как не- которое число; С i - весовой коэффициент 1-й

группы (принимается равным единице);

К - модуль контроля;

Гх1 - остаток от деления числа X

на модуль К.

При возникновении ошибки в одной и групп 0( число А превращается в А и между остатками г(А) и г (А) раз- ница составляет

Если место ошибки известно, то ее исправление легко осуществит, так как

И - tfj +

отсюда 0d j { 5 j - A J К

для определения места возникновения ошибки используются частные контрольные разряды f() для каждой группы разрядов, представляющие собой свертк этой группы разрядов по модулю К f К.

Первый блок 6 памяти осуществляет формирование величины (А). Групп 8 блоков по модулю формирует остатки по модулю К i от содержимого регистров группы 4.

Второй блок 14 памяти формирует признак контроля, означающий возможность правильного декодирования. Нулевое значение сигнала на выходе блока 14 формируется при нулевых значениях сигналов на выходах блоков сравнения группы 12 и элемента ИЛИ 13, а также при наличии единичного сигнала на выходе элемента ИЛИ 13 и одного из блоков сравнения группы 12. Это означает правильную коррекцию ошибки.

Устройство работает следующим образом.

На входы регистров групп 4 и 5 поступает подлежащее исправлению число. Его информационная часть поступа- ет на входы блоков 6 свертки по модулю группы, где формируются частные контрольные признаки для каждой .из фиксированных групп. Эта информация сравнивается с помощью блоков сравнения группы 12 с частными контрольными признаками, хранящимися в регистрах группы 5, в результате чего на выходах этих блоков формируются сигналы, соответствующие единичному уровню для тех блоков сравнения группы 12, где ошибка обнаружена, и нулевому уровню для блоков группы 12, где ошибка не обнаружена. Кроме того, информация числа с регистров группы 4 поступает на входы узла 7 свертки по модулю, туда же поступает и инверсное значение (К-г(А)) контрольного признака с первого блока 6 памяти. В результате на выходе узла 7 свертки формируется разность контрольных приз -наков, равная величине искажения в той группе, номер j которой определен с помощью групп 12 блоков сравнения utfj г(А)-г(А)-К.

Этот код поступает на элемент ИЛИ 13, в котором формируется единичный сигнал, если обнаружено искажение или нулевой сигнал, если искажение не обнаружено. Кроме того, этот код поступает на второй вход сумматора 10, в

котором осуществляется коррекция кода группы,выбираемой из информационной части числа соответствующим коммутатором группы 9 по сигналу, сформированному блоком сравнения группы 12. По этому сигналу производится запись в соответствующий регистр группы 4 исправленного кода,с выхода сумматора 10 через соответствующий коммутатор группы 11. Сигналы с выхода элемента ИЛИ 13 и с выходов блоков групп 12 используются в блоке 14 памяти для чтения признака возможности или невозможности правильного декодирования устройством подлежащего контролю числа.

В результате работы устройства на регистре группы 4 формируется скорректированное .число, передаваемое на группу 15 информационных выходов устройства , и признак правильного или каправильного декодирования, формируемый на выходе 16 устройства. Это дает возможность потребителю принять решение о.возможности или невозможности использования информации по группе 15 выходов устройства. Причем сигнал неправильного декодирования на выходе 16 устройства формируется ,только тогда, когда характер искажения исходного числа превышает возможности кода,

Формула изобретения

Устройство для исправления ошибок, содержащее группу информационных регистров, группу регистров контрольных разрядов, узел свертки по модулю, сум матор, две группы коммутаторов и группу блоков свертки по модулю, причем информационные входы информационных регистров группы образуют группу информационных входов устройства, ин- формационный вход первого регистра контрольных разрядов группы подключен к входу обобщенного контрольного разряда устройства, информационные входы регистров контрольных разрядов груп

0

5

0

5

д ,

0

0

пы образуют группу входов частных - контрольных разрядов устройства, выхс- ды информационных регистров группы соединены с информационными входами соответствующих блоков свертки по модулю группы и информационными, входами соответствующих коммутаторов первой группы, выходы коммутаторов первой группы соединены с первой информационной группой входов сумматора, информационные входы коммутаторов второй группы подключены к выхо.пу результата сумматора, отличающее с я тем, что, С целью повышения быстродействия устройства, в него введены два блока памяти, элемент ИЛИ и группа блоков сравнения, причем выходы блоков свертки по модулю группы соединены с первыми информационными входами блоков сравнения группы, выход первого регистра контрольных разрядов группы соединен с адресным входом первого блока памяти, выходы регистров контрольных разрядов группы, начиная с второго, соединены с вторыми информационными входами соответствующих блоков сравнения группы, выходы несравнения которых соединены с управляющими входами соответствующих коммутаторов первой и второй групп, выходы информационных регистров группы и выход первого блока памяти соединены с соответствующими разрядами информационного входа узла свертки по модулю, группа выходов которого соединена с второй группой информационных входов сумматора и группой входов элемента ИЛИ, выходы несравнения блоков сравнения группы и выход элемента ИЛИ соединены с соответствующими разрядами адресного входа второго блока памяти, выход которого является выходом рризнака контроля устройства, выходы информационных регистров группы образуют группу информационных выходов устройства, выходы коммутаторов второй группы соединены с информационными входами соответствующих информационных регистров группы.

| УСТРОЙСТВО для ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ ОШИБОК В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 0 |

|

SU369567A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для исправления ошибокВ СиСТЕМЕ ОСТАТОчНыХ КлАССОВ | 1979 |

|

SU842820A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-07—Публикация

1989-06-09—Подача