Изобретение относится к автоматике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством.

Целью изобретения является повышение точности преобразователя путем дополнительной коррекции неортогональности фаз и выравнивания амлитуд сигналов.

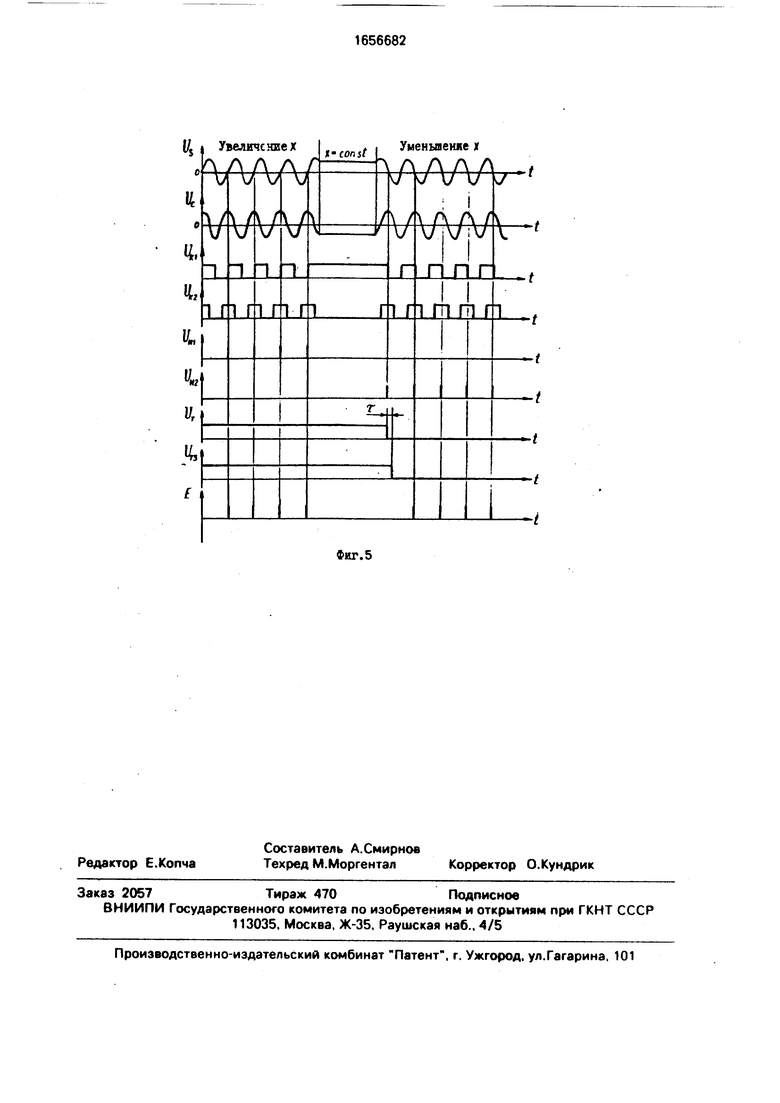

На фиг. 1 изображена структурная схема преобразователя; на фиг. 2 - структурная схема формирователя максимальных кодов; на фиг. 3 - структурная схема формирователя минимальных кодов; на фиг. 4 - структурная схема блока управления; на фиг. 5 - временные диаграммы блока управления.

Преобразователь перемещения в код (фиг. 1) содержит синусно-косинусный датчик (СКД) 1 перемещения, аналого-цифровые преобразователи (АЦП) 2 и 3, аналоговые вычитатели 4 и 5, блок 6 управления, формирователь 7 максимальных кодов, формирователь 8 минимальных кодов, сумматор 9, цифроанаголовый преобразо- ва- ель (ЦАП) 10, формирователь 11 максимальных кодов, формирователь 12 минимальных кодов, сумматор 13, цифроаOs

ел о (

00

ю

налоговый преобразователь (ЦАП) 14, усилитель 15, аналоговый вычитатель 16, АЦП 17, сумматоры 18 и 19, усилитель 20, аналоговый сумматор 21, АЦП 22, усилители 23 и 24, формирователи 25 и 26 максимальных кодов, интерполятор 27, генератор 28 импульсов.

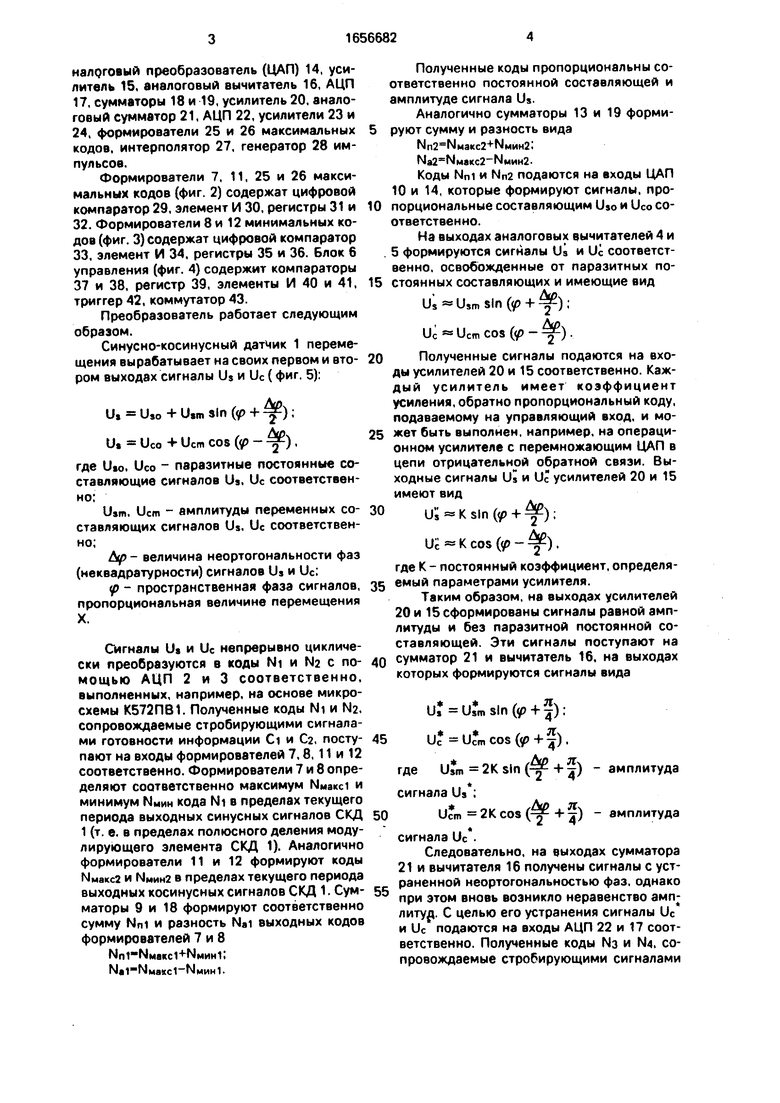

Формирователи 7, 11, 25 и 26 максимальных кодов (фиг. 2) содержат цифровой компаратор 29, элемент И 30, регистры 31 и

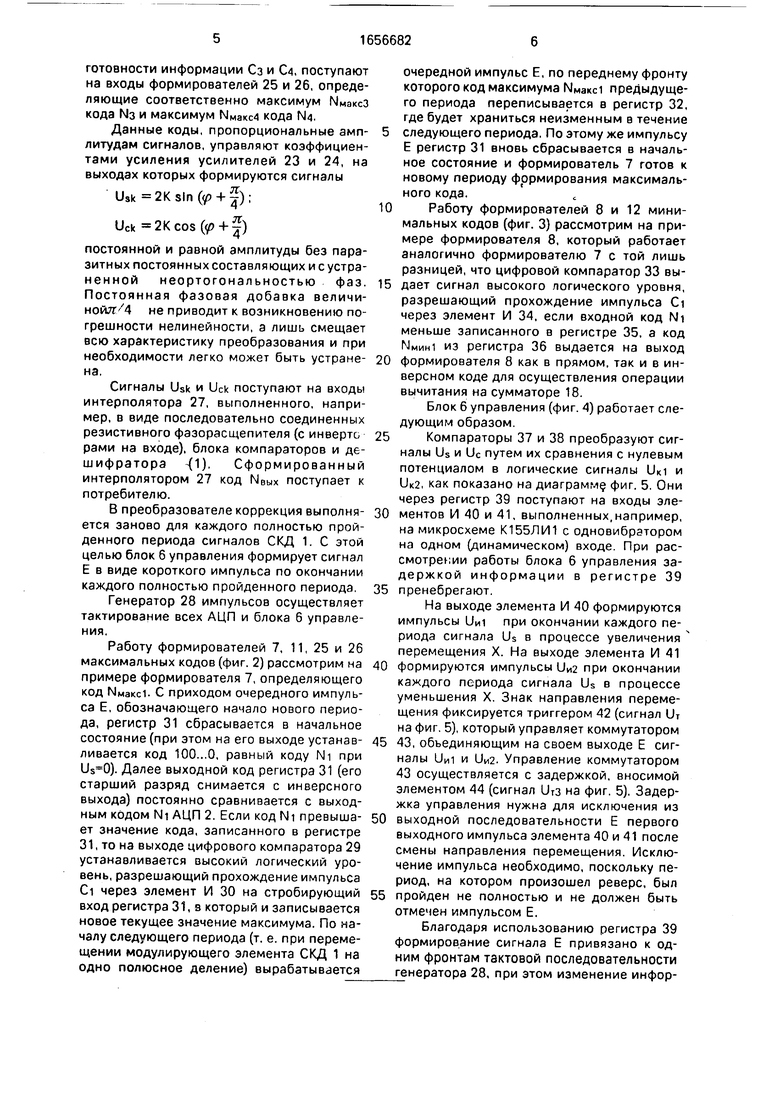

32.Формирователи 8 и 12 минимальных кодов (фиг. 3) содержат цифровой компаратор

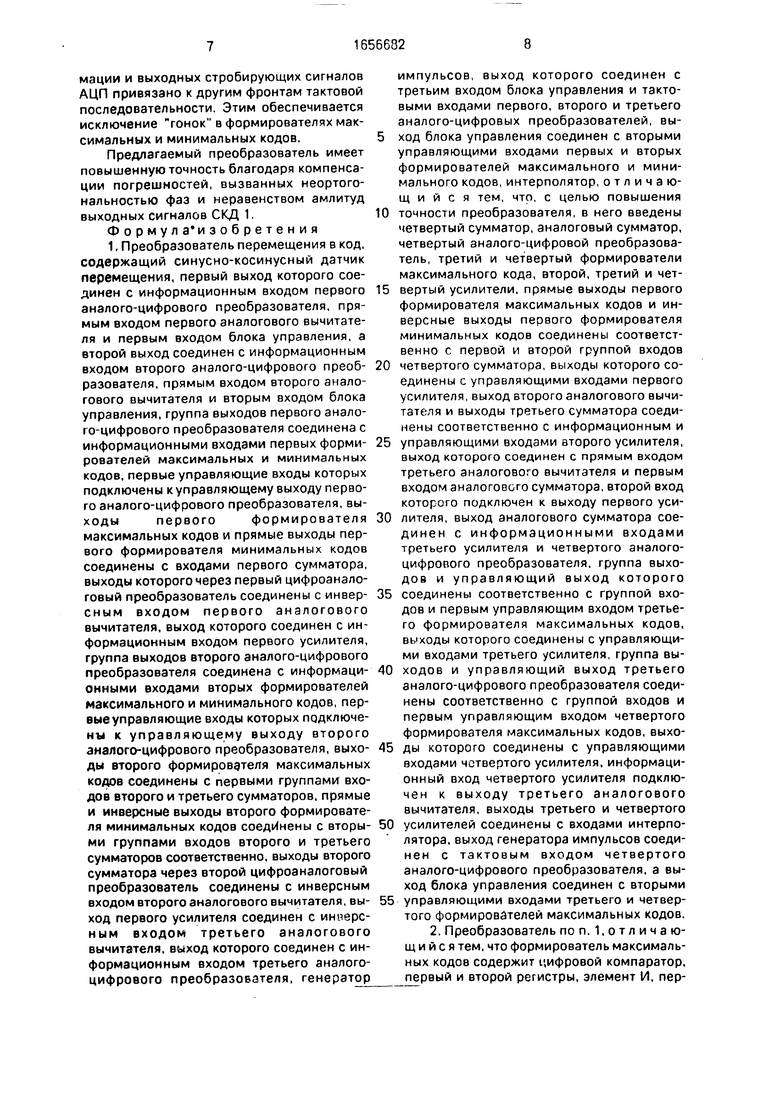

33,элемент И 34, регистры 35 и 36. Блок 6 управления (фиг. 4) содержит компараторы 37 и 38, регистр 39, элементы И 40 и 41, триггер 42, коммутатор 43.

Преобразователь работает следующим образом.

Синусно-косинусный датчик 1 перемещения вырабатывает на своих первом и втором выходах сигналы Us и Uc (фиг. 5):

U, U,o + U,n,slnft +);

Ut Uco + Ucm COS (tf - ) .

где Uso. Uco паразитные постоянные составляющие сигналов Us, Uc соответственно;

Usm, Ucm амплитуды переменных составляющих сигналов Us. Uc соответственно;

btp - величина неортогональности фаз (неквадратурности) сигналов Us и Uc:

р - пространственная фаза сигналов, пропорциональная величине перемещения X.

Сигналы Us и Uc непрерывно циклически преобразуются в коды NI и N2 с помощью АЦП 2 и 3 соответственно, выполненных, например, на основе микросхемы К572ПВ1. Полученные коды NI и N2. сопровождаемые стробирующими сигналами готовности информации Ci и С, поступают на входы формирователей 7,8,11 и 12 соответственно. Формирователи 7 и 8 определяют соответственно максимум ММакс1 и минимум NMHH кода NI в пределах текущего периода выходных синусных сигналов СКД 1 (т. е. в пределах полюсного деления модулирующего элемента СКД 1). Аналогично формирователи 11 и 12 формируют коды НМакс2 и ММин2 в пределах текущего периода выходных косинусных сигналов СКД 1. Сумматоры 9 и 18 формируют соответственно сумму ЫП1 и разность Nai выходных кодов формирователей 7 и 8

Nn1-NMaitc1+NMHHi;

Ма1-Ммакс1-Ммин1.

Полученные коды пропорциональны соответственно постоянной составляющей и амплитуде сигнала Us.

Аналогично сумматоры 13 и 19 форми- руют сумму и разность вида

Мп2 Ммакс2+Нмин2:

Na2 NMaicc2-NMMM2.

Коды Nnt и Мп2 подаются на входы ЦАП 10 и 14, которые формируют сигналы, про- порциональные составляющим Uso и Uco соответственно.

На выходах аналоговых вычитателей 4 и 5 формируются сигналы Us и Uc соответственно, освобожденные от паразитных по- стоянных составляющих и имеющие вид

Us «Usm sin (р + );

Uc « Ucm COS (p - ) .

Полученные сигналы подаются на входы усилителей 20 и 15 соответственно. Каждый усилитель имеет коэффициент усиления, обратно пропорциональный коду, подаваемому на управляющий вход, и может быть выполнен, например, на операционном усилителе с перемножающим ЦАП в цепи отрицательной обратной связи. Выходные сигналы Us и Uc усилителей 20 и 15 имеют вид

u;«Ksln(p+);

Uc « К cos (p - &).

где К - постоянный коэффициент, определяемый параметрами усилителя.

Таким образом, на выходах усилителей 20 и 15 сформированы сигналы равной амплитуды и без паразитной постоянной составляющей. Эти сигналы поступают на

сумматор 21 и вычитатель 16, на выходах которых формируются сигналы вида

U sin ((р + ) ; U U mCosfo +).

где 2К sin ( + ) - амплитуда

сигнала Us :

Ucm 2KCOS

f+) амплитуда

5

сигнала Uc

Следовательно, на выходах сумматора 21 и вычитателя 16 получены сигналы с устраненной неортогональностью фаз, однако при этом вновь возникло неравенство амплитуд. С целью его устранения сигналы Uc и Uc подаются на входы АЦП 22 и 17 соответственно. Полученные коды Ыз и N4. сопровождаемые стробирующими сигналами

готовности информации Сз и С4, поступают на входы формирователей 25 и 26, определяющие соответственно максимум ЫмаксЗ кода Мз и максимум NMaicc4 кода N4.

Данные коды, пропорциональные амплитудам сигналов, управляют коэффициентами усиления усилителей 23 и 24, на выходах которых формируются сигналы

USk 2Ksln(p + );

Uck 2Kcos(p + )

постоянной и равной амплитуды без паразитных постоянных составляющих и с устра- ненной неортогональностью фаз. Постоянная фазовая добавка величиной 1 не приводит к возникновению погрешности нелинейности, а лишь смещает всю характеристику преобразования и при необходимости легко может быть устранена.

Сигналы Usk и Uck поступают на входы интерполятора 27, выполненного, например, в виде последовательно соединенных резистивного фазорасщепителя (с инверто рами на входе), блока компараторов и дешифратора -(1). Сформированный интерполятором 27 код NBwx поступает к потребителю.

В преобразователе коррекция выполняется заново для каждого полностью пройденного периода сигналов СКД 1. С этой целью блок 6 управления формирует сигнал Е в виде короткого импульса по окончании каждого полностью пройденного периода.

Генератор 28 импульсов осуществляет тактирование всех АЦП и блока 6 управления.

Работу формирователей 7, 11, 25 и 26 максимальных кодов (фиг. 2) рассмотрим на примере формирователя 7, определяющего код Ммакс1. С приходом очередного импульса Е, обозначающего начало нового периода, регистр 31 сбрасывается в начальное состояние (при этом на его выходе устанавливается код 100...О, равный коду NI при ). Далее выходной код регистра 31 (его старший разряд снимается с инверсного выхода) постоянно сравнивается с выходным кодом NI АЦП 2. Если код NI превышает значение кода, записанного в регистре 31, то на выходе цифрового компаратора 29 устанавливается высокий логический уровень, разрешающий прохождение импульса Ci через элемент И 30 на стробирующий вход регистра 31, в который и записывается новое текущее значение максимума. По началу следующего периода (т. е. при перемещении модулирующего элемента СКД 1 на одно полюсное деление) вырабатывается

очередной импульс Е, по переднему фронту которого код максимума ЫМакс1 предыдущего периода переписывается в регистр 32, где будет храниться неизменным в течение

следующего периода. По этому же импульсу Е регистр 31 вновь сбрасывается в начальное состояние и формирователь 7 готов к новому периоду формирования максимального кода.

0 Работу формирователей 8 и 12 минимальных кодов (фиг. 3) рассмотрим на примере формирователя 8, который работает аналогично формирователю 7 с той лишь разницей, что цифровой компаратор 33 вы5 дает сигнал высокого логического уровня, разрешающий прохождение импульса Ci через элемент И 34, если входной код NI меньше записанного в регистре 35, а код NMMH из регистра 36 выдается на выход

0 формирователя 8 как в прямом, так и в инверсном коде для осуществления операции вычитания на сумматоре 18.

Блок 6 управления (фиг. 4) работает следующим образом.

5Компараторы 37 и 38 преобразуют сигналы Us и Uc путем их сравнения с нулевым потенциалом в логические сигналы Ук1 и , как показано на диаграмму фиг. 5. Они через регистр 39 поступают на входы эле0 ментов И 40 и 41, выполненных,например, на микросхеме К155ЛИ1 с одновибрэтором на одном (динамическом) входе. При рассмотрении работы блока 6 управления задержкой информации в регистре 39

5 пренебрегают.

На выходе элемента И 40 формируются импульсы Уи1 при окончании каждого периода сигнала Us в процессе увеличения перемещения X. На выходе элемента И 41

0 формируются импульсы иИ2 при окончании каждого периода сигнала Us в процессе уменьшения X. Знак направления перемещения фиксируется триггером 42 (сигнал UT на фиг. 5), который управляет коммутатором

5 43, объединяющим на своем выходе Е сигналы иИ1 и Un2. Управление коммутатором 43 осуществляется с задержкой, вносимой элементом 44 (сигнал Ur3 на фиг. 5). Задержка управления нужна для исключения из

0 выходной последовательности Е первого выходного импульса элемента 40 и 41 после смены направления перемещения. Исключение импульса необходимо, поскольку период, на котором произошел реверс, был

5 пройден не полностью и не должен быть отмечен импульсом Е.

Благодаря использованию регистра 39 формирование сигнала Е привязано к одним фронтам тактовой последовательности генератора 28, при этом изменение информации и выходных стробирующих сигналов АЦП привязано к другим фронтам тактовой последовательности. Этим обеспечивается исключение гонок в формирователях максимальных и минимальных кодов.

Предлагаемый преобразователь имеет повышенную точность благодаря компенсации погрешностей, вызванных неортогональностью фаз и неравенством амлитуд выходных сигналов СКД 1.

Формул а изобретения 1, Преобразователь перемещения в код, содержащий синусно-косинусный датчик перемещения, первый выход которого соединен с информационным входом первого аналого-цифрового преобразователя, прямым входом первого аналогового вычитате- ля и первым входом блока управления, а второй выход соединен с информационным входом второго аналого-цифрового преоб- разователя, прямым входом второго аналогового вычитателя и вторым входом блока управления, группа выходов первого аналого-цифрового преобразователя соединена с информационными входами первых форми- рователей максимальных и минимальных кодов, первые управляющие входы которых подключены к управляющему выходу первого аналого-цифрового преобразователя, выходы первого формирователя максимальных кодов и прямые выходы первого формирователя минимальных кодов соединены с входами первого сумматора, выходы которого через первый цифроанало- говый преобразователь соединены с инвер- сным входом первого аналогового вычитателя, выход которого соединен с информационным входом первого усилителя, группа выходов второго аналого-цифрового преобразователя соединена с информаци- онными входами вторых формирователей максимального и минимального кодов, первые управляющие входы которых подключены к управляющему выходу второго аналого-цифрового преобразователя, выхо- ды второго формирователя максимальных кодов соединены с первыми группами входов второго и третьего сумматоров, прямые и инверсные выходы второго формирователя минимальных кодов соединены с вторы- ми группами входов второго и третьего сумматоров соответственно, выходы второго сумматора через второй цифроаналоговый преобразователь соединены с инверсным входом второго аналогового вычитателя, вы- ход первого усилителя соединен с инверсным входом третьего аналогового вычитателя. выход которого соединен с информационным входом третьего аналого- цифрового преобразователя, генератор

импульсов, выход которого соединен с третьим входом блока управления и тактовыми входами первого, второго и третьего аналого-цифровых преобразователей, выход блока управления соединен с вторыми управляющими входами первых и вторых формирователей максимального и минимального кодов, интерполятор, отличающийся тем, что, с целью повышения точности преобразователя, в него введены четвертый сумматор, аналоговый сумматор, четвертый аналого-цифровой преобразователь, третий и четвертый формирователи максимального кода, второй, третий и четвертый усилители, прямые выходы первого формирователя максимальных кодов и инверсные выходы первого формирователя минимальных кодов соединены соответственно с первой и второй группой входов четвертого сумматора, выходы которого соединены с управляющими входами первого усилителя, выход второго аналогового вычитателя и выходы третьего сумматора соединены соответственно с информационным и управляющими входами второго усилителя, выход которого соединен с прямым входом третьего аналогового вычитэтеля и первым входом аналогового сумматора, второй вход которого подключен к выходу первого усилителя, выход аналогового сумматора соединен с информационными входами третьего усилителя и четвертого аналого- цифрового преобразователя, группа выходов и управляющий выход которого соединены соответственно с группой входов и первым управляющим входом третьего формирователя максимальных кодов, выходы которого соединены с управляющими входами третьего усилителя, группа выходов и управляющий выход третьего аналого-цифрового преобразователя соединены соответственно с группой входов и первым управляющим входом четвертого формирователя максимальных кодов, выходы которого соединены с управляющими входами четвертого усилителя, информационный вход четвертого усилителя подключен к выходу третьего аналогового вычитателя, выходы третьего и четвертого усилителей соединены с входами интерполятора, выход генератора импульсов соединен с тактовым входом четвертого аналого-цифрового преобразователя, а выход блока управления соединен с вторыми управляющими входами третьего и четвертого формирователей максимальных кодов. 2. Преобразователь по п. 1, о т л и ч a tout и и с я тем, что формирователь максимальных кодов содержит цифровой компаратор, первый и второй регистры,элемент И, первая группа входов цифрового компаратора является информационными входами формирователя максимальных кодов и соединена с информационными входами первого регистра, выходы которого соединены с информационными входами второго регистра и второй группой входов цифрового компаратора, выход цифрового компаратора соединен с одним входом элемента И, другой вход которого является первым управляющим входом формирователя максимальных кодов, а выход соединен с тактовым входом первого регистра, установочный вход первого регистра соединен с тактовым входом второго регистра и является вторым управляющим входом формирователя максимальных кодов, прямыми выходами которого являются выходы второго регистра.

3. Преобразователь поп. отличающийся тем, что формирователь минимальных кодов содержит цифровой компаратор, первый и второй регистры, элемент И, выходы первого регистра соединены с информационными входами второго регистра и первой группой входов цифрового компаратора, вторая группа входов которого является информационными входами формирователя минимальных кодов и соединена с информационными входами первого регистра, выход цифрового компаратора соединен с одним входом элемента И, другой вход которого является первым управляющим входом формирователя минимальных кодов, а выход соединен с тактовым входом первого регистра, установочный вход первого регистра соединен с тактовым входом второго регистра и является вторым управляющим входом формирователя минимальных кодов, прямыми и

инверсными выходами которого являются

соответствующие выходы второго регистра.

4. Преобразователь по п. 1, о т л и ч а ющи и с я тем, что блок управления содержит

первый и второй компараторы, регистр, первый и второй элементы И, триггер, коммутатор и элемент задержки, первые входы первого и второго компараторов являются соответственно первым и вторым входами блока управления, вторые входы первого и

второго компараторов подключены к общей шине, а выходы первого и второго компараторов соединены с соответствующими информационными входами регистра, тактовый вход которого является третьим

входом блока управления, выход первого разряда регистра соединен с прямым динамическим входом первого элемента И и инверсным динамическим входом второго элемента И, выход второго разряда регистра соединен с управляющими входами первого и второго элементов И, выходы первого и второго элементов И соединены с соответствующими входами триггера, выход которого через элемент задержки соединен с

управляющим входом коммутатора, первый и второй информационные входы коммутатора соединены с выходами соответственно второго и первого элементов И, а выход коммутатора является выходом блока управления.

29

V,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для кодирования аналоговых сигналов | 1989 |

|

SU1624696A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЛИНЕЙНЫХ ПЕРЕМЕЩЕНИЙ | 1991 |

|

RU2078302C1 |

| УЛЬТРАЗВУКОВОЙ ЭХОИМПУЛЬСНЫЙ ТОЛЩИНОМЕР | 2003 |

|

RU2246694C1 |

| Устройство для измерения экстремумов | 1983 |

|

SU1108465A1 |

| Устройство для определения экстремумов | 1981 |

|

SU985749A1 |

| Способ преобразования угла поворота вала в код и устройство для его осуществления | 1987 |

|

SU1457165A1 |

| ЦИФРОВОЙ ПРИЕМНИК СПУТНИКОВОЙ НАВИГАЦИИ | 1995 |

|

RU2090902C1 |

| Многоканальный преобразователь перемещения в код | 1987 |

|

SU1495994A1 |

| УСТРОЙСТВО КОРРЕКЦИИ ФОРМЫ КРИВОЙ НАПРЯЖЕНИЯ | 2014 |

|

RU2580944C1 |

| Устройство стабилизации динамического диапазона сигнала | 1986 |

|

SU1480096A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. С целью повышения точности путем дополнительной коррекции неортогональности фаз и выравнивания амплитуд сигналов в преобразователь, содержащий синусно-косинусный датчик (СКД) перемещений, три аналого-цифровых преобразователя, три аналоговых вычитателя, два формирователя максимальных кодов, два формирователя минимальных кодов, три сумматора, два цифроаналоговых преобразователя, усилитель, интерполятор, генератор импульсов, блок управления, введены четвертый сумматор, аналоговый сумматор, четвертый аналого-цифровой преобразователь, третий и четвертый формирователи максимальных кодов и три усилителя. В преобразователе измеряют постоянные и переменные составляющие выходных сигналов СКД. выравнивают амплитуды переменных составляющих синусных и косинусных сигналов, путем взаимного суммирования и вычитания этих сигналов компенсируют неортогональность и дополнительно выравнивают амплитуды синусно-косинусных сигналов. 3 з. п. ф-лы, 5 ил. ё

А

С. Ј.

-33

34

с,.

I Фиг.4

I

0

М

mffif

30

31

32

R6

и

V,

i/m rtl

35

Ьб

14

с

К

о

Ifc ч,

И,

ч.

1/г

ч,

f

| Преснухин Л | |||

| Н | |||

| и др | |||

| Фотоэлектрические преобразователи информации | |||

| М.: Машиностроение, 1974, с | |||

| ПЕЧНОЙ ЖЕЛЕЗНЫЙ РУКАВ (ТРУБА) | 1920 |

|

SU199A1 |

| Клапанный регулятор для паровозов | 1919 |

|

SU103A1 |

| ФОТОЭЛЕКТРИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ «ПЕРЕМЕЩЕНИЕ —ФАЗА» | 0 |

|

SU238245A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Запальная свеча для двигателей | 1924 |

|

SU1967A1 |

Авторы

Даты

1991-06-15—Публикация

1989-06-01—Подача