00

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УСКОРЕННОЙ СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2011 |

|

RU2446560C1 |

| Цифровой согласованный фильтр сигналов с дискретной частотной манипуляцией | 1986 |

|

SU1438017A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1984 |

|

SU1187157A1 |

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1992 |

|

RU2114514C1 |

| Генератор гармонических сигналов | 1989 |

|

SU1626379A1 |

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

| УСТРОЙСТВО КОНТРОЛЯ ОШИБОК В ЦИФРОВЫХ СИСТЕМАХ ПЕРЕДАЧИ НА БАЗЕ ТЕХНОЛОГИИ АТМ | 2009 |

|

RU2408985C2 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Ранговый обнаружитель сигналов | 1981 |

|

SU970291A1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение точности стабилизации при одноканальном и многоканальном источниках входного сигнала. Устройство стабилизации содержит мультиплексор 1, эл-т 2 с регулируемым коэф.передачи, сумматоры 3, 9 и 15, АЦП 4, блок выделения 5 минимального и максимального уровней сигнала, вычитатели 6, 7, 16, 18 и 20, весовой усилитель 8, перемножители 10 и 17, эл-ты постоянной памяти 11 и 19, цифровой компаратор 12, эл-ты памяти 13 и 21, дешифратор 14, ЦАП 22 и блок формирования 23 управляющих импульсов. Устройство имеет два режима работы: режим калибровки и рабочий режим. При многоканальном источнике входного сигнала осуществляется опрос всех источников сигнала и цикл процесса калибровки повторяется. В рабочем режиме сигналы не формируются, а лишь происходит считывание информации из эл-тов памяти 13 и 21. Цель достигается за счет использования цифровых эл-тов и введения поправки при определении величины смещения, обусловленной тем, что сумматор 3 включен после эл-та 2, а также за счет простоты ступенчатой аппроксимации гиперболической регулировочной характеристики эл-та 2. 1 з.п.ф-лы, 7 ил.

Фиг.1 f t

CD О

Изобретение относится к радиотехнике, в частности к системам автоматической регулировки усиления, и может быть использовано при калибровке коэффициентов передачи каналов

Цель изобретения - повышение точности, а также повышение точности при многоканальном источнике входного сигнала.

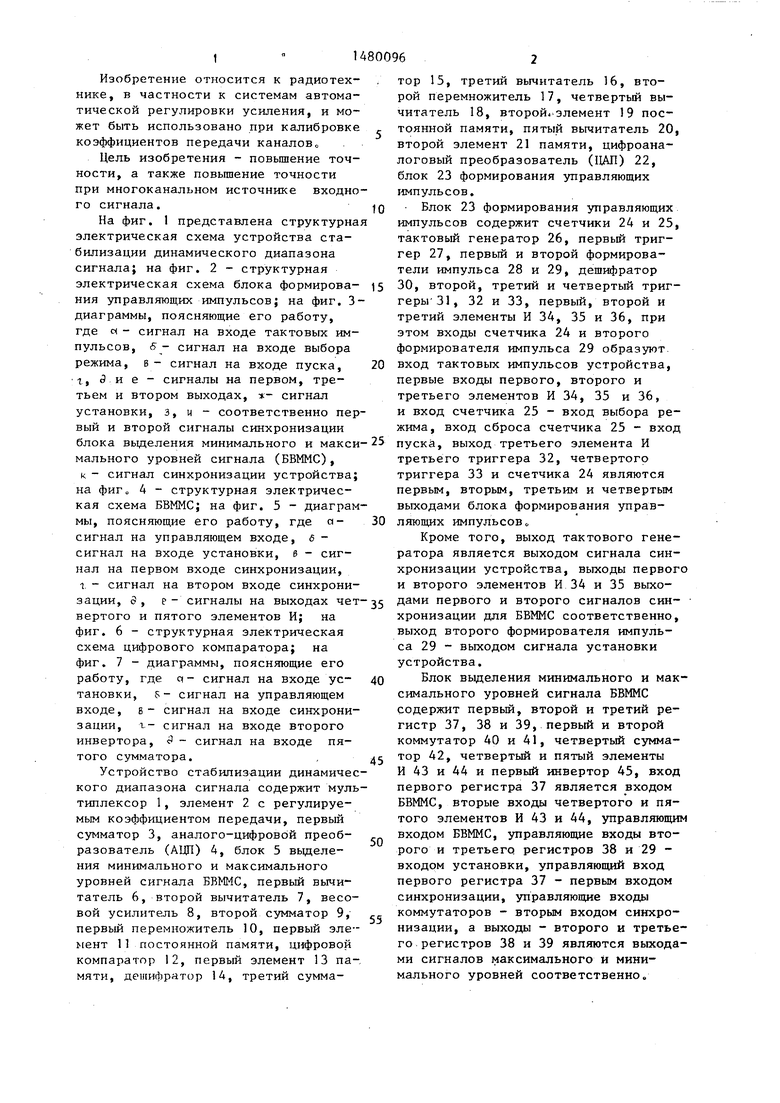

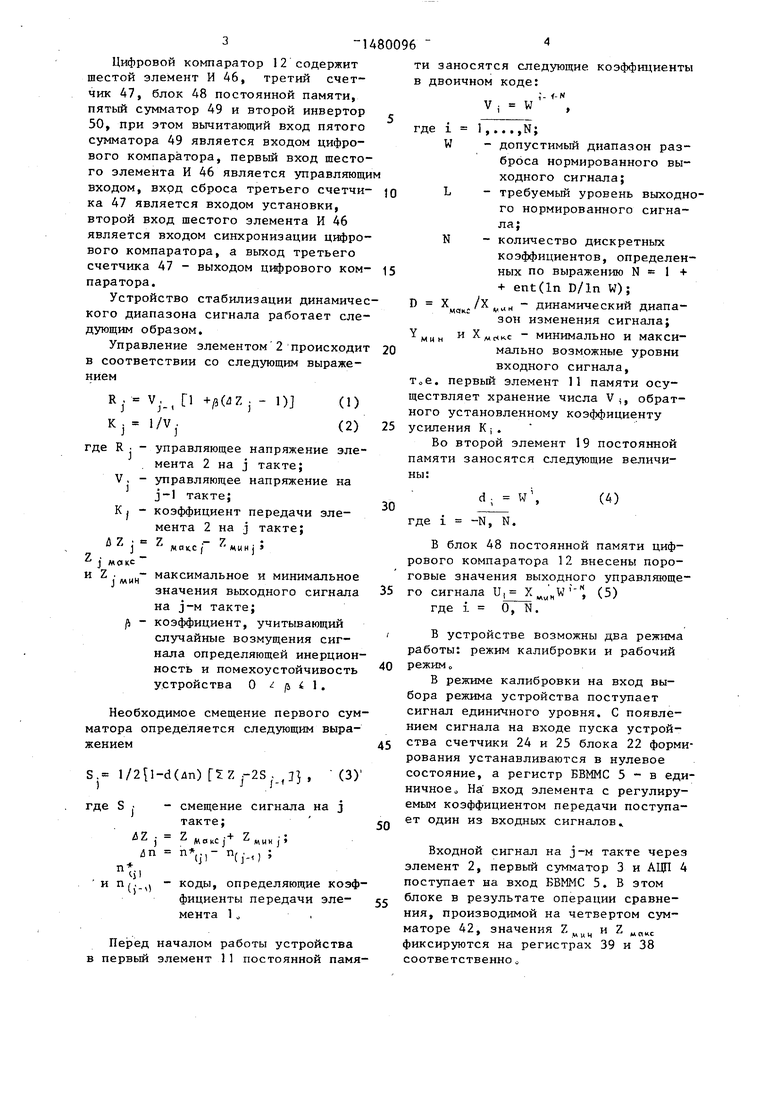

На фиг. 1 представлена структурная электрическая схема устройства стабилизации динамического диапазона сигнала; на фиг. 2 - структурная электрическая схема блока формирова- ния управляющих импульсов; на фиг. 3- диаграммы, поясняющие его работу, где « - сигнал на входе тактовых импульсов, б- сигнал на входе выбора режима, ъ - сигнал на входе пуска, t, 3 и е - сигналы на первом, треБлок 23 формирования управляющ импульсов содержит счетчики 24 и тактовый генератор 26, первый три гер 27, первый и второй формирова тели импульса 28 и 29, дешифратор 30, второй, третий и четвертый тр геры 31, 32 и 33, первый, второй третий элементы И 34, 35 и 36, пр этом входы счетчика 24 и второго формирователя импульса 29 образую вход тактовых импульсов устройств первые входы первого, второго и третьего элементов И 34, 35 и 36 и вход счетчика 25 - вход выбора

жима, вход сброса счетчика 25 - в

тьем и втором выходах, - сигнал установки, з, и - соответственно первый и второй сигналы синхронизации блока выделения минимального и макси-25 пуска, выход третьего элемента И мального уровней сигнала (БВММС), третьего триггера 32, четвертого к - сигнал синхронизации устройства; на фиг о 4 - структурная электрическая схема БВММС; на фиг. 5 - диаграмтриггера 33 и счетчика 24 являютс первым, вторым, третьим и четверт выходами блока формирования управ ляющих импульсов„

мы, поясняющие его работу, где а

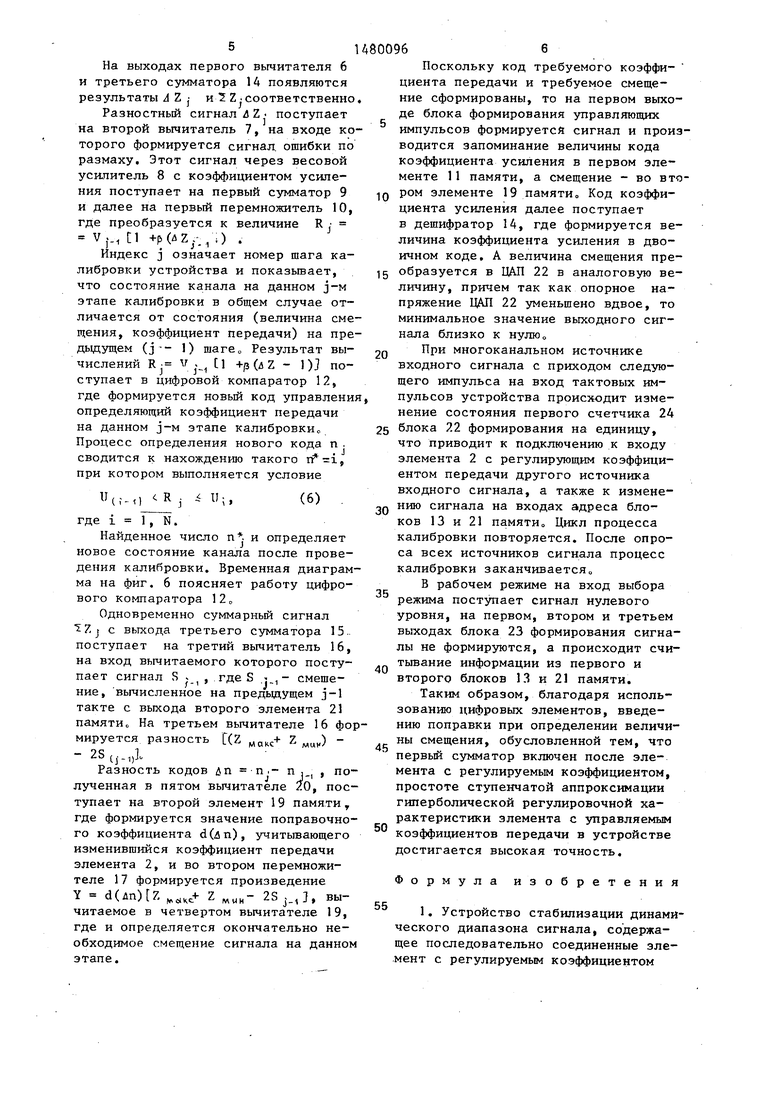

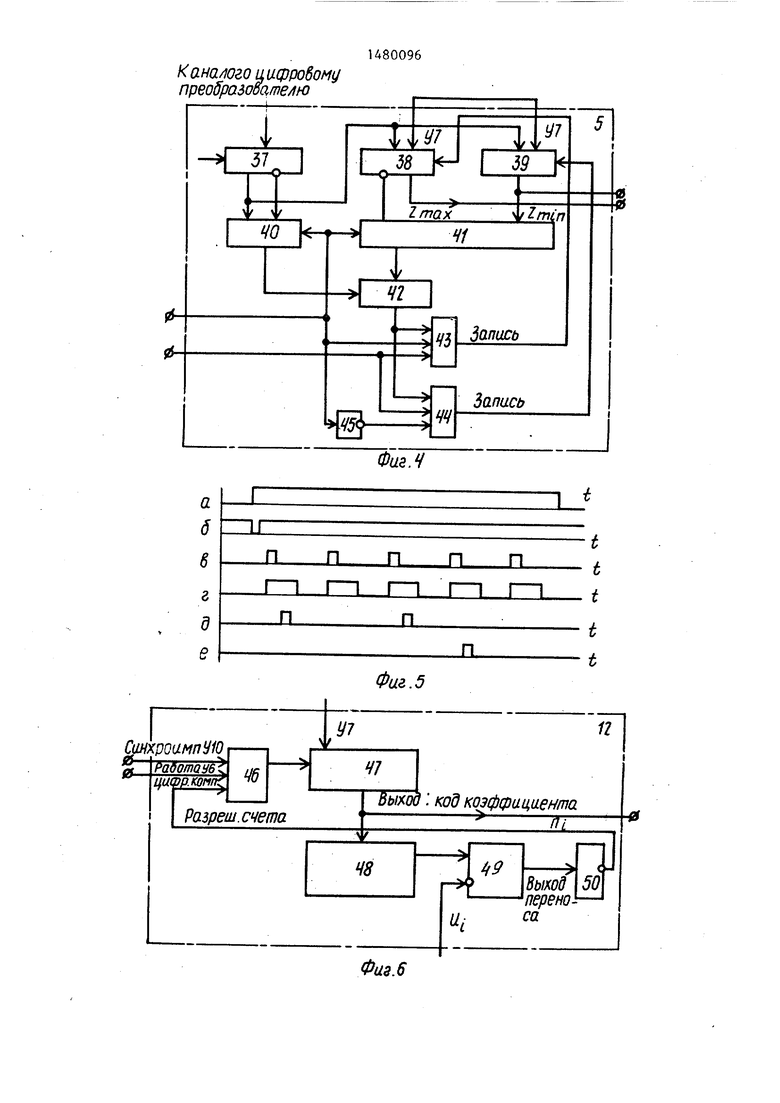

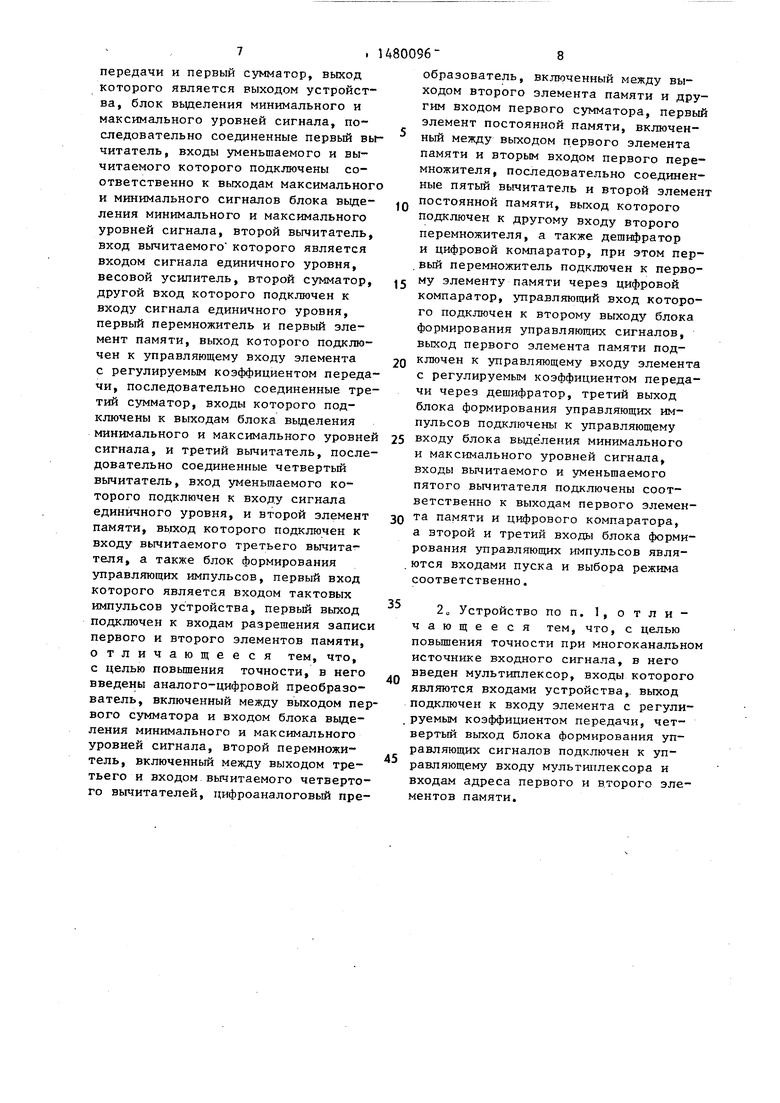

сигнал на управляющем входе, б - сигнал на входе установки, в - сигнал на первом входе синхронизации, т - сигнал на втором входе синхронизации, 3, е- сигналы на выходах чет вертого и пятого элементов И; на фиг. 6 - структурная электрическая схема цифрового компаратора; на фиг. 7 - диаграммы, поясняющие его работу, где q- сигнал на входе установки, 5- сигнал на управляющем входе, в - сигнал на входе синхронизации, г- сигнал на входе второго инвертора, d - сигнал на входе пятого сумматора.

Устройство стабилизации динамического диапазона сигнала содержит мультиплексор 1, элемент 2 с регулируемым коэффициентом передачи, первый сумматор 3, аналого-цифровой преобразователь (АЦП) 4, блок 5 выделения минимального и максимального уровней сигнала ББММС, первый вычитатель 6, второй вычитатель 7, весовой усилитель 8, второй сумматор 9, первый перемножитель 10, первый элемент 11 постоянной памяти, цифровой компаратор 12, первый элемент 13 памяти, дешифратор 14, третий сумма

тор 15, третий вычитатель 16, второй перемножитель 17, четвертый вычитатель 18, второй элемент 19 постоянной памяти, пятый вычитатель 20, второй элемент 21 памяти, цифроана- логовый преобразователь (ЦДЛ) 22, блок 23 формирования управляющих импульсов.

Блок 23 формирования управляющих импульсов содержит счетчики 24 и 25, тактовый генератор 26, первый триггер 27, первый и второй формирователи импульса 28 и 29, дешифратор 30, второй, третий и четвертый триггеры 31, 32 и 33, первый, второй и третий элементы И 34, 35 и 36, при этом входы счетчика 24 и второго формирователя импульса 29 образуют вход тактовых импульсов устройства, первые входы первого, второго и третьего элементов И 34, 35 и 36, и вход счетчика 25 - вход выбора репуска, выход третьего элемента И третьего триггера 32, четвертого

жима, вход сброса счетчика 25 - вход

пуска, выход третьего элемента И третьего триггера 32, четвертого

5 пуска, выход третьего элемента И третьего триггера 32, четвертого

0

0

5

5

0

5

триггера 33 и счетчика 24 являются первым, вторым, третьим и четвертым выходами блока формирования управляющих импульсов„

Кроме того, выход тактового генератора является выходом сигнала синхронизации устройства, выходы первого и второго элементов И 34 и 35 выходами первого и второго сигналов синхронизации для БВММС соответственно, выход второго формирователя импульса 29 - выходом сигнала установки устройства.

Блок выделения минимального и максимального уровней сигнала БВММС содержит первый, второй и третий регистр 37, 38 и 39, первый и второй коммутатор 40 и 41, четвертый сумматор 42, четвертый и пятый элементы И 43 и 44 и первый инвертор 45, вход первого регистра 37 является входом БВММС, вторые входы четвертого и пятого элементов И 43 и 44, управляющим входом БВММС, управляющие входы второго и третьего регистров 38 и 29 - входом установки, управляющий вход первого регистра 37 - первым входом синхронизации, управляющие входы коммутаторов - вторым входом синхронизации, а выходы - второго и третьего регистров 38 и 39 являются выходами сигналов максимального и минимального уровней соответственно.

3-14

Цифровой компаратор 12 содержит шестой элемент И 46, третий счетчик 47, блок 48 постоянной памяти, пятый сумматор 49 и второй инвертор 50, при этом вычитающий вход пятого сумматора 49 является входом цифрового компаратора, первый вход шестого элемента И 46 является управляющи входом, вход сброса третьего счетчи- ка 47 является входом установки, второй вход шестого элемента И 46 является входом синхронизации цифрового компаратора, а выход третьего счетчика 47 - выходом цифрового ком- паратора.

Устройство стабилизации динамического диапазона сигнала работает следующим образом.

Управление элементом 2 происходит в соответствии со следующим выражением

V.

}1/V,

1 +/3(dZj - OJ

(1)

(2)

J

R ; - управляющее напряжение элемента 2 на j такте; управляющее напряжение на j-1 такте;

коэффициент передачи элемента 2 на j такте;

V.

К, Д Z

J

Z

j «оке ZJMHH/ - 7

NOK.C ( ММН j

максимальное и минимальное значения выходного сигнала на j-м такте; коэффициент, учитывающий случайные возмущения сигнала определяющей инерционность и помехоустойчивость устройства 0 /& 1 .

Необходимое смещение первоматора определяется следующим жением

s. i/2{i-d An) zj-2s/ f:},

где S

Zj&n

смещение сигнала такте;

7 +7

Ј м о кс jт

п,.,- п.

МНИ J

ф

Ф

П(, -0

коды, определяющие коэффициенты передачи эле- 55 мента 1„

Перед началом работы устройства в первый элемент 11 постоянной памяти заносятся следующие коэффициенты в двоичном коде:

, - f-N

V i W

де

W

N

X

1,...,N;

-допустимый диапазон разброса нормированного выходного сигнала;

-требуемый уровень выходного нормированного сигнала;

-количество дискретных коэффициентов, определенных по выражению N 1 + + ent(ln D/ln W);

VXMWH динамический диапазон изменения сигнала;

мнн и Х/мсчкс - минимально и максимально возможные уровни входного сигнала,

т0е. первый элемент 11 памяти осуществляет хранение числа V, обратного установленному коэффициенту усиления К j.

Во второй элемент 19 постоянной памяти заносятся следующие величины:

30

d . W

(4)

где i -N, N.

В блок 48 постоянной памяти цифрового компаратора 12 внесены пороговые значения выходного управляющего сигнала U, XWUH где I О, N.

W

;-N

(5)

0

5

0

5

В устройстве возможны два режима работы: режим калибровки и рабочий режим

В режиме калибровки на вход выбора режима устройства поступает сигнал единичного уровня. С появлением сигнала на входе пуска устройства счетчики 24 и 25 блока 22 формирования устанавливаются в нулевое состояние, а регистр БВММС 5 - в единичное На вход элемента с регулируемым коэффициентом передачи поступает один из входных сигналов

Входной сигнал на j-м такте через элемент 2, первый сумматор 3 и АЦП 4 поступает на вход БВММС 5. В этом блоке в результате операции сравнения, производимой на четвертом сумматоре 42, значения ZMU4 и Z Maiic фиксируются на регистрах 39 и 38 соответственно„

На выходах первого вычитателя 6 и третьего сумматора 14 появляются результаты A Z j и 2 Z Соответственно,

Разностный сигнал &Z поступает на второй вычитатель 7, на входе которого формируется сигнал, ошибки по размаху. Этот сигнал через весовой усилитель 8 с коэффициентом усиления поступает на первый сумматор 9 и далее на первый перемножитель 10, где преобразуется к величине R у V-., 1 +p(AZ/-.1 ,) .

Индекс j означает номер шага калибровки устройства и показывает, что состояние канала на данном j-м этапе калибровки в общем случае отличается от состояния (величина смещения, коэффициент передачи) на предыдущем (j - 1) шаге„ Результат вычислений Rj v H tl +p(iZ - 1)J поступает в цифровой компаратор 12, где формируется новый код управления определяющий коэффициент передачи на данном j-м этапе калибровки„ Процесс определения нового кода п . сводится к нахождению такого , при котором выполняется условие

R

i U

(6)

где i 1, N.

Найденное число п. и определяет новое состояние канала после проведения калибровки. Временная диаграмма на фиг. 6 поясняет работу цифрового компаратора 12„

Одновременно суммарный сигнал Zj с выхода третьего сумматора 15. поступает на третий вычитатель 16, на вход вычитаемого которого поступает сигнал S ч , гдеS ,- смешение, вычисленное на предыдущем j-1 такте с выхода второго элемента 21 памяти На третьем вычитателе 16 формируется разность (Z макс+ Z MUH) - - 2S (j-uL

Разность кодов дп

п ,- лученная в пятом вычитателе

п

J-, , ПО20, поступает на второй элемент 19 памятит где формируется значение поправочного коэффициента dCfln), учитывающего изменившийся коэффициент передачи элемента 2, и во втором перемножителе 17 формируется произведение Y d(An)Z KC+ Z MWH- 28,3, вы- читаемое в четвертом вычитателе 19, где и определяется окончательно необходимое смещение сигнала на данном этапе.

5

0

Поскольку код требуемого коэффициента передачи и требуемое смещение сформированы, то на первом выходе блока формирования управляющих импульсов формируется сигнал и производится запоминание величины кода коэффициента усиления в первом элементе 11 памяти, а смещение - во втором элементе 19 памяти Код коэффициента усиления далее поступает в дешифратор 14, где формируется величина коэффициента усиления в двоичном коде, А величина смещения преобразуется в ЦДЛ 22 в аналоговую величину, причем так как опорное напряжение ПАП 22 уменьшено вдвое, то минимальное значение выходного CHI- нала близко к нулю

При многоканальном источнике входного сигнала с приходом следующего импульса на вход тактовых импульсов устройства происходит изменение состояния первого счетчика 24 5 блока 22 формирования на единицу, что приводит к подключению к входу элемента 2 с регулирующим коэффициентом передачи другого источника входного сигнала, а также к изменению сигнала на входах адреса блоков 13 и 21 памяти„ Цикл процесса калибровки повторяется. После опроса всех источников сигнала процесс калибровки заканчивается

В рабочем режиме на вход выбора режима поступает сигнал нулевого уровня, на первом, втором и третьем выходах блока 23 формирования сигналы не формируются, а происходит считывание информации из первого и второго блоков 13 и 21 памяти.

Таким образом, благодаря использованию цифровых элементов, введению поправки при определении величины смещения, обусловленной тем, что первый сумматор включен после элемента с регулируемым коэффициентом, простоте ступенчатой аппроксимации гиперболической регулировочной характеристики элемента с управляемым коэффициентов передачи в устройстве достигается высокая точность.

0

5

0

5

0

Формула изобретения

передачи и первый сумматор, выход которого является выходом устройства, блок выделения минимального и максимального уровней сигнала, последовательно соединенные первый вы- читатель, входы уменьшаемого и вычитаемого которого подключены соответственно к выходам максимального и минимального сигналов блока выделения минимального и максимального уровней сигнала, второй вычитатель, вход вычитаемого которого является входом сигнала единичного уровня, весовой усилитель, второй сумматор, другой вход которого подключен к входу сигнала единичного уровня, первый перемножитель и первый элемент памяти, выход которого подключен к управляющему входу элемента с регулируемым коэффициентом передачи, последовательно соединенные третий сумматор, входы которого подключены к выходам блока выделения минимального и максимального уровней сигнала, и третий вычитатель, последовательно соединенные четвертый вычитатель, вход уменьшаемого которого подключен к входу сигнала единичного уровня, и второй элемент памяти, выход которого подключен к входу вычитаемого третьего вычита- теля, а также блок формирования управляющих импульсов, первый вход которого является входом тактовых импульсов устройства, первый выход подключен к входам разрешения записи первого и второго элементов памяти, отличающееся тем, что, с целью повышения точности, в него введены аналого-цифровой преобразователь, включенный между выходом первого сумматора и входом блока выделения минимального и максимального уровней сигнала, второй перемножитель, включенный между выходом третьего и входом вычитаемого четвертого вычитателей, циФроаналоговый пре10

15

480096-8

образователь, включенный между выходом второго элемента памяти и другим входом первого сумматора, первый элемент постоянной памяти, включенный между выходом первого элемента памяти и вторым входом первого пере- множителя, последовательно соединенные пятый вычитатель и второй элемент постоянной памяти, выход которого подключен к другому входу второго перемножителя, а также дешифратор и цифровой компаратор, при этом первый перемножитель подключен к первому элементу памяти через цифровой компаратор, управляющей вход которого подключен к второму выходу блока формирования управляющих сигналов, выход первого элемента памяти подключен к управляющему входу элемента с регулируемым коэффициентом передачи через дешифратор, третий выход блока формирования управляющих импульсов подключены к управляющему 25 входу блока выделения минимального и максимального уровней сигнала, входы вычитаемого и уменьшаемого пятого вычитателя подключены соответственно к выходам первого элемента памяти и цифрового компаратора, а второй и третий входы блока формирования управляющих импульсов являются входами пуска и выбора режима соответственно.

20

30

2 о Устройство по п. отличающееся тем, что, с целью повышения точности при многоканальном источнике входного сигнала, в него введен мультиплексор, входы которого являются входами устройства, выход подключен к входу элемента с регулируемым коэффициентом передачи, четвертый выход блока формирования управляющих сигналов подключен к управляющему входу мультиплексора и входам адреса первого и второго элементов памяти.

К ана/юго цифровому преобразователю

1

-л.

HoJ

v w

f

-

п п п п п

п

п

п.

ll#7 Зй N-J

/

У7

% K-J LjOrn

-

I

41

V3

Запись

W

Запись

Фиа.У

п п

п.

t t t

t t

Фаг.5

Фаз.6

Фиг.7

| Устройство стабилизации динамического диапазона сигнала | 1985 |

|

SU1298857A1 |

Авторы

Даты

1989-05-15—Публикация

1986-08-01—Подача