Изобретение относится к технике электросвязи и может использоваться в системах передачи дискретной информации и телеграфии.

Цель изобретения - повышение помехозащищенности.

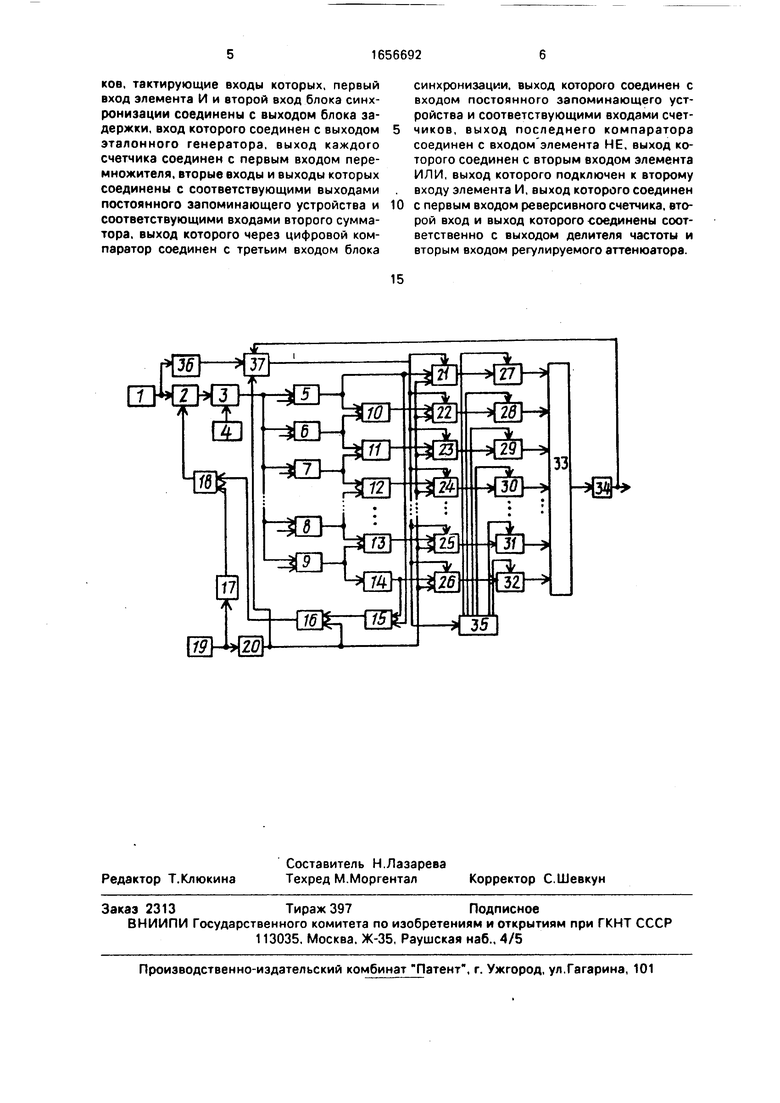

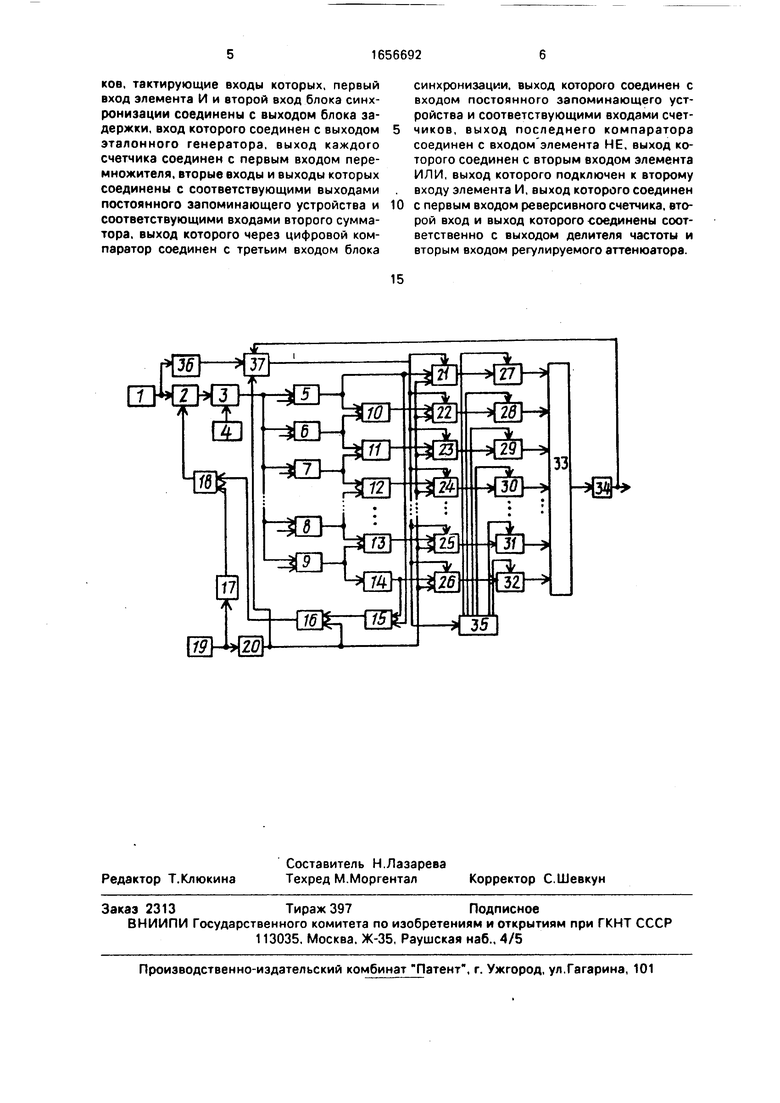

На чертеже изображена структурная электрическая схема предлагаемого приемника.

Приемник содержит фильтр 1 нижних частот, регулируемый аттенюатор 2, первый сумматор 3, генератор 4 вспомогательного шума, N+2 компараторов 5-9, N+1 сумматоров 10-13 по модулю два, элемент НЕ 14, элемент ИЛИ 15, элемент И 16, делитель 17 частоты, реверсивный счетчик 18, эталонный генератор 19, блок 20 задержки, N+3 счетчиков 21-26, N+3 переключателей 27- 32, второй сумматор 33, цифровой компаратор 34, постоянное запоминающее устройство 35, ограничитель 36 уровня, блок 37 синхронизации.

Приемник работает следующим образом.

На вход приемника поступает смесь сигнала и помехи. После прохождения фильтра 1 она поступает на регулируемый аттенюатор 2, коэффициент ослабления которого определяется кодом старших разрядов реверсивного счетчика 18, включенного в цепь обратной связи приемника. Стабилизированная по уровню смесь поступает на вход сумматора 3 (аналогового), где к ней добавляется вспомогательное шумовое напряжение смещения с амплитудой , которое формируется генератоО

ел а а о ю

ром 4. Вспомогательное напряжение добавляется для того, чтобы избежать возможного подавления сигнала мощной помехой при ограничении в компараторах. Сформированное таким образом напряжение подается на неинвертирующие входы N+ 2 компараторов 5-9, на инвертирующие входы которых подаются постоянные напряжения Ui/U2 ...UN+ 2 от источника питания, причем Ui-U2 U2-U3...UN-H-UN+2 AU.

Сигналы с выходов компараторов в виде логических уровней подаются на входы N+1 сумматоров 10-13, причем на каждый из блоков поступают сигналы с выходов соседних компараторов (т.е. имеющих напряжения срабатывания, отличающиеся на Ли). Сигналы с выхода сумматоров 10-13 определяют время нахождения т смеси сигнала, помехи и вспомогательного шумового напряжения в 1-й внутренней зоне между значениями Ui и Ui-1 (, N+2) за время, равное длительности двоичного символа информации т . Сигнал с выхода компаратора 5 определяет время нахождения смеси выше уровня Ui за время т , а сигнал с выхода элемента НЕ 14 - время нахождения смеси ниже уровня UN+З за время г . Очевидно

N -1-3

2

I 1

Каждый из счетчиков 21-26 подсчитывает число импульсов эталонного генератора 19 за время нахождения смеси в 1-й зоне, т.е. формирует оценку т в двоичном коде. По сигналу синхронизации,подаваемому на установочный вход каждого счетчика с выхода блока 37 в момент окончания двоичного символа, код, накопленный в каждом счетчике, умножается в соответствующем перемножителе на свой коэффициент bi. хранящийся в постоянном запоминающем устройстве 35. Выборка соответствующих коэффициентов из постоянного запоминающего устройства 35 производится по сигналу (импульсу считывания), подаваемому на его тактовый вход от блока 37. Этот сигнал аналогичен сигналу, подаваемому на установочные входы счетчиков. Данное постоянное запоминающее устройство является безадресным: каждый коэффициент по своей шине подается на вход соответствующего перемножителя в момент поступления импульса считывания. При этом содержимое каждого счетчика обнуляется. Результаты N+3 перемножений суммируются в сумматоре 33 (цифровом) полученная сумма сравнивается с нулевым порогом в цифровом компараторе 34, на выходе которого формируется оценка двоичного символа.

Цепь обратной связи работает следующим образом. Сигналы с выходов компаратора 5 и элемента НЕ 14 определяют суммарное время нахождения смеси внеин- тервала напряжений 1)м+2, Ui . Объединяя в элементе ИЛИ 15, эти сигналы поступают на первый вход элемента Т 16, на второй вход которого поступают импульсы с выхода эталонного генератора 19, задержанные в

блоке 20 на время -1 , где тэт - период

следования импульсов эталонного генератора 19. Импульсы с выхода элемента И 16 поступают на вход обратного счета ревер- 5 сивного счетчика 18, на вход прямого счета которого поступают импульсы эталонного генератора 19, прошедшие через делитель

17.Блок 20 необходим для избежания возможности одновременного поступления им0 пульсов на оба входа реверсивного счетчика

18.Код старших разрядов реверсивного счетчика 18 управляет коэффициентом ослабления дискретного регулируемого аттенюатора 2, через который замыкается

5 цепь обратной связи приемника.Таким образом, цепь обратной связи поддерживает постоянным время нахождения смеси вне интервала и|м- 2,и1. которое определяется коэффициентом деления делителя

0 17 частоты.

Формула изобретения Приемник двоичных символов, содержащий последовательно соединенные фильтр нижних частот, ограничитель уровня

5 и блок синхронизации, эталонный генератор, выход которого соединен с входом делителя частоты, первый компаратор, выход которого соединен с первым входом эле0 мента ИЛИ, элемент И, реверсивный счетчик, отличающийся тем, что, с целью повышения помехозащищенности, в него введены регулируемый аттенюатор, первый сумматор, генератор вспомогательного шу5 ма, блок задержки, N компараторов, N+1 сумматоров по модулю два, N+3 счетчиков, N+3 перемножителей, второй сумматор, цифровой компаратор и постоянное запоминающее устройство, причем выход

0 фильтра нижних частот через регулируемый аттенюатор соединен с первым входом первого сумматора, второй вход которого соединен с выходом генератора вспомогательного шума, выход первого сум5 матора соединен с входами всех компараторов, выход каждого из которых соединен с соответствующими входами двух соседних сумматоров по модулю два, выходы каждого сумматора по модулю два и выходы первого компаратора и элемента НЕ соединены со счетными входами соответствующих счетчиков, тактирующие входы которых, первый вход элемента И и второй вход блока синхронизации соединены с выходом блока задержки, вход которого соединен с выходом эталонного генератора, выход каждого счетчика соединен с первым входом перемножителя, вторые входы и выходы которых соединены с соответствующими выходами постоянного запоминающего устройства и соответствующими входами второго сумматора, выход которого через цифровой компаратор соединен с третьим входом блока

0

синхронизации, выход которого соединен с входом постоянного запоминающего устройства и соответствующими входами счетчиков, выход последнего компаратора соединен с входом элемента НЕ, выход которого соединен с вторым входом элемента ИЛИ, выход которого подключен к второму входу элемента И, выход которого соединен с первым входом реверсивного счетчика, второй вход и выход которого соединены соответственно с выходом делителя частоты и вторым входом регулируемого аттенюатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Приемник двоичных символов | 1985 |

|

SU1261137A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1318925A1 |

| Аудиометр | 1988 |

|

SU1531990A1 |

| НУЛЕВОЙ РАДИОМЕТР | 1996 |

|

RU2124213C1 |

| Адаптивный групповой приемник многочастотного кода с импульсно-кодовой модуляцией | 1989 |

|

SU1830632A1 |

| Устройство для управления погружной насосной установкой | 1982 |

|

SU1281747A1 |

| Адаптивный корректор для системы передачи многоуровневых сигналов | 1975 |

|

SU559399A1 |

| Измеритель комплексных параметров СВЧ-четырехполюсника | 1989 |

|

SU1800394A1 |

| Устройство регулирования компенсатора реактивной мощности | 1990 |

|

SU1830524A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

Изобретение относится к электросвязи. Цель изобретения - повышение помехозащищенности. Приемник содержит фильтр 1 нижних частот, регулируемый аттенюатор 2, сумматоры 3 и 33, генератор 4 вспомогательного шума, компараторы 5-9, сумматоры 10-13 по модулю два, элемент НЕ 14, элемент ИЛ И 15, элемент И 16, делитель 17 частоты, реверсивный счетчик 18, эталонный генератор 19, блок 20 задержки, счетчики 21-26, переключатели 27-32, цифровой компаратор 34, постоянное запоминающее устройство 35, ограничитель 36 уровня и блок 37 синхронизации. Входная смесь сигнала и помехи через фильтр 1 поступает на аттенюатор 2, коэффициент ослабления которого определяется кодом счетчика 18, включенного в цепь обратной связи приемника. Эта цепь поддерживает постоянным время нахождения смеси вне заданного интервала, которое определяется коэффициентом деления делителя 17. К стабилизированной по уровню смеси далее добавляется вспомогательное шумовое напряжение для того, чтобы избежать возможного подавления сигнала мощной помехой при ограничении в компараторах 5-9. Путем последующих преобразований на выходе приемника формируется оценка двоичного символа информации. 1 ил. Ё

| Приемник двоичных символов | 1985 |

|

SU1261137A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-06-15—Публикация

1989-06-08—Подача