113

Изобретение относится к радиотехнике и может быть использовано при создании анализаторов спектра сигнала, работаюпщх при разных диапазонах анализа и с различной разрешающей способностью.

Целью изобретения является расширение функциональных возможностей цифрового анализатора спектра за счет реализации возможности изменения диапазона анализа и разрешающей способности анализатора.

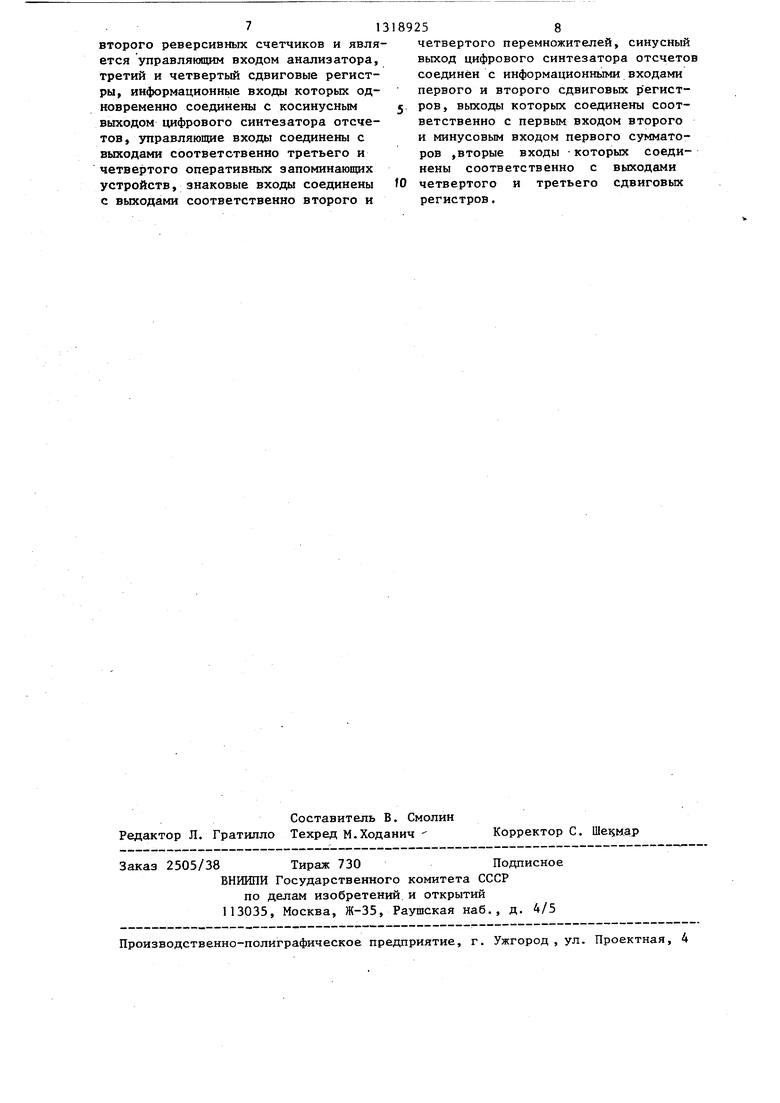

На чертеже приведена блок-схема цифрового анализатора спектра.

Цифровой анализатор спектра содержит квадратурный преобразователь 1, первый и второй бинарные аналого-цифровые преобразователи (АЦП) 2 и 3, первый. и второй реверсивные счетчики А и 5, формирователь 6 порога, гтервый, второй, третий, четвертый, пятый, шестой цифровые компараторы 7-12, первый и второй элементы ИЛИ 13 и 14, первое, второе, третье, четвертое оперативное запоминающее устройство (ОЗУ) 15-18, ггервый, второй, третий, четвертый перемножители 19- 22, цифровой синтезатор отсчетов (ЦСО) 23, первый, второй, третий, четвертый сдвиговые регистры 24-27, первый л второй сумматоры 28 и 29, первый и второй накопительные сумматора 30 и 31, вычислитель 32 модуля.

Входом анализатора является вход квадратурного преобразователя 1, первый и второй выходы которого соединены с входами соответственно первого и второго бинарных АЦП 2 и 3, выходы которых соединены с первыми входами соответственно первого и второго реверсивных счетчиков 4 и 5, вторые входы первого и второго реверсивных счетчиков 4 и 5 соединены одновременно с входом формирователя 6 порога, являющегося одновременно управляющим входом анализатора. Первый, второй, третий выходы формирователя 6 порога соединены с вторыми входами соответственно первого и шестого (7 и 12), третьего и четвертого (9 и 10), второго и пятого (8 и 11) цифровых компараторов. Первые входы первого, второго и третьего цифровых компараторов 7-9 одновременно соединены с выходом первого реверсивного счетчика 4, а первые входы четвертого, пятого и шестого цифровых компараторов 10-12 одновременно соединены

52

с выходом второго реверсивного счетчика 5. .Выходы первого и третьего цифровых компараторов 7 и 9 соединены соответственно с первым и вторым

входами первого элемента ИЛИ 13.

Выходы четвертого и шестого цифровых компараторов 10 и 12 соединены соответственно с первым и вторым вхоами второго элемента ИЛИ 14. Выходы

второго и пятого цифровых компараторов 8 и 1I соединены с входами соответственно первого и второго ОЗУ 15 и 16. Выход первого ОЗУ 15 одновременно соединен с первыми входами первого и второго перемножителей 19 и 20. Выход второго ОЗУ 16 одновременно соединен с первыми входами третьего и четвертого перемножителей 21 и 22. Вторые входы первого и третьего перемножителей 19 и 21 одновременно соединены со знаковым синусным выходом ЦСО 23, знаковый косинусный выход которого одновременно соединен с вторыми входами второго, и четвертого перемножителей 20 и 22. Синусный выход ЦСО 23 соединен одновременно с третьими входами первого и вторрго сдвиговых регистров 24 и 25, а косинусный выход - с первыми входами третьего и четвертого сдвиговых регистров 26 и 27. Вход третьего ОЗУ 17, выход которого одновременно соединен с первым сдвиговым регистром 24 и вторым входом третьего сдвигового

регистра 26, соединен с выходом первого элемента ИЛИ 13. Вход четвертого ОЗУ 18, вь1ход которого бдновре- менно соединен с вторым сдвиговым регистром 25 и вторым входом четвертого сдвигового регистра 27, соединен с выходом второго элемента или 14. . Выходы первого, второго, третьего и четвертого перемножителей 19-22 соединены соответственно с вторым

входом первого сдвигового регистра 24, третьим входом третьего сдвигового регистра 26, вторым входом второго сдвигового регистра 25 и третьим ходом четвертого сдвигового регистра 27. Минусовой и второй входы перого сумматора 28 соединены с выходаи соответственно второго и третьего сдвиговых регистров 25 и 26, а перый и второй входы второго сумматора

29 соединены с выходами соответствен- о первого и четвертого сдвиговых егистров 24 и 27.Выходы первого и торого сумматоров 28 и 29 соединены

313

с входами соответственно первого и второго накопительных сумматоров 30 и 31. Первый вход вычислителя 32 модуля соединен с выходом первого накопительного сумматора 30, а второй вход - с выходом второго накопительного сумматора 31. Выход Код частоты ЦСО 23 является первым выходом анализатора, а выход вычислителя 32 модуля - вторым выходом анализатора;

Цифровой анализатор спектра работает следующим образом.

Квадратурный преобразователь 1 формирует из входного сигнала y(t) квадратурные компоненты комплексной огибающей, поступающие на бинарные АЦП 2 и 3, выполняющие операцию бинарного квантования. Ограниченные по амплитуде сигналы поступают на знаковые входы реверсивных счетчиков 4 и 5 со сбросом, на которых выполнены цифровые фильтры. По сигналу управления изменяется время накопления в реверсивных счетчиках, что равнозначно изменению полосы цифрового фильтра. Время накопления и полоса связаны обратной пропорциональной зависимостью

о 1

т;

где Afgcp - полоса фильтра;

Т - время накопления. С выходов реверсивных счетчиков 4 и 5 сигналы в виде многоразрядных чисел поступают на входы цифровых компараторов 7-9 и 10-12, где осуществляется сравнение этих чисел с пороговыми многоразрядными кодами,-формируемыми в формирователе 6 порога в зависимости от сигнала управления. Первьш и шестой цифровые компараторы

7и 12 сравнивают эти числа с многоразрядными пороговыми кодами Z+-, третий и четвертый цифровые компараторы 9 и 10 - с кодами Z-; второй и пятый цифровые компарторы 8 и 11 - с кодами Zj,, соответствующими исходному состоянию реверсивных счетчиков 4 и 5. С выходов первого и третьего цифровых компараторов 7 и 9, а также четвертого и шестого цифровых компараторов 10 и 12 сигналы, фиксирующие превьшение порогов, поступают на входы первого и второго логических элементов ИЛИ 13 и 14 соответственно. Второй и пятый цифровые компараторы

8и 11 формируют сигналы, соответствующие знакам, а первый и третий.

54

четвертый и шестой цифровые компараторы 7 и 9, 10 и 12 совместно с элементами ИЛИ 13 и 14 - модулям квадратурных компонент входного сигнала.

Сигналы, соответствующие модулям и знакам квадратурных компонент, поступают на ОЗУ 15-18, где осуществляется временная компрессия, т.е. считыва- - ние информации со значительно большей

скоростью, чем запись. Временная компрессия способствует значительному сокращению времени анализа исследуемого частотного диапазона. С выходом первого и второго ОЗУ 15 и 16 сжатые

во времени сигналы, представляющие знаки квадратурных компонент входного сигнала, поступают на первые входы первого и второго, третьего и четвертого перемножителей 19 и 20, 21 и 22

соответственно. На вторые входы этих перемножителей поступают с ЦСО 23 сигналы, представляющие знаки квадратурных компонент опорного колебания. В перемножителях 19-22 бсуществляется перемножение знаков квадратурных, компонент, сжатых во времени входного и опорного сигналов. С выходом третьего и четвертого ОЗУ 17 и 18 сжатые во времени сигналы, представляющие

модули квадратурных компонент входного сигнала, поступают на сдвиговые регистры 24-27, куда также с ЦСО 23 заводятся сигналы, представляющие в виде мнргоразрядньк кодов модули

квадратурных компонент опорного сигнала. На сдвиговых регистрах 24-27 осуществляется перемножение модулей квадратурных компонент, сжатых во времени входного и опорного сигналов.

Операция перемножения сводится к

сдвигу на один разряд в сторону старших разрядов (умножение на 2) модуля соответствующей квадратурной компоненты опорного сигнала при наличии

на выходе соответствующего ОЗУ модуля квадратурной компоненты входного сигнала высокого логического уровня (1). При наличии на выходе ОЗУ низкого логического уровня (О) операция перемножения модулей квадратурных компонент входного и опорного сигналов (сжатых во времени) сводится к записи без сдвига в соответствующие сдвиговые регистры модуля соответствующей

квадратурной компоненты опорного сигнала. Результатам перемножения модулей квадратурных компонент входного и опорного сигналов в сдвиговых

513

регистрах 24-27 соответственно присваиваются знаки, полученные в результате перемножения знаков квадратурных компонент входного и опорного сигналов. С выходов первого и четвертого сдвиговых регистров 24 и 27 числа суммируются на втором сумматоре 29, с выходов третьего и второго сдвиговых регистров 25 и 26 числа вычитаются на первом сумматоре 28. С выходов первого и второго сумматоров 28 и 29 числа поступают, на входы первого И второго накопительных сумматоров 30 и 31, где осуществляется усреднение на интервале Т накопления действительной и мнимой частей произведения квадратурных компонент входного и опорного сигналов. Время Тц накопления определяет разрешающую способность анализатора спектра. С выходов йакопительных сумматоров 30 и 31 результаты усреднения действительной и мнимой частей произведения квадратурных компонент входного и опорного сигналой X и Y поступают на вычислитель 32 модуля, реализующий операцию

Z 1XH-|Y1

вместо значительно более сложной в реализации оптимальной операции Z

. Полученное в результате число содер 1а- т в себе информацию об уровне спектральной составляющей входного сигнала. Параллельно с ЦСО 23 снимается код частоты, соответст- анализируемой спектральной составляющей.

о р м у л а

изобретения

Цифровой анализатор спектра, содержащий квадратурньп преобразователь, ВХ.ОД которсэго является входом анализатора, а первый и второй выходы подключены соответственно к первому и второму бинарным аналого-цифро- вьм преобразователям, первое оперативное запоминающее устройство, выход которого соединен с первыми входами первого и второго перемножителей, второе оперативное запоминающее устройство, выход которого соединен с первыми входами третьего и четвертого перемножителей, цифровой синтезатор отсчетов, синусный знаковый выход которого соединен с вторыми входами первого и третьего перемножителей, а косинусный знаковый выход соединен ,с вторыми входами второго и четверто9256

го перемножителей, пыход цифрового

синтезатора отсчетов Код частоты является первым выходом анализатора, последовательно соединенные первый сумматор, первый накопительный сумматор и вычислитель модуля, выход которого является вторым выходом анализатора, последовательно соединенные второй сумматор, второй накопиQ тельный сумматор, выход которого соединен с вторым входом вычислителя модуля, отличающийся тем, что с целью расширения функциональных возможностей цифрового анализатора

спектра, в него введены первый и второй реверсивные счетчики,первые входы которых соединены с выходами соответственно первого и второго бинарных аналого-цифровых преобразоватеQ лей, первый, второй и третий цифровые компараторы, первые входы которых одновременно соединены с выходом первого реверсивного счетчика, четвертый, пятый и шестой цифровые компара5 торы, первые входы которых одновременно соединены с выходом второго реверсивного счетчика, последовательно соединенные первый элемент ИЛИ, третье оперативное запоминающее устрой0 ство и управляющий вход первого сдвигового регистра, знаковый вход которого соединен с выходом первого перемножителя, последовательно соеди-. ненные второй элемент ИЛИ, четвертое

оперативное запоминающее устройство и управляющий вход второго сдвигового регистра, знаковый вход которого- соединен с выходом третьего перемножителя, первый и второй входы первого

Q элемелта ИЛИ соединены с выходами соответственно первого и третьего цифровых компараторов, а первый и второй входы второго элемента ИЛИ соединены с выходами соответственно

четвертого и шестого цифровых компараторов, формирователь порога, первый выход которого соединен с вторыми входами первого и шестого цифровых компараторов, второй выход формировад теля порога соединен с вторыми входами третьего и четвертого цифровых компараторов, третий выход формирователя порога соединен с вторыми входами второго и пятого цифровых компара5 Торов, выходы которых соединены соответственно с входами первого и второго оперативного запоминающего устройства, вход формирователя порога соединен с вторыми входами первого и

713

второго реверсивных счетчиков и является управляющим входом анализатора, третий и четвертый сдвиговые регистры, информационные входы которых одновременно соединены с косинусным выходом цифрового синтезатора отсчетов , управляющие входы соединены с выходами соответственно третьего и четвертого оперативных запоминающих устройств, знаковые входы соединены с выходами соответственно второго и

Составитель В. Смолин Редактор Л. Гратилло Техред М.Ходанич Заказ 2505/38 Тираж 730Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород , ул. Проектная, 4

189258

четвертого перемножителей, синусный выход цифрового синтезатора отсчетов соединён с информационными входами первого и второго сдвиговых р егист5 ров, выходы которых соединены соответственно с первым входом второго и минусовым входом первого сумматоров ,вторые входы - которых соединены соответственно с выходами

fO четвертого и третьего сдвиговых регистров.

Корректор С. .ар

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

| Адаптивный групповой приемник многочастотного кода с импульсно-кодовой модуляцией | 1989 |

|

SU1830632A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Когерентный приемник частотно-манипулированных радиосигналов с непрерывной фазой | 1990 |

|

SU1716615A1 |

| Адаптивный групповой приемник многочастотного кода с импульсно-кодовой модуляцией | 1989 |

|

SU1635273A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| СПОСОБ ПОИСКА МНОГОЛУЧЕВОГО ШИРОКОПОЛОСНОГО СИГНАЛА И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ, СПОСОБ ОБНАРУЖЕНИЯ И ОЦЕНКИ РАЗМЕРА КЛАСТЕРА СИГНАЛОВ ЛУЧЕЙ И БЛОК, ЕГО РЕАЛИЗУЮЩИЙ | 2001 |

|

RU2208916C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1983 |

|

SU1840196A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1984 |

|

SU1840075A1 |

| СПОСОБ ЧАСТОТНО-ВРЕМЕННОЙ СИНХРОНИЗАЦИИ СИСТЕМЫ СВЯЗИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2003 |

|

RU2304359C2 |

Цифровой анализатор спектра содержит квадратурный преобразователь 1, бинарные аналого-цифровые преобразователи 2,3 реверсивные счетчики 4,5, формирователь 6 порога, цифровые компараторы 7-12, элементы ИЛИ 13, 14, оперативные запоминающие устройства 15-18, перемножители 19- 22, цифровой синтезатор 23 отсчетов, сдвиговые регистры 24-27, сумматоры 28, 29, накопительные сумматоры 30, 31 и вычислитель 32 модуля. Изобретение позволяет расширить функциональные возможности цифрового анализатора спектра за счет реализации возможности изменения диапазона анализа и разрешающей способности анализатора. 1 ил. nJ. u(t) 3 А f Выход loo эо

| Радиоприемные устройства./Под ред | |||

| Л.Г | |||

| Барулина | |||

| - М.: Радио и связь, 1984, с | |||

| Машина для разделения сыпучих материалов и размещения их в приемники | 0 |

|

SU82A1 |

Авторы

Даты

1987-06-23—Публикация

1985-09-12—Подача