1

Изобретение относится к электросвязи и может использоваться в системах передачи дискретной информации

Цель изобретения - повьпиение помехоустойчивости.

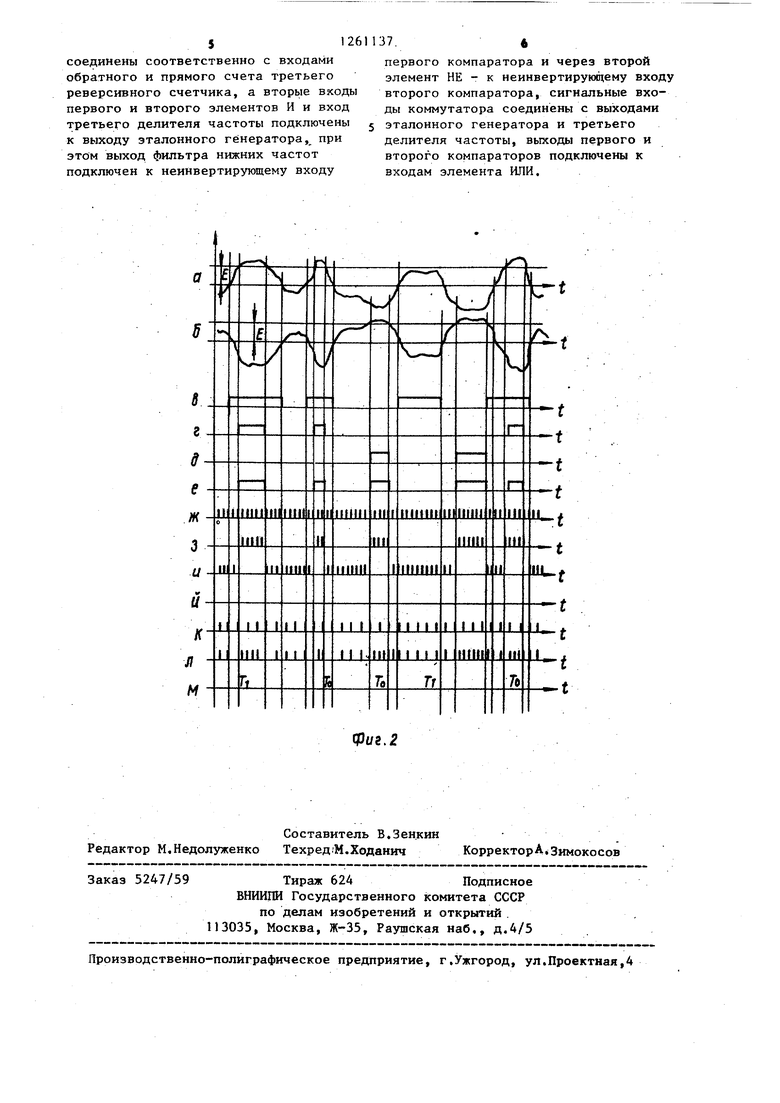

На фиг.1 представлена структурная электрическая схема приемника двоичных- символов; на фиг.2 - временные диаграммы, поясняющие принцип его работы.

Приемник двоичных символов содержит фильтр 1 нижних частот, ограничитель 2 уровня, дискретизатор 3, блок 4 задержки, перемножитель 5, первый реверсивный счетчик 6, блок 7 добавления-исключения импульсов, второй реверсивный счетчик 8, детектор 9 переходов сигнала, первый делитель 10 частоты и эталонньй генератор 11, а также содержит первый и второй компараторы 12 и 13, элемент ИЛИ 14, первый элемент НЕ 15, первый элемент И 16, второй делитель 17 частоты, второй элемент НЕ 18, второ элемент И 19, третий реверсивный счетчик 20, цифроаналоговый преобразователь 21, третий делитель 22 частоты и коммутатор 23.

Приемник двоичных символов работа ет следующим образом.

На вход приемника поступает смесь сигнала и шума. После фильтра I нижних частот эта смесь (фиг.2а) поступает на ограничитель 2 уровня. .Знак смеси и шума (фиг.2Ь) с выхода ограничителя 2 уровня постлтпает на реверсирующий вход второго реверсивного счетчика 8. На неинвертирующий вход первого компаратора 12 .подается прямой сигнал (фиг,2а), а через второй элемент 8 НЕ на неинвертирующий вход второго компаратора 13 поступает инверсный сигнал (фиг.22). В первом и втором компараторах 12 и 13 поступившие сигналы сравниваются с пороговым напряжением Е, поступающим на их инвертирующие входы с выхода цифро-аналогового преобразователя 21 Сигналы в виде логических уровней с первого и второго компараторов 12 и 13 (фиг.22,5) поступают на входы элемента ИЛИ 14 и после сложения суммарный сигнал (фиг.2е) поступает на первый вход второго элемента И 19 и через первый элемент НЕ 15 - на . первый вход первого элемента И 16. На вторые входы первого и второго элементов И 16 и 19 подается сигнал

5 0 5

о

- 5

0

137: 2

с выхода эталонного генератора 11 (фиг. 2) с выхода первого элемента И 16 сигнал (фиг.2у) через второй делитель 17 частоты с коэффициентом деления, равным N, поступает на вход прямого счета третьего реверсивного счетчика 20, на вход обратного счета которого поступает сигнал с выхода второго элемента И 19 (фиг.2). В третьем реверсивном счетчике 20 происходит усреднение и состоя ние старших разрядов этого счетчика декодируется в цифроаналоговом преобразователе 21, вырабатывающем пороговое напряжение Е, значение которого зависит от времени усреднения в третьем реверсивном счетчике 20 и от коэффициента деления второго делителя 17 частоты.

На сигнальные входы коммутатора 23 подаются последовательности с эталонного генератора П и с третьего делителя 22 частоты (фиг.2 р), коэффициент деления которого равен К. При сигнале логического О на управляющем входе коммутатора 23 на тактовом входе второго реверсивного счетчика В действует последовательность с выхода третьего делителя 22 частоты, а при сигнале логической 1 - последовательность с выхода эталонного генератора П (фиг,2л).

Схема синхронизации (фиг.1 пунктирная линия) работает следующим об- разом.

Знак ограниченной входной смеси с выхода ограничителя 2 уровня опрашивается с помощью дискретизатора 3 в момейты действ.ия импульсов на выходе первого делителя 10 частоты, который совместно с блоком 7 добавления-исключения импульсов выполняет функции дискретного фазовращателя. Эквивалентная полоса пропускания регулируется с помощью первого реверсивного счетчика 6. Время задержки блоком 4 задержки равняется длительности единичного символа. Детектор 9 переходов из выходного сигнала второго реверсивного счетчика 8 выраба- тьшает сигнал -«-1, если в двух соседних тактах следует комбинация 01, сигнал -1, если в соседних тактах следует комбинация 10, и сигнал О, если в соседних тактах следуют комбинации 00 или 11, при этом на выходах перемножителя 5 вьщеляются сигналы ошибкиJ которые принимают одно

31

из трех значений: нуль на обоих выходах; I на первом выходе и О .на втором выходе; О на первом выходе и 1 на втором выходе.

Эти сигналы управляют работой первого реверсивного счетчика 6, определяя направление его счета. Количество импульсов, поступивших на тактовый вход второго реверсивного счетчика 8, между соседними импульса ми на его установочном входе, поступающими с первого делителя 10 часто- ты и определяющими границы символов входного сигнала будет зависеть от величины входной -смеси сигнала и шум и определяет знак поступившего очередного символа информации (фиг.2м) Работа устройства-прототипа характеризуется следующим алгоритмом:

( u,-t.),

где Ш - оценка значения принятого символа;

- соответственно промежутки

времени, когда входной сиг- нал положителен и отрицателен на интервале (t , t).

Очевидно t - t, о t- o .,

Работа предлагаемого приемника

двоичных символов описывается другим

алгоритмом

(2,.1€,-,-м),

где К 1 - некоторый коэффициент,

равньш величине коэффици ента деления третьего делителя 22 частоты (на фиг.2k величина К равна

. . ,

D, ;Cj , L,J b4 - соответственно время на-

хождения входного сигнала в диапазонах (),

(+Е, О), (О, -Е), - (-Е, -со) в течение времени анализа символа . на интервале (t, ; t).

, .,4, 4Т,,

При этом t - t,

Автоподстройка порогового напряжения Е производится следящей системой 50 таким образом, чтобы отношение средних времен присутствия входного сигнала внутри и вне порогов (-E,tE) равнялось определенной величине, равной коэффициенту деления N второго5S делителя 17 частоты.

Величины с, , cj , f, и Т зависят не только от знака входной смеси

1374

сигнал-щум, но и от ее величины в )тличие от устройства-прототипа, где Г4- и t. зависят лишь от знака входной смеси.

Таким образом, повышение помехоустойчивости приема двоичных символов достигается за счет учета не только знака, но и величины входной смеси сигнал-шум.

Формула изобретения

Приемник двоичных символов, содержащий последовательно соединенные фильтр нижних частот, ограничитель уро.чня, дискретизатор, блок задержки и перемножитель, выходы которого через первьй реверсивный счетчик подключены к управляющим входам блока добавления-исключения импульсов, второй реверсивный счетчик, детектор переходов сигнала, первый делитель частоты и эталонный генератор, выход которого подключен к тактовому входу блока добавления-исключения импульсов, выход которого через первый делитель частоты подключен к второму входу дискретизатора и к установочном входу второго реверсивного счетчика, выход которого через детектор пере- ходов сигнала соединен с вторым входом перемножителя и является выходом приемника, при этом реверсирующий вход второго реверсивного счетчика подключен к выходу ограничителя уровня, а вход фильтра нижних частот является входом приемника, отличающийся тем, что, с целью повьш1ения помехоустойчивости, в него введены первый и второй компараторы, элемент ИЛИ, последовательно соединенные первый элемент НЕ, первый элемент И и второй делитель частоты, второй элемент НЕ, второй элемент И, последовательно соединенные третий : реверсивный счетчик и цифроаналого- вый преобразователь, третий делитель частоты и коммутатор, выход которого подключен к тактовому входу второго реверсивного счетчика, причем инвертирующие вхрда 1 первого и второго компараторов соединены с выходом цифро- аналогового преобразователя, выход элемента ИЛИ подключен к первому . входу второго элемента И, входу первого элемента НЕ и к управляющему входу коммутатора, выходы второго элемента И и второго делителя частоты

512611

соединены соответственно с входами обратного и прямого счета третьего реверсивного счетчика, а вторые входы первого и второго элементов И и вход третьего делителя частоты подключены j к выходу эталонного генератора, при этом выход фильтра нижних частот подключен к неинвертирующему входу

Составитель В.Зен.кин Редактор М.Недолуженко Техред.-М.Ходанич Корректор А Зимокосов

5247/59

Тираж 624Подписное

ВИНИЛИ Государственного комитета СССР

по делам изобретений и открытий . 113035, Москва, Ж-35, Раушская наб,, д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

первого компаратора и через второй элемент НЕ - к неинвертирующему входу второго компаратора, сигнальные входы коммутатора соединены с выходами эталонного генератора и третьего делителя частоты, выходы первого и второго компараторов подключены к входам элемента ИЛИ,

Фиг.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Приемник двоичных символов | 1989 |

|

SU1656692A1 |

| КВАЗИКОГЕРЕНТНЫЙ МОДУЛЯТОР СИГНАЛОВ КВАДРАТУРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2581646C1 |

| Устройство фазовой автоподстройки частоты | 1984 |

|

SU1166301A1 |

| КВАЗИКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР СИГНАЛОВ БИНАРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2566813C1 |

| КВАЗИКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР СИГНАЛОВ КВАДРАТУРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2582331C1 |

| КВАЗИКОГЕРЕНТНЫЙ МОДУЛЯТОР СИГНАЛОВ БИНАРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2567002C1 |

| ФАЗОЧУВСТВИТЕЛЬНЫЙ ПРИЕМНИК ДЛЯ РЕЛЬСОВОЙ ЦЕПИ | 1991 |

|

RU2041099C1 |

| Устройство для измерения защищенности сигнала от помех | 1989 |

|

SU1658400A2 |

| Радиоприемное устройство с защитой от помех | 1990 |

|

SU1786666A1 |

| Цифровое устройство слежения за задержкой псевдослучайной последовательности | 1983 |

|

SU1088146A1 |

Изобретение относится к электросвязи. Повьопается помехоустойчивость. Приемник содержит фильтр нижних частот 1, ограничитель уровня 2, дискретизатор 3, блок задержки 4, перемножитель 5, два реверсивных счетчика (PC) 6 и 8, блок добавления - исключения импульсов 7, детектор переходов .сигнала 9, делитель частоты (ДЧ) 10 и эталонньй генератор 11. Для достижения цели в приемник введены ;;ва компаратора 12 и 13, элемент ИЛИ 4, два элемента НЕ 15 и 18, два элемента И 16 и 19, два ДЧ 17 и 22, PC 20, НАЛ 21 и коммутатор 23, с помощью которьпс осуществляется учет не только знака, но и величины входной .смеси сигнал - шум. 2 ил. П а с Фиг. 1

| Жодзишский М.И | |||

| и др | |||

| Цифровые cиcтe ы фазовой синхронизации | |||

| М.: Советское радио, 1980, с.69. |

Авторы

Даты

1986-09-30—Публикация

1985-05-20—Подача