k/ 1C

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля монотонности кодов | 1988 |

|

SU1575223A1 |

| Устройство для управления каналами | 1984 |

|

SU1372329A2 |

| Устройство для сбора и обработки информации | 1982 |

|

SU1057950A2 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Устройство для контроля | 1981 |

|

SU1072052A1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU951408A1 |

| Устройство для контроля блоков памяти | 1985 |

|

SU1283859A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| Многоканальное устройство для сбора данных | 1983 |

|

SU1095163A1 |

| Устройство для контроля монотонно изменяющегося кода | 1985 |

|

SU1304174A1 |

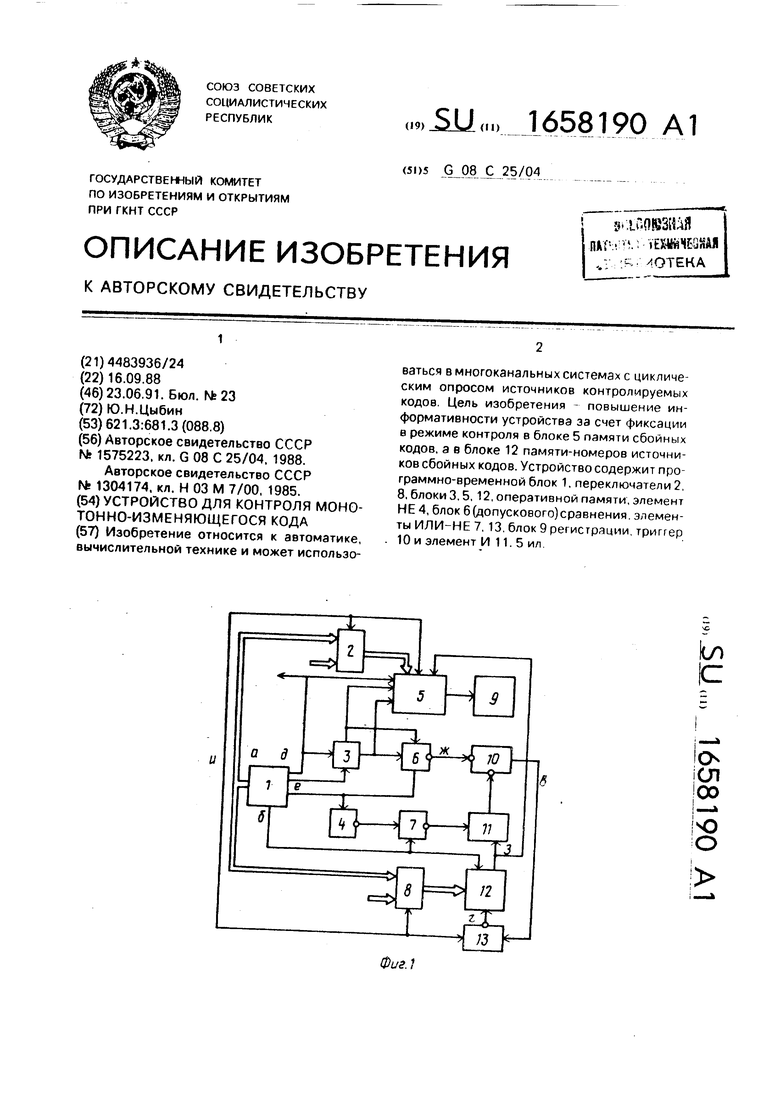

Изобретение относится к автоматике, вычислительной технике и может использоваться в многоканальных системах с циклическим опросом источников контролируемых кодов. Цель изобретения - повышение информативности устройства за счет фиксации в режиме контроля в блоке 5 памяти сбойных кодов, а в блоке 12 памяти-номеров источников сбойных кодов. Устройство содержит программно-временной блок 1, переключатели 2, 8, блоки 3.5,12, оперативной памяти, элемент НЕ 4, блок 6(допускового)сравнения элементы ИЛИ-НЕ 7, 13. блок 9 регистрации триггер 10 и элемент И 11. 5 ил

о ел

00

I

Изобретение относится к автоматике, вычислительной технике и может использоваться в последовательных многоканальных системах с циклическим опросом источников контролируемых кодов.

Целью изобретения является повышение информативности устройства.

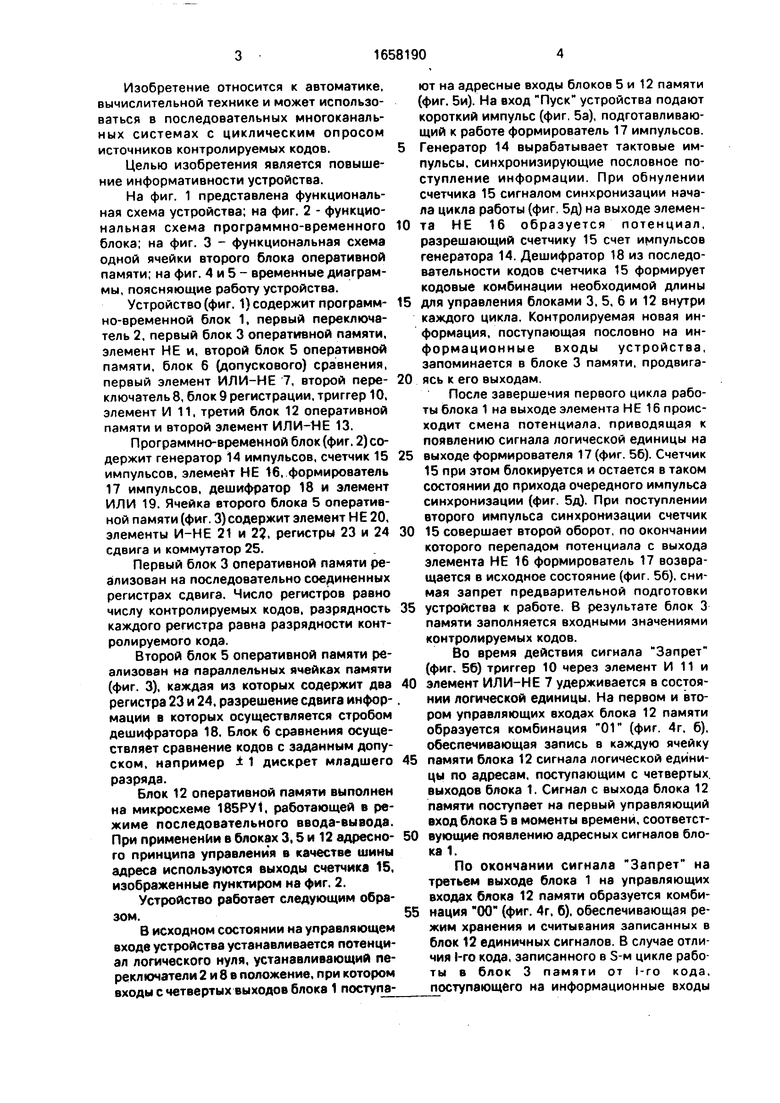

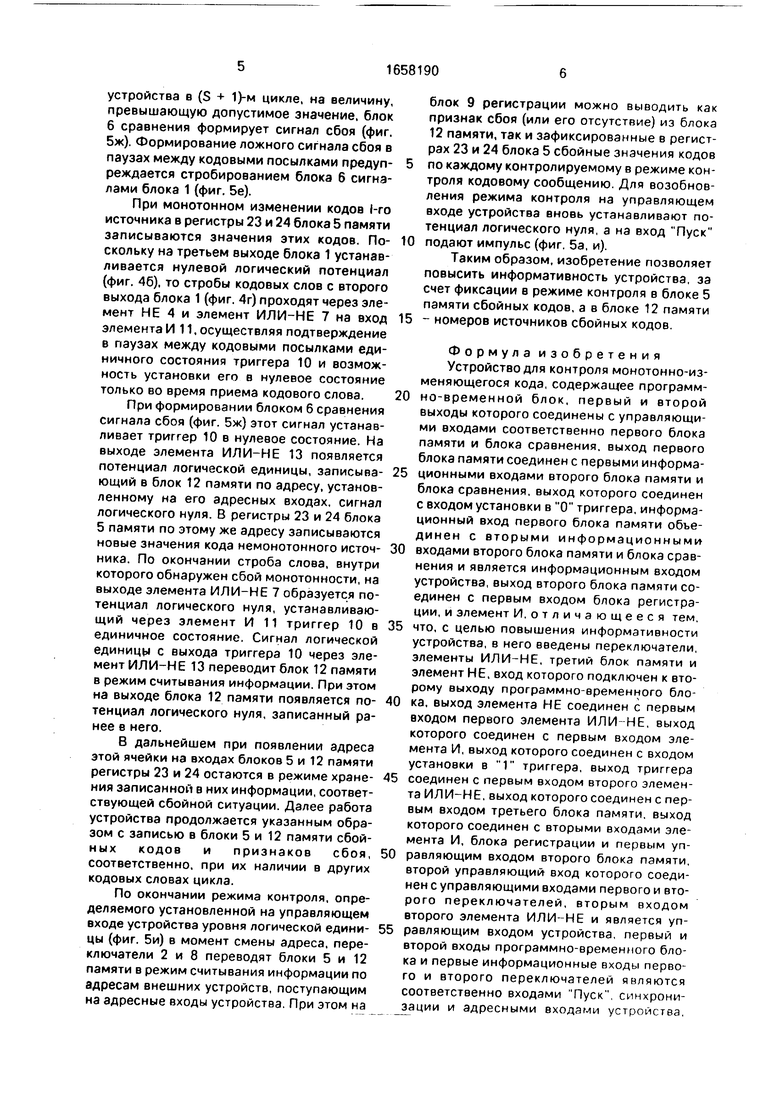

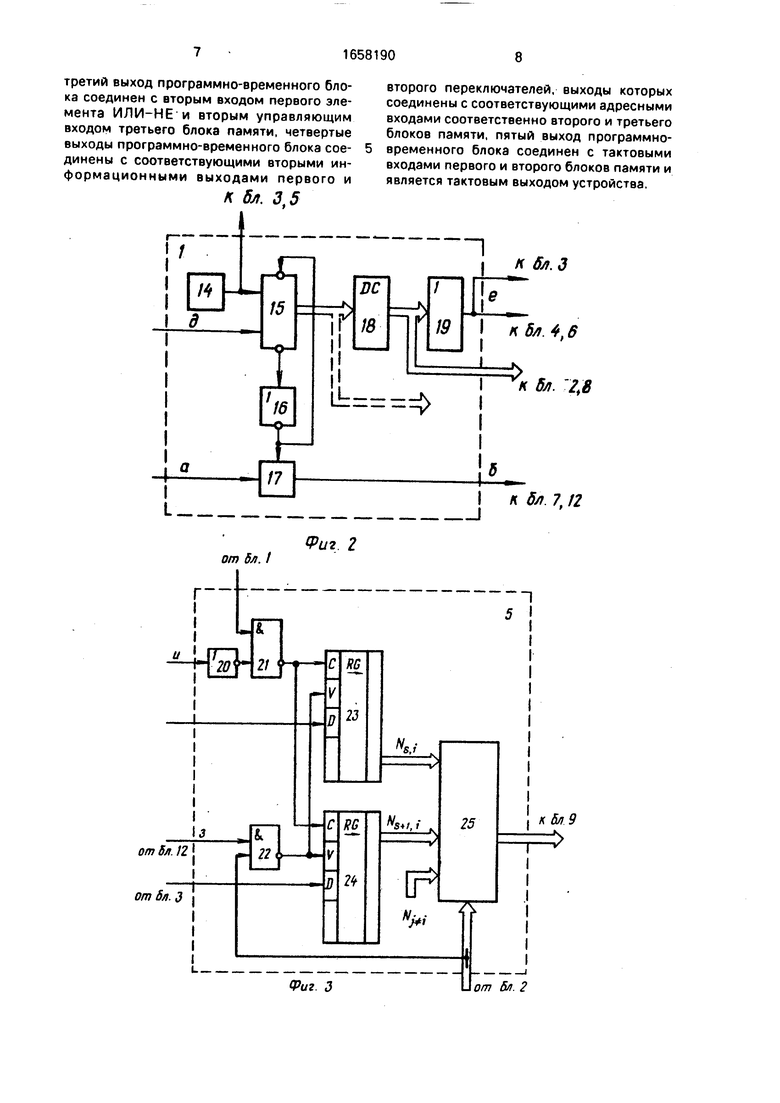

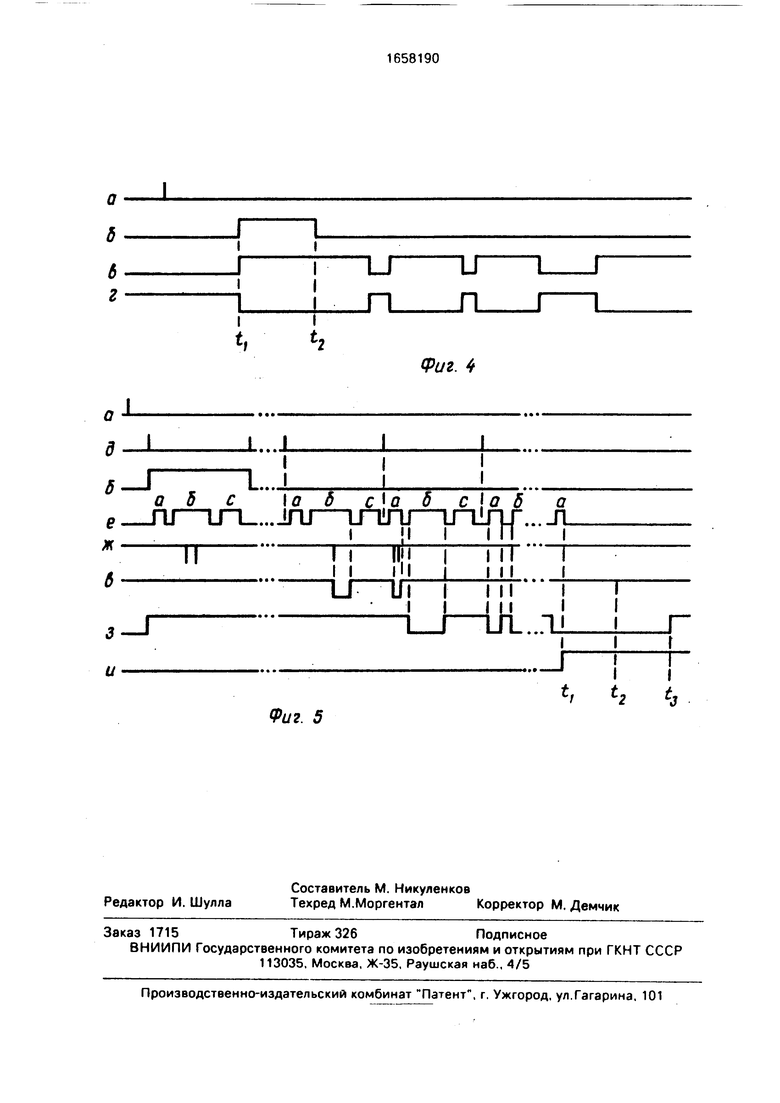

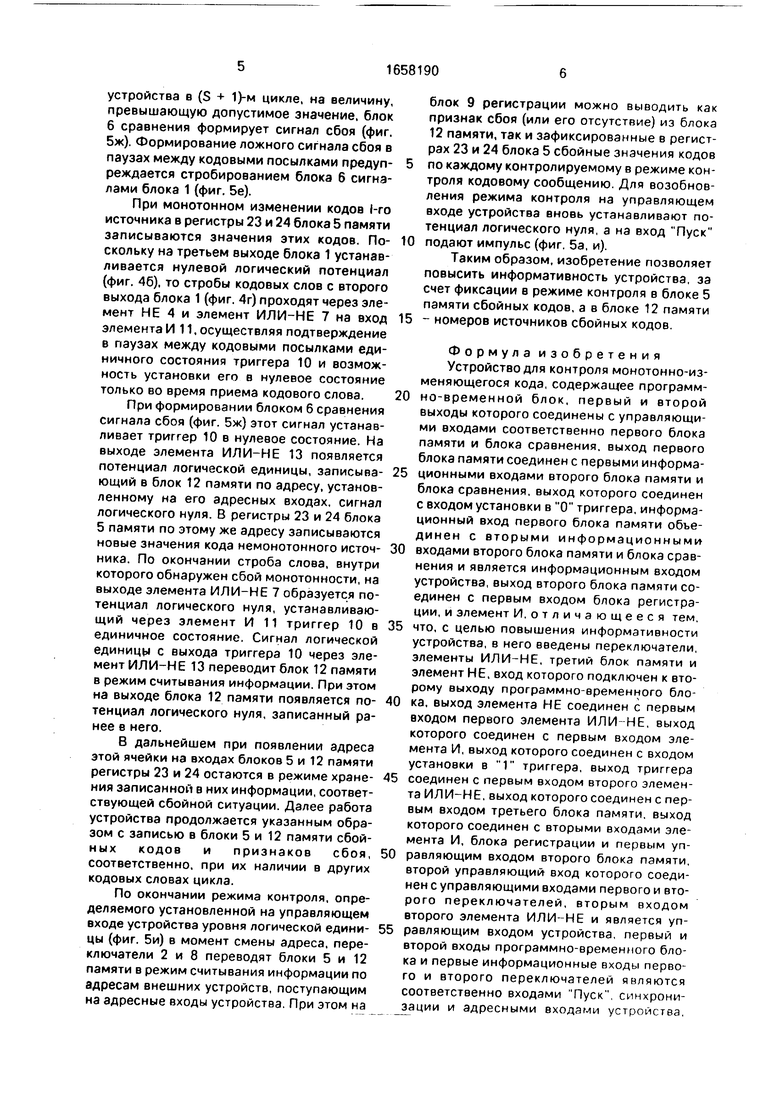

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - функциональная схема программно-временного блока; на фиг. 3 - функциональная схема одной ячейки второго блока оперативной памяти; на фиг. 4 и 5 - временные диаграммы, поясняющие работу устройства.

Устройство (фиг, 1) содержит программно-временной блок 1, первый переключатель 2, первый блок 3 оперативной памяти, элемент НЕ и, второй блок 5 оперативной памяти, блок 6 (допускового) сравнения, первый элемент ИЛИ-НЕ 7, второй переключатель 8, блок 9 регистрации, триггер 10, элемент И 11, третий блок 12 оперативной памяти и второй элемент ИЛИ-НЕ 13.

Программно-временной блок (фиг, 2) содержит генератор 14 импульсов, счетчик 15 импульсов, элемейт НЕ 16, формирователь 17 импульсов, дешифратор 18 и элемент ИЛИ 19. Ячейка второго блока 5 оперативной памяти (фиг. 3) содержит элемент НЕ 20, элементы И-НЕ 21 и 22, регистры 23 и 24 сдвига и коммутатор 25.

Первый блок 3 оперативной памяти реализован на последовательно соединенных регистрах сдвига. Число регистров равно числу контролируемых кодов, разрядность каждого регистра равна разрядности контролируемого кода.

Второй блок 5 оперативной памяти реализован на параллельных ячейках памяти (фиг. 3), каждая из которых содержит два регистра 23 и 24, разрешение сдвига информации в которых осуществляется стробом дешифратора 18. Блок 6 сравнения осуществляет сравнение кодов с заданным допуском, например 1 дискрет младшего разряда.

Блок 12 оперативной памяти выполнен на микросхеме 185РУ1, работающей в режиме последовательного ввода-вывода. При применении в блоках 3,5 и 12 адресного принципа управления в качестве шины адреса используются выходы счетчика 15, изображенные пунктиром на фиг. 2.

Устройство работает следующим образом.

В исходном состоянии на управляющем входе устройства устанавливается потенциал логического нуля, устанавливающий переключатели 2 и 8 в положение, при котором входы с четвертых выходов блока 1 поступают на адресные входы блоков 5 и 12 памяти (фиг. 5и). На вход Пуск устройства подают короткий импульс (фиг, 5а), подготавливающий к работе формирователь 17 импульсов.

Генератор 14 вырабатывает тактовые импульсы, синхронизирующие пословное поступление информации. При обнулении счетчика 15 сигналом синхронизации начала цикла работы (фиг, 5д) на выходе элемен0 та НЕ 16 образуется потенциал, разрешающий счетчику 15 счет импульсов генератора 14. Дешифратор 18 из последовательности кодов счетчика 15 формирует кодовые комбинации необходимой длины

5 для управления блоками 3, 5, б и 12 внутри каждого цикла. Контролируемая новая информация, поступающая пословно на информационные входы устройства, запоминается в блоке 3 памяти, продвига0 ясь к его выходам.

После завершения первого цикла работы блока 1 на выходе элемента НЕ 16 происходит смена потенциала, приводящая к появлению сигнала логической единицы на

5 выходе формирователя 17 (фиг. 56). Счетчик 15 при этом блокируется и остается в таком состоянии до прихода очередного импульса синхронизации (фиг. 5д). При поступлении второго импульса синхронизации счетчик

0 15 совершает второй оборот, по окончании которого перепадом потенциала с выхода элемента НЕ 16 формирователь 17 возвращается в исходное состояние (фиг. 56). снимая запрет предварительной подготовки

5 устройства к работе. В результате блок 3 памяти заполняется входными значениями контролируемых кодов.

Во время действия сигнала Запрет (фиг. 56) триггер 10 через элемент И 11 и

0 элемент ИЛИ-НЕ 7 удерживается в состоянии логической единицы. На первом и втором управляющих входах блока 12 памяти образуется комбинация 01 (фиг. 4г. б), обеспечивающая запись в каждую ячейку

5 памяти блока 12 сигнала логической единицы по адресам, поступающим с четвертых, выходов блока 1. Сигнал с выхода блока 12 памяти поступает на первый управляющий вход блока 5 в моменты времени, соответст0 вующие появлению адресных сигналов блока 1.

По окончании сигнала Запрет на третьем выходе блока 1 на управляющих входах блока 12 памяти образуется комби5 нация 00 (фиг. 4г, б), обеспечивающая режим хранения и считывания записанных в блок 12 единичных сигналов. В случае отличия 1-го кода, записанного в S-м цикле работы в блок 3 памяти от 1-го кода. поступающего на информационные входы

устройства в (S + 1)-м цикле, на величину, превышающую допустимое значение, блок 6 сравнения формирует сигнал сбоя (фиг. 5ж). Формирование ложного сигнала сбоя в паузах между кодовыми посылками предупреждается стробированием блока б сигналами блока 1 (фиг. 5е).

При монотонном изменении кодов 1-го источника в регистры 23 и 24 блока 5 памяти записываются значения этих кодов. Поскольку на третьем выходе блока 1 устанавливается нулевой логический потенциал (фиг. 46), то стробы кодовых слов с второго выхода блока 1 (фиг. 4г) проходят через элемент НЕ 4 и элемент ИЛИ-НЕ 7 на вход элемента И 11, осуществляя подтверждение в паузах между кодовыми посылками единичного состояния триггера 10 и возможность установки его в нулевое состояние только во время приема кодового слова.

При формировании блоком 6 сравнения сигнала сбоя (фиг. 5ж) этот сигнал устанавливает триггер 10 в нулевое состояние. На выходе элемента ИЛИ-НЕ 13 появляется потенциал логической единицы, записывающий в блок 12 памяти по адресу, установленному на его адресных входах, сигнал логического нуля. В регистры 23 и 24 блока 5 памяти по этому же адресу записываются новые значения кода немонотонного источника. По окончании строба слова, внутри которого обнаружен сбой монотонности, на выходе элемента ИЛИ-НЕ 7 образуется потенциал логического нуля, устанавливающий через элемент И 11 триггер 10 в единичное состояние. Сигнал логической единицу с выхода триггера 10 через элемент ИЛИ-НЕ 13 переводит блок 12 памяти в режим считывания информации. При этом на выходе блока 12 памяти появляется потенциал логического нуля, записанный ранее в него.

В дальнейшем при появлении адреса этой ячейки на входах блоков 5 и 12 памяти регистры 23 и 24 остаются в режиме хранения записанной в них информации, соответствующей сбойной ситуации. Далее работа устройства продолжается указанным образом с записью в блоки 5 и 12 памяти сбойных кодов и признаков сбоя, соответственно, при их наличии в других кодовых словах цикла.

По окончании режима контроля, определяемого установленной на управляющем входе устройства уровня логической единицы (фиг. 5и) в момент смены адреса, переключатели 2 и 8 переводят блоки 5 и 12 памяти в режим считывания информации по адресам внешних устройств, поступающим на адресные входы устройства. При этом на

блок 9 регистрации можно выводить как признак сбоя (или его отсутствие) из блока 12 памяти, так и зафиксированные в регистрах 23 и 24 блока 5 сбойные значения кодов

5 по каждому контролируемому в режиме контроля кодовому сообщению. Для возобновления режима контроля на управляющем входе устройства вновь устанавливают потенциал логического нуля, а на вход Пуск

10 подают импульс (фиг. 5а, и).

Таким образом, изобретение позволяет повысить информативность устройства, за счет фиксации в режиме контроля в блоке 5 памяти сбойных кодов, а в блоке 12 памяти

15 - номеров источников сбойных кодов.

Формула изобретения Устройство для контроля монотонно-изменяющегося кода, содержащее программ0 но-временной блок, первый и второй выходы которого соединены с управляющими входами соответственно первого блока памяти и блока сравнения, выход первого блока памяти соединен с первыми информа5 ционными входами второго блока памяти и блока сравнения, выход которого соединен с входом установки в О триггера, информационный вход первого блока памяти объединен с вторыми информационными

0 входами второго блока памяти и блока сравнения и является информационным входом устройства, выход второго блока памяти соединен с первым входом блока регистрации, и элемент И, отличающееся тем,

5 что, с целью повышения информативности устройства, в него введены переключатели, элементы ИЛИ-НЕ, третий блок памяти и элемент НЕ, вход которого подключен к второму выходу программно-временного бло0 ка, выход элемента НЕ соединен с первым входом первого элемента ИЛИ-НЕ, выход которого соединен с первым входом элемента И, выход которого соединен с входом установки в 1 триггера, выход триггера

5 соединен с первым входом второго элемента ИЛИ-НЕ, выход которого соединен с первым входом третьего блока памяти, выход которого соединен с вторыми входами элемента И, блока регистрации и первым уп0 равляющим входом второго блока памяти, второй управляющий вход которого соединен с управляющими входами первого и второго переключателей, вторым входом второго элемента ИЛИ-НЕ и является уп5 равляющим входом устройства, первый и второй входы программно-временного блока и первые информационные входы первого и второго переключателей являются соответственно входами Пуск, синхронизации и адресными входами устройства.

третий выход программно-временного блока соединен с вторым входом первого элемента ИЛИ-НЕ и вторым управляющим входом третьего блока памяти, четвертые выходы программно-временного блока соединены с соответствующими вторыми информационными выходами первого и

К 6/1. J 5

LI

Фиг. 2 от 5л. I

второго переключателей, выходы которых соединены с соответствующими адресными входами соответственно второго и третьего блоков памяти, пятый выход программно- временного блока соединен с тактовыми входами первого и второго блоков памяти и является тактовым выходом устройства.

Фиг. 5

| Устройство для контроля монотонности кодов | 1988 |

|

SU1575223A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство для контроля монотонно изменяющегося кода | 1985 |

|

SU1304174A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-06-23—Публикация

1988-09-16—Подача