Устройство относится к автоматике и вычислительной технике и может бытЬ| использовано в последовательных мно- роканальных системах с временным раз- , делением контролируемых кодов.

Цель изобретения - повышение достоверности устройства.

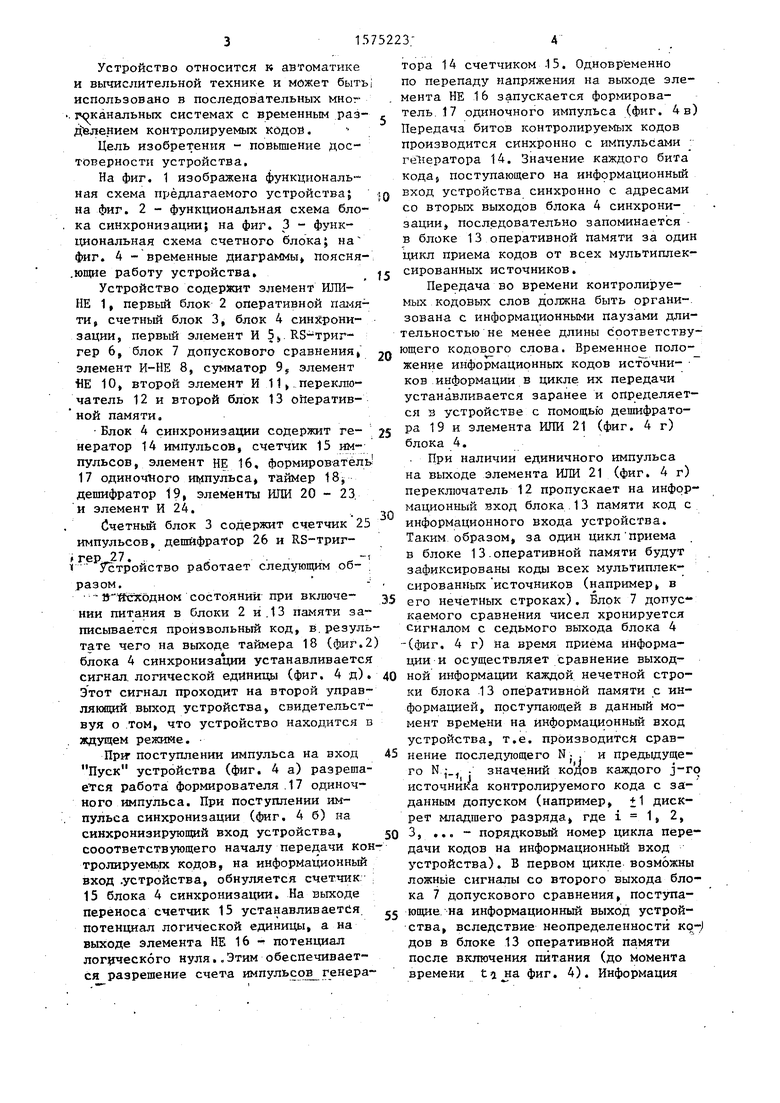

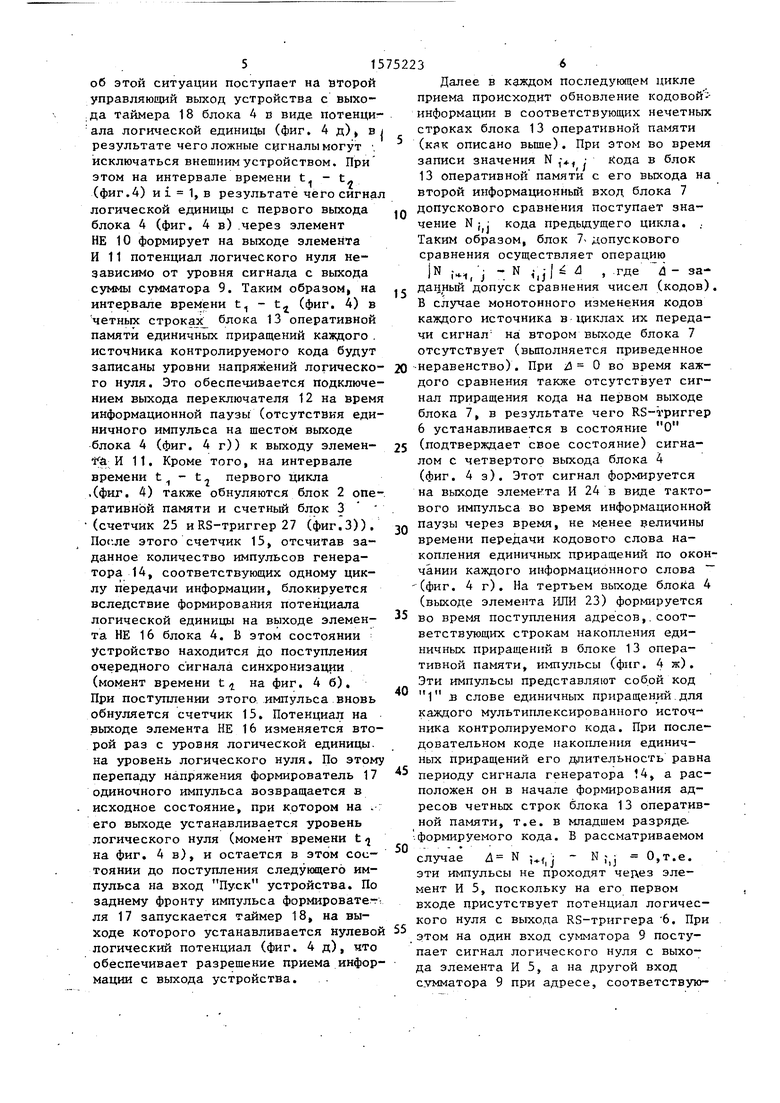

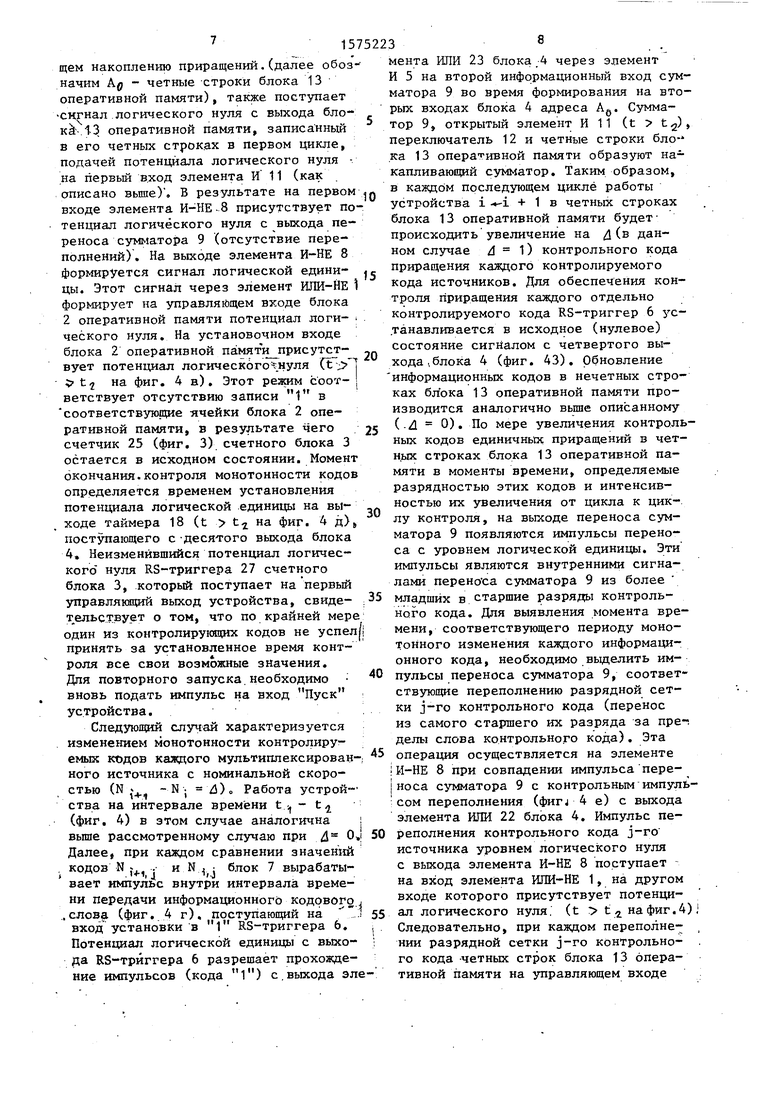

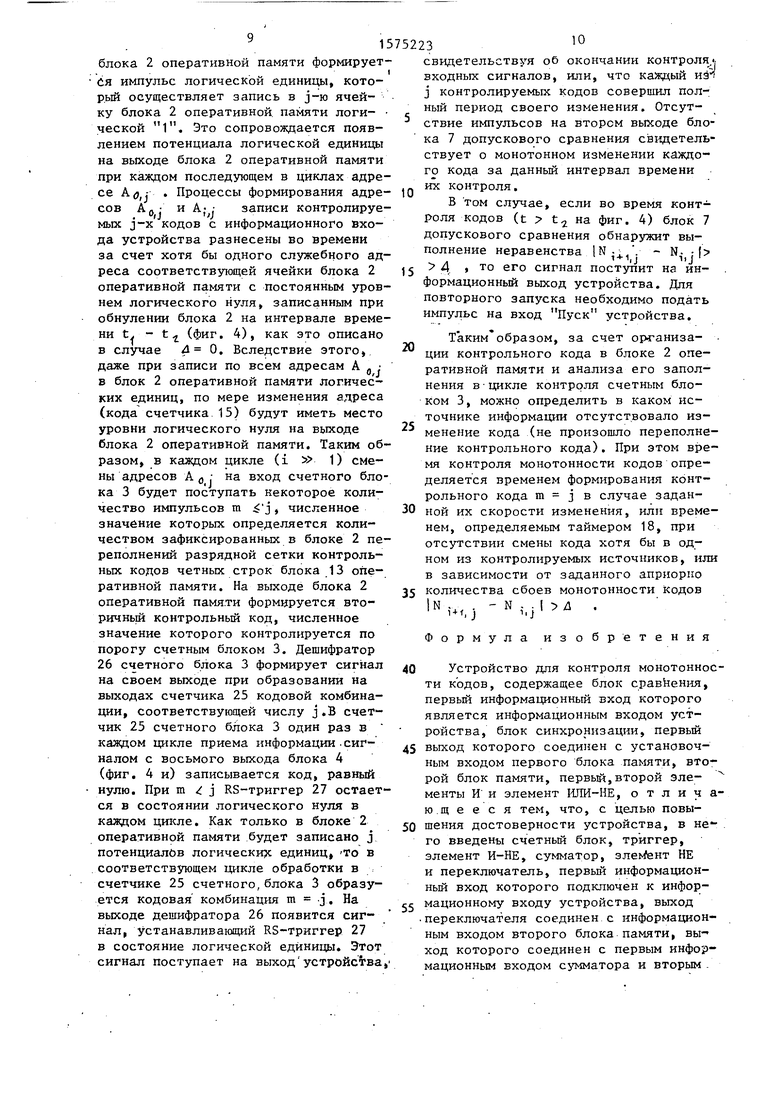

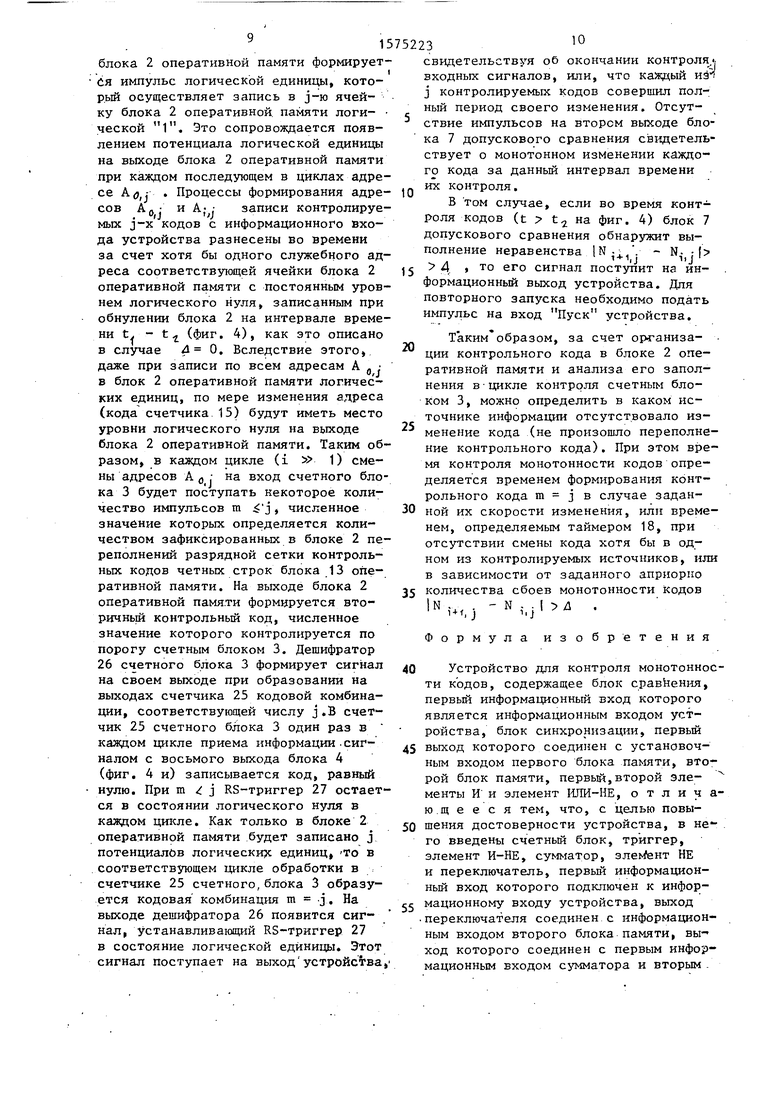

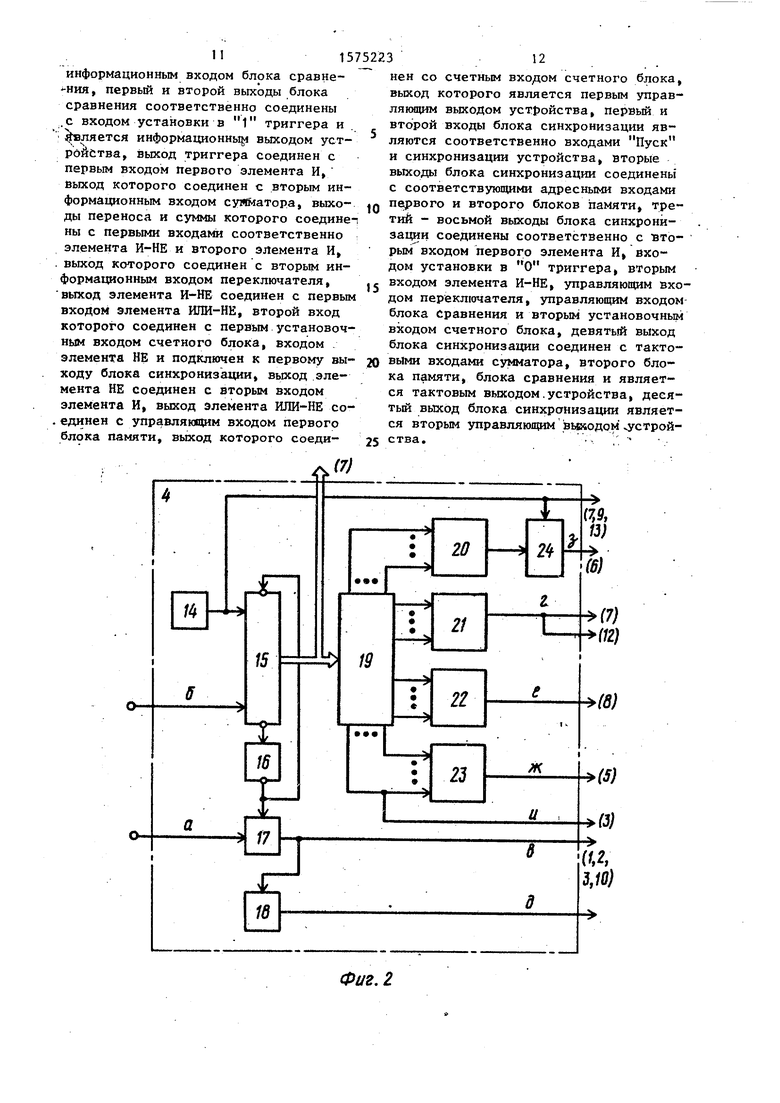

На фиг. 1 изображена функциональная схема предлагаемого устройства; ,Q на фиг. 2 - функциональная схема блока синхронизации; на фиг. 3 - функциональная схема счетного блока; на фиг. 4 - временные диаграммы поясня- ющие работу устройства.

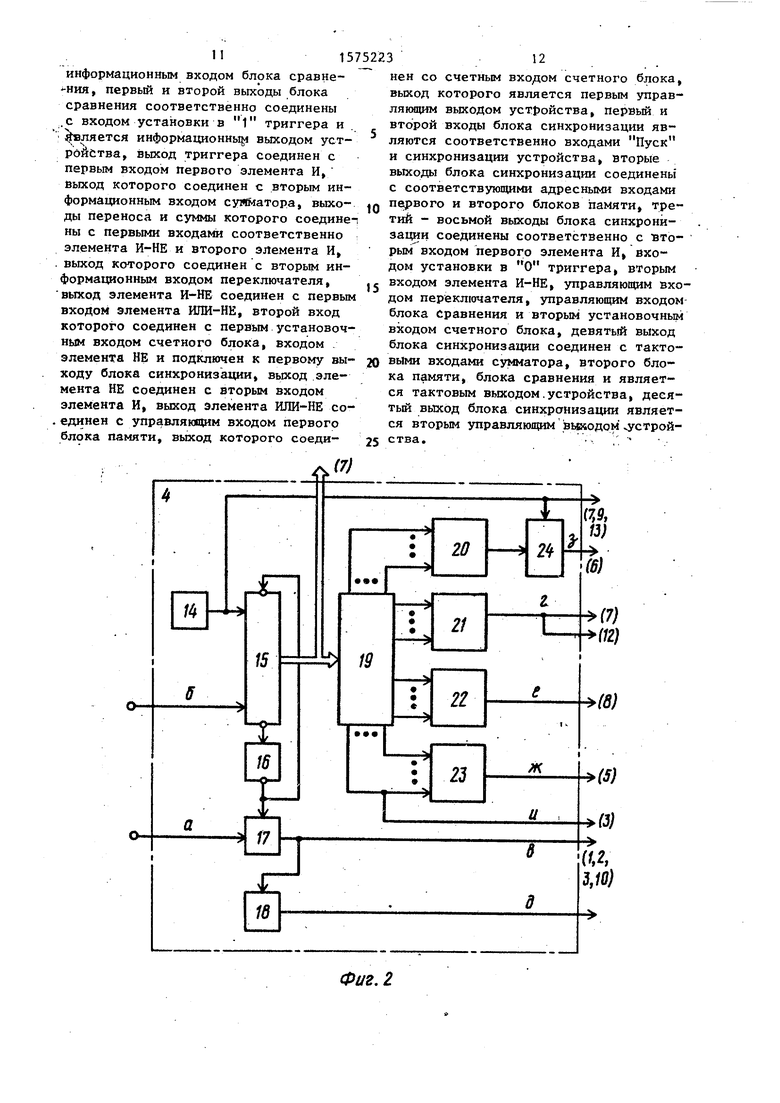

Устройство содержит элемент ИЛИ- НЕ 1, первый блок 2 оперативной памяти, счетный блок 3, блок 4 синхронизации, первый элемент И 5, RS-триг™ гер 6, блок 7 допускового сравнения jn элемент И-НЕ 8, сумматор 95 элемент ЯЕ 10, второй элемент И 11, переключатель 12 и второй блок 13 оператив- ной памяти.

Блок 4 синхронизации содержит ге- 25 нератор 14 импульсов, счетчик 15 импульсов, элемент НЕ 16, формирователь 17 одиночного импульса, таймер 18, дешифратор 19, элементы ИЛИ 20 - 23 и элемент И 24.

Счетный блок 3 содержит счетчик 25 импульсов, дешифратор 26 и RS-триггер 27.ч

Устройство работает следующим образом. - .

йосодном состоянии при включе- 5 нии питания в блоки 2 и 13 памяти записывается произвольный код, в результате чего на выходе таймера 18 (фиг.2) блока 4 синхронизации устанавливается сигнал логической единицы (фиг. 4 д). 40 Этот сигнал проходит на второй управляющий выход устройства свидетельствуя о том, что устройство находится в ждущем режиме.

При- поступлении импульса на вход 45 Пуск устройства (фиг. 4 а) разрешается работа формирователя 17 одиночного импульса. При поступлении импульса синхронизации (фиг. 4 б) на синхронизирующий вход устройства, jo сооответствующего началу передачи контролируемых кодов, на информационный вход .устройства, обнуляется счетчик 15 блока 4 синхронизации. На выходе переноса счетчик 15 устанавливается „ потенциал логической единицы, а на выходе элемента НЕ 16 - потенциал логического нуля.„Этим обеспечивается разрешение счета импульсов генера

30

;

n

5

5 0

5 o

0

тора 14 счетчиком 15. Одновременно по перепаду напряжения на выходе элемента НЕ 16 запускается формирователь 17 одиночного импульса (фиг. 4 в) Передача битов контролируемых кодов производится синхронно с импульсами генератора 14. Значение каждого бита кода8 поступающего на информационный вход устройства синхронно с адресами со вторых выходов блока 4 синхронизации, последовательно запоминается в блоке 13 оперативной памяти за один цикл приема кодов от всех мультиплексированных источников.

Передача во времени контролируемых кодовых слов должна быть организована с информационными паузами длительностью не менее длины соответствующего кодового слова. Временное положение информационных кодов источников информации в цикле их передачи устанавливается заранее и определяется з устройстве с помощью дешифратора 1 9 и элемента ИЛИ 21 (фиг. 4 г) блока 4.

При наличии единичного импульса на выходе элемента ИЛИ 21 (фиг. 4 г) переключатель 12 пропускает на информационный вход блока 13 памяти код с информационного входа устройства. Таким образом, за один цикл приема в блоке 13 оперативной памяти будут зафиксированы коды всех мультиплексированных источников (например в его нечетных строках). Блок 7 допускаемого сравнения чисел хронируется сигналом с седьмого выхода блока 4 -(фиг. 4 г) на время приема информации и осуществляет сравнение выходной информации каждой нечетной строки блока 13 оперативной памяти с информацией, поступающей в данный момент времени на информационный вход устройства, т.е. производится сравнение последующего N; . и предыдущего N . значений кодов каждого j-ro источника контролируемого кода с заданным допуском (например, +1 дискрет младшего разряда где i 1, 2, 3, ... - порядковый номер цикла передачи кодов на информационный вход устройства). В первом цикле возможны ложные сигналы со второго выхода блока 7 допускового сравнения, поступающие на информационный выход устройства, вследствие неопределенности ко-J дов в блоке 13 оперативной памяти после включения питания (до момента времени фиг. 4). Информация

об этой ситуации поступает на второй управляющий выход устройства с выхода таймера 18 блока 4 в виде потенциала логической единицы (фиг. 4 д), в/ результате чего ложные сигналы могут исключаться внешним устройством. При этом на интервале времени t. - t- (фиг.4) и i 1, в результате чего сигнал логической единицы с первого выхода блока 4 (фиг. 4 в) через элемент НЕ 10 формирует на выходе элемента И 11 потенциал логического нуля независимо от уровня сигнала с выхода суммы сумматора 9. Таким образом, на интервале времени t, - t (фиг. 4) в четных строках блока 13 оперативной памяти единичных приращений каждого источника контролируемого кода будут записаны уровни напряжений логического нуля. Это обеспечивается подключением выхода переключателя 12 на время информационной паузы (отсутствия единичного импульса на шестом выходе блока 4 (фиг. 4 г)) к выходу элемен- И 11. Кроме того, на интервале времени t1 - t первого цикла .(фиг. 4) также обнуляются блок 2 оперативной памяти и счетный блок 3 (счетчик 25 иRS-триггер 27 (фиг.З)). Пос.ле этого счетчик 15, отсчитав заданное количество импульсов генератора 14, соответствующих одному циклу передачи информации, блокируется вследствие формирования потенциала логической единицы на выходе элемента НЕ 16 блока 4. В этом состоянии устройство находится до поступления очередного сигнала синхронизации (момент времени t на фиг. 4 б). При поступлении этого импульса вновь обнуляется счетчик 15. Потенциал на выходе элемента НЕ 16 изменяется второй раз с уровня логической единицы на уровень логического нуля. По этому перепаду напряжения формирователь 17 одиночного импульса возвращается в исходное состояние, при котором на . его выходе устанавливается уровень логического нуля (момент времени t -j на фиг. 4 в), и остается в этом состоянии до поступления следующего импульса на вход Пуск устройства. По заднему фронту импульса формирователя 17 запускается таймер 18, на выходе которого устанавливается нулевой логический потенциал (фиг. 4 д), ото обеспечивает разрешение приема информации с выхода устройства.

0

5

0

5

0

5

0

5

0

5

Далее в каждом последующем цикле приема происходит обновление кодовой -- информации в соответствующих нечетных строках блока 13 оперативной памяти (кяк описано выше). При этом во время записи значения N ,-., ; Кода в блок 13 оперативной памяти с его выхода на второй информационный вход блока 7 допускового сравнения поступает значение N ; . кода предыдущего цикла. Таким образом, блок 7 допускового сравнения осуществляет операцию

1N , j - N i.jl - й г«е заданный допуск сравнения чисел (кодов).

В случае монотонного изменения кодов каждого источника в циклах их передачи сигнал на втором выходе блока 7 отсутствует (выполняется приведенное неравенство). При А 0 во время каждого сравнения также отсутствует сигнал приращения кода на первом выходе блока 7, в результате чего RS-триггер 6 устанавливается в состояние О (подтверждает свое состояние) сигналом с четвертого выхода блока 4 (фиг. 4 з). Этот сигнал формируется на выходе элемента И 24 в виде тактового импульса во время информационной паузы через время, не менее величины времени передачи кодового слова накопления единичных приращений по окончании каждого информационного слова

-(фиг. 4 г). На тертьем выходе блока 4 (выходе элемента ИЛИ 23) формируется во время поступления адресов, соответствующих строкам накопления единичных приращений в блоке 13 оперативной памяти, импульсы (фиг. 4 ж). Эти импульсы представляют собой код 1м в слове единичных приращений для каждого мультиплексированного источника контролируемого кода. При последовательном коде накопления единичных приращений его длительность равна периоду сигнала генератора 14, а расположен он в начале формирования адресов четных строк блока 13 оперативной памяти, т.е. в младшем разряде

формируемого кода. В рассматриваемом

случае 4 N +f|j - N )3 0,т.е. эти импульсы не проходят чер,ез элемент И 5, поскольку на его первом входе присутствует потенциал логического нуля с выхода RS-триггера 6. При этом на один вход сумматора 9 поступает сигнал логического нуля с выхода элемента И 5, а на другой вход сумматора 9 при адресе, соответствую-

щем накоплению приращений.(далее обоз начим Ад - четные строки блока 13 оперативной памяти), также поступает -сигнал логического нуля с выхода бло- оперативной памяти, записанный в его четных строках в первом цикле, подачей потенциала логического нуля - на первый вход элемента И 11 (как описано выше). В результате на первом входе элемента И-НЕ 8 присутствует потенциал логического нуля с выхода переноса сумматора 9 (отсутствие переполнений) . На выходе элемента И-НЕ 8 формируется сигнал логической едини- цы. Этот сигнал через элемент ИЛИ-НЕ 1 формирует на управляющем входе блока 2 оперативной памяти потенциал логи- ческого нуля. На установочном входе блока 2 оперативной памяти присутст- вует потенциал логического-г.нуля t2 на фиг. 4 в). Этот режим соответствует отсутствию записи 1 в соответствующие ячейки блока 2 оперативной памяти, в результате чего счетчик 25 (фиг. 3) счетного блока 3 остается в исходном состоянии. Момент окончания.контроля монотонности кодов определяется временем установления потенциала логической единицы на выходе таймера 18 (t tz на фиг. 4 д), поступающего с -десятого выхода блока 4 Неизменившийся потенциал логического нуля RS-триггера 27 счетного блока 3, который поступает на первый управляющий выход устройства, свидетельствует о том, что по крайней мере один из контролирующих кодов не успел принять за установленное время контроля все свои возможные значения. Для повторного запуска необходимо вновь подать импульс на вход Пуск устройства.

Следующий случай характеризуется изменением монотонности контролируемых кодов каждого мультиплексированного источника с номинальной скоро

стью

(N

1+1

-N. Л) о Работа устройства на интервале времени t ,, - t (фиг. 4) в этом случае аналогична выше рассмотренному случаю при Д- 0, Далее, при каждом сравнении значений кодов N у . и N : блок 7 вырабатывает импульс внутри интервала времени передачи информационного кодового .слова (фиг. 4 г), поступающий на

1 RS-триггера 6.

вход установки в

Потенциал логической единицы с выхода RS-трйггера 6 разрешает прохождение импульсов (кода 1) с выхода эле

10

1 |

25

| i ,

емента ИЛИ 23 блока 4 через элемент И 5 на второй информационный вход сумматора 9 во время формирования на вторых входах блока 4 адреса АО. Сумматор 9, открытый элемент И 11 (t t2), переключатель 12 и четные строки бло- ка 13 оперативной памяти образуют накапливающий сумматор. Таким образом, в каждом последующем цикле работы устройства i + 1 в четных строках блока 13 оперативной памяти будет происходить увеличение на Д(в данном случае ) контрольного кода приращения каждого контролируемого кода источников. Для обеспечения контроля приращения каждого отдельно контролируемого кода RS-триггер 6 устанавливается в исходное (нулевое) состояние сигналом с четвертого вы- хода(блока 4 (фиг. 43). Обновление

информационных кодов в нечетных строках блока 13 оперативной памяти производится аналогично выше описанному ( Л 0). По мере увеличения контрольных кодов единичных приращений в четных строках блока 13 оперативной памяти в моменты времени, определяемые разрядностью этих кодов и интенсивностью их увеличения от цикла к циклу контроля, на выходе переноса сумматора 9 появляются импульсы переноса с уровнем логической единицы. Эти импульсы являются внутренними сигналами переноса сумматора 9 из более младших в старшие разряды контрольного кода. Для выявления момента времени, соответствующего периоду монотонного изменения каждого информационного кода, необходимо выделить импульсы переноса сумматора 9, соответствующие переполнению разрядной сетки j-ro контрольного кода (перенос из самого старшего их разряда за пределы слова контрольного кода). Эта операция осуществляется на элементе И-НЕ 8 при совпадении импульса пере- |носа сумматора 9 с контрольным импульсом переполнения (фиг4 4 е) с выхода элемента ИЛИ 22 блока 4. Импульс переполнения контрольного кода j-ro источника уровнем логического нуля с выхода элемента И-НЕ 8 поступает на вход элемента ИЛИ-НЕ 1, на другом входе которого присутствует потенци- ал логического нуля (t t г на фиг. 4) Следовательно, при каждом переполнении разрядной сетки j-ro контрольного кода четных строк блока 13 оперативной памяти на управляющем входе

30

35

40

45

50

55

блока 2 оперативной памяти формируетi

ся импульс логической единицы, который осуществляет запись в j-ю ячейку блока 2 оперативной памяти логи- ческой 1. Это сопровождается появлением потенциала логической единицы на выходе блока 2 оперативной памяти при каждом последующем в циклах адресе АО : . Процессы формирования адресов А. и А;: записи контролируемых j-x кодов с информационного входа устройства разнесены во времени за счет хотя бы одного служебного адреса соответствующей ячейки блока 2 оперативной памяти с постоянным уровнем логического нуля, записанным при обнулении блока 2 на интервале времени tj - tЈ (фиг. 4), как это описано в случае Л 0. Вследствие этого, даже при записи по всем адресам А 0 в блок 2 оперативной памяти логических единиц, по мере изменения адреса (кода счетчика 15) будут иметь место уровни логического нуля на выходе блока 2 оперативной памяти. Таким образом, в каждом цикле (i 1) смены адресов А 0 на вход счетного блока 3 будет поступать некоторое количество импульсов га j, численное значение которых определяется количеством зафиксированных в блоке 2 переполнений разрядной сетки контрольных кодов четных строк блока 13 оперативной памяти. На выходе блока 2 оперативной памяти формируется вторичный контрольный код, численное значение которого контролируется по порогу счетным блоком 3. Дешифратор 26 счетного блока 3 формирует сигнал на своем выходе при образовании на выходах счетчика 25 кодовой комбинации, соответствующей числу j.B счетчик 25 счетного блока 3 один раз в каждом цикле приема информации.сигналом с восьмого выхода блока 4 (фиг. 4 и) записывается код, равный нулю. При m j RS-триггер 27 остается в состоянии логического нуля в каждом цикле. Как только в блоке 2 оперативной памяти будет записано j потенциалов логических единиц, -то в соответствующем цикле обработки в счетчике 25 счетного,блока 3 образуется кодовая комбинация m .j. На выходе дешифратора 26 появится сигнал, устанавливающий RS-триггер 27 в состояние логической единицы. Этот сигнал поступает на выход устройства,1

522310

свидетельствуя об окончании контроля.-, входных сигналов, или, что каждый иэ j контролируемых кодов совершил полный период своего изменения. Отсутствие импульсов на втором выходе блока 7 допускового сравнения свидетельствует о монотонном изменении каждого кода за данный интервал времени их контроля.

В том случае, если во время конт10

15

20

25

30

35

роля кодов (t t2 на фиг. 4) блок 7 допускового сравнения обнаружит выполнение неравенства 1N- + 1. - N. | 4 .то его сигнал поступит на информационный выход устройства. Для повторного запуска необходимо подать импульс на вход Пуск устройства.

Таким образом, за счет ор аниза- - ции контрольного кода в блоке 2 оперативной памяти и анализа его заполнения в цикле контроля счетным блоком 3, можно определить в каком источнике информации отсутствовало изменение кода (не произошло переполнение контрольного кода). При этом время контроля монотонности кодов определяется временем формирования контрольного кода m j в случае заданной их скорости изменения, или временем, определяемым таймером 18, при отсутствии смены кода хотя бы в одном из контролируемых источников, или в зависимости от заданного априорно количества сбоев монотонности кодов

..,,

-

Формула изобретения

Устройство для контроля монотонности кодов, содержащее блок сравнения, первый информационный вход которого является информационным входом устройства, блок синхронизации, первый

выход которого соединен с установочным входом первого блока памяти, второй блок памяти, первый,второй элементы И и элемент ИЛИ-НЕ, отличающееся тем, что, с целью повышения достоверности устройства, в него введены счетный блок, триггер, элемент И-НЕ, сумматор, элемент НЕ и переключатель, первый информационный вход которого подключен к информационному входу устройства, выход переключателя соединен с информационным входом второго блока памяти, выход которого соединен с первым информационным входом сумматора и вторым

информационным входом блока сравне- Ния, первый и второй выходы блока сравнения соответственно соединены с входом установки в 1 триггера и Является информационны выходом устройства, выход триггера соединен с первым входом первого элемента И, выход которого соединен с вторым информационным входом сумматора, выходы переноса и суммы которого соединены с первыми входами соответственно элемента И-НЕ и второго элемента И, выход которого соединен с вторым инормационным входом переключателя, выход элемента И-НЕ соединен с первым входом элемента ИЛИ-НЕ, второй вход которого соединен с первым установочным входом счетного блока, входом элемента НЕ и подключен к первому выходу блока синхронизации, выход элемента НЕ соединен с вторым входом элемента И, выход элемента ИЛИ-НЕ со- единен с управляющим входом первого блока памяти, выход которого соеди

нен со счетным входом счетного блока, выход которого является первым управляющим выходом устройства, первый и второй входы блока синхронизации являются соответственно входами Пуск и синхронизации устройства, вторые выходы блока синхронизации соединены с соответствующими адресными входами первого и второго блоков памяти, третий - восьмой выходы блока синхронизации соединены соответственно с вторым входом первого элемента И входом установки в О триггера, вторым

с входом элемента И-НЕ, управляющим входом переключателя, управляющим входом блока сравнения и вторым установочным входом счетного блока, девятьй выход блока синхронизации соединен с такто0 выми входами сумматора, второго блока памяти, блока сравнения и является тактовым выходом устройства, десятый выход блока синхронизации является вторым управляющим выходом .устрой5 ства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля монотонно изменяющегося кода | 1988 |

|

SU1658190A1 |

| Устройство для контроля монотонно изменяющегося кода | 1986 |

|

SU1478337A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

| Устройство для преобразования телевизионного стандарта | 1986 |

|

SU1343562A1 |

| Устройство поиска степени оптимальности размещения в кластерных многопроцессорных системах при направленной передаче информации | 2022 |

|

RU2798392C1 |

| Микропрограммное устройство управления | 1985 |

|

SU1310816A1 |

| Устройство поиска степени оптимальности размещения в кластерных многопроцессорных системах | 2022 |

|

RU2791419C1 |

| Устройство для определения технического состояния механизмов циклического действия | 1989 |

|

SU1686334A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

Изобретение относится к автоматике, вычислительной технике и может использоваться в последовательных многоканальных системах с временным разделением контролируемых кодов. Устройство осуществляет накопление в блоке 13 памяти единичных приращений контролируемых кодов и формирование в блоке 2 памяти контрольного кода разрядностью, равной числу источников кодов, анализ которого счетным блоком 3 позволяет определить, в каком источнике информации отсутствовало изменение кода в цикле контроля, что повышает достоверность результатов. Устройство содержит элемент ИЛИ-НЕ 1, блоки 2,13 оперативной памяти, счетный блок 3, блок 4 синхронизации, элементы И 5,11, триггер 6, блок 7 допускового сравнения, элемент И-НЕ 8, сумматор 9, элемент НЕ 10 и переключатель 12. 4 ил.

Фиг. 2

Фиг Л

| Устройство для сравнения чисел | 1983 |

|

SU1157540A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля монотонно изменяющегося кода | 1986 |

|

SU1478337A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-06-30—Публикация

1988-09-16—Подача