11283859

Изобретение относится к запоминаю щим устройс.твам и может быть исполь- . зовано для динамического функционального контроля с заданным быстродействием запоминающих устройств с произ- 5 вольной выборкой.

Цель изобретения - повышение надежности устройства.

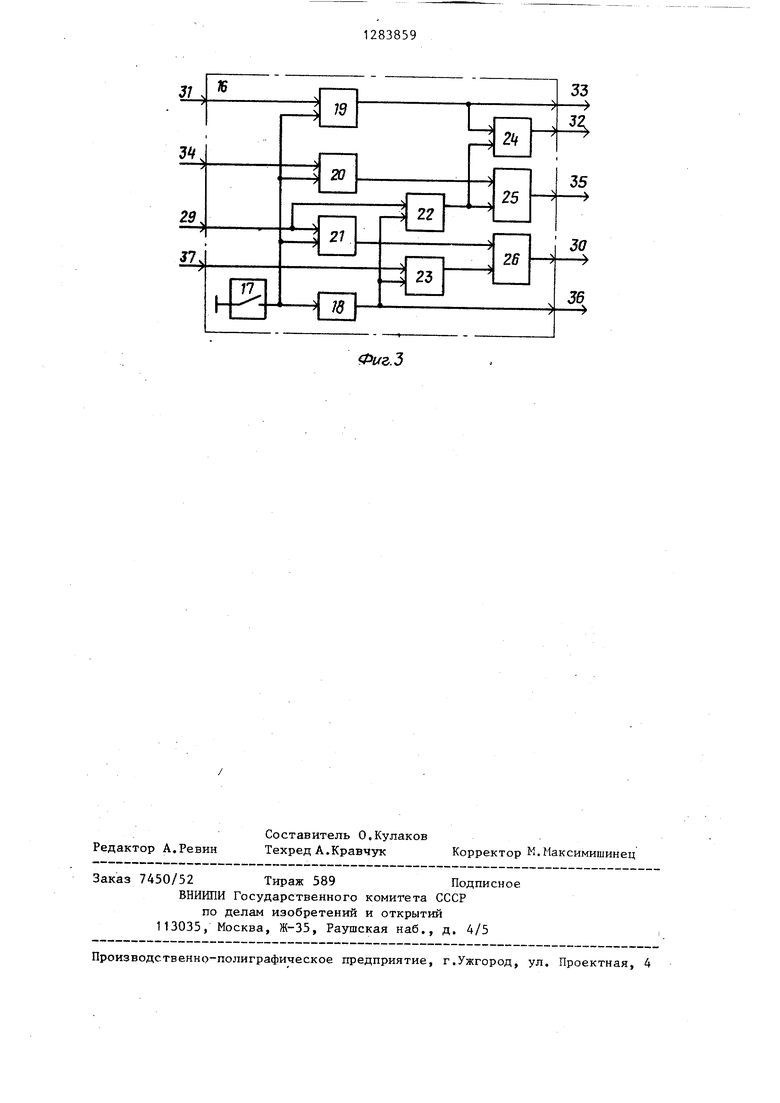

На фиг.1 изображена функциональ- |нАя схема предлагаемого устройства; |на фиг,2 и 3 - соответственно генератор псевдослучайных чисел и блок логических элементов.

Устройство содержит контролируемый блок 1 памяти, блок 2 управления, схему 3 сравнения, формирователь 4 контрольных кодов, первый мультиплексор 5, адресньш счетчик 6, генератор 7 псевдослучайных чисел, содерJO

15

рез мультиплексор 14 коммутацию кодов с выходов адресного счетчика 6, Во втором режиме работы блок 16 логических .элементов осуществляет прохождение сигналов с выхода 29 блока 2 управления на счетный вход 3 адресного счетчика 6 и на тактовый вход 32 генератора 7, а с выхода 37 переполнения адресного счетчика 6 на вход 30 триггера 13, причем сигналом на управляющем входе 33 мультиплексора 5 осуществляется подключение адресных выходов устройства к выходам адресного счетчика 6, а сигналом на входах 36 второго .14 и третьего 15 мультиплексоров - подключение соответственно выходов счетчика 12 числа обращений к управляющим входам генератора 7 псевдослучайных чисел, а

кащий сдвиговый регистр 8, дешифра- { его управляющих выходов к информацитор 9, элементы Неравнозначность 10 и ключи 11,

Устройство содержит также счетчик 12 числа обращений, триггер 13 счетного типа, второй 14 и третий 15 мультиплексоры и блок 16 логических элементов, содержащий коммутирующий элемент 17, инвертор 18, пять логических элементов И 19-23 и три логических элемента ИЛИ 24-26.

На чертеже обозначены установочные входы 27 и 28 устройства.

Устройство работает в двух режимах :

контроль блоков памяти по произвольным адресам предварительно записанных алгоритмических тестов;

контроль записи в проверяемый блок памяти случайных тестов.

25

30

35

40

онным выходам устройства.

Устройство работает следующим образом,

Режим проверки блока 1 памяти по произвольным адресам начинается с записи в него контрольньпс тестов, генерируемых формирователем 4, в результате чего триггер 13 обнуляется, на первый счетньй вход адресного ( счетчика 6 подаются сигналы с выхода блока 2 управления и адресная-информация, сформированная счетчиком 6, проходит через мультиплексор 5 на адресные выходы устройства и входы формирователя 4, который формирует однозначно соответствующие адресной информации контрольные коды по задан ному алгоритму, например бегущие 1 и О и (или) шахматный порядок. Сигналы обращения, поступающие с блока 2 управления, проводят запись в блок 1 памяти формируемых кодов по всем адресам. После предварительной записи тестов переходят непосредственно к режиму контроля блока памяти. Проверяемый блок переводят в режим чтения, счетчик 6 обнуляется и проверка начинается с нулевой ячейки блока 1 памяти, В счетчик 12 числа обращений по входам 28 вводится уставка, значение Y которой (где Y - целое число) определяет число переходов из ячейки блока 1 памяти, задаваемой кодом счетчика 6, а ячейки, номера которых формир лотся случайным образом генератором 7,

Выбор режима определяется коммутирующим элементом 17 блока 16 логических элементов, которьш в первом режиме осуществляет прохождение сигналов с выхода 29 блока 2 управления на вход 30 триггера 13, а с выхода 31 триггера 13 на тактовый вход 32 генератора 7 псевдослучайных чисел и на управляющий вход 33 мультиплексора 3j с выхода 34 п -реполнения счетчика 12 числа обращений на счет1ный вход 35 адресного счетчика 6, причем сигнал на выходе 36 блока 16 осуществляет коммутацию через мультиплексор 15 на информационные выходы устройства контрольный код формиро вателя 4, на управляющие входы генератора 7 псевдослучайных чисел че-

5

O

15

рез мультиплексор 14 коммутацию кодов с выходов адресного счетчика 6, Во втором режиме работы блок 16 логических .элементов осуществляет прохождение сигналов с выхода 29 блока 2 управления на счетный вход 35 адресного счетчика 6 и на тактовый вход 32 генератора 7, а с выхода 37 переполнения адресного счетчика 6 на вход 30 триггера 13, причем сигналом на управляющем входе 33 мультиплексора 5 осуществляется подключение адресных выходов устройства к выходам адресного счетчика 6, а сигналом на входах 36 второго .14 и третьего 15 мультиплексоров - подключение соответственно выходов счетчика 12 числа обращений к управляющим входам генератора 7 псевдослучайных чисел, а

5

0

5

0

5

0

5

онным выходам устройства.

Устройство работает следующим образом,

Режим проверки блока 1 памяти по произвольным адресам начинается с записи в него контрольньпс тестов, генерируемых формирователем 4, в результате чего триггер 13 обнуляется, на первый счетньй вход адресного ( счетчика 6 подаются сигналы с выхода блока 2 управления и адресная-информация, сформированная счетчиком 6, проходит через мультиплексор 5 на адресные выходы устройства и входы формирователя 4, который формирует однозначно соответствующие адресной информации контрольные коды по заданному алгоритму, например бегущие 1 и О и (или) шахматный порядок. Сигналы обращения, поступающие с блока 2 управления, проводят запись в блок 1 памяти формируемых кодов по всем адресам. После предварительной записи тестов переходят непосредственно к режиму контроля блока памяти. Проверяемый блок переводят в режим чтения, счетчик 6 обнуляется и проверка начинается с нулевой ячейки блока 1 памяти, В счетчик 12 числа обращений по входам 28 вводится уставка, значение Y которой (где Y - целое число) определяет число переходов из ячейки блока 1 памяти, задаваемой кодом счетчика 6, а ячейки, номера которых формир лотся случайным образом генератором 7,

Блок 2 управления сигнгшами с выхода 29 переключает триггер 13, с

выходов которого сигналы поступают на запуск счетчика 12, на тактовый Ьход генератора 7 и попеременно подключают через мультиплексор 5 к адресным входам блока 1 памяти выходы счетчика 6 или генератора 7. Таким образом, последовательно осуществляется проверка перехода из определенной ячейки блока 1 памяти, код адреса которой определяется счетчиком 6, к (M-Y) ячейкам, коды адреса которых формируются генератором 7 (где М - емкость счетчика 12 числа обращений) После (M-Y) переходов по произвольным адресам блока 1 памяти счетчик 12 переполняется и сигнал переполнения поступает через блок 16 логических элементов на второй счетный вход счетчика 6, тем самым осуществляется переход к проверке следующей ячейки.

Выходы счетчика 6 через ключи 11 генератора 7 управляют обратной связью регистра 8, т.е. при переходе к проверке следующей ячейки блока 1 памяти изменяется случайная последовательность адресов перехода, генерируемых регистром 8. Дешифратор 9 предназначен для обнаружения нулевого состояния регистра В и предотвращает запирание генератора 7 в это состоянии при включении питания и (или) нормальном режиме работы.

С целью расширения числа различных последовательностей, формируемых генератором 7, предусматривается воз мояйность занесения по входам 27 в регистр 8 начального числа Р.(где Р - целое число).

При обнаружении схемой 3 сравнения несоответствия хранимой после предварительной записи информации с кодом формирователя 4, на вход бло-, ка 2 управления поступает сигнал, запрещающий дальнейшую работу устройства, при этом коды в счетчике 6 и регистре 8 сохраняются и однозначно определяют два адреса перехода, при котором произошел сбой, причем направление перехода (от кода счетчика 6 к коду регистра 8 или наоборот) определяется по состоянию триггера 13. Индикация счетчика 6, регистра 8 и триггера 13 выводится на табло (не показано) и позволяет пользователю оперативно определить причину сбойной ситуации.

O

5

0

5

0

Для вывода всей совокупности адресов при сбойной ситуации на пульт оператора, например дисплей (не показан), и обеспечения многократного считывания последовательности псев- - дослучайньк адресов и подачи их на адресные выходы устройства предусмотрен режим циклического контроля. Для этого блок 2 управления блокирует вход счетчика 6 (цепь блокировки не показана), при этом в счетчике 6 раняется код адреса, при котором про- ,изошел сбой, в регистр 8 вносится начальное число Р, в счетчик 12 каждый раз Яосле переполнения вносится уставка Y, а блок 2 управления формирует сигналы обращения к проверяемому блоку 1 памяти и триггеру 13, тем самым обеспечивается многократное считывание адресов и информации проверяемого блока 1. памяти.

Режим контроля записи в проверяе-; .мый блок 1 памяти случайных тестов i начинается с обнуления счетчика 6 и триггера 13. В счетчик 12 заносится по входу 28 уставка У, определяющая количество проверяемых случайных тестов, а в регистр 8 заносится по вхо-. ду 27 начальное число Р.

С выхода 29 блока 2 управления подаются сигналы на второй счетный ВХОД счетчика 6 и на тактовый вход генератора 7. Сформированные счетчиком 6 адресная информация и генератором 7 случайная последовательность передаются соответственно через мультиплексоры 5 и 15 на адресные и информационные выходы устройства. Сигналами обращения, поступающими с блока 2 управления на проверяемый блок 1 памяти, производят запись случайных кодов по всем адресам. После перебора всех адресов сигнал с выхода

37 переполнения счетчика 6 поступает . на вход триггера 13. В регистр 8 вновь заносится по входам 27 число Р, блок 1 памяти сигналов с блока 2 управления переводится в режим чтения и осуществляется контроль записанной в

блок ;.1 памяти случайной последовательности. После перебора всех адресов с выхода переполнения счетчика 6 на вход триггера 13 вновь поступает сигнал,

который передается на счетчик 12. По входам 27 в регистре 8 заносится число Р и начинается новый цикл запись- чтение, причем формируемая генератором 7 случайная последовательность

изменяется, так как на управляющие обратной связью регистра 8 входы ге- . нератора 7 через мультиплексор 14 по- , дается с разрядных выходов счетчика 12 изменяемый код.5

При обнаружении сбоя схемой 3 сравнения блок 2 управления прекращает работу. Коды, записанные в счетчик 6 и регистре 8, сохраняются и однозначгенератора псевдослучайных чисел и один из входов счетчика числа обращений, счетный вход которого подключен к одному из выходов триггера, отличающееся тем, что, с целью повышения надежности устройства, оно содержит второй и третий мультиплексоры и блок логических элементов, первый выход которого подключен к упно определяют адрес и код информации,10 равляющему входу первого мультиплек- при котором произошел сбой.

Формула изобретения

сора, второй - к управляющим входам второго и третьего мультиплексоров, третий - к тактовому входу генератора псевдослучайных чисел, четвертый - к другому счетному входу адресного счетчика и пятый выход - к входу триггера, другой выход которого соединен с первым входом блока логических элементов, второй вход которого подключен к выходку переполнения адресного счетчика, третий - к третьему выходу блока управления, а четвертый вход - к выходу переполнения счетчика числа обращения, разрядные выходы которого соединены с одними из входов второго мультиплексора, другие входы которого подключены к разрядным выходам адресного счетчика, а выходы - к управляющим входам генератора псевдослучайных чисел, управляющие выходы которого соединены с одними из входов третьего мультиплексора, другие входы которого подключены к выходам формирователя контрольных кодов, а

Устройство для контроля блоков памяти, содержащее блок управления, схему сравнения, формирователь контрольных кодов, первый мультиплексор, адресный счетчик, триггер, счетчик числа обращений и генератор псевдо- случайных чисел, управ шющие выходы которого подключены к одним из входов первого мультиплексора, выходы которого соединены с входами формирователя контрольных кодов и являются адресными выходами устройства, а другие входе первого мультиплексора подключены к разрядным выходам адресного счетчика, один из счетных входов которого соединен с первым выходом блока управления, второй выход которого является управляющим выходом устройства, а вход соединен с выходом схемы сравнения, одни из входов которой являются информационными входами .35 выходы соединены с другими входами

устройства, установочными входами которого являются установочные входы

генератора псевдослучайных чисел и один из входов счетчика числа обращений, счетный вход которого подключен к одному из выходов триггера, отличающееся тем, что, с целью повышения надежности устройства, оно содержит второй и третий мультиплексоры и блок логических элементов, первый выход которого подключен к управляющему входу первого мультиплек-

сора, второй - к управляющим входам второго и третьего мультиплексоров, третий - к тактовому входу генератора псевдослучайных чисел, четвертый - к другому счетному входу адресного счетчика и пятый выход - к входу триггера, другой выход которого соединен с первым входом блока логических элементов, второй вход которого подключен к выходку переполнения адресного счетчика, третий - к третьему выходу блока управления, а четвертый вход - к выходу переполнения счетчика числа обращения, разрядные выходы которого соединены с одними из входов второго мультиплексора, другие входы которого подключены к разрядным выходам адресного счетчика, а выходы - к управляющим входам генератора псевдослучайных чисел, управляющие выходы которого соединены с одними из входов третьего мультиплексора, другие входы которого подключены к выходам формирователя контрольных кодов, а

схемы сравнения и являются информационными выходами устройства. ,

м

Ри,г. 1

27

Фиг. 2

Редактор А.Ревин

Составитель О.Кулаков Техред А.Кравчук

Заказ 7450/52 Тираж 589Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

Фиг. 5

Корректор М.Максимишинец

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков памяти | 1981 |

|

SU951408A1 |

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1358003A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Цифровой имитатор радиотелеграфного канала связи | 1985 |

|

SU1275465A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| ФОРМИРОВАТЕЛЬ ТЕСТОВ | 1991 |

|

RU2012924C1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ СИГНАЛОВ | 2009 |

|

RU2416157C1 |

| Устройство для формирования тестов | 1990 |

|

SU1795462A1 |

Изобретение относится к области вычислительной техники и предназначено для динамического функционального контроля с заданным быстродействием запоминающих устройств с произвольной выборкой. Устройство может быть применено в контрольно-измерительных системах с повышенными требованиями к достоверности контроля. В состав устройства входят 6jiOK управления, адресный счетчик, три мультиплексора, счетчик числа обращений, триггерV формирователь импульсных кодов, схема сравнения и генератор псевдослучайных чисел. Работает устройство в четырех режимах: Запись тестов, Контроль ЗУ, Циклический контроль адресных формирователей, Контроль ЗУ случайными тестами. За счет использования генератора псевдослучайных чисел, мультиплексоров и счетного триггера устройство обес- печивает высокую достоверность и one- ративность контроля на рабочей час- f тоте при небольших аппаратурных затратах. 3 ил. tNd 00 со 00 сд о

| 0 |

|

SU407398A1 | |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля блоков памяти | 1977 |

|

SU619968A2 |

| Микрофонный капсюль | 1926 |

|

SU9514A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-01-15—Публикация

1985-04-23—Подача