(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления каналами | 1979 |

|

SU877519A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство управления для селекторного канала | 1984 |

|

SU1238095A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для коррекции микрокоманд | 1984 |

|

SU1164709A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

Изобретение относится к вычислительной технике, предназначено для управления каналами ввода-вывода. Целью изобретения является повышение надежности за счет восстановления после сбоя любой микропрограммы работы устройства. Устройство для уп

Wfff

ifgyi V/«W 52

paFt. ieiiHH Kana.naNfH содержит регистр i адреса текущей мнкрокоманлы, буфер- nbrii регистр 2 данных, узел 3 элементов И, буферный регистр А }1азначения, буферный регистр 5 адреса микрокоманды, основной регистр 6 данных, регистр 7 контроля, основной регистр 8 адреса назначения, основной регистр 9 адреса микрокоманды, коммутаторы 10, 14, узел 11 элементов ИЛИ, регистр 12 ошибок, элемент И 15, элемент ИЛИ 13, сумматоры 17, 20 по модулю два, блоки 19, 31 управления адресом локальной памяти или регистров

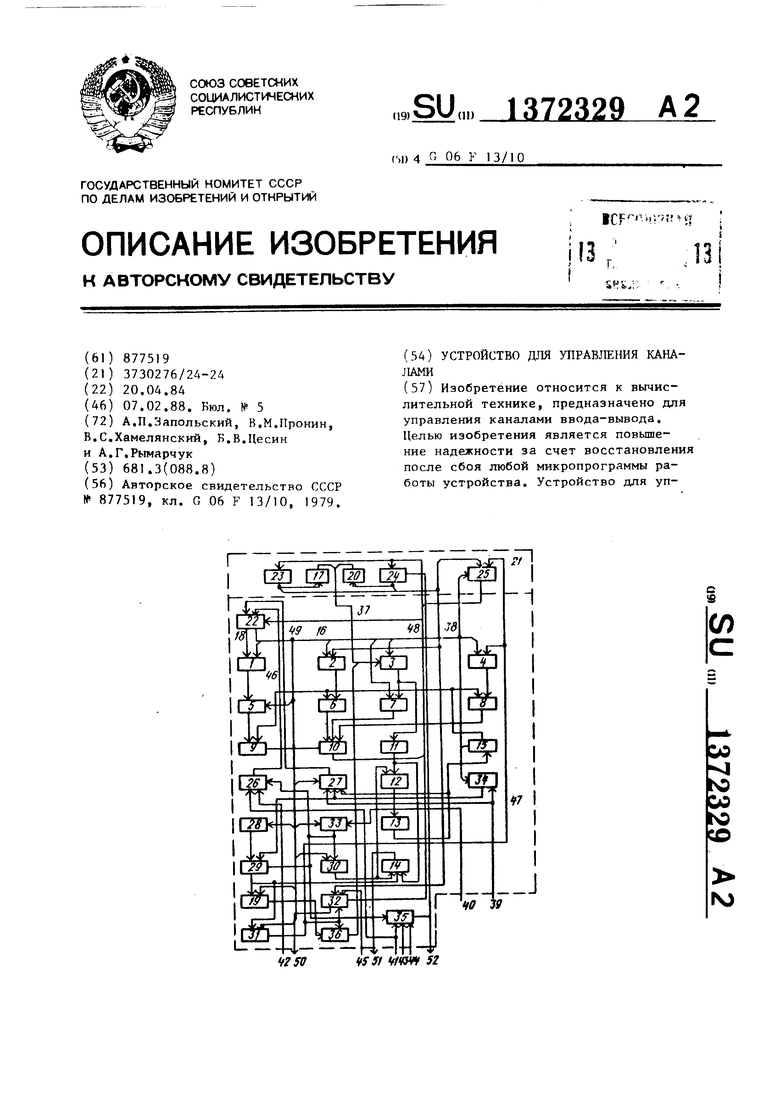

Изобретение относится к вычислительной технике, предназначено для управления каналами ввода-вывода и является усовершенствованием изобретения по авт. св. № 877519.

Целью изобретения является повышение надежности за счет восстановления после сбоя любой микропрограммы работы устройства.

На чертеже приведена блок-схема устройства.

Устройство для управления каналами содержит регистр I адреса текущей микрокоманды, буферный регистр 2 данных, узел 3 элементов И, буферный регистр 4 адреса назначения, буферный регистр 5 адреса микрокоманды, основной регистр 6 данных, регистр 7 контроля, основной регистр 8 адреса назначения, основной регистр 9 адреса микрокоманды, первый коммутатор 10, узел 11 элементов ИЛИ, регистр 12 ошибок, элемент ИЛИ 13, второй коммутатор 14, элемент И 15, группу уп- равляюпшх входов 16 устройства, сумматор 17 по модулю два, группу адресных входов 18 устройства, первый блок 19 управления адресом локальной памяти или регистров каналов, сумматор 20 по модулю 2, процессор 21, блок 22 микропрограммного управления арифметико-логический блок 23, оперативную память 24, локальную память 23, блок 26 формирования микрокоман- ;1Ы, блок 27 управления адресом мик-

каналов, процессор 21, блок 22 микро- npoi-раммного управления, арифметико- логический блок 23, оперативную память 24, локальную память 25, блок 26 формирования микрокоманды, блок 27 управления адресом микрокоманды, регистр 28 адреса канала, блок 29 выбора канала, синхронизатор 30 сбоев разделенного цикла, коммутатор 32 шин, блок 33 управления разделенным циклом, блок 34 управления микропрограммными прерываниями, блок 35 определения числа передаваемых байтов, блок 36 сравнения. 1 ил.

5

„ 35

рокоманды, регистр 28 адреса канала, блок 29 выбора адреса канала, синхронизатор 30 сбоев разделенного цикла, второй блок 31 управления адресом локальной памяти или регистров каналов, коммутатор 32 шин, блок 33 управления разделенным циклом, блик 34 управления микропрограммными прерываниями, блок 35 определения числа передаваемых байтов, блок 36 сравнения, входные шины 37-45 устройства, выходные шины 46-52 устройства.

Устройство работает следующим образом.

Операция ввода-вывода инициируется командой ввода-вывода, выполняемой процессором 21, В команде указан адрес канала и адрес устройства в канапе. Затем из фиксированной области оперативной памяти 24 считывается адресное слово канала, которое указывает адрес первого командного слова канала, содержащего код выполняемой команды, начальный адрес данных, счетчик передаваемых байтов и специальные признаки. Операция передачи данных в дальнейшем проходит под управлением командного слова канала, заполненного микропрограммой, реализующей команду ввода-вьшода, в рабочей области локальной п амяти 25 для каждого канала и в регистрах каналов. Для адресации областей локальной памяти для каналов и регистров каналов микропрограмма заносит в регистр 28

номер канала, на котором выполняется команда. Номер канала поступает в блок 29 выбора адреса канала, которы формирует потенциал выбранного в дан ный момент канала. При выполнении микрокоманды, обращающейся к области локальной памяти 25, по потенциалу канала и управляющему сигналу 16 блоки 19 и 31 вырабатывают коммутирую- пщй сигнал 47, который адресует область локальной памяти 25 выбранного канала, а также поступает в коммутатор 32 шин, разрегаая коммутацию выбранного канала с устройством. При считывании командного слова канала код выполняемой команды, два младших бита адреса, четыре младших бита счетчика байтов и специальные признаки заносятся в регистры скоммутиро- ванного канала.

Получив всю необходимую информацию, канал освобождает процессор 21 для выполнения следующих команд и продолжает работу, используя информа цию, расположенную в локальной памяти 25 и регистрах канала при помощи разделенных циклов, которые служат для передачи данных между каналом и оперативном памятью 24, следуюш 1х микропрограмм: обработки состояния, организации цепочки команд и цепочки данных, косвенной адресации данных.

При необходимости вызвать соответствующую микропро -рамму канал устанавливает запрос на микропрограммное прерывание, который вместе с кодом вызываемой микропрограммы через группу тин 39 запросов поступает в блок 27 и в блок 34.

Блок 34 по синхронизирующему сигналу с шины 16, вырабатываемому блоком 22, фиксирует запросы от каналов и определяет наиболее приоритетньй, причем наивысший приоритет у канала с меньщим номером. Исключение составляет запрос на микропрограмму косвенной адресации данных, который обладает наименьшим приоритетом, т.е. этот запрос обрабатывается только после обслужива1шя запросов других каналов, даже менее приоритетных.

Способ обнаружения отибок в устройстве Основан на введении дополнительной аппаратуры для формирования кода, в котором машинная ошибка сводится к логической ошибке. Схемы контроля рассчитаны в основном на обна

Q15 20

25 зо

Q

дс

50

5

ружение однократных и нечетных мног-о- кратных ошибок. Основным методом контроля Является контрол) по нечетности шин. Схема: блок контроля и сумматор 17, обнаруживая четное число единиц (включая контрольное),выдает сигнал оушбки. Кроме контроля по нечетности используется и другие методы, в частности контроль дублированием блока управления адресом локальной памяти или регистров каналов, для чего кроме основного блока 19 приведены второй блок 31 и блок 36 сравнения, выдаюш,ий сигнал ошибки.

Восстановление после сбоя рассчитано на перемежающиеся сбои, которые вызываются изменением таких факторов, как температура, изменение напряжения вторичных источником питания, помехи и т.д. и заключаются в повторении сбойной микрокоманды. Для повторения необходимо иметь адрес сбойной микрокоманды и исходные операнды.

В выбранной системе микрокоманд часть функ1Ц1й текущей микрокоманды выполняется в цикле следующей микрокоманды. Поэтому сбой каждой микрокоманды может в зависимости от его типа фиксироваться в ее цикле или в следующем и запоминать информацию для создания контрольной точки для восстановления нужной для сбойной микрокоманды (ошибка типа 1) и предьщущей (типа 2), отсюда следует, что для восстановления необходимо два каскада регистров, запоминающих состояние до сбоя - основные регистры отражают состояние для предыдущей микрокоманды, а буферные - для текущей микрокоманды.

В каждой микрокоманде состояние буферного регистра адреса микрокоманды 5 переписывается в основной регистр 9 адреса микрокоманды, а затем в буферный регистр 5 переписьшается текущее значение адреса микрокоманды из регистра I адреса текущей микрокоманды, причем стробы для занесения в указанные регистры поступают по ишне 16 с выхода блока 22.

При этом происходит занесение в буферные регистры данных 2 и адреса назначения А и основные регистры 6 и 8 соответственно. При возникновении сбоя сигнал об опшбке от одного из сумматоров 17 по модулю два или из блока 36 поступает на группу элемен5137232

тов и 3, на вход которой поступают стробы, с выхода блока 22 по шине 16, а с выходов группы узла элементов И 3 поступают на вход регистра 7 и на г вход группы узла элементов ИЛИ 1I, где объединяются по типам ошибок в зависимости от времени возникновения, С выхода группы узла элементов ИЛИ 11 типы ошибок поступают в регистр 1210 и на коммутатор 14,на второй вход которого с выхода блока 29 поступает потенциал канала, при работе которого возник сбой, а на первый вход - стробы с выхода синхронизатора 30.

15

Разделенный цикл служит для обмена данными между памятью и каналами и выполняется как микрокоманда Память, Ои может прерывать любую выполняющуюся микропрограмму, а сбои, которые могут возникнуть в разделенном цикле, относятся не к прерванной микропрограмме, обслуживающей какой- либо канал, а к каналу, по требованию которого выполнялся разделенный цикл. Коммутатор 14 и синхронизатор 30 служат для разделения сбоев в микропрограммах и в разделенных циклах и для определения связанных с этими процедурами каналов. Информационный сигнал в синхронизатор 30 поступает с выхода блока 33 управления разделенным циклом, Стробированный сигнал .сбоя в разделенном цикле с выхода коммутатора 14 через выход устройства по шине 51 поступает в каналы для установки сбоя в канале.

Кроме того, выход синхронизатора 30 блокирует установку регистра 12, Выход регистра 12 ошибок собирается элементом ИЛИ 13 для выработки общего сигнала ошибки, который с выхода элемента ИЛИ 13 подается на вход элемента И 15 для блокировки строба переписи из буферных регистров 5, 2 и 4 в основные регистры 9, 6 и 8 соответственно. Строб переписи, заведенный с выхода блока 22 на вход элемента И 15, проходит или не проходит через элемент И 13 в зависимоти от блокировки с выхода элемента ИЛИ 13, Основные регистры 9, 6 и 8 и регистр 7 контроля через коммутатор 10 могут быть прочитаны и проанализированы микропрограммой восстновления.

5

0

5

0

5

0

5

0

5

Формула изобретения

Устройство для управления каналами по ант, ев, № 877519, о т л и - ч а ю I l е f с я тем, что, с целью повышения надежности за счет восстановления после сбоя любой микропрограммы работы устройства, в него введены регистр адреса текущей микрокоманды, основной и буферньш регистры данных, второй блок управления адресами локальной памяти и регистров каналов, основной и буферный регистры адреса микрокоманды, регистр контроля, два коммутатора, регистр ошибок, синхронизатор сбоев разделенного цикла, блок сравнения, узел элементов ИЛИ, узел элементов И, элемент ИЛИ, элемент И, причем группа управляю1тих входов устройства соединена с уцравляюпц1ми входами регистра адреса текущей микрокоманды, буферных регистров адреса микрокоманды данных адреса назначения, второго блока управления адресами локальной памяти и регистров каналов, синхронизатора сбоев разделенного цикла, регистра контроля, узла элементов И и первым входом элемента И, группы адресных входов устройства соединены с группой информационных входов регистра адреса текущей микрокоманды, выходы которого соединены с группой информационных входов буферного регистра адреса микрокоманды, выходы которого соединены с группой информационных входов основного регистра адреса микрокоманды, выходы которого соединены с первой адресной группой входов первого коммутатора, информационная, управляющая и вторая адресные группы входов которого соединены с выходами соответственно основного регистра данных, регистра контроля и основного регистра адреса назначения, выход первого коммутатора соединен с первой информационной адресной группой выходов устройства, информационная группа входов которого соединена с группой информационных входов буферного регистра данных, выходы которого соединены с группой информационных входов основного регистра данных, информационные выходы первого блока управления адресами локальной памяти и регистров каналов соединены с первой группой входов блока сравнения и группой информационных входов буферного регистра адреса назначения, выходы которого соединены с группой информационных входов основного регистра адреса назначения, выход блока управления разделением циклов соединен с информационньм входом синхронизатора сбоев разделенного цикла, выход которого соединен с управляющими входами второго коммутатора и регистра ошибок, выходы блока выбора адреса канала соединены с адресной группой входов второго коммутатора и группой информационных входов второго блока управления адресами локальной памяти и регистров каналов, информационные выходы которого соединены с второй группой входов блока сравнения, выход которого и группа контрольных входов устройства соединены с группой входов узла элементов И, выходы которого соединены с группой информационных входов регистра контроля и через узел элементов ИЛИ - с группой информационных входов регистра ошибок и информационной группой выходов второго коммутатора, выходы которого являются второй информационно-адресной группой выходов устройства, выход регистра ошибок через элемент ИЛИ соединен с контрольным входом блока управления адресом микрокоманд и вторым входом элемента И, выход которого соединен с управляющими входами основных регистров адреса микрокоманды, данных и адреса назначения.

| Устройство для управления каналами | 1979 |

|

SU877519A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-07—Публикация

1984-04-20—Подача