1

Изобретение относится к вычислительной технике и может быть использовано при построении надежных микропроцессорных систем и является усовершенствованием изобретения по авт. св. № 1260960.

Цель изобретения - повышение достоверности контроля.

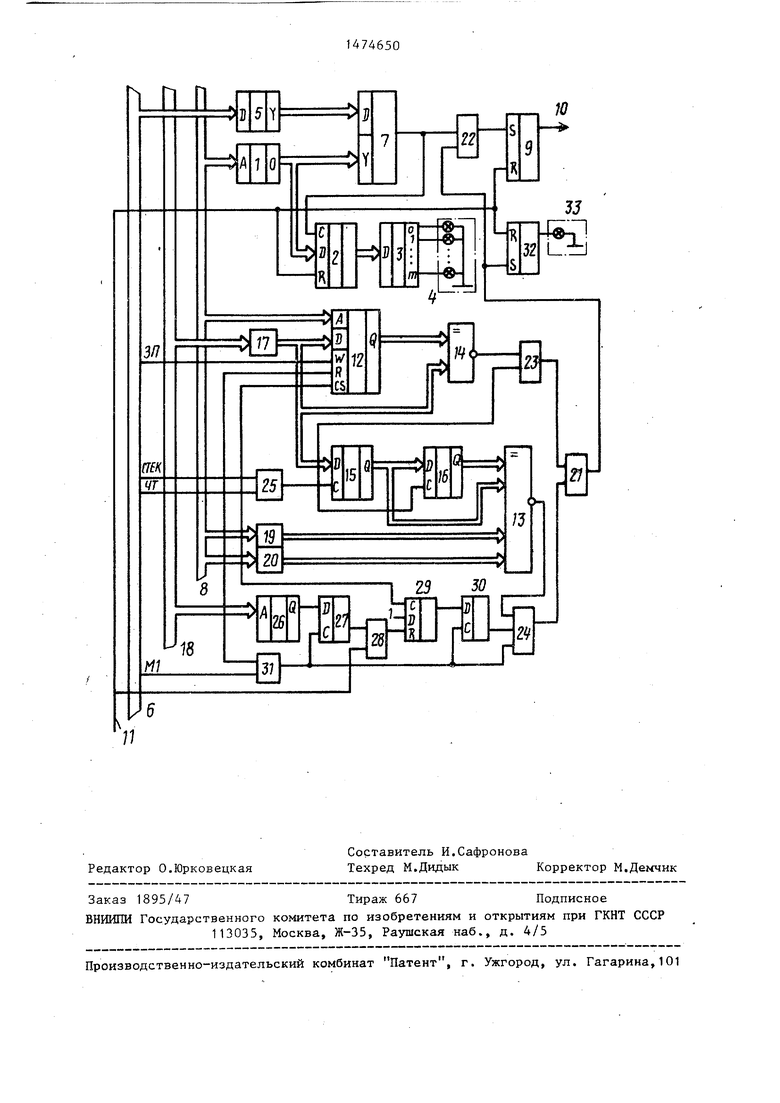

На чертеже изображена структурная схема устройства.

Устройство для контроля микропроцессорной системы содержит последовательно соединенные первый блок 1 постоянной памяти, первый регистр 2, дешифратор 3 и блок 4 элементов индикации, пифратор 55 вход которого подключен к управляющей шине 6 контролируемой микропроцессорной системы, мультиплексор 7Э адресный вход 8 для подключения к шине адреса контролируемой микропроцессорной системы, первый триггер 9, выход которого является выходом 10 ошибки устройства, вход 11 сброса устройства, блок 12 оперативной памяти, вторую 13 и первую 14 схемы сравнения, второй 15 и третий 16 регистры, первый узел 17 свертки по модулю два, вход 18 для подключения шины данных микропроцессорной системы, второй 19 и третий 20 узлы свертки по модулю два, второй 21 и первый 22 элементы ИЛИ, первый 23 и второй 24 элементы И, третий элемент И 25, второй блок 26 постоянной памяти, четвертьй триггер 27, третий элемент ИЛИ 28, третий триггер 29, пятый триггер 30, четвертьй элемент И 31, второй триггер 32 и элемент 33 индикации.

Nl

Ј

CD Oi

Устройство работает следующим образом.

Устройство обеспечивает контроль наиболее распространенной микропро- цессорной системы с тремя шинами: шиной адреса, шиной данных и шиной управления. Для обеспечения контроля микропроцессорной системы шина 6 устройства подключается к управляющей шине контролируемой системы, вход 8 к ее адресной шине, вход 18 - к шине данных, вход 11 сброса - к цепи сброса микропроцессора, а выход 10 сигнала ошибки - к входу запроса преры- вания микропроцессора.

В общем случае контролируемая микропроцессорная система содержит постоянную память (ПЗУ), оперативную память (ОЗУ), в которой организуется стек, и устройства ввода-вывода (УЕВ На стадии программирования программист должен распределить зону адресного пространства микропроцессора и закрепить за каждым из устройств сие- темы определенную адресную зону. При этом, как правило, часть адресного пространства остается неиспользован- ной.

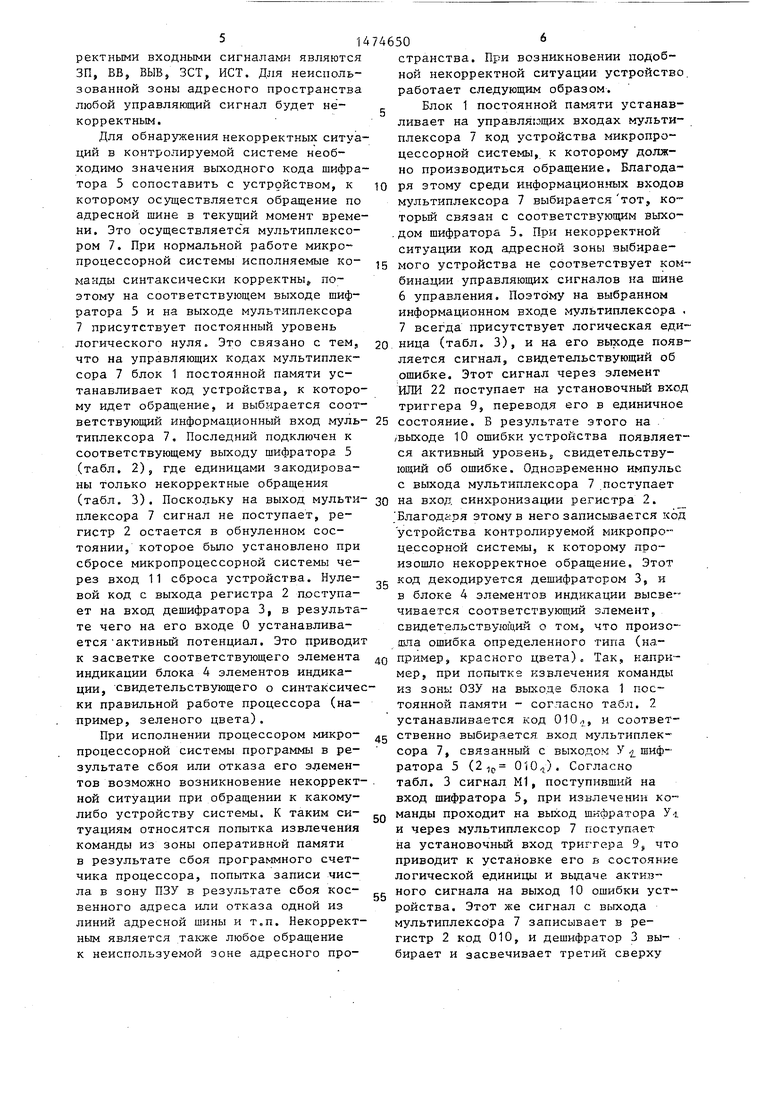

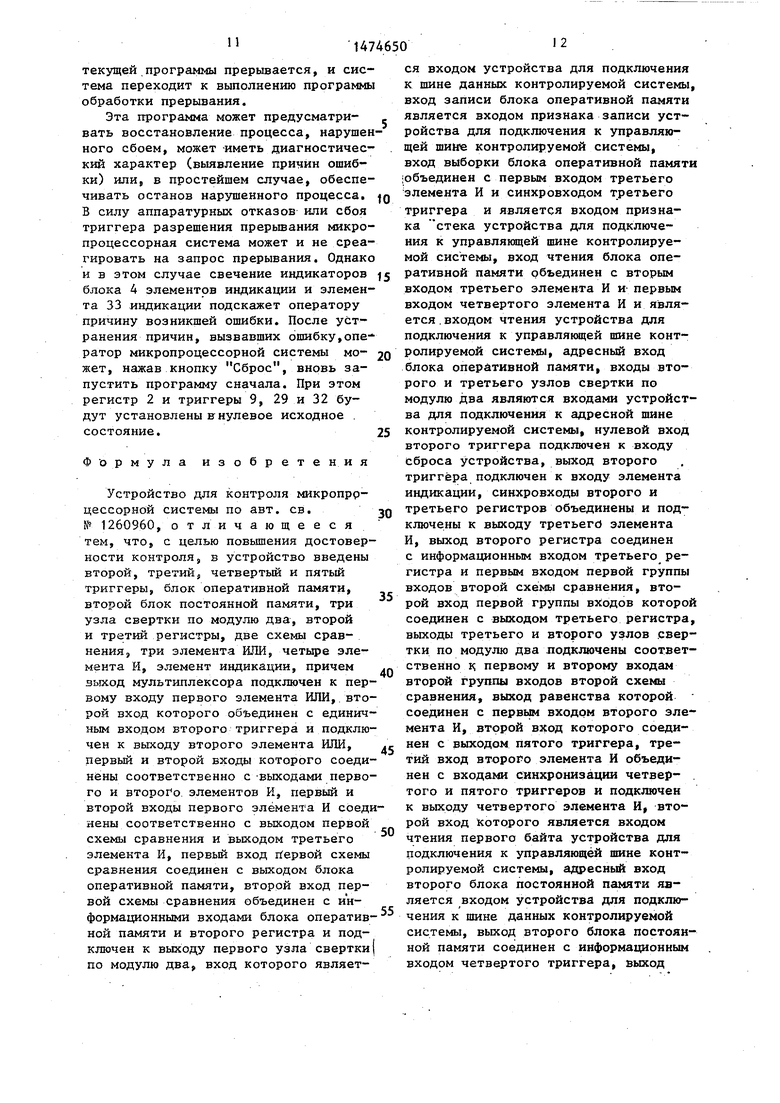

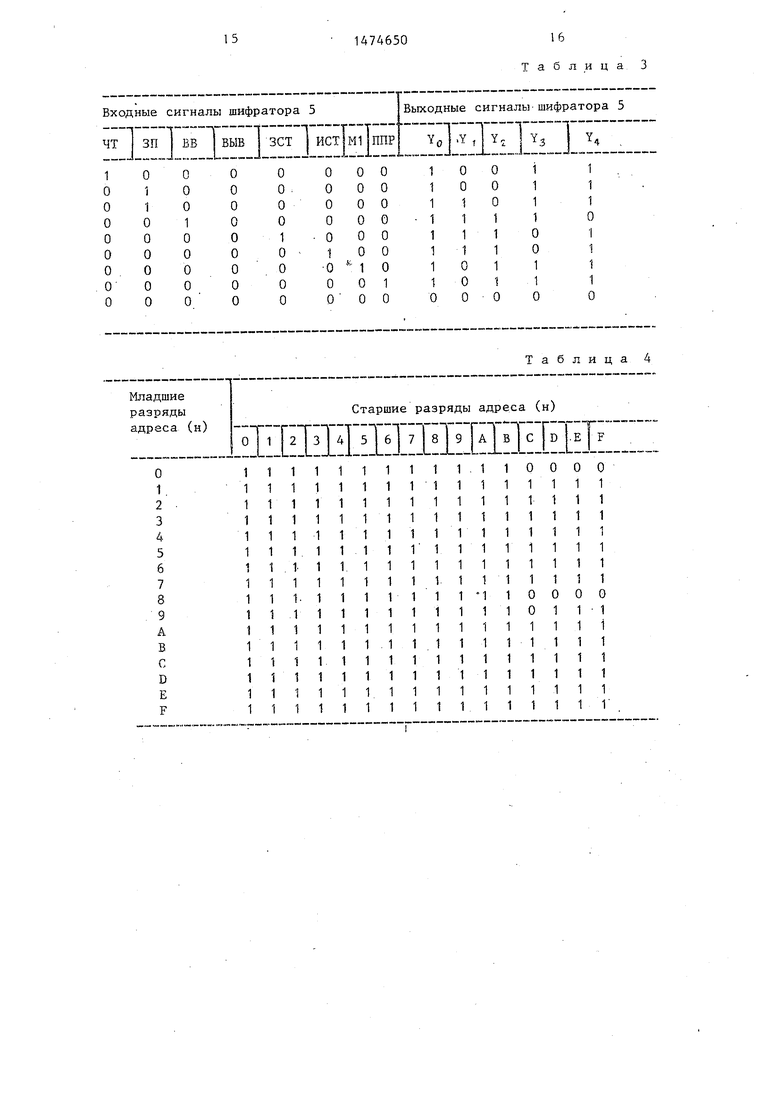

Для обращения к конкретному уст- ройству микропроцессор формирует на шине адреса соответствующий код, обеспечивающий активацию выбранного устройства. Для упрощения селекции выбираемого устройства распределение адресов осуществляется таким образом, чтобы по старшим разрядам адреса можно было определить устройст- во0 к которому осуществляется обращение. Количество используемых для этого старших разрядов определяется минимальным объемом адресного пространства, закрепляемого за каким-либо устройством микропроцессорной системы. Пусть, например,, для идентифи- кации выбираемого устройства системы использовано 5 разрядов Ац, Af , А13, А адресной шины и зоны адресного пространства распределены в соответствии с табл. 1.

При таком составе контролиуемой микропроцессорной системы устройство, к которому осуществляется обращение, может быть указано трехразрядным кодом. Перекодирование входного кода на старших разрядах шины адреса в код, указывающий тип выбираемого устройства, осуществляется блоком 1 пос0 5

0 5

0 0 5

5

0

5

тоянной памяти. Для этого в нем по соответствующим адресам хранятся коды устройств микропроцессорной системы. Пусть код ПЗУ-001, код ОЗУ-010,

код стека -011, код УВВ - 100, а код неиспользованной зоны - 000. Тогда в блоке 1 постоянной памяти должны храниться коды в соответствии с табл 2 о

Таким образом, при обращении микропроцессора к какому-либо конкретному устройству системы на выходах блока 3 постоянной памяти формируется соответствующий код, и мультиплексор 7 выбирает соответствующий информационный вход, подключенный к одному из выходов шифратора 5, вход которого подключен к управляющей шине 6 контролируемой системы. В состав шины управления типовой микропроцессорной системы входят следующие сигналы: Чтение памяти (ЧТ); Запись IB память (ЗП) (ВВ); Вывод (ВЫВ); Стек (СТЕК); Загрузка в стек (ЗСТ); Извлечение из стека (ИСТ); Чтение первого байта коман-г ды (М1); Подтверждение прерывания (ППР).

При этом предполагается, что все сигналы, за исключением сигнала Стек, стробированы соответствующими строб-сигналами микропроцессора Прием (DB1N) или Запись (WR).. При этом ЗСТ Стек - Запись, ИСТ Стек - Прием.

Очевидно, что при нормальном функционировании системы микропроцессор генерирует управляющие сигналы в строгом соответствии с устройством, к которому обращается. Нарушение этого соответствия свидетельствует об отказе или сбое в системе и является некорректной ситуацией. Шифратор 5 обеспечивает кодирование этих ситуаций в соответствии с допустимыми комбинациями управляющих сигналов. Функционирование шифратора 5 описывается табл. 3.

Каждый разряд выходного кода шифратора 5 соответствует устройству контролируемой микропроцессорной системы (У0 - неиспользуемая зона адресного пространства, У-i - ПЗУ, У г ОЗУ, У-j - стек, У 4 устройства ввода-вывода) . Единицы правой части табл, 3 соответствует некорректным, а нули - корректным синтаксическим ситуациям. Например, для ПЗУ некор

рентными входными сигналами являются ЗП, ВВ, ВЫВ, ЗСТ, ИСТ. Для неиспользованной зоны адресного пространства любой управляющий сигнал будет некорректным.

Для обнаружения некорректных ситуаций в контролируемой системе необходимо значения выходного кода шифратора 5 сопоставить с устройством, к которому осуществляется обращение по адресной шине в текущий момент времени. Это осуществляется мультиплексором 7. При нормальной работе микропроцессорной системы исполняемые команды синтаксически корректны поэтому на соответствующем выходе шифратора 5 и на выходе мультиплексора 7 присутствует постоянный уровень логического нуля. Это связано с тем, что на управляющих кодах мультиплексора 7 блок 1 постоянной памяти устанавливает код устройства, к которому идет обращение, и выбирается соответствующий информационный вход муль- типлексора 7, Последний подключен к соответствующему выходу шифратора 5 (табл. 2), где единицами закодированы только некорректные обращения

/выходе 10 ошибки устройства появля ся активный уровеньs свидетельству ющий об ошибке. Одновременно импул с выхода мультиплексора 7 поступае

(табл. 3). Поскольку на выход мульти- зо на вход синхронизации регистра 2.

плексора 7 сигнал не поступает, регистр 2 остается в обнуленном состоянии, которое было установлено при сбросе микропроцессорной системы через вход 11 сброса устройства. Нулевой код с выхода регистра 2 поступает на вход дешифратора 3, в результате чего на его входе 0 устанавливается активный потенциал. Это цриводит к засветке соответствующего элемента индикации блока 4 элементов индикации, свидетельствующего о синтаксически правильной работе процессора (например, зеленого цвета).

При исполнении процессором микропроцессорной системы программы в результате сбоя или отказа его элементов возможно возникновение некорректной ситуации при обращении к какому- либо устройству системы. К таким ситуациям относятся попытка извлечения команды из зоны оперативной памяти в результате сбоя программного счетчика процессора, попытка записи числа в зону ПЗУ в результате сбоя косвенного адреса или отказа одной из линий адресной шины и т,п. Некорректным является также любое обращение к неиспользуемой зоне адресного про Благод ря этому в него записывается устройства контролируемой микропро цессорной системы, к которому произошло некорректное обращение. Это Зс код декодируется дешифратором 3, и в блоке 4 элементов индикации высв чивается соответствующий элемент, свидетельствующий о том, что произ шла ошибка определенного типа (например, красного цвета). Так, напр

40

45

50

55

мер, при попытке извлечения команд из зоны ОЗУ на выхода блока 1 постоянной памяти - сопасно табл. 2 устанавливается код 010,1, и соотве ственно выбирается вход мультиплек сора 7, связанный с выходом ратора 5 (21с 0(0,,). Согласно табл. 3 сигнал М1, поступивший на вход шифратора 5, при извлечении к манды проходит на выход шифратора и через мультиплексор 7 поступает на установочный вход триггера 9f ч приводит к установке его в состоян логической единицы и выдаче активного сигнала на выход 10 ошибки ус ройства. Этот же сигнал с выхода мультиплексора 7 записывает в регистр 2 код 010, и дешифратор 3 выбирает и засвечивает третий сверху

5

5

0

странства. При возникновении подобной некорректной ситуации устройство работает следующим образом.

Блок 1 постоянной памяти устанавливает на управляющих входах мультиплексора 7 код устройства микропроцессорной системы, к которому должно производиться обращение. Благодаря этому среди информационных входов мультиплексора 7 выбирается тот, ко™ торый связан с соответствующим выхо- .дом шифратора 5. При некорректной ситуации код адресной зоны выбираемого устройства не соответствует комбинации управляющих сигналов на шине

6управления. Поэтому на выбранном информационном входе мультиплексора .

7всегда присутствует логическая единица (табл. 3), и на его выходе появляется сигнал, свидетельствующий об ошибке. Этот сигнал через элемент ИЛИ 22 поступает на установочный вход триггера 9, переводя его в единичное состояние. В результате этого на

/выходе 10 ошибки устройства появляется активный уровеньs свидетельствующий об ошибке. Одновременно импульс с выхода мультиплексора 7 поступает

Благод ря этому в него записывается код устройства контролируемой микропроцессорной системы, к которому произошло некорректное обращение. Этот код декодируется дешифратором 3, и в блоке 4 элементов индикации высвечивается соответствующий элемент, свидетельствующий о том, что произошла ошибка определенного типа (например, красного цвета). Так, напри

5

0

5

мер, при попытке извлечения команды из зоны ОЗУ на выхода блока 1 постоянной памяти - сопасно табл. 2 устанавливается код 010,1, и соответственно выбирается вход мультиплексора 7, связанный с выходом У шифратора 5 (21с 0(0,,). Согласно табл. 3 сигнал М1, поступивший на вход шифратора 5, при извлечении команды проходит на выход шифратора У-i и через мультиплексор 7 поступает на установочный вход триггера 9f что приводит к установке его в состояние логической единицы и выдаче активного сигнала на выход 10 ошибки устройства. Этот же сигнал с выхода мультиплексора 7 записывает в регистр 2 код 010, и дешифратор 3 выбирает и засвечивает третий сверху

714

элемент индикации блока 4 элементов индикации. Этот элемент можно назвать Ошибка при обращении к ОЗУ. Указанная информация может использоваться при ремонте контролируемой системы. В рассмотренном типе некорректных синтаксических ситуаций комбинация управляющих сигналов на шине 6 управления является корректной9 а некорректно ее сочетание с адресом на адресной шине системы.

Однако, кроме подобных некорректных ситуаций, в результате сбоев и отказов могут возникать и другие, связанные с искажением информации, хранимой в стековой области ОЗУ9 или сбоем программного счетчика при возвратах из подпрограмм.

Известно, что стековая область ОЗУ используется для временного хранения содержимого внутренних регистров микропроцессора, а также для хранения адресов возвратов из подпрограмм. Очевидно, что для нормального функционирования микропроцессорной системы необходимо обеспечить достоверность информации, считываемой из стека. В большинстве МПС (например, на базе микропроцессора КР580ИК80А считывание информации осуществляется з двух последовательных -машинных циклах обращения к стеку„ При этом адрес возврата, извлеченной из стека, загружается в программный счетчик микропроцессора, что обеспечивает выполнение следующей команды по данному адресу. При работе МПС в условиях помех эта информация может искажаться. При этом возможны две некорректные ситуации: из стека считывается некорректная информация, из стека считывается корректный адрес возврата, но искажение происходит в момент загрузки в программный счетчик.

Для обнаружения первой некорректной ситуации вся информация, записываемая в стек МПС, записывается такж в блок 12 оперативной памяти. При этом для уменьшения разрядности бло- |ка 12 информация записывается в него в преобразованном виде. Узел 17 свертки преобразует полворазрядныи код шины данных в усеченный код (в простейшем случае - в код по модулю два)

В качестве узла 17 свертки может быт

использована, например, схема контроля четности и нечетности К155ИП2, Количество младших разрядов шины адтэе0

5

0

5

са, подключенных к адресным входам блока 12 оперативной памяти, определяется исходя из максимального числа уровней вложения в стек для конкретной микропроцессорной системы. Запись, информации в блок 12 оперативной памяти производится лишь при наличии сигналов Запись и Стек на шине 6 управляющих сигналов системы. При извлечении информации из стека МПС на шину данных схема 14 сравнения осуществляет контроль соответствия данных, установленных на шине данных системы, и данных, считываемых с блока 12 оперативной памяти. Оценка результата этого контроля осуществляется с помощью элемента И 23 в момент появления сигнала Чтение на шине 6 управляющих сигналов. Если эти данные не совпадают, то импульс с выхода элемента И 23 через элемен- ты ИЛИ 21 и 22 вызывает переход триггеров 32 и 9 из исходного состояния, в котором они находились в результате действия сигнала Сброс в начале работы микропроцессорной системы, в активное. В результате этого на выходе 10 ошибки устройства появляется активный уровень, свидетельствующий о некорректной ситуации в контролируемой системе. Одновременно с этим загорается элемент 33 индикации, указывая оператору на тип ошибки.

Для обнаружения второй некорректной ситуации информация, установленная на шине данных в машинных циклах чтения стека, записывается в последовательно соединенные регистры 15 и 16. Запись осуществляется по синхровходу регистров при наличии сигналов Стек и Чтение на шине 6 управляющих сигналов контролируемой системы. При нормальном функционировании в микро- 5 процессорных системах (например, на базе микропроцессора КР580ИК80А) обращение к стеку всегда осуществляется в двух соседних машинных циклах работы процессора. Поэтому информа0

5

0

0

ция, извлекаемая из стека в первом цикле, записывается с выхода узла 17

15, а во втором 15 записывается в регистр 16 - предыдущее значение. Смена информации в

свертки в регистр цикле - в регистр новое значение а

регистрах 15 и 16

о суще ствляется лишь при выполнении команд, связанных с циклами чтения стека. Таким образом8 в регистрах 15 и 16 информация может представлять либо адрес последнего возврата из подпрограммы, либо содержимое регистровой пары микропроцессора. Сигналы с выходов регистров 15 и 16 поступают на первую группу входов схемы 13 сравнения, осуществляющей контроль выполнения перехода в программе по адресу возврата из текущей подпрограммы. Для этого на вторую группу входов схемы 13 сравнения поступает информация с адресной шины микропроцессорной системы. Эта информация поступает на схему 13 сравнения в преобразован ном виде с помощью узлов 19 и 20 свертки кодов, аналогичных узлу 17 свертки. Каждый из элементов 19 и 20 преобразует соответственно младшие и старшие байты адресной шины систе- мы, поскольку информация об адресе в регистрах 16 и 15 представлена в виде преобразованных младшего и старшего байтов адреса возврата из подпрограммы. Результат сравнения кодов с выхода схемы 13 сравнения оценивается с помощью элемента И 24 в момент приема кода очередной команды, если предыдущая команда была командо возврата из подпрограммы. Это проис- ходит следующим образом. Информация о типе выполняемой команды (команды возврата из подпрограммы или остальные) хранится в блоке 26 постоянной памяти. В момент появления на шине данных микропроцессорной системы первого байта команды (на шине 6 управления системы присутствуют сигналы М1 и Чтение) производится запись сигнала с выхода блока 26 постоянной памяти в триггер 27.

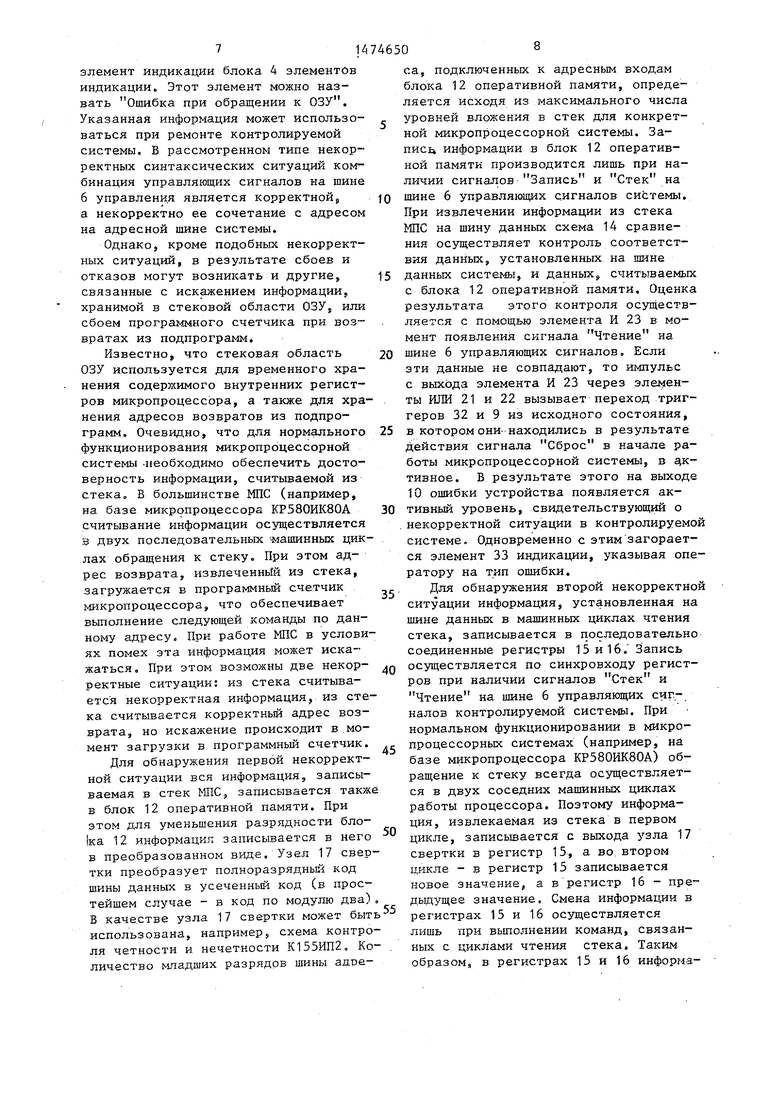

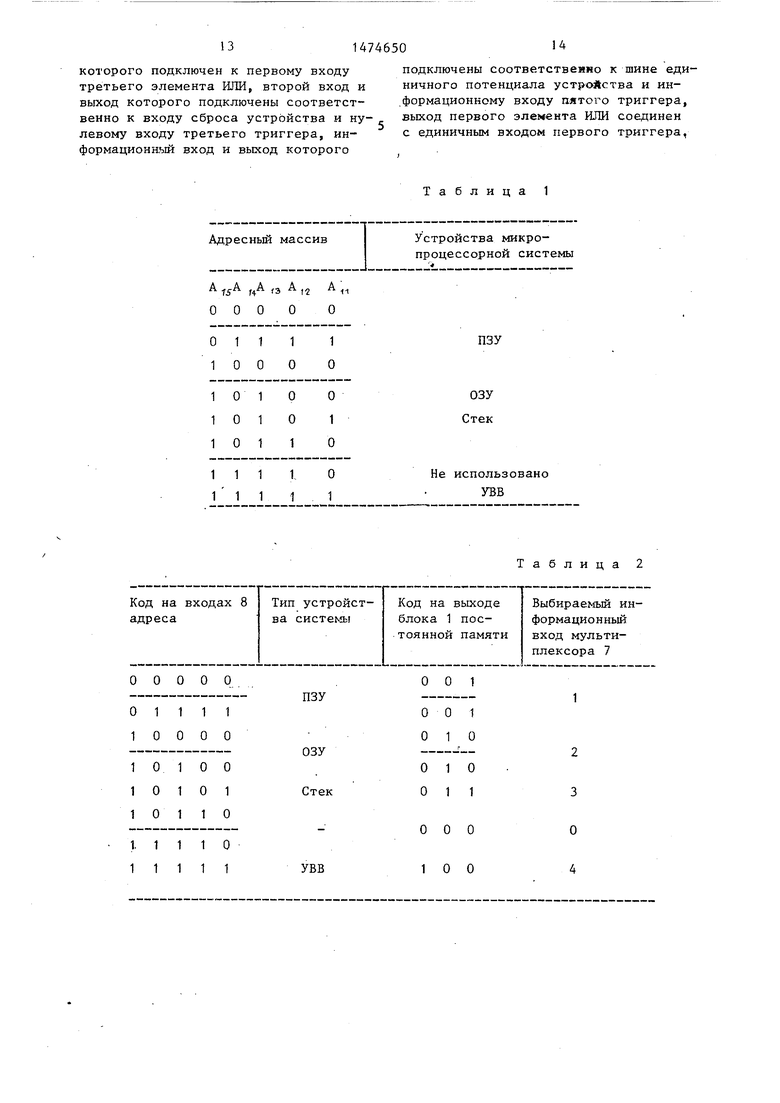

Блок 26 постоянной памяти предназначен для выделения из всей совокупности команд, выполняемых микропроцессором, команд возврата из подпрограммы. Поэтому код выполняемой команды в данном устройстве выступает как адрес одноразрядной ячейки блока 26 постоянной памяти. Для правильной работы устройства с микропроцессорной системой (например, на

базе микропроцессора КР580ИК80А) кода, хранимые в блоке 26 постоянной памяти,должны соответствовать данным приведенным в табл. 4.

Каждая клеточка табл. 4 соответствует одному из 256 возможных адресов Все команды возврата из подпрограмм закодированы нулем, остальные коман

Q 0 5 Q

0

5

0

5

ды - единицей. В начале работы систем по сигналу Сброс триггер 29 находится в исходном нулевом состоянии. Если выполняются команды, не связанные с возвратом из подпрограмм, то триггер 27 находится в единич«ом состоянии. Сигнал логической единицы с выхода триггера 27 через элемент ИЛИ

28удерживает, по входу сброса триггер

29в исходном состоянии. Если выполняется команда возврата из подпрограммы, то сигнал логического нуля

с выхода триггера 27 через элемент ИЛИ 28 снимает управление триггером 29 по вхрду сброса, .При наличии на управляющей шине 6 первого сигнала Стек, поступающего на синхровход триггера 29, сигнал логической единицы на D-входе триггера 29 переводит его в активное состояние. В этом состоянии триггер 29 находится до момента приема следующей команды микропроцессора, не связанной с возвратом из стека. Состояние триггера 29 нужно рассматривать как признак контроля адреса следующей команды микропроцессора. Этот признак в каждом машинном цикле выборки первого байта команды по сигналу с выхода элемента И 31 записывается в триггер 30. При выполнении команд, не связанных с возвратом из подпрограммой, триггер 30 постоянно находится в нулевом состоянии, запирая элемент И 24. Так как при выполнении команды возврата триггер 29 переходит в единичное состояние, то при выборке первого байта следующей команды триггер 30 также переходит в единичное состояние. Это обеспечивает оценку результата сравнения ожидаемого и фактического адресов, сформированного на выходе схемы 13 сравнения. Если эти адреса не совпадают, то на выходе схемы 13 сравнения устанавливается единичный потенциал, и стройиру- ющий сигнал с выхода элемента И 31 проходит через элементы И 2ч и ИЛИ 2 и переключает триггеры 9 и 32, В результате этого на выходе 10 ошибки устройства появляется активный уровень и загорается элемент 33 индикации, свидетельствуя о возникновении ошибки в контролируемой системе.

Выход 10 ошибки устройства соеди- ,няется с входом запроса прерывания микропроцессорной системы, поэтому при возникновении ошибки выполнение

текущей программы прерывается, и система переходит к выполнению программы обработки прерывания.

Эта программа может предусматри

вать восстановление процесса, нарушенного сбоем, может иметь диагностический характер (выявление причин ошибки) или, в простейшем случае, обеспечивать останов нарушенного процесса, В силу аппаратурных отказов или сбоя триггера разрешения прерывания микропроцессорная система может и не среагировать на запрос прерывания. Однако и в этом случае свечение индикаторов блока 4 элементов индикации и элемента 33 индикации подскажет оператору причину возникшей ошибки. После устранения причин, вызвавших ошибку,оператор микропроцессорной системы мо- жет, нажав кнопку Сброс, вновь запустить программу сначала. При этом регистр 2 и триггеры 9, 29 и 32 будут установлены в нулевое исходное состояние.

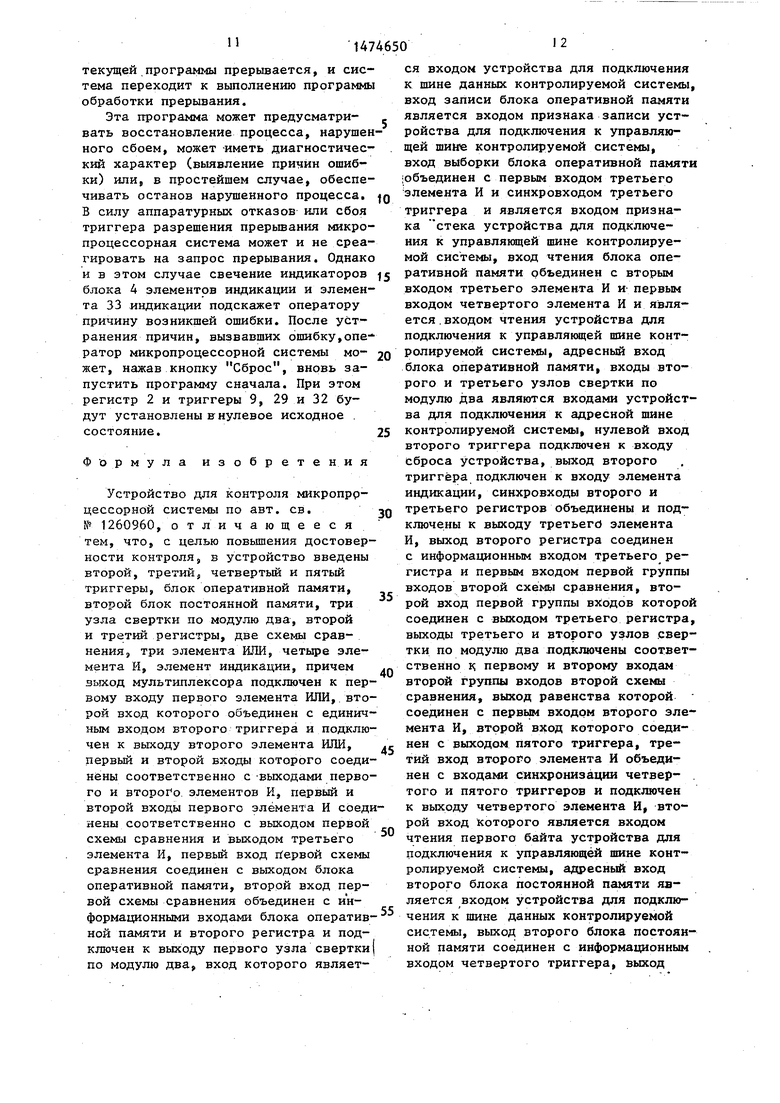

Формула изобретения

Устройство для контроля микропроцессорной системы по авт. св. № 1260960, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введены второй, третий; четвертый и пятый триггеры, блок оперативной памяти, второй блок постоянной памяти, три узла свертки по модулю два, второй и третий регистры, две схемы сравнения, три элемента ИЛИ, четыре элемента И, элемент индикации, причем выход мультиплексора подключен к первому входу первого элемента ИЛИ, второй вход которого объединен с единичным входом второго триггера и подключен к выходу второго элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами первого и второго элементов И, первый и второй входы первого элемента И соединены соответственно с выходом первой схемы сравнения и выходом третьего элемента И, первый вход ггёрвой схемы сравнения соединен с выходом блока оперативной памяти, второй вход первой схемы сравнения объединен с информационными входами блока оператив- ной памяти и второго регистра и подключен к выходу первого узла свертки) по модулю два, вход которого являет

5

g5 0 5

,Q «с 5

0

ся входом устройства для подключения к шине данных контролируемой системы, вход записи блока оперативной памяти является входом признака записи устройства для подключения к управляющей шине контролируемой системы, вход выборки блока оперативной памяти объединен с первым входом третьего элемента И и синхровходом третьего

триггера и является входом признака стека устройства для подключения к управляющей шине контролируемой системы, вход чтения блока оперативной памяти объединен с вторым входом третьего элемента И и первым входом четвертого элемента И и является входом чтения устройства для подключения к управляющей шине контролируемой системы, адресный вход блока оперативной памяти, входы второго и третьего узлов свертки по модулю два являются входами устройства для подключения к адресной шине контролируемой системы, нулевой вход второго триггера подключен к входу сброса устройства, выход второго триггера подключен к входу элемента индикации, синхровходы второго и третьего регистров объединены и подключены к выходу третьего1 элемента И, выход второго регистра соединен с информационным входом третьего регистра и первым входом первой группы входов второй схемы сравнения, второй вход первой группы входов которой соединен с выходом третьего регистра, выходы третьего и второго узлов свертки по модулю два подключены соответственно к. первому и второму входам второй группы входов второй схемы сравнения, выход равенства которой соединен с первым входом второго элемента И, второй вход которого соединен с выходом пятого триггера, третий вход второго элемента И объединен с входами синхронизации четвертого и пятого триггеров и подключен к выходу четвертого элемента И, второй вход которого является входом чтения первого байта устройства для подключения к управляющей шине контролируемой системы, адресный вход второго блока постоянной памяти является входом устройства для подключения к шине данных контролируемой системы, выход второго блока постоянной памяти соединен с информационным входом четвертого триггера, выход

которого подключен к первому входу третьего элемента ИЛИ, второй вход и выход которого подключены соответственно к входу сброса устройства и нулевому входу третьего триггера, информационный вход и выход которого

подключены соответственно к шине единичного потенциала устройства и информационному входу пятого триггера, выход первого элемента ИЛИ соединен с единичным входом первого триггера,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1536384A1 |

| Устройство для контроля микропроцессорной системы | 1989 |

|

SU1640693A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1545221A1 |

| Устройство для синтаксического контроля программ микропроцессорной системы | 1985 |

|

SU1260960A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1460722A1 |

| Устройство для контроля микропроцессора | 1988 |

|

SU1599862A1 |

| Устройство для контроля микропроцессора | 1989 |

|

SU1817096A1 |

| Устройство прерываний микропроцессорной системы | 1988 |

|

SU1621030A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1559347A1 |

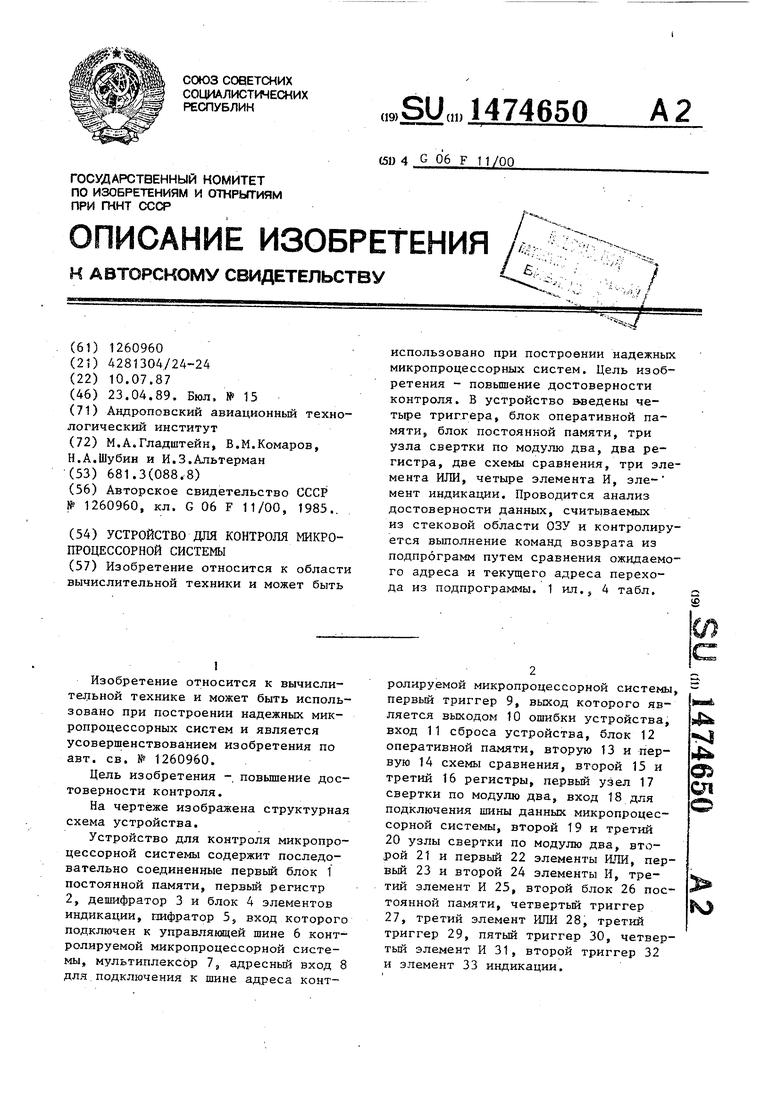

Изобретение относится к области вычислительной техники, может быть использовано при построении надежных микропроцессорных систем и является усовершенствованием изобретения по авт. св. N1260960. Цель изобретения - повышение достоверности контроля. В устройство введены четыре триггера, блок оперативной памяти, блок постоянной памяти, три узла свертки по модулю два, два регистра, две схемы сравнения, три элемента ИЛИ, четыре элемента И, элемент индикации. В устройстве проводится анализ достоверности данных, считываемых из стековой области ОЗУ. В устройстве контролируется выполнение команд возврата из подпрограмм путем сравнения ожидаемого адреса и текущего адреса перехода из подпрограммы. 1 ил., 4 табл.

Адресный массив Устройства микропроцессорной системы

«...«..« «----

fj Н э 12 -И

0000 О

01111ПЗУ

1000 О

1010ООЗУ

10101Стек

1011О

11110Не использовано

j j 1 i j

Таблица 2

Код на входах 8 Тип устройст- Код на выходе Выбираемый ин- адреса | ва системы блока 1 пос- формационный

тоянной памяти вход мультиплексора 7

00000001

ПЗУ1

01111001

10000 010

ОЗУ -2

1010001010101Стек 0113

10110

000О

11110

11111 УВВ1004

Таблица 1

Входные сигналы шифратора 5

3U | ВВ БЫВ ЗСТ ИСТ М1 ППР

ЧТ

Младшие разряды адреса (н)

Старшие разряды адреса (н)

О 1 Г2Т3 | 4Т 5 | 61 7 I 8 | 9 А | В | С JD I E I F

1111111111110000

1111111111111111 1111111111111111 1111111111111111 1111111111111111 1111111111111111 1111111111111111 1111111111111111

1111111111 110000 1111111111110111

1111111111111111 1111111111111111 1111111111111111 1111111111111111

1111111111111111

1 1

11111111111

1

Таблица 3

Выходные сигналы шифратора 5

Таблица 4

Старшие разряды адреса (н)

1

| Устройство для синтаксического контроля программ микропроцессорной системы | 1985 |

|

SU1260960A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-04-23—Публикация

1987-07-10—Подача