SK)

Os СЛ 00 СА 00 СЛ

Изобретение относится к вычислительной технике и технике связи и можеть быть использовано в системах передачи информации

Цель изобретения - повышение точности восстановления сигналов

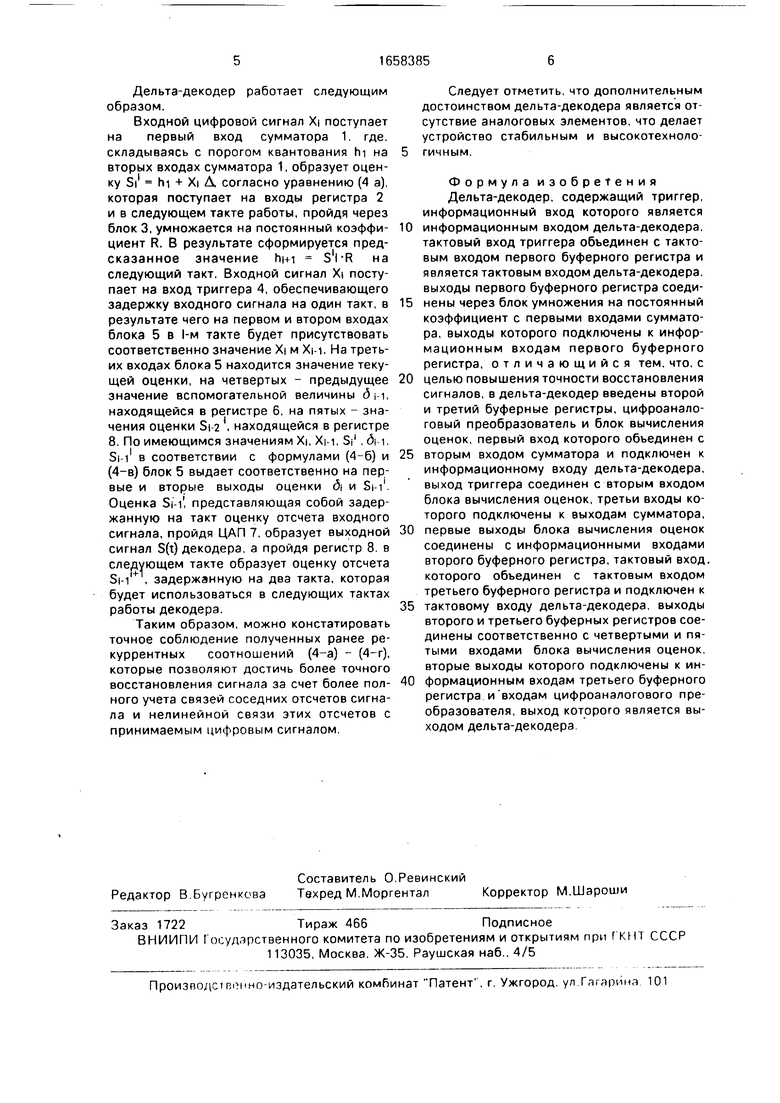

На чертеже представлена блок-схема дельта-декодера.

Дельта-декодер содержит сумматор 1, первый буферный регистр 2, блок 3 умножения на постоянный коэффициент, триггер 4, блок 5 вычисления оценок, второй буферный регистр 6, цифроаналоговый преобразователь (ЦАП) 7 и третий буферный регистр 8. На чертеже обозначены информационный и тактовый входы 9 и 10

Блок 3 умножения на постоянный коэффициент и блок 5 вычисления оценок могут быть выполнены на ПЗУ,

Для объяснения принципа работы дельта-декодера рассмотрим решение задачи синтеза дельта-кодека для гаусс-марковского процесса. Считаем входной сигнал, представленный отсчетами Si, 81-1, Si 2, Si з -Sa Si, которые квантуются кодером в порядке возрастания индекса Таким образом, имеем вектор отсчетов s(i) (Si, Si 1, ,Si), размерностью I, имеющий совместную плотность вероятностей

p(f(0) P(SI Si)

Для гаусс-марковского процесса

P(S(I)) P(Si/Si 1) -P(Si 1/Si 2) P(S2/Si) -P(Si),

где P(Sk/Sk-i)

(1 -Rf

X

ры, имеет вид системы i уравнений с i неизвестными

,VK, 2 D(1-R2)J P((,))dS(,)|

5,-h,

(2)

,V24,L P(5(,,ld§(0|

3w9«-l4

Система (2), хотя и имеет решение, од- нако не может в таком виде быть основой для синтеза оптимального декодера. Чтобы обеспечить возможость практической реализации алгоритма, будем считать, что оценки сигнала, полученные при задержке более чем 2 такта, практически равными, т е Sk Sk 1 при k I-2 Здесь верхний индекс указывает на номер такта, в котором производится оценивание отсчета S. Так,напри- мер, обозначение Si 2 означает оценку отсчета Si-2, получаемую в -м такте С учетом этого перепишем (2) в виде

25

, ,,2 D(l-RI)P(s(,))d5(.)j6ch

б

б- --,. ib.-,2 n7#|p(3.))dS,l

s;,-s:e

Первое уравнение описывает оптимальную оценку текущего отсчета, второе - пред- шествующего Для кодера Si1 RSi 1 + Xi Л где А const - шаг квантования в кодере Приравняв два выражения и произведя интегрирование для Si1 получим систему

|s;-«s , + &,,A,

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный дельта-кодер | 1988 |

|

SU1658384A1 |

| Дельта-кодер | 1989 |

|

SU1612375A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1990 |

|

SU1727131A1 |

| Дельта-кодек | 1987 |

|

SU1427572A1 |

| Дельта-модулятор | 1988 |

|

SU1658383A1 |

| Адаптивный телевизионный дельта-кодер | 1989 |

|

SU1690199A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| Устройство для передачи сигналов приращений с предсказанием | 1982 |

|

SU1089605A2 |

| Цифровой фильтр | 1986 |

|

SU1387174A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

Изобретение относится к вычислительной технике и технике связи. Его использование в системах передачи информации позволяет повысить точность восстановления сигналов. Дельта-декодер содержит сумматор 1, буферный регистр 2, блок 3 умножения на постоянный коэффициент и триггер 4. Благодаря введению блока 5 вычисления оценок, буферных регистров 6, 8 и цифроаналогового преобразователя 7 обеспечивается более полный учет связей соседних отсчетов сигнала. 1 ил.

X

exp j(Sk-RSk-1)2

2 D(1 -R2)

l,

где D - дисперсия сигнала S,

R - коэффициент корреляции соседних отсчетов сигнала S

В результате последовательного сравнения значения Si. Sa. 5з с порогами квантования hi, h2, Ьз передаются цифровые сигналы Xi, X2, Хз , характеризующие диапазон принадлежности величины Sk Так например, если Xk 1, то Sk hk и следовательно, диапазон Sk - ©k fhk °° в противном случае ©k - °°, h k

Таким образом, образуются векторы пе- реданных сигналов X(i) - (Хч X,) и областей квантования 0(i) (01,02 0i)

Точное решение, полученное для синтеза наилучшей с точки зрения минимума мощности ошибки восстановления структу

где S-a DO-R HpffMldSMl

Lk h

)eri(x). интеграл вероятностей

1 /J t

Полученную систему удобно переписать в виде рекуррентных уравнений

(4-а) Si RS, i1 1 X, Л

(4-6)5,, -2(,1(ux,x,,erf

(4-в)5, -R(SiiM S, i ) + X, A

(4-г)5м SM

Первое из этих уравнений формирует оценку текущего отсчета второе формирует оценку предыдущего отсчета с учетом ему предшествовавшего и последующего отсчетов что повышает точность оценивания Величина б является вспомогательной

Дельта-декодер работает следующим образом.

Входной цифровой сигнал Х| поступает на первый вход сумматора 1. где. складываясь с порогом квантования hi на вторых входах сумматора 1, образует оценку Si1 hi + Х| Л согласно уравнению (4 а), которая поступает на входы регистра 2 и в следующем такте работы, пройдя через блок 3, умножается на постоянный коэффициент R. В результате сформируется предсказанное значение Ьм s l-R на следующий такт. Входной сигнал X) поступает на вход триггера 4, обеспечивающего задержку входного сигнала на один такт, в результате чего на первом и втором входах блока 5 в 1-м такте будет присутствовать соответственно значение Х| м Хм. На третьих входах блока 5 находится значение текущей оценки, на четвертых - предыдущее значение вспомогательной величины (5 и, находящейся в регистре 6, на пятых - значения оценки Si-2 . находящейся в регистре 8. По имеющимся значениям Xi, Хм. Si1 . (5м, Si-i1 в соответствии с формулами (4-6) и (4-в) блок 5 выдает соответственно на первые и вторые выходы оценки д и 5м1. Оценка 5м , представляющая собой задержанную на такт оценку отсчета входного сигнала, пройдя ЦАП 7, образует выходной сигнал S(t) декодера, а пройдя регистр 8. в следующем такте образует оценку отсчета SM , задержанную на два такта, которая будет использоваться в следующих тактах работы декодера.

Таким образом, можно констатировать точное соблюдение полученных ранее рекуррентных соотношений (4-а) - (4-г), которые позволяют достичь более точного восстановления сигнала за счет более полного учета связей соседних отсчетов сигнала и нелинейной связи этих отсчетов с принимаемым цифровым сигналом.

Следует отметить, что дополнительным достоинством дельта-декодера является отсутствие аналоговых элементов, что делает устройство стабильным и высокотехноло- гичным.

Формула изобретения Дельта-декодер, содержащий триггер, информационный вход которого является

информационным входом дельта-декодера, тактовый вход триггера объединен с тактовым входом первого буферного регистра и является тактовым входом дельта-декодера, выходы первого буферного регистра соединены через блок умножения на постоянный коэффициент с первыми входами сумматора, выходы которого подключены к информационным входам первого буферного регистра, отличающийся тем, что, с

целью повышения точности восстановления сигналов, в дельта-декодер введены второй и третий буферные регистры, цифроанало- говый преобразователь и блок вычисления оценок, первый вход которого обьединен с

вторым входом сумматора и подключен к информационному входу дельта-декодера, выход триггера соединен с вторым входом блока вычисления оценок, третьи входы которого подключены к выходам сумматора,

первые выходы блока вычисления оценок соединены с информационными входами второго буферного регистра, тактовый вход, которого обьединен с тактовым входом третьего буферного регистра и подключен к

тактовому входу дельта-декодера, выходы второго и третьего буферных регистров соединены соответственно с четвертыми и пятыми входами блока вычисления оценок, вторые выходы которого подключены к информационным входам третьего буферного регистра и входам цифроаналогового преобразователя, выход которого является выходом дельта-декодера.

Авторы

Даты

1991-06-23—Публикация

1988-04-15—Подача