ю vj

сд

VI

ю

11

Изобретение относится к вычислительной технике и технике связи и может быть использовано в системах передачи информации.

Цель изобретения - повышение достоверности передаваемой информации..

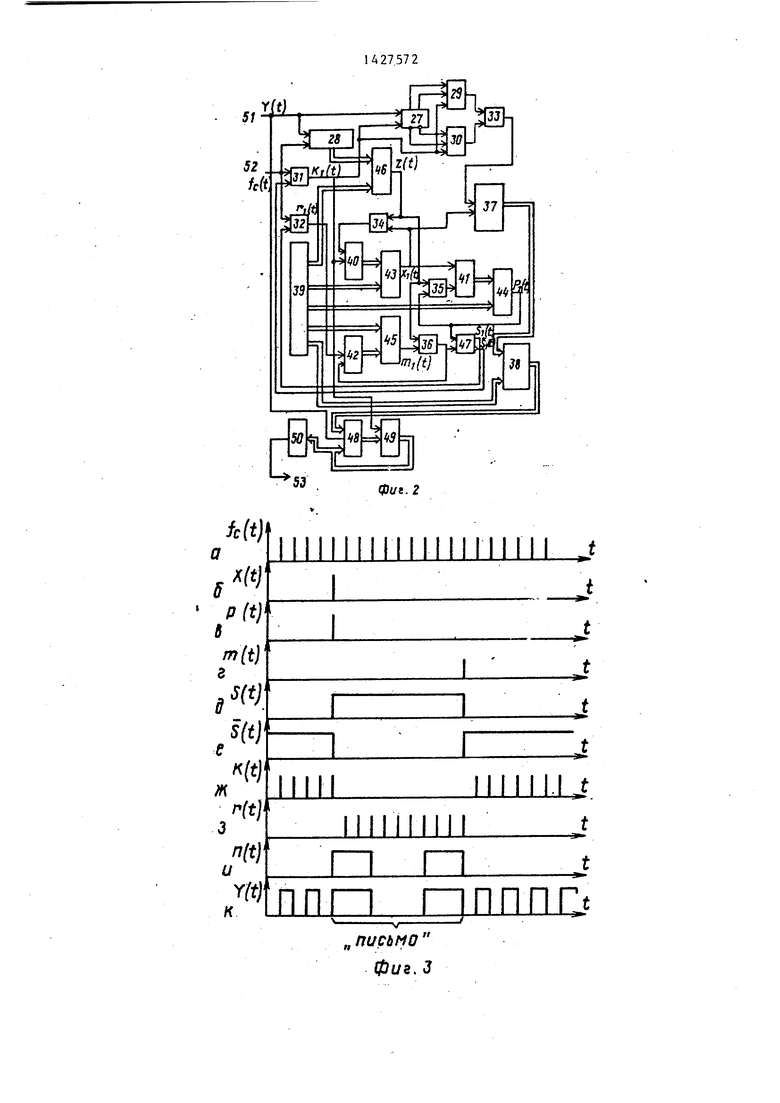

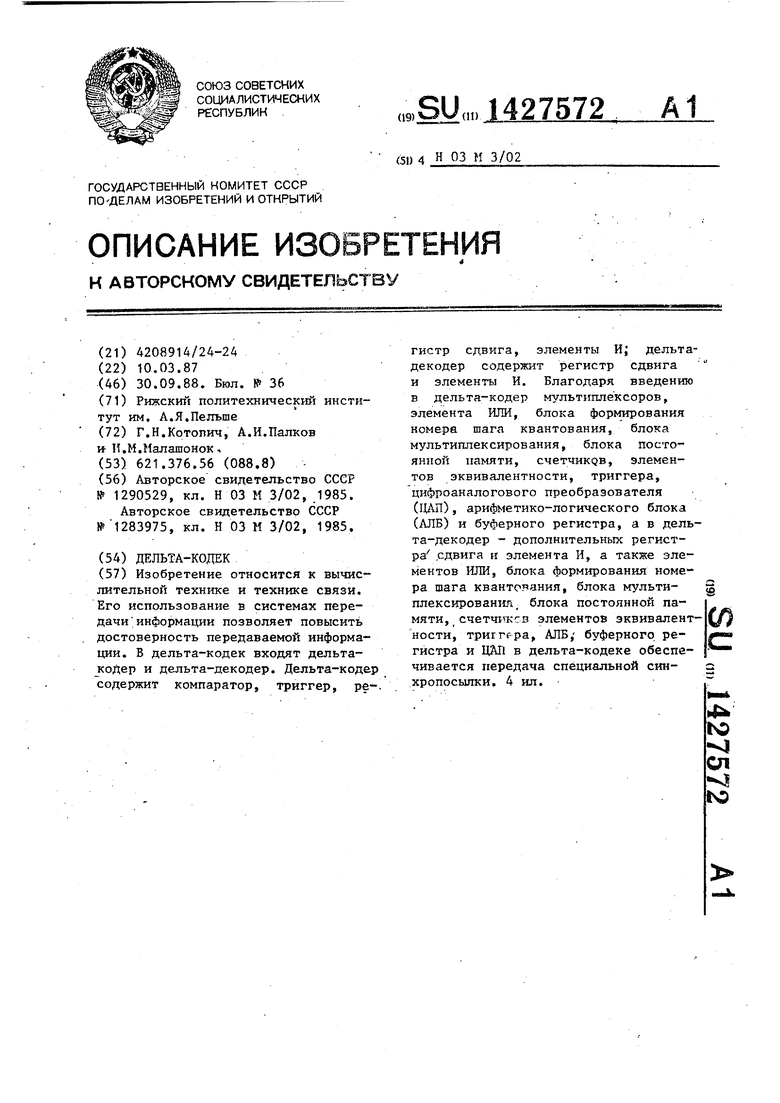

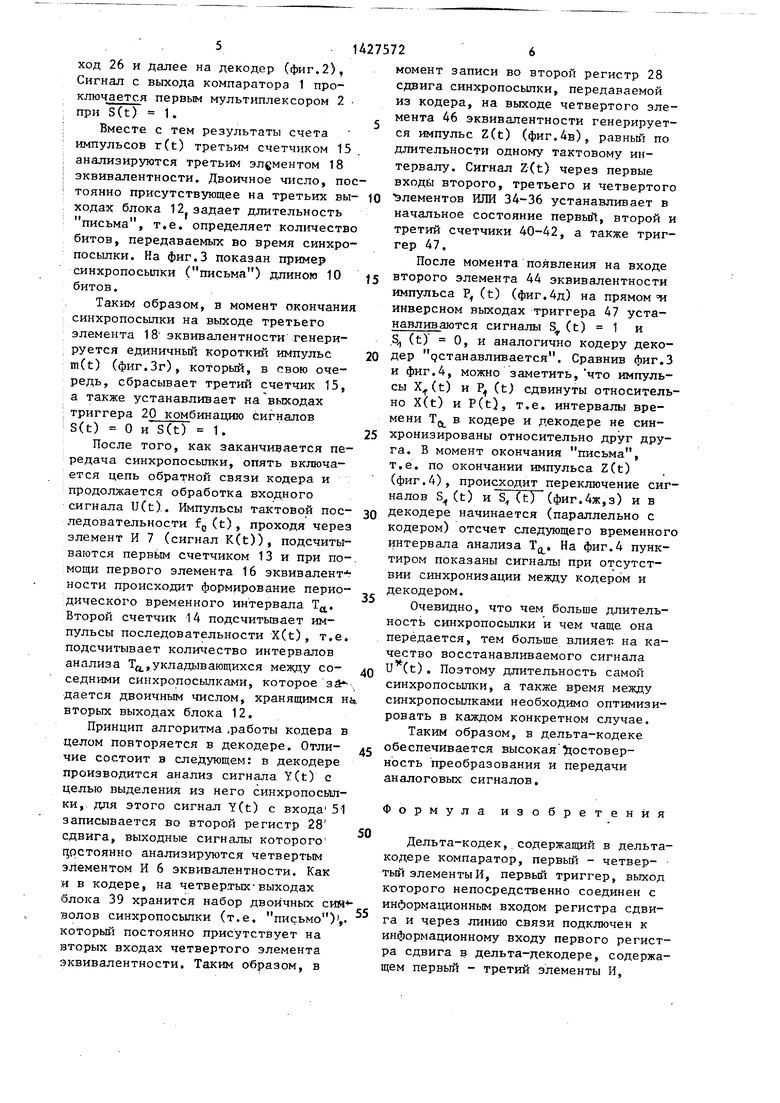

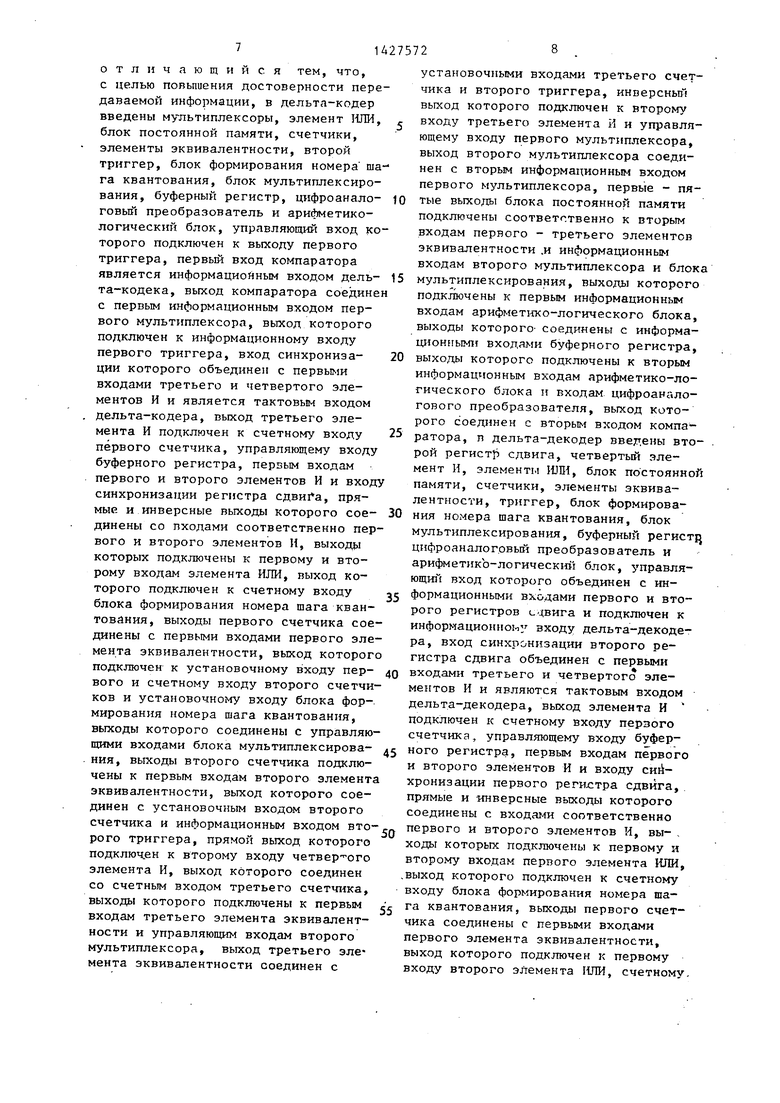

На фиг.i и 2 изображрны функциональные схемы соответственно дельта- кодера и дельта-декодера; на фиг.З и 4 - временные диаграммы их работы.

Дельта-кодек состоит из дельта-кодера и дельта-декодера, соединенных через линию связи.

рого подключены к входам дешифраторов минимальной и максимальной величин и являются выходами блока, выходы дешифраторов максимальной и минимальной величин соединены с третьими входами соответственно первого и второго элементов И.

На фиг.З приняты следующие обозначения: а - тактовая последовательность импульсов с частотой f (t) на входе 25, б - сигнал X(t) на выходе элемента 16

первого элемента 1Ь эквивалентности, в - сигнал P(t) на выходе второ

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Дельта-кодер | 1986 |

|

SU1381716A1 |

| Дельта-кодер | 1986 |

|

SU1381715A1 |

| Дельта-кодер | 1984 |

|

SU1197088A1 |

| Устройство для измерения шума квантования дельта-кодека | 1987 |

|

SU1450121A1 |

| Дельта-кодер | 1985 |

|

SU1290529A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| Универсальный дельта-кодек | 1982 |

|

SU1078612A1 |

| Кодек системы связи | 1983 |

|

SU1150770A1 |

| Дельта-кодер | 1987 |

|

SU1429321A1 |

Изобретение относится к вычислительной технике и технике связи. Его использование в системах передачи информации позволяет повысить достоверность передаваемой информации. В дельта-кодек входят дельта- кодер и дельта-декодер. Дельта-кодер содержит компаратор, триггер, ре-. гистр сдвига, элементы И; дельта- декодер содержит регистр сдвига и элементы И. Благодаря введению в дельта-кодер мультиплексоров, элемента ИЛИ, блока форьгарования номера шага квантования, блока мультиплексирования, блока постоянной памяти, счетчикрв, элементов эквивалентности, триггера, цифроаналогового преобразователя (lIAn) , арифметико-логического блока (АЛБ) и буферного регистра, а в дельта-декодер - дополнительных регистра .сдвига и элемента И, а также элементов ИЛИ, блока формирования номера шага квантования, блока мультиплексирования, блока постоянной памяти, счетчртксв элементов эквивалентности, триггера, АЛБ, буферного, регистра и ЦАП в дельта-кодеке обеспечивается передача специальной син- хропосылки. 4 ил. € сг

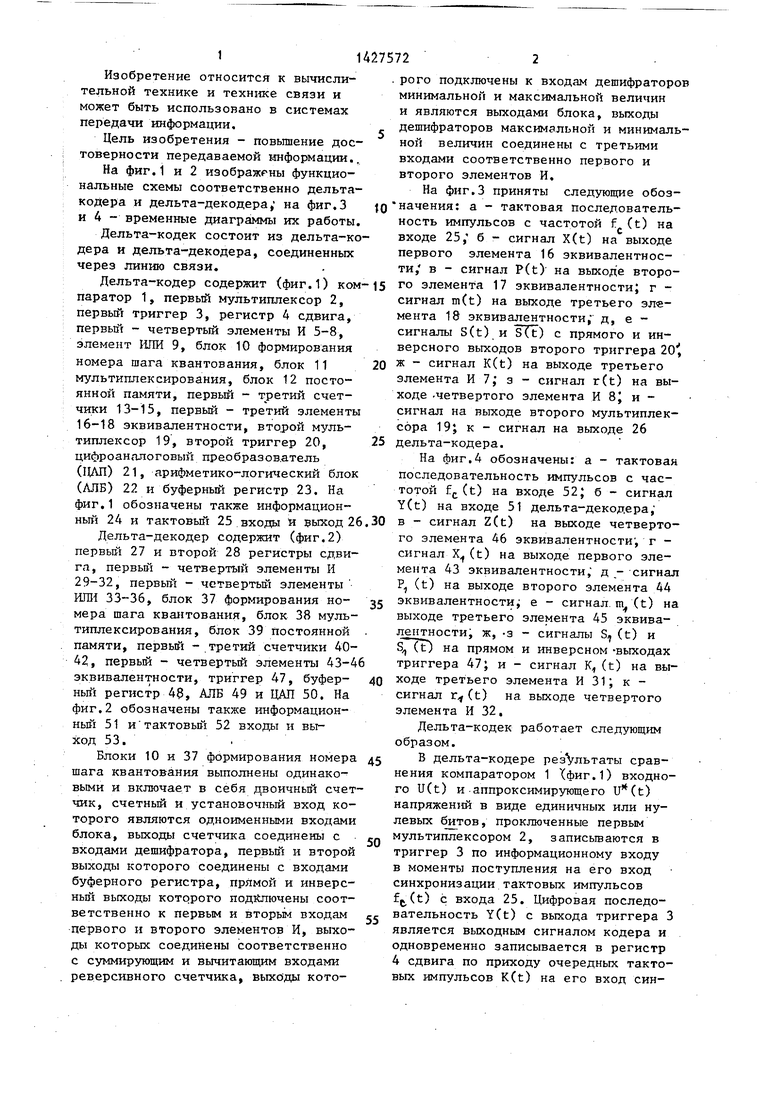

Дельта-кодер содержит (фиг.1) ком-15 го элемента 17 эквивалентности;

паратор 1, первый мультиплексор 2, первый триггер 3, регистр 4 сдвига, nepBbrii - четвертый элементы И 5-8, элемент ИЛИ 9, блок 10 формирования номера шага квантования, блок 11 мультиплексирования, блок 12 постоянной памяти, первый - третий счетчики 13-15, первый - третий элементы 16-18 эквивалентности, второй мультиплексор 19, второй триггер 20, цифроаналоговый преобразователь (ЦЛП) 21, арифметико-логический блок (ЛЛБ) 22 и буферный регистр 23. На фиг.1 обозначены также информационный 24 и тактовьш 25 входы и вькод26

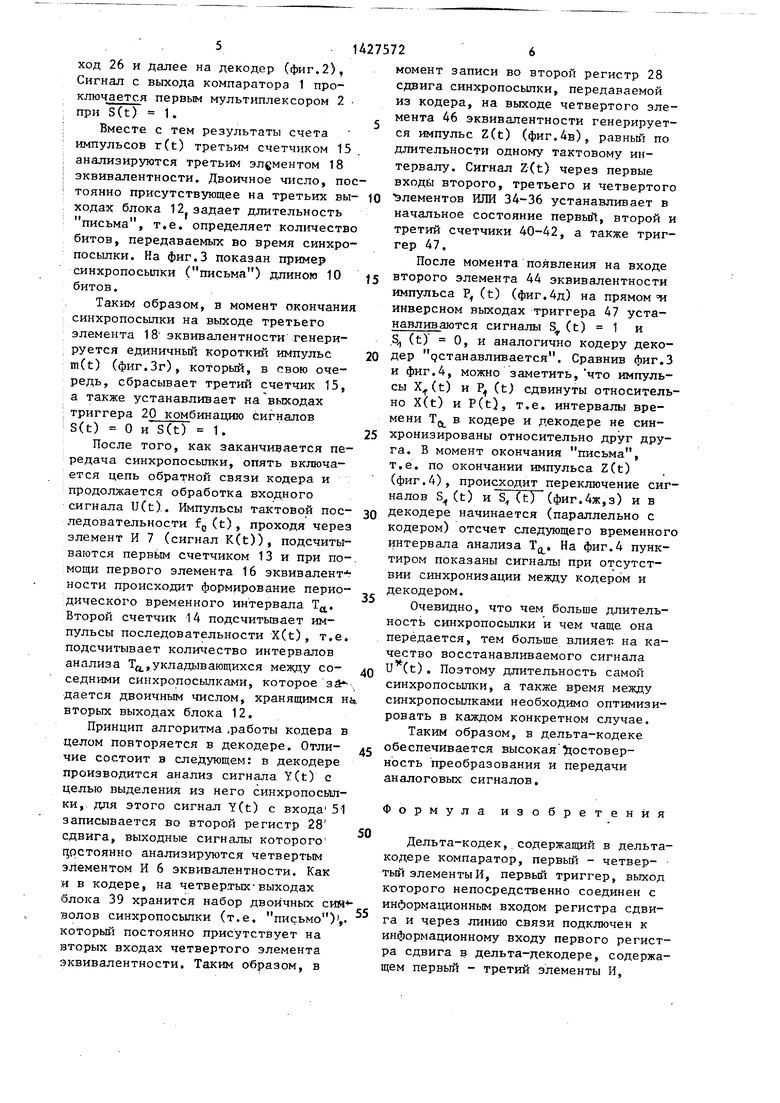

Дельта-декодер содержит (фиг.2) первый 27 и второй 28 регистры сдвига, первьй - четвертый элементы И 29-32, первый - четвертый элементы ИЛИ 33-36, блок 37 формирования но- мера шага квантования, блок 38 мультиплексирования, блок 39 Постоянной памяти, первый - третий счетчики 40- 42, первый - четвертый элементы 43-4 эквивалентности, триггер 47, буфер- ньп1 регистр 43, АЛБ 49 и ЦАП 50. На фиг.2 обозначены также информационный 51 и тактовьп 52 входы и выход 53.

Блоки 10 и 37 формирования номера шага квантования выполнены одинако- выми и включает в себя двоичный счетчик, счетный и установочный вход которого являются одноименными входами блока, выходы счетчика соединены с входами дешифратора, первьп и второй выходы которого соединены с входами буферного регистра, прямой и инверс- ньп вьпсоды которого подключены соответственно к первым и вторьм входам первого и второго элементов И, выходы которых соединены соответственно с суммирзлющим и вычитающим входами реверсивного счетчика, выходы котог сигнал m(t) на выходе третьего элемента 18 эквивалентности; д, е - сигналы S(t) и sTf) с прямого и инверсного выходов второго триггера 20 ж - сигнал K(t) на выходе третьего элемента И 7; з - сигнал r(t) на выходе -четвертого элемента И 8J и - сигнал на выходе второго мультиплексора 19; к - сигнал на выходе 26 дельта-кодера.

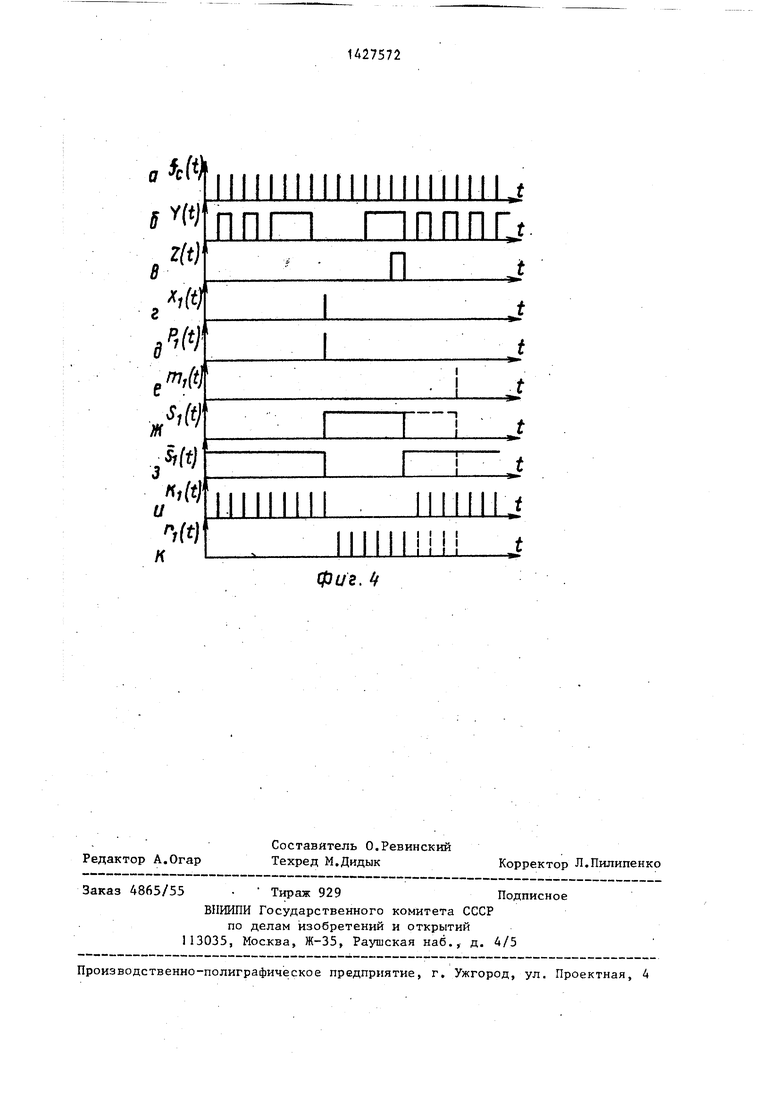

На фиг.4 обозначены: а - тактовая последовательность импульсов с частотой ) на входе 52J б - сигнал Y(t) на входе 51 дельта-декодера; в - сигнал Z(t) на выходе четвертого элемента 46 эквивалентности , г - сигнал Х(t) на выходе первого элемента 43 эквивалентности, д .- сигнал Р, (t) на выходе второго элемента 44

на

эквива- j (t) и

эквивалентности; е - сигнал, т (t)

выходе третьего элемента 45 лептности; ж, -3 - сигналы S S (Т) на прямом и инверсном -выходах триггера 47; и - сигнал К (t) на выходе третьего элемента И 31; к - сигнал г Ct) на выходе четвертого элемента И 32.

Дельта-кодек работает следующим образом.

В дельта-кодере peзVльтaты сравнения компаратором 1 (фиг.1) входного U(t) и аппроксимирующего U (t) напряжений в виде единичных или нулевых битов, проключенные первым мультиплексором 2, записьгоаются в триггер 3 по информационному входу в моменты поступления на его вход синхронизации тактовых импульсов fj(t) с входа 25. Цифровая последовательность Y(t) с выхода триггера 3 является выходным сигналом кодера и одновременно записывается в регистр 4 сдвига по приходу очередных тактовых импульсов K(t) на его вход синхронизации. Продвигаясь по регистру 4 сдвига импульсная последовательность Y(t) анадизируется элементами И 5 и 6 и элементом ИЛИ 9, на выходе которого генерируются короткие единичные импульсы всякий раз, когда в последовательности Y(t) появляются два (и более) одинаковых единичных или нулевых сигнала, следующие подряд. Как и в известном устройстве, длительность единичных импульсов на выходе элемента ИЛИ 9 определяется длительностью тактовых импульсов, что обусловлено заведением сигнала K(t) на третьи входы элементов И 5 и 6.

Последовательность коротких единичных импульсов с выхода,элемента ИЛИ 9 поступают на счетньй вход блока 10 формирования номера шага квантования, где в течение интервала анализа Т( производится обработка данной последовательности имщшь- сов, и по его окончании на выходе (в дбоичном виде) устанавливается номер текущего шага квантования.

Алгоритм формирования номера шага квантования может быть выбран таким же., как в известном устройства, но может быть другим.

Периодический интервал времени TO, определяется числом, хранящимся в двоичном коде в блоке 12 (первые выходы) и формируется при помощи первого счетчика 13 и первого элемента 16 эквивалентности.

Двоичное число, соответствующее номеру текущего шага квантования, поступает на управляющие входы блока 1 мультиплексирования.

Блок 11 проключает один из хранящихся в двоичном виде на пятых выходах блока 12 значений шагов квантования в соответствии с кодом, установившиеся на его управляющих входах,Двоичное число, соответствующее текущему шагу квантования, с выхода блока 11 поступает на первые входы АЛБ 22 и в зависимости от состояния его управляющего входа либо суммируется, либо вычитается из двоичного числа, присутствующего

50 входам второго мультиплексора 16, через который последовательно про- ключается комбинация двоичных символов n(t) (фиг.Зи), поступающих на его информационные входы с четвертых вы- С выхода второго

выхода мультиплексора 19 письмо (сигнал

на вторых входа АЛБ 22. Двоичное

число на вторых входах АЛБ 22 явля:ет- -55 ходов блока 12

ся результатом аналогичной арифмёти

ческой операции (произведенной в n(t)) проключается при помощи первого

дыдущем тактовом интервале), храня- мультиплексора 2 и через информационщимся в буферном регистре 23 в те- ный вход триггера 3 передается на выличину напряжения U(t) входного сигнала

чение одного тактового интервала. На выходе буферного регистра 23 таким образом образуется двоичное число, величина которого определяет веаппроксимации

в цепи обратной связи кодера. Преобразование данного двоичного числа в уровень напря0 жения U(t) производит ЦАП 21.

Импульсы X(t) (фиг.Зб), отмечающие окончание каждого временного интервала Тд, поступают на счетный вход второго счетчика 14. В момент, когда

5 двоичные числа на выходах второго 14 и на вторых выходах блока 12 равны, на выходе второго элемента 17 эквивалентности пояз ляется короткий единичный импульс (фиг.Зв),

0 Этот импульс P(t) сбрасывает по установочному входу второй счетчик 14 и через информационный вход второго триггера 20 устанавливает на его прямом выходе (сигнал S(t).cocтoя5 ние 1, а на инверсном - соотвеч- ственно (сигнал SCtl О (фиг.3д,е).

В момент появления импульса P(t) прекращается поступление импульсов последовательности K(t) на регистр 4

0 сдвига и на элементы И 5 и 6, а также на буферный регистр 23 и на пер- вый счетчик 13, что означает времен нуга остановку работы цепи обратной связи кодера. В то время как кодер

g стоит, при помощи третьего счетчика 15, первого 2 и второго 19 м льти- плексоров 2, 19 на выход 26 кодера (сигнал Y(.t) передается синхропосыл- ка, называемая письмом (фиг.Зк),

0 которая представляет собой набор двоичных символов, хранящихся в параллельном виде на четвертых выходах блока 12. В случае,, когда сигналы S(t) 1

5 и S(t) О, импульсы последовательности f(t), проходя через элеМе 5т И 8, поступает на счетцый вход гре- тьего счетчика 15. Выходы.третьего счетчика 15 подключены к управляющем

0 входам второго мультиплексора 16, через который последовательно про- ключается комбинация двоичных символов n(t) (фиг.Зи), поступающих на его информационные входы с четвертых вы- С выхода второго

выхода мультиплексора 19 письмо (сигнал

5 ходов блока 12

ход 26 и далее на декодер (фиг.2), Сигнал с выхода компаратора 1 про- ключается первым мультиплексором 2 при S(t) 1.

Вместе с тем результаты счета импульсов r(t) третьим счетчиком 15 анализируются третьим элементом 18 эквивалентности. Двоичное число, постоянно присутствующее на третьих вы- ходах блока 12 задает длительность письма, т.е. определяет количество

момент записи во второй регистр 28 сдвига синхропосьшки, передаваемой из кодера, на выходе четвертого эле мента 46 эквивалентности генерирует ся импульс Z(t) (фиг.Дв), равный по длительности одному тактовому интервалу. Сигнал Z(t) через первые входы второго, третьего и четверто Элементов ИЛИ 34-36 устанавливает в начальное состояние первьй, второй третий счетчики 40-42, а также три гер 47.

После момента появления на вход второго элемента 44 эквивалентности импульса Р (t) (фиг.4д) на прямом и инверсном выходах триггера 47 устаиО, и аналогично кодеру деко

15

битов, передаваемых во время синхропосьшки. На фиг.З показан пример синхропосьшки (письма) длиною 10 битов.

Таким образом, в момент окончания синхропосьшки на выходе третьего элемента 18 эквивалентности генерируется единичный короткий импульс 20 m(t) (фиг.Зг), который, в свою очередь, сбрасывает третий счетчик 15, а также устанавливает на выходах триггера 20 комбинацию сигналов S(t) О и S(t) 1.25

После того, как заканчивается передача синхропосьшки, опять включается цепь обратной связи кодера и продолжается обработка входного сигнала U(t).. Импульсы тактовой пос- зо Декодере начинается (параллельно с

навливаются сигналы S (t) 1

s, (t)дер рстанавливается. Сравнив фиг и фиг.4, можно заметить, что импул сы X(t) и Р (t) сдвинуты относител но X(t) и P(t), т.е. интервалы времени Tg в кодере и декодере не синхронизированы относительно друг дру га. В момент окончания письма, т.е. по окончании импульса Z(t) (фиг.4), происходит переключение си налов S (t) и S (t) (фиг.4ж,з) и в

ледовательности f (t) , проходя через элемент И 7 (сигнал K(t)), подсчитываются nepBbiM счетчиком 13 и при по-, мощи первого элемента 16 эквивалент- ности происходит формирование периодического временного интервала Т(. Второй счетчик 14 подсчитьшает импульсы последовательности X(t), т.е. подсчитывает количество интервалов анализа Т,укладывающихся между соседними синхропосьшками, которое зй дается двоичным числом, хранящимся нг вторых выходах блока 12.

Принцип алгоритма .работы кодера в целом повторяется в декодере. Отличие состоит в следующем: в декодере производится анализ сигнала Y(t) с целью выделения из него синхропосьшки, для этого сигнал Y(t) с входа 51 записывается во второй регистр 28 сдвига, выходные сигналы которого гуэстоянно анализируются четвертым элементом И 6 эквивалентности. Как и в кодере, на четвертых-выходах блока 39 хранится набор двоичных сия

35

40

45

50

кодером) отсчет следующего временно интервала анализа Т. На фиг. 4 пунк тиром показаны сигналы при отсутствии синхронизации между кодером и декодером.

Очевидно, что чем больше длитель ность синхропосьшки и чем чаще она передается, тем больще влияет- на к чество восстанавливаемого сигнала u (t) . Поэтому длительность самой синхропосьшки, а также время между синхропосьшками необходимо оптимизи ровать в каждом конкретном случае.

Таким образом, в дельта-кодеке обеспечивается высокая остовер- ность преобразования и передачи аналоговых сигналов.

Формула изобретени

Дельта-кодек,.содержащий в дель кодере компаратор, первый - четвер тый элементы И, первый триггер, выхо которого непосредственно соединен информационным входом регистра сдв

волов синхропосьшки (т.е. письмо),. га и через линию связи подключен к

который постоянно присутствует на вторых входах четвертого элемента эквивалентности. Таким образом, в

с

ю

275726

момент записи во второй регистр 28 сдвига синхропосьшки, передаваемой из кодера, на выходе четвертого элемента 46 эквивалентности генерируется импульс Z(t) (фиг.Дв), равный по длительности одному тактовому интервалу. Сигнал Z(t) через первые входы второго, третьего и четвертого Элементов ИЛИ 34-36 устанавливает в начальное состояние первьй, второй и третий счетчики 40-42, а также триггер 47.

После момента появления на входе второго элемента 44 эквивалентности импульса Р (t) (фиг.4д) на прямом и инверсном выходах триггера 47 устаиО, и аналогично кодеру деко15

20 25

зо Декодере начинается (параллельно с

навливаются сигналы S (t) 1

s, (t)дер рстанавливается. Сравнив фиг.З и фиг.4, можно заметить, что импульсы X(t) и Р (t) сдвинуты относительно X(t) и P(t), т.е. интервалы времени Tg в кодере и декодере не синхронизированы относительно друг друга. В момент окончания письма, т.е. по окончании импульса Z(t) (фиг.4), происходит переключение сигналов S (t) и S (t) (фиг.4ж,з) и в

Декодере начинается (параллельно с

кодером) отсчет следующего временного интервала анализа Т. На фиг. 4 пунктиром показаны сигналы при отсутствии синхронизации между кодером и декодером.

Очевидно, что чем больше длительность синхропосьшки и чем чаще она передается, тем больще влияет- на качество восстанавливаемого сигнала u (t) . Поэтому длительность самой синхропосьшки, а также время между синхропосьшками необходимо оптимизировать в каждом конкретном случае.

Таким образом, в дельта-кодеке обеспечивается высокая остовер- ность преобразования и передачи аналоговых сигналов.

Формула изобретения

Дельта-кодек,.содержащий в дельта- кодере компаратор, первый - четвертый элементы И, первый триггер, выход которого непосредственно соединен с информационным входом регистра сдвиинформационному входу первого регистра сдвига в дельта-декодере, содержащем первый - третий элементы И,

о т л и ч а ю щ и и с. я тем, что, с целью повьпиения достоверности передаваемой информации, в дельта-кодер введены мультиплексоры, элемент ИЛИ, блок постоянной памяти, счетчики, элементы эквивалентности, второй триггер, блок формирования номера шага квантования, блок мультиплексирования, буферный регистр, цифроанало- говый преобразователь и арифметико- логический блок, управляющий вход которого подключен к выходу первого триггера, первый вход компаратора является информационным входом дель- та-кодека, выход компаратора соединен с первым информационным входом первого мультиплексора, выход которого подключен к информационному входу первого триггера, вход синхрониэа- ции которого объединен с первыми входами третьего и четвертого элементов И и является тактовым входом дельта-кодера, выход третьего элемента И подключен к счетному входу первого счетчика, управляющему входу буферного регистра, первым входам первого и второго элементов И и входу синхронизации регистра сдви1 а, прямые и инверсные выходы которого сое- динены со входами соответственно первого и второго элементов Н, выходу которых подключены к первому и второму входам элемента ИЛИ, выход которого подключен к счетному входу блока формирования номера шага квантования, выходы первого счетчика соединены с первыми входами первого элемента эквивалентности, выход которого подключен к установочному входу пер- вого и счетному входу второго счетчиков и установочному входу блока фор-, мирования номера шага квантования, выходы которого соединены с управляющими входами блока мультиплексирова- НИН, выходы второго счетчика подключены к первым входам второго элемента эквивалентности, выход которого соединен с установочным входом второго счетчика и информационньЕМ входом вто- рого триггера, прямой выход которого подключ.ен к второму входу четвер- ого элемента И, выход которого соединен со счетным входом третьего счетчика, выходы которого подключены к первым входам третьего элемента эквивалентности и управляющим входам второго мультиплексора, выход третьего элемента эквивалентности соединен с

установочными входами третьего счетчика и второго триггера, инверсньш выход которого подключен к второму входу третьего элемента И и управляющему входу первого мультиплексора, выход второго мультиплексора соединен с вторым информационнь м входом первого мультиплексора, первые - пятые выходы блока постоянной памяти подключены соответственно к вторым входам первого - третьего элементов эквивалентности .и информационным входам второго мультиплексора и блок мультиплексирования, выходы которого подключены к первым информационным входам арифметико-логического блока, выходы которого- соединены с информационными входами буферного регистра, выходы которого подключены к вторым информационным входам арифметико-логического блока и входам цифроанало- гового преобразователя, выход которого соединен с вторым входом компаратора, п дельта-декодер введены второй регистр сдвига, четвертый элемент И, элементы ШШ, блок постоянно памяти, счетчики, элементы эквивалентности, триггер, блок формирования номера щага квантования, блок мультиплексирования, буферный регист цифроаналогрвый преобразователь и арифметикЬ-логическш блок, управляющий вход которого объединен с информационными входами первого и второго регистров и подключен к информационному входу дельта-декодера, вход синхронизации второго регистра сдвига объединен с первыми входами третьего и четвертого элементов И и являются тактовым входом дельта-декодера, выход элемента И подключен к счетному входу первого счетчика, управляющему входу буферного регистра, первым входам первого и второго элементов И и входу сии- хронизации первого регих:тра сдвига, прямые и -инверсные вьтходы которого соединены с входами соответственно первого и второго элементов И, вы- , ходы которых подключены к первому и второму входам первого элемента liJlH, .выход которого подключен к счетному входу блока формирования номера шага квантования, выходы первого счетчика соединены с первыми входами первого элемента эквивалентности, выход которого подключен к первому входу второго элемента ИЛИ, счетному

входу второго счетчика и установочному входу блока формирования номера шага квантования, выходы которого соединены с управляющими входами блока мультиплексирования, выходы второ- iro счетчика подключены к первым вхо- |дам второго элемента эквивалентности, выход которого соединен с первым вхо- ;дом третьего элемента ИЛИ и информа- ционным входом триггера, прямой выход которого подключен к второму входу четвертого элемента И, выход которого соединен со счетным входом третьего счетчика, выходы которого подключены к первым входам третьего элемента эквивалентности, выход которого соединен с первым входом четвертого элемента ИЛИ, выход которого подключен к установочным входам тре- :тьего счетчика и второго счетчика, инверсный выход которого соединен с ;вторым входом третьего элемента И, выходы второго регистра сдвига под

25

ключены к первым входам четвертого элемента эквивалентности, выход которого соединен с вторыми входами второго - четвертого элементов ИЛИ, выходы второго и третьего элементов ИЛИ подключены к установочным входам соответственно первого и второго счетчиков, первые - пятые выходы

блока постоянной памяти подключены соответственно к вторым входам первого - четвертого элементов эквивалентности и информационным входам блока мультиплексирования, выходы

которого подключены к первым информационным входам арифметико-логического блока, выходы которого соединены с информационными входами буферного регистра, выходы которого подключены к вторым информационным входам арифметико-логического блока и входа: цифроаналогового преобразователя, выход которого является выходом дельта-кодека.

t)

QOt/e. 2

письмо

Фи9. 3

а С

д

)

. , r(t/

P,(tf е

/

,w| llt}

и

фиг. //

Авторы

Даты

1988-09-30—Публикация

1987-03-10—Подача