вивалентности 21, три элемента совпадения 22, 24, 27, инвертор 23, реверсивный счетчик 25, кодопреобразователь 26, сумматор 28, АЛБ 29, буферный регистр 30, ЦАП 31, фильтр нижних, частот 32. Для обеспечения цели на передающей стороне введены дешифратор макс, состояния счетчика

(ДМСС) 16, дешифратор нулевого состояния-счетчика (ДНСС) 17, второй блок эквивалентности 18 и четвертьй элемент совпадения 19, а на приемной стороне введены ДМСС 33, ДНСС 34, блок эквивалентности 35, два элемента совпадения 36, 38 и компаратор 37, 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Дельта-кодек | 1987 |

|

SU1427572A1 |

| Дельта-кодер | 1984 |

|

SU1197088A1 |

| Дельта-кодер | 1986 |

|

SU1381716A1 |

| Дельта-кодер | 1987 |

|

SU1429321A1 |

| Дельта-кодер | 1985 |

|

SU1290529A1 |

| Дельта-кодер | 1986 |

|

SU1381715A1 |

| Дельта-кодер | 1987 |

|

SU1441482A1 |

| Дельта-кодер | 1988 |

|

SU1646056A1 |

| Устройство конференц-связи | 1979 |

|

SU886311A1 |

Изобретение относится к электросвязи и предназначено для высококачественного преобразования аналоговых сигналов в цифровой вид дпя последующей передачи цифрового потока по линии связи и обратного преобразова1 ия в аналоговую форму. Целью изобретения является повышение помехозащищенности путем устранения ошибок аппроксимации, отношения С/Ш восстанавливаемого сигнала. Устр-во состоит из передающей части I (кодера), приемной части 2 (декодера) и соединяющего их канала связи 3. .Кодер 1 содержит компаратор 4, регистр 5, блок эквивалентности 6, три элемента совпадения 7, 9, 12, инвертор 8, реверсив- ньй счетчик 10, кодопреобразователь 11, арифметико-логический блок (АЛЕ) 13, буферный регистр 14, ЦАП 15. Декодер 2 содержит регистр 20, блок экi (Л 00 О5 ел со О5 4

1

Изобретение относится к электросвязи и предназначено для высококачественного преобразования аналоговых сигналов в цифровой вид для последующей передачи цифрового потока по линии связи и обратного преобразования в аналоговую форму.

Целью изобретения является повышение помехозащищенности путем устранения ошибок аппроксимации, отношения сигнал/шум восстанавливаемого сигнала.

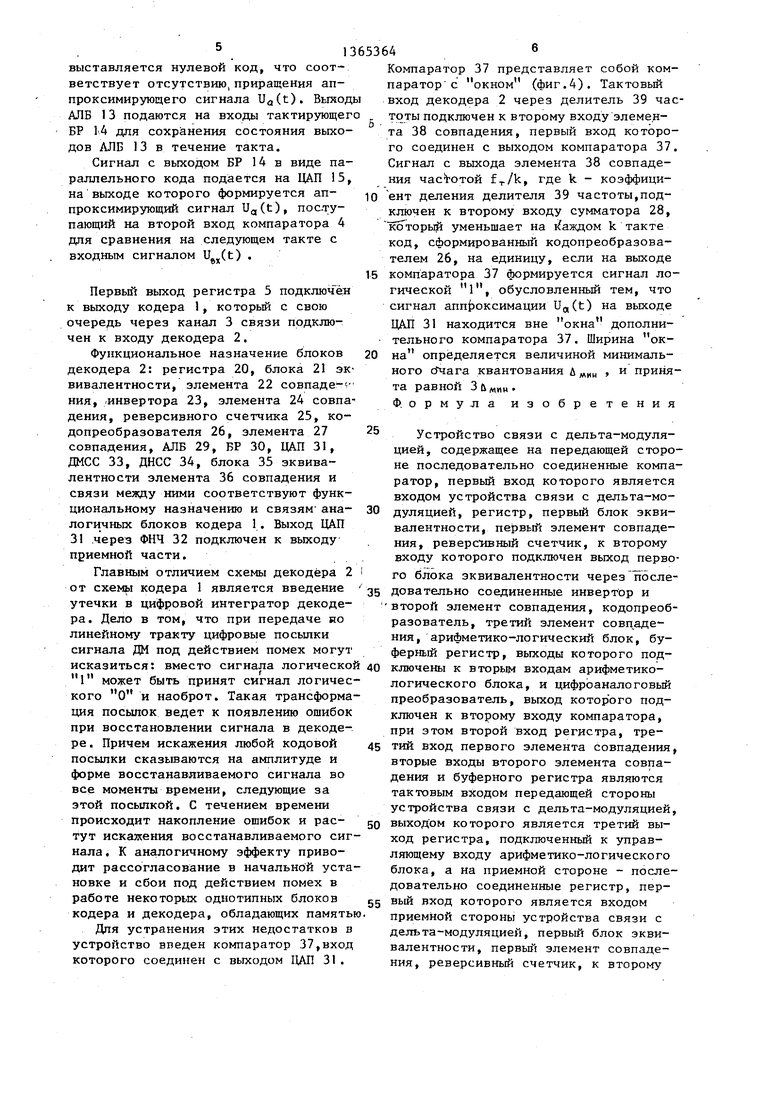

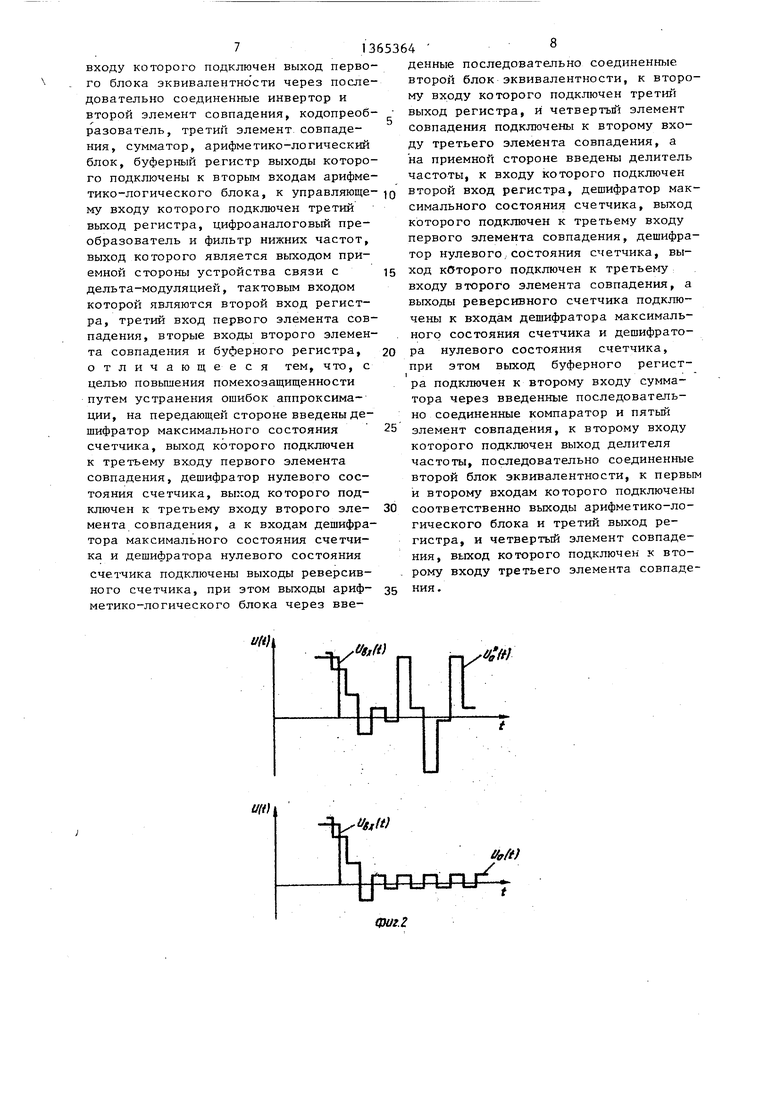

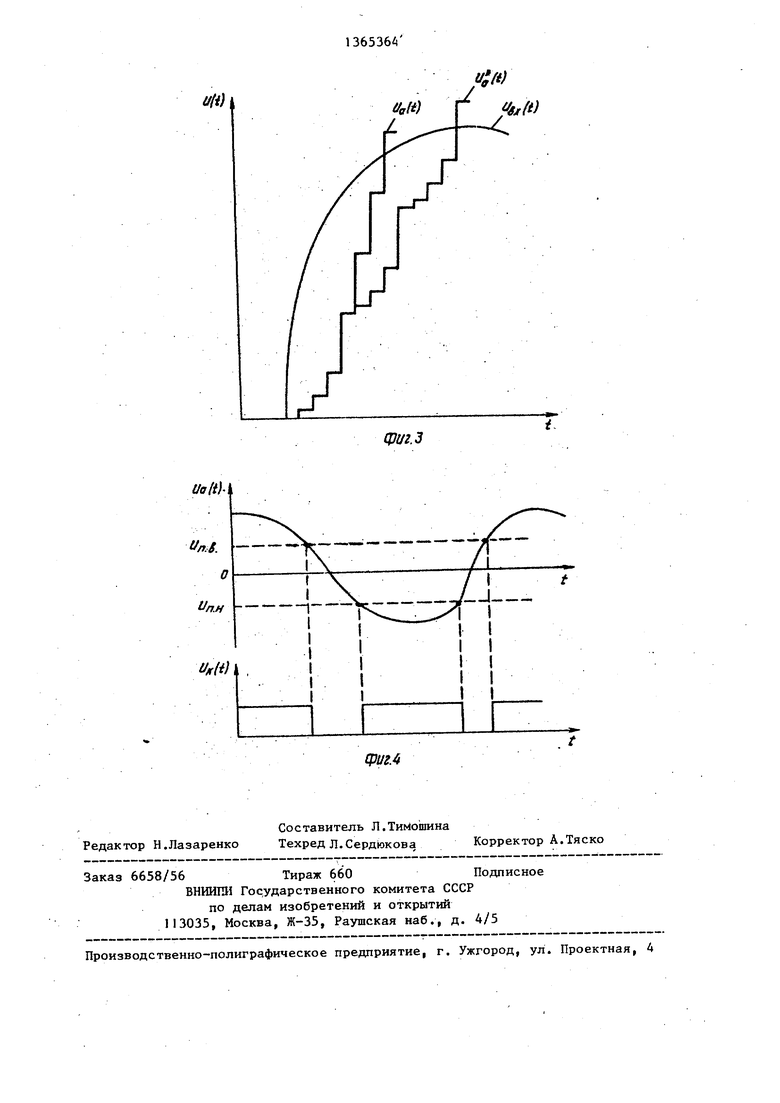

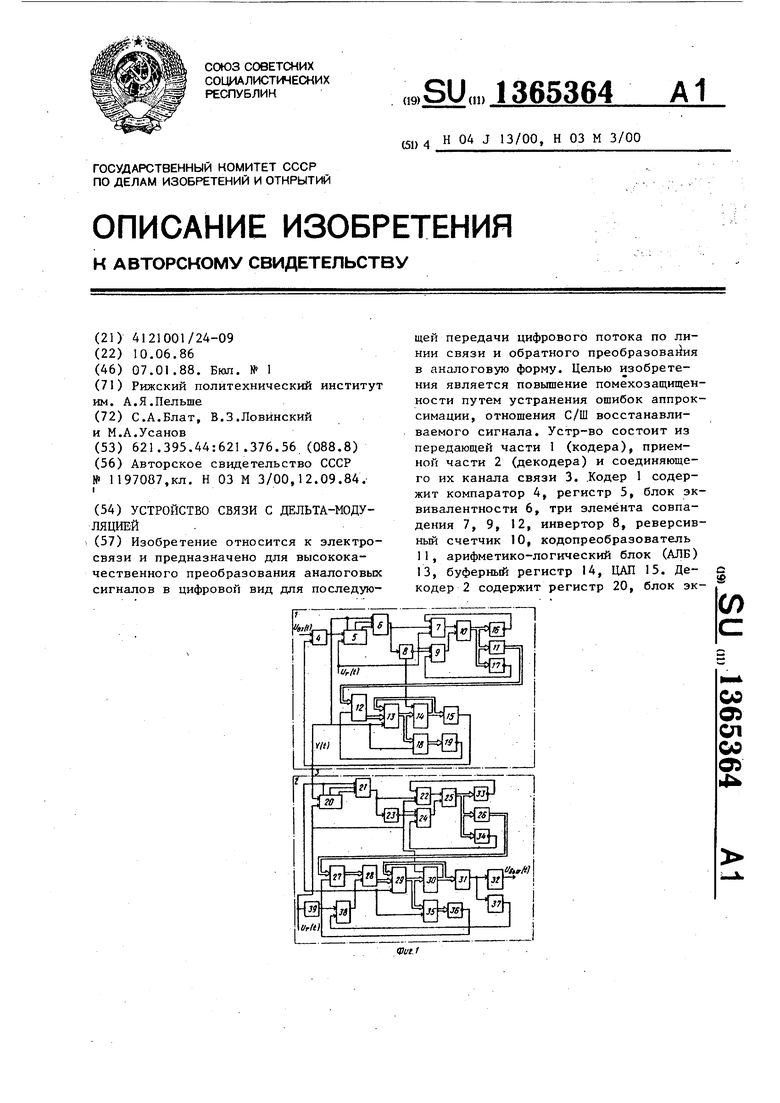

На фиг.1 приведена блок-схема устройства связи с дельта-модуляцией; на фиг.2 - 4 - временные диаграммы, поясняющие принцип работы устройства.

Устройство связи с дельта-модуляцией состоит из передающей час ти 1 (кодера), приемной части 2 (декодера) и соединяющего,их канала 3 связи. Кодер 1 содержит компаратор 4, регистр 5, первый блок 6 эквивалентности, первый элемент 7 совпадения, инвертор 8, второй элемент 9 совпадения, реверсивный счетчик 10, кодопреобразователь 11, третий элемент 12 совпадения, арифметико-логический блок (АЛБ) 13, буферньй регистр (БР) 14, цифроаналоговый преобразователь (ЦАП) 15, дешифратор 16 максимального состояния счетчика (ДМСС), дешифратор 17 нулевого состояния счетчика (ДНСС), второй блок 18 эквивалентности, четвертый элемент 19 совпадения.

Декодер 2 содержит регистр 20, первый блок 21 эквивалентности, первый элемент 22 совпадения, инвертор 23, второй элемент 24 совпадения, реверсивный счетчик 25, кодопреобразователь 26, третий элемент 27 совпадения, сумматор 28, АЛБ 29, БР 30, ЦДЛ

31, фильтр нижних частот (ФНЧ) 32, ДМСС 33, ДНСС 34, второй блок 35 эквивалентности, четвертый элемент 36

совпадения, компаратор 37, пятьш элемент 38 совпадения и делитель 39 частоты.

Предлагаемое устройство работает следующим образом.

Аналоговый сигнал Uj)t(t) поступает на первый вход компаратора 4 и сравнивается с аппроксимирующим сигналом Ua(t), поступающим на второй вход компаратора 4 с выхода ЦАП 15 в peзультате обработки входного сигнала на предыдущем тракте. Сигнал с выхода компаратора 4 поступает на вход регистра 5,на первом выходе которого формируется выходная дельта-модулированная (ДМ), импульсная последовательность y(t). Продвигаясь далее по регистру 5, три последних бита импульсной последовательности y(t) подаются на блок эквивалентности 6, ,на

выходе которого появляется единица свякий раз, когда в импульсной последовательности y(t) присутствует трехэлементная пачка единичных либо нулевых символов. Если же пачка отсутствует, то на выходе блока 6 эквивалентности присутствует нуль.

Сигнал с выхода блока 6 эквивалентности через элемент 7 совпадения в прямом виде подается на вход прямого счета реверсивного счетчика 10, а в инверсном виде через инвертор 8 и элемент 9 совпадения - на вход обратного счета реверсивного счетчика 10. На вторые входы элементов 7 и 9 совпадения подается тактовая последовательность U(t), в результате чего длинные (телеграфные) импульсы, поступающие на первые входы этих схем.

преобразуются в короткие импульсы-на их выходах. Таким образом, при появлении пачек единичных либо нулевых символов в импульсной последовательности y(t) на вход прямого счета реверсивного счетчика 10 подаются короткие импульсы, число которых зависит от количества трех элементных пачек символов, увеличивающие состояние счетчика от нулевого до максимального. Причем, комбинация четырех одинаковых символов, например 1111, расценивается как две пачки. Как только в последовательности y(t) появляются различные импульсы, коротки импульсы поступают на вход обратного счета реверсивного счетчика; 10 и

Цифровой код с выхода реверсивного

уменьшают его состояние.

Код на выходе реверсивного счетчи-2о счетчика 10 подается на вход кодопре- ка 10 определяет необходимую величину рбразователя 11, с выхода которого шага квантования. Следовательно, при

через элемент 12 совпадения на первые входы АЛБ 13 подается в цифровом виде информация о величине шага квантова- 25 ния в соответствии с заложенным в структуре кодопреобразователя 11 законом компандирования, При наличии в цифровой последовательности y(t) сигнала логического О АЛБ 13 уменьшаотсутствии пачек в последовательности y(t) величина шага квантования, уменьшается до минимально возможной. Однако вследствие циклического перехода реверсивного счетчика 10 из минимального состояния в максимальное возникают значительные шумы свободно-

35

40

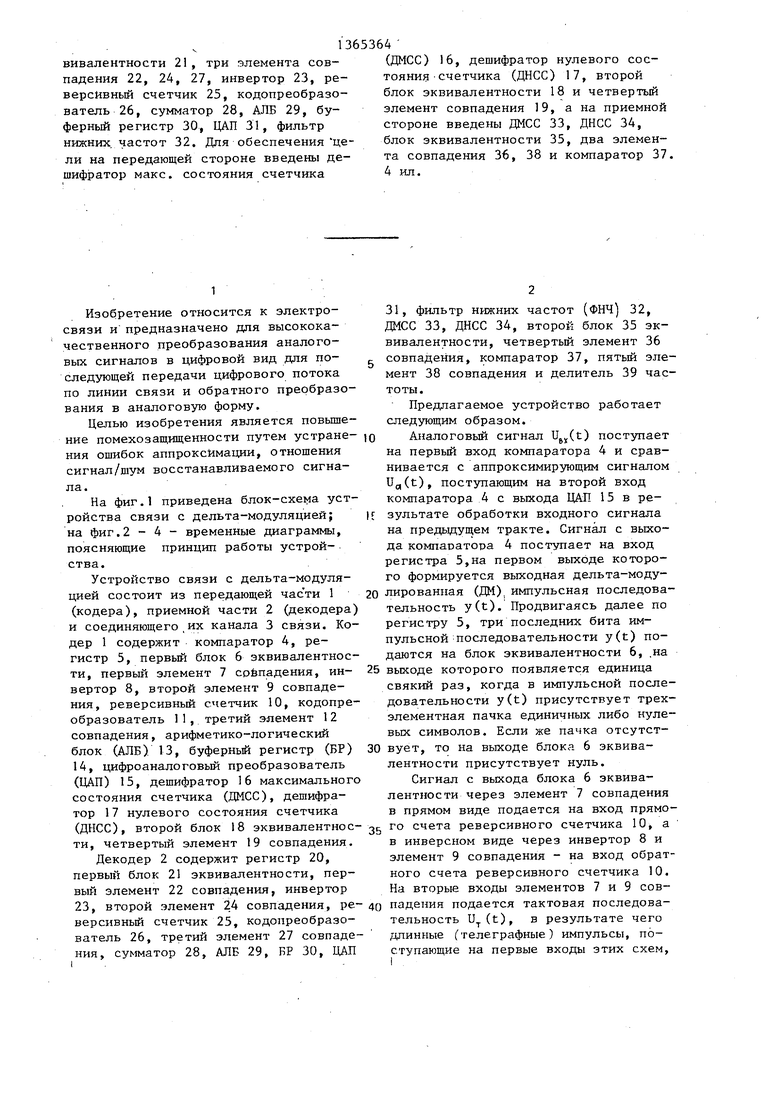

го канала. Описанная ситуация поясня- зо ет цифровой код, выставленный на преется диаграммой на фиг. 2, где ) входной сигнал дельта-кодера; U(t) сигнал аппроксимации в предлагаемом .устройстве; U(t) - сигнал аппроксимации в известном устройстве; U.(t) - сигнал на выходе дополнительного компаратора; и„ - верхнее пороговое напряжение дополнительного компаратора; Un.M - нижнее пороговое напряжение дополнительного компаратора.

Дпя устранения шумов свободного канала введен ДНСС 17, который подключен к выходу реверсивного счетчика 10. При наличии на выходе реверсивного счетчика 10 кода, соответствую- 45 щего его нулевому состоянию: ДНСС 17 выставляет сигнал запрета на третий вход элемента 9 совпадения, в результате чего подача коротких импульсов на вход обратного счета реверсивного счетчика 10 прекращается и циклический переход в максимальное состояние становится невозможным.

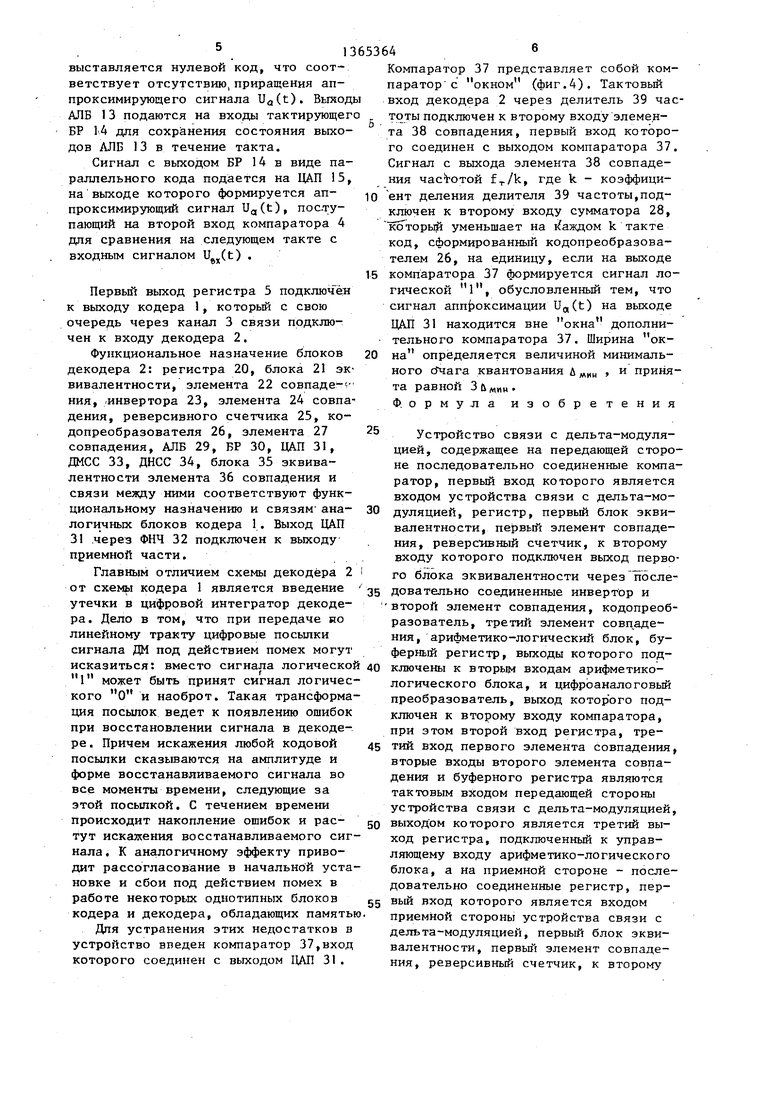

При наличии в импульсной последо-. - вательности y(t) пачек большой длины, gg вход, может возникнуть циклический переход реверсивного счетчика 10 из максимального состояния в нулевое при его переполнении, что приводит к появлению

50

дьщущем такте на величину, задаваемую кодопреобразователем 1, а при наличии в цифровой последовательности

y(t) сигнала логической 1 - увеличивает на ту же величину. Для этого на управляющий вход АЛБ 13 подается цифровая последовательность y(t) с первого выхода регистра 5. На вторые входы АЛБ 13 с выходов буферного регистра 14 подается цифровой код, со- соответствующий величине напряжения аппроксимации на предыдущем такте. Дпя защиты от ошибок аппроксимации на границах динамического диапазона, возникающих в АЛБ 13, входы m старших разрядов из общего числа выходов п АЛБ 13 заведены на блок эквивалентности 18, где . Число разрядов п - m зависит от величины максимального шага квантования, формируемого кодопреобразователем 11. Каждый и m разрядов блока эквивалентности 18 сравнивается с битом последовательности y(t), поступающей на ее второй

и в случае их эквивалентности через элемент 19 совпадения на второй вход элемента 12 совпадения поступает сигнал логического О. В результате этого на первые входы АЛБ 13

шумов, вызванных перегрузкой по крутизне, в выходном сигнале. Описанная ситуация поясняется диаграммой на

фиг.З. Для борьбы с описанными шумами и расширения динамического диапазона дельта-кодека к выходу реверсивного счетчика 10 подключен ДМСС 16, которьп при появлении на выходе реверсивного счетчика 10 кода, соответствующего его максимальному состоянию, на третий вход элемента совпадения 7 выставляет сигнал запрета, в результате чего, подача коротких импульсов на вход прямого счета реверсивного счетчика 10 прекращается и циклический переход в нулевое состояние становится невозможным.

Цифровой код с выхода реверсивного

счетчика 10 подается на вход кодопре- рбразователя 11, с выхода которого

через элемент 12 совпадения на первые входы АЛБ 13 подается в цифровом виде информация о величине шага квантова- ния в соответствии с заложенным в структуре кодопреобразователя 11 законом компандирования, При наличии в цифровой последовательности y(t) сигнала логического О АЛБ 13 уменьша5

0

5

g вход,

0

дьщущем такте на величину, задаваемую кодопреобразователем 1, а при наличии в цифровой последовательности

y(t) сигнала логической 1 - увеличивает на ту же величину. Для этого на управляющий вход АЛБ 13 подается цифровая последовательность y(t) с первого выхода регистра 5. На вторые входы АЛБ 13 с выходов буферного регистра 14 подается цифровой код, со- соответствующий величине напряжения аппроксимации на предыдущем такте. Дпя защиты от ошибок аппроксимации на границах динамического диапазона, возникающих в АЛБ 13, входы m старших разрядов из общего числа выходов п АЛБ 13 заведены на блок эквивалентности 18, где . Число разрядов п - m зависит от величины максимального шага квантования, формируемого кодопреобразователем 11. Каждый и m разрядов блока эквивалентности 18 сравнивается с битом последовательности y(t), поступающей на ее второй

и в случае их эквивалентности через элемент 19 совпадения на второй вход элемента 12 совпадения поступает сигнал логического О. В резульвход,

тате этого на первые входы АЛБ 13

выставляется нулевой код, что соответствует отсутствию, приращения аппроксимирующего сигнала Ua(t). Выход АЛБ 13 подаются на входы тактирующег БР 1 Л для сохранения состояния выходов АЛБ 13 в течение такта.

Сигнал с выходом БР 14 в виде параллельного кода подается на ЦАП 15, на выходе которого формируется аппроксимирующий сигнал Ug (t) , пос.ту- пающий на второй вход компаратора 4 дня сравнения на следующем такте с входным сигналом U(t) .

Первьй выход регистра 5 подключён к выходу кодера 1, который с свою очередь через канал 3 связи подключен к входу декодера 2.

Функциональное назначение блоков декодера 2: регистра 20, блока 21 эквивалентности, элемента 22 совпаде- - ния, .инвертора 23, элемента 24 совпа дения, реверсивного счетчика 25, кодопреобразователя 26, элемента 27 совпадения, АЛБ 29, БР 30, ЦАП 31, даСС 33, ДНСС 34, блока 35 эквивалентности элемента 36 совпадения и связи между ними соответствуют функциональному назначению и связям аналогичных блоков кодера 1. Выход ЦАП 31 .через ФНЧ 32 подключен к выходу приемной части.

Главным отличием схемы декодера 2 от схемь кодера 1 является введение утечки в цифровой интегратор декодера. Дело в том, что при передаче но линейному тракту цифровые посылки сигнала ДМ под действием помех могут

Устройство связи с дельта-модуляцией, содержащее на передающей стороне последовательно соединенные компаратор, первый вход которого является входом устройства связи с дельта-модуляцией, регистр, первый блок эквивалентности, первый элемент совпадения, реверс ивный счетчик, к второму входу которого подключен выход первого блока эквивалентности через Ттосле довательно соединенные инвертор и второй элемент совпадения, кодопреобразователь, третий элемент совп,аде- ния, арифметико-логический блок, буферный регистр, выходы которого подисказиться: вместо сигнала логической 40 ключены к вторым входам арифметико- ..«„-,, и.,, ... „.,„,.„„ „«..„„ логического блока, и цифроаналоговый

преобразователь, выход которого подключен к второму входу компаратора, при этом второй вход регистра, тре45 тий вход первого элемента совпадения, вторые входы второго элемента совпадения и буферного регистра являются тактовым входом передающей стороны устройства связи с дельта-модуляцией,

50 выходом которого является третий выход регистра, подключенный к управляющему входу арифметико-логического блока, а на приемной стороне - последовательно соединенные регистр, пер55 вый вход которого является входом приемной стороны устройства связи с дельта-модуляцией, первый блок эквивалентности, первьп элемент совпадения, реверсивный счетчик, к второму

может быть принят сигнал логического о и наоброт. Такая трансформация посылок ведет к появлению ошибок при восстановлении сигнала в декодере. Причем искажения любой кодовой посылки сказываются на амплитуде и форме восстанавливаемого сигнала во все моменты времени, следующие за этой посьшкой. С течением времени происходит накопление ошибок и растут искажения восстанавливаемого сигнала . К аналогичному эффекту приводит рассогласование в начальной установке и сбои под действием помех в работе некоторых однотипных блоков кодера и декодера, обладающих памятью.

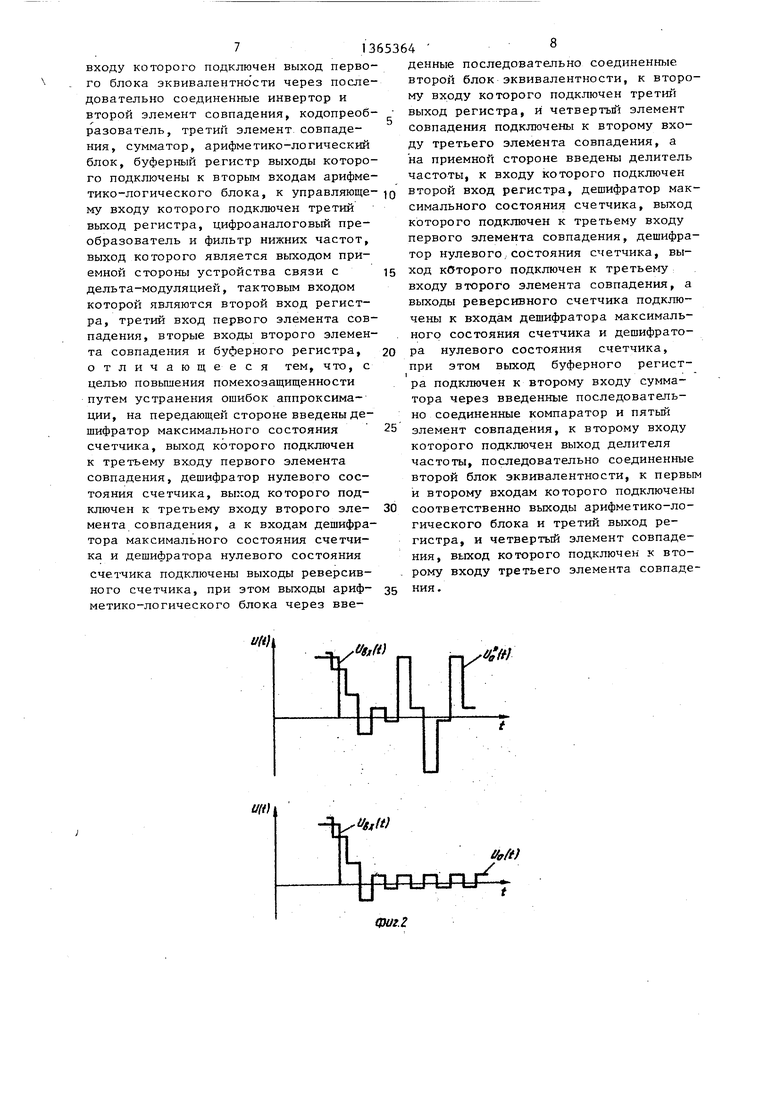

Дпя устранения этих недостатков в устройство введен компаратор 37,вход которого соединен с выходом ПАП 31.

Компаратор 37 представляет собой компаратор с окном (фиг.4). Тактовый вход декодера 2 через делитель 39 частоты подключен к второму входу элемента 38 совпадения, первый вход которого соединен с выходом компаратора 37. Сигнал с выхода элемента 38 совпадения частотой , где k - коэффици0 ент деления делителя 39 частоты,подключен к второму входу сумматора 28, коЪорьш уменьшает на ь аждом k такте код, сформированньш кодопреобразователем 26, на единицу, если на выходе

5 компаратора 37 формируется сигнал логической 1, обусловленньш тем, что сигнал апп|эоксимации Ид (t) на выходе

ЦАП 31 находится вне окна дополнительного компаратора 37. Ширина ок- 0 на определяется величиной минимального сГчага квантования д , и принята равной 3 и мин Формула изобретения

Устройство связи с дельта-модуляцией, содержащее на передающей стороне последовательно соединенные компаратор, первый вход которого является входом устройства связи с дельта-модуляцией, регистр, первый блок эквивалентности, первый элемент совпадения, реверс ивный счетчик, к второму входу которого подключен выход первого блока эквивалентности через Ттосле довательно соединенные инвертор и второй элемент совпадения, кодопреобразователь, третий элемент совп,аде- ния, арифметико-логический блок, буферный регистр, выходы которого под5

0

5

0 ключены к вторым входам арифметико- логического блока, и цифроаналоговый

входу которого подключен выход первого блока эквивалентно сти через последовательно соединенные инвертор и второй элемент совпадения, кодопреобразователь, третий элемент совпадения, сумматор, арифметико-логический блок, буферный регистр выходы которого подключены к вторым входам арифметико-логического блока, к управляюще- ig второй вход регистра, дешифратор макму входу которого подключен третий выход регистра, цифроаналоговый преобразователь и фильтр нижних частот, выход которого является выходом приемной стороны устройства связи с дельта-модуляцией, тактовым входом которой являются второй вход регистра, третий вход первого элемента совпадения, вторые входы второго элемента совпадения и буферного регистра, отличающееся тем, что, с целью повышения помехозащищенности путем устранения ошибок аппроксимации, на передающей стороне введены дешифратор максимального состояния счетчика, выход которого подключен к третьему входу первого элемента совпадения, дешифратор нулевого состояния счетчика, выход которого подключен к третьему входу второго эле- мента совпадения, а к входам дешифратора максимального состояния счетчика и дешифратора нулевого состояния счетчика подключены выходы реверсивного счетчика, при этом выходы ариф- метико-логического блока через введенные последовательно соединенные второй блок эквивалентности, к второму входу которого подключен третий выход регистра, и четвертьй элемент совпадения подключены к второму входу третьего элемента совпадения, а на приемной стороне введены делитель частоты, к входу которого подключен

симального состояния счетчика, выход которого подключен к третьему входу первого элемента совпадения, дешифратор нулевого,состояния счетчика, выход которого подключен к третьему входу второго элемента совпадения, а выходы реверсивного счетчика подключены к входам дешифратора максимального состояния счетчика и дешифратора нулевого состояния счетчика,

при этом выход буферного регист- 1 ра подключен к второму входу сумматора через введенные последовательно соединенные компаратор и пятый элемент совпадения, к второму входу которого подключен выход делителя частоты, последовательно соединенные второй блок эквивалентности, к первы и второму входам которого подключены соответственно выходы арифметико-логического блока и третий выход регистра, и четвертый элемент совпадения, выход которого подключен к второму входу третьего элемента совпадения.

-,

,lt)

tfaft)

Фиг.г

UoUli

фиг.З

| Дельта-кодер | 1984 |

|

SU1197087A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-01-07—Публикация

1986-06-10—Подача