тор 9 книтанцин, блок 10 проверки ошибки, датчик 11 сигнала квитанции, приемный блок 12 буферной памяти, ключ 13,инверторы 14 и 23, формирователь 15 управляющих сигналов, элементы ИЛИ 16,17,26 и 27, мультиплексоры 18 и 19, передатчик 20, таймеры 21, 24 и 25 и передающий блок буферной памят В режиме приема межмоноканального сообщения селектор 8 анализирует принадлежность передаваемого сообщения данной станции приемнику информации. При установлении принадлежности передаваемого сообщения данной станции на его выходе устанавливается уровень 1, в противном случае О. В режиме передачи внутримоноканального сообщения при заполнении блока 2.2. с его выхода поступает сигнал запроса передачи на первые входы таймеров 21 и 25. Записанная в блок 22 информция через мультиплексор 18 поступает на входы формирователя 15 и передатчика 20. Формирователь 15 формирует сигнал, разрешающий работу передатчика 20. Количество повторных передач является системным параметром. Если в течение установленного T.apiмером 21 промежутка времени поступает квитанция, то на выходе селектора 9 появляется уровень 1, который производит сброс таймеров 21 и 25, т.е. становится возможным передача следующего сообщения. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи информации по магистрали | 1983 |

|

SU1109782A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для передачи информации | 1989 |

|

SU1700571A1 |

| Устройство для передачи информации | 1988 |

|

SU1509970A1 |

| Устройство для перадачи информации | 1990 |

|

SU1711217A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ЭВМ С МОНОКАНАЛОМ | 1991 |

|

RU2032213C1 |

| СИСТЕМА УПРАВЛЕНИЯ СВЕТОФОРАМИ НА ПЕРЕКРЕСТКЕ | 1998 |

|

RU2158445C2 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ЭВМ С ОБШИМ КАНАЛОМ СВЯЗИ | 1995 |

|

RU2103730C1 |

| Устройство для передачи информации в кольцевом канале связи | 1989 |

|

SU1691864A1 |

| СПУТНИКОВАЯ СИСТЕМА СВЯЗИ "КИБОЛ" | 1992 |

|

RU2033693C1 |

Изобретение относится к электросвязи и может быть использовано в локальных вычислительных сетях. Цель изобретения - повышение быстродействия. Устройство содержит на каждой станции приемник 1, регистр 2 моноканала, дешифратор 3, компаратор 4, элементы И 5,6,28 и 29, счетчик 7 импульсов, селектор 8 адреса, селектор 9 квитанции, блок 10 проверки ошибоки, датчик 11 сигнала квитанции, приемный блок 12 буферной памяти, ключ 13, инверторы 14 и 23, формирователь 15 управляющих сигналов, элементы ИЛИ 16,17,26 и 27, мультиплексоры 18 и 19, передатчик 20, таймеры 21,24 и 25 и передающий блок 22 буферной памяти. В режиме приема межмоноканального сообщения селектор 8 анализирует принадлежность передавемого сообщения данной станции приемнику информации. При установлении принадлежности передаваемого сообщения данной станции на его выходе устанавливается уровень "1", в противном случае "0". В режиме передачи внутримоноканального сообщения при заполнении блока 22 с его выхода поступает сигнал запроса передачи на первые входы таймеров 21 и 25. Записанная в блок 22 информация через мультиплексор 18 поступает на входы формирователя 15 и передатчика 20. Формирователь 15 формирует сигнал, разрешающий работу передатчика 20. Количество повторных передач является системным параметром. Если в течение установленного таймером 21 промежутка времени поступает квитанция, то на выходе селектора 9 появляется уровень "1", который производит сброс таймеров 21 и 25, т.е. становится возможным передача следующего сообщения. 2 ил.

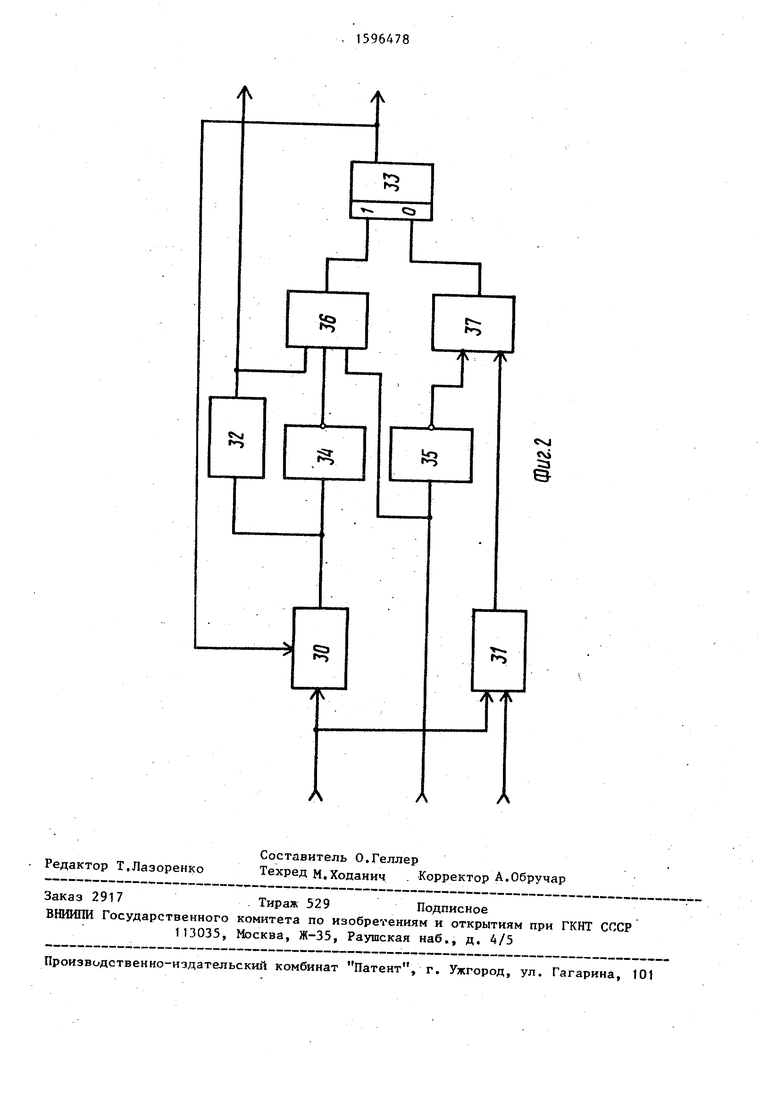

Изобретение относится к электросвязи и может быть использовано в ло кальных вычислительных сетях. Цель изобретения - повьшгение быстродействия. На фиг.1 изображена структурная электрическая схема предложенного устройства; на фиг.2 - структурная электрическая схема логического блока., Устройство для приема и передачи данных содержит на каждой станции приемник 1, регистр 2 моноканала, дешифратор 3, комапаратор 4,первый 5 и второй 6 элементы И, счетчик 7, импульсовJ селектор 8 адреса, селектор 9 квитанции, блок 10 проверки .ошибки, . датчик 11 сигнала квитанции приемный блок 12 буферной памяти, ключ 13, первый инвертор 14, формиро ватель 15 управляющих сигналов, первый 16 и второй 17 элементы ИЛИ, пер вый 18 и второй 19 мультиплексоры, передатчик 20, первый таймер 21, передающий блок 22 буферной памяти, второй инвертор 23, второй 24 и третий 25 таймеры, третий 26 и четвертый 27 элементы ИЛИ, третий 28 и чет вертый 29 элементы И. Логический блок содержит первый 30 и второй 31 детекторы, генератор 32 импульсов, триггер 33, первый 34 и второй 33 инверторы, элемент И 36 и элемент ИЛИ 37. Устройство работает следующим образом. Существует четыре режима работы: режим приема внутримоноканального сообщения, режим приема межмоноканального сообщения, режим передачи внутримоноканального сообщения, режим передачи межмоноканального сообщения . Режим приема внутримоноканального сообщения. Рассмотрим моноканал 1. Сообщение из моноканала поступает на выход приемника 1, откуда следует на информационные входы регистра 2, селекторов 8 и 9, блока 10 проверки ошибки, приемного блока 12 буферной памяти.. Одновременно с этим с выхода приемника.1 на синхровходы селекторов 8 и 9, блока 10 проверки ошибки, счетный первый вход счетчика 7 по- , ступают синхроимпульсы. При поступлении на первый вход счетчика 7 числа импульсов, соответствующих позиции номера моноканала-приемника информации, на его первом выходе появляется сигнал, записывающий номер моноканала-приемника в регистр 2. Код номера моноканала-приемника поступает на информационный вход дешифратора 3 и компаратора 4. Дешифратор 3 анализирует возможность достижения передаваемым сообщением моноканала-приемника инфомации. При установлении достижимости на выходе дешифратора 3 появляется уровень 1, в противном случае О. Компаратор 4 анализирует принадлежность передаваемого сообщения данном моноканалу (моноканалу i). При установлении соответствия передаваемого сообщения данному моноканалу на его выходе устанавливается уровень О, в противном случае 1. Селектор 8 адреса анализирует принадлежность передаваемого сообщения данной станции приемнику информации. При установлении принадлежности передаваемого сообщения дан ной станции на его выходе устанавливается уровень 1, в противном случае О. Приемный блок 12 буферной памяти в соответствии с поступающими синхроимпульсами запоминает передаваемое информационное сообщение, а блок 10 проверки анализирует наличие в нем ошибок, Если в передаваемом пакете нет ошибок, то на ее выхо де появляется уровень 1, в противном случае О, В данном режиме на выходе дешифратора 3 появляется уровень 1, на выходе компаратора 4 уровень О. Тогда на выходе инверто ра 23 устанавливается уровень 1, который через элемент ИЛИ 26 поступает на четвертый элемент И 6, При нахождении на выходе селектора 8 уро ня 1, т.е. принадлежности сообщения данному абоненту, на выходе элемента ИЛИ 16 появляется уровень 1, который в случае нахождения на выходе блока 10 проверки уровня 1 через элемент И 6 ра-зрешает перезапись информационного сообщения через ключ 13 (на управляющий вход которого поступил сигнал уровня 1) на пе вый информационный выход устройства. Одновременно с этим уровень изменяет направление передачи мультиплексора 18 на первый вход-выход и через элемент ИЛИ 17 в формирователь 15 управляющих сигналов поступает сигнал разрешения работы. С выхода датчика 11 сигнала квитанции информация через мультиплексор 18 подаётся на вход формирователя 15 управляющих сигналов. При этом на выходе детектора-30 устанавливается уровень О, генератор 32 формирует сигнал 1, длитель ность которого соответствует длине передаваемого в канале сообщения. Последний фронт сигнала с выхода генератора 32 через элемент И 36 устанавливает триггер 33 в 1, разрешая работу перехватчика 20. Передаваемая информация через передатчик 20 посту 1 пает в моноканал. По истечении времени передачи сообщения генератор 3Zустанавливается в состояние- О и производит сброс счетчика 7. Режим приема межмоноканального сообщения. Поступление сообщения на входы приемника 1, регистра 2, селекторов 8 и 9, блока 10 проверки ошибки, приемного блока 12 буферной памяти аналогично режиму приема внутримоноканального сообщения. При приеме сообщения, адресованного удаленному моноканалу, код последнего поступает на вход компаратора 4, на выходе которого устанавливается уровень 1, и на вход дешифратора 3. При установлении достижимости удаленного моноканалаприемника информации с выхода дешифратора 3 производится запуск таймера 24 на время задержки вьщачи квитанции подтверждения, гарантирующее отсутствие конфликтов при ее передаче. По истечении этого времени на выходе таймера 24 появляется уровень 1, который поступил через второй вход элемента ИЛИ 26 (на первом входе которого уровень О) на четвертый вход элемента И 6. Поступающий уровень 1 через элемент ИЛИ 16 поступает на третий вход элемента И 6 и в случае отсутствия ошибок, т.е. нахождении уровня 1 на выходе блока 10 проверки ошибки, разрешает перезапись из буфера 12 через мультиплексор 19, направление которого было изменено на второй вход-выход, в передающий буфер 22 другой станции моноканала j.Сообщение из блока 22 моноканала 1 затем передается через моноканал j адресату. В случае поступления квитанции на переданное сообщение по моноканалу j во время счета таймера 24 на прямом выходе селектора 9 появляется уровень 1, который производит сброс таймера 24 и квитанция подтверждения данным мостом не будет передана, а также не произойдет перезапись из буфера 12 ,в блок 22 другой станции, так как сигнал уровня О не даст соответствующего разрешения. Это же произойдет и в случае недостижимости удаленного моноканала приемника, так как на вьгкоде элемента ИЛИ 26 находится уровень О. Режим передачи внутримоноканального сообщения. 715 При заполнении блока 22 с его выхода поступает сигнал запроса передачи на первые входы таймеров 21 и 25, а также через элемент ИЛИ 17 на третий вход логического блока 15. Записанная в блок 22 информация через мультиплексор 18 поступает на входы логического блока 15 и передатчика |20.. В формиро)ателе 15 управляющих сигналов детекторы 30 и 31 устанавливаются в О и производится запуск генератора 32, который формирует сигнал , передний фронт сигнала с выхода генератора 32 через элемент И 3 на других входах которого находится уровень 1, устанавливает триггер 33 в 1, тем самым формируя сигнал разрешения работы передатчика 20, В случае, если в это время передается информация по моноканалу, то она производит установку детектора 31 и сигнал 1 на его выходе запрещает установку триггера 33, Сигнал разрешения передачи разрешает выдачу ин формации передатчиком 20 в моноканал Поступивший на входы таймеров 21 и 25 сигнал запроса передачи включае их на время, в течение которого долж на поступать квитанция на переданное сообщение при внутри- и межмоноканал ной передаче соответственно. Если в установленное время квитанция не поступит, то на выходе таймера 21 появится сигнал 1, бдиовременно с .. этим присходит прием устройством передающего сообщения, В данном режиме на выходе компаратора 4 устанавливается уровень О, а на выходе ий зертора 23 - уровень 1, Последний через элемент И 28 (после отработки таймера 21) через элемент ИЛИ 27 пос ,тупает на вход блока 22, устанавливая переданное сообщение в исходное с (стояние и сообщение повторно передается в канал. Количество повторных передач является системным параметро Если в течение установленного таймером 21 промежутка времени поступает квитанция, то на прямом выходе селек тора 9 появляется уровень 1,,который производит сброс таймеров 20 и 25, т,е. становится возможной передача следующего сообщения. Режим передачи межмоноканального сообщения. Функционирование формирователя 15 управляющих сигналов аналогично ре8жиму передачи внутрнмоноканального сообщения. Поступивший с блока 22 сигнал запускает таймер 25 на время, в течение которого должна поступить квитанция на переданное сообщение в данном режгтме. Предающееся сообщение принимается устройством. На выходе компаратора А устанавливается уро1, который после конца счета вень 1, который таймера 25 при непоступлении квитанции через элемент И 29 через элемент ИЛИ 27 поступает на вход блока 22, устанавливая переданное сообщение в исходное состояние 5 и сообщение повторно передается в канал. Количество повторных передач является системным параметром. Если в течение установленного таймером 25 промеж тка времени поступает квитанция, то на прямом выходе селектора 9 появляется уровень 1, который производит сброс таймеров 21 и 25, т.е. становится возможной передача следующего сообщения. Работа части устройства, функционирующей в моноканале j, аналогична вьш1ерассмотренной. Эффективность изобретения заключается в уменьшении времени межмоно- канальных передач, выражающ1- хся в возможности использования неограниченного числа мостов, связывающих любые моноканалы, что приводит к увеличению быстродействия устройства. Формула изобретения Устройство для приема и передачи дгчных, содержащее на каждой станции приемник, информационный выход которого соединен с первым входом формирователя управляющих сигналов, первьм входом регистра моноканала. входом селектора адреса, первым входом селектора квитанции с первым входом блока проверки ошибок и первым входом приемного блока буферной памяти,/второй вход которого подключен к синхронизирующему выходу приемника, второму входу блока проверки ошибок, второму входу селектора квитанции, втором входу селектора адреса и первому входу первого элемента И, выход которого соединен с первым входом счетчика, прямой выход которого соединен с вторым входом регистра моноканала, выход которого соединен с входом дешифратора и с первым входом компаратора, выход которого соединен с первым входом первого элемента ИЛИ, с входом первого инвертора : и первым входом второго мультиплексора, второй вход которого подключен к выходу приемника блока буферной памяти и первому входу ключа, второй вход которого подключен к выходу первого ин зертора, датчик сигнала квитанции, выход которого соединен с первым входом первого мультиплексора, выход которого соединен с вторы. I входом формирователя управ(Пяющих сигналов и первым входом передатчика, второй вход которого подключен к первому выходу формирователя управляющих сигналов, третий вход которого подключен к выходу втог рого элемента ИЛИ, первый вход которого соединен с третьим входом примного блока буферной памяти, с выходом второго элемента И и третьим входом первого мультиплексора, второй вход которого соединен с первьм выходом передающего блока буферной памяти, второй выход которого соединен с вторым входом второго элемента ИЛИ и первым входом первого таймера, второй вход которого подключен к прямому выходу селектора квитанции, инверсный вькод которого соединен с первым входом второго элемента И, второй вход которого подключен с выходу первого элемента ИЛИ, второй вход которого подключен к выходу селектора адреса, при этом второй выход формирователя управляющих сигналов соединен с вторым входом счетчика, инверсный выход которого соединен с вторым входом первого элемента И, выход блока проверки ошибок соединен с третьим входом второго элемента И, вход приемника и выход передатчика подключены к моноканалу, а / выход ключа и выход второго, мультиплексора являются информационными выходами устройства, информационными входами которого являются третий вход второго мультиплексора и первый вход передающего блока буферной памяти, второй вход первого компаратора является опорным входом устройства, отличающееся тем, что, с целью повышения быстродействия, введены второй и третий таймеры, третий и четвертый элементы ИЛИ, третий и четвертый элементы И и второй инвертор, выход которого соединен с первым входом третьего элемента И и с первым входом третьего.элемента ИЛИ, второй вход которого подключен к выходу второго таймера, первый вход которого подключен к прямому выходу селектора квитанции и первому входу третьего таймера, второй вход которого соединен с первым входом первого таймера, выход которого соединен с вторым входом третьего элемента И, выход которого соединен с первым входом четвертого элемента ИЛИ, второй вход которого подключен к выходу четвертого элемента И, первый вход которого соединенс выходом компаратора и входом второго инвертора, при этом выход дешифратора соединен с вторым входом второго таймера, выход третьего элемента ИЛИ подк.пючен к четвертому входу второго элемента И, выход третьего тг.ймера соединен с вторым входом четвертого элемента И, а выход четвертого элемента ИЛИ подключен к второму входу переключающего блока буферной памяти.

J

f

t

b-S

Ж Ж

Cvsl

J

g

r

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

Авторы

Даты

1990-09-30—Публикация

1988-07-07—Подача