Изобретение относится к специализированным средствам вычислительной техники и может быть использовано в аппаратуре, осутцеств тяющей спектральную обработку сигналов с дельта-модуляцией в реальном масштабе времени.

Цель изобретения - расширение области применения за счет вычисления дискретного преобразования Фурье () входного сигнала с линейной дельта-модуляцией.

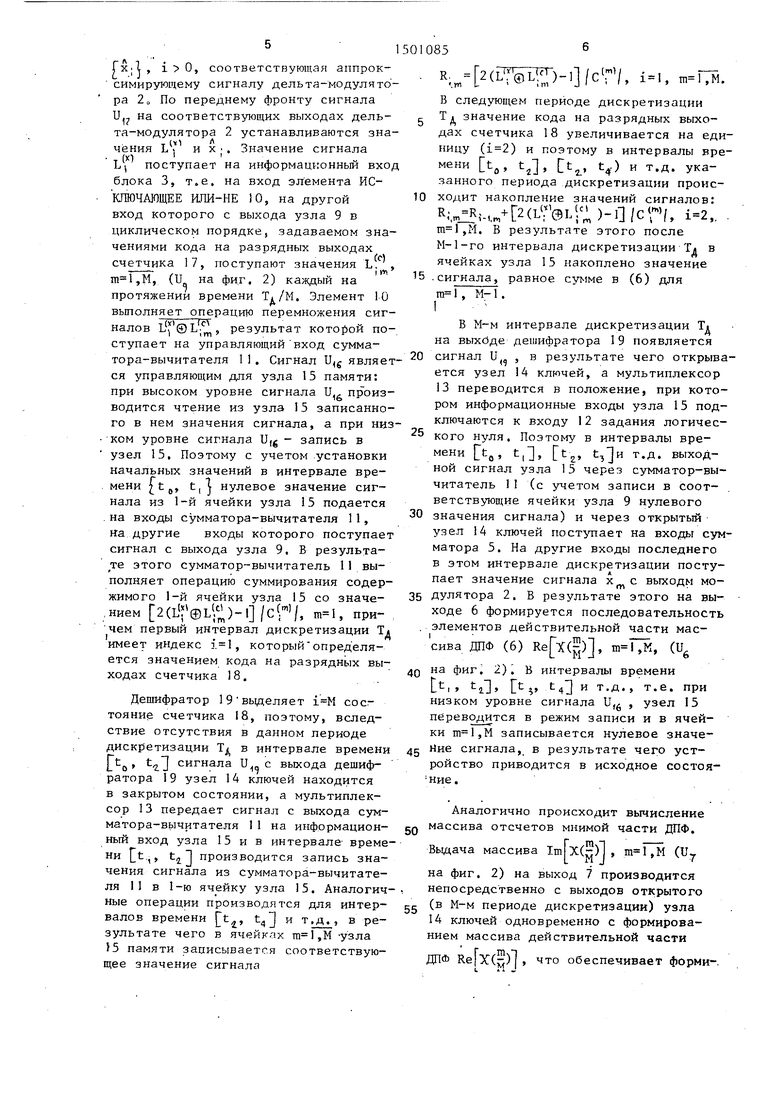

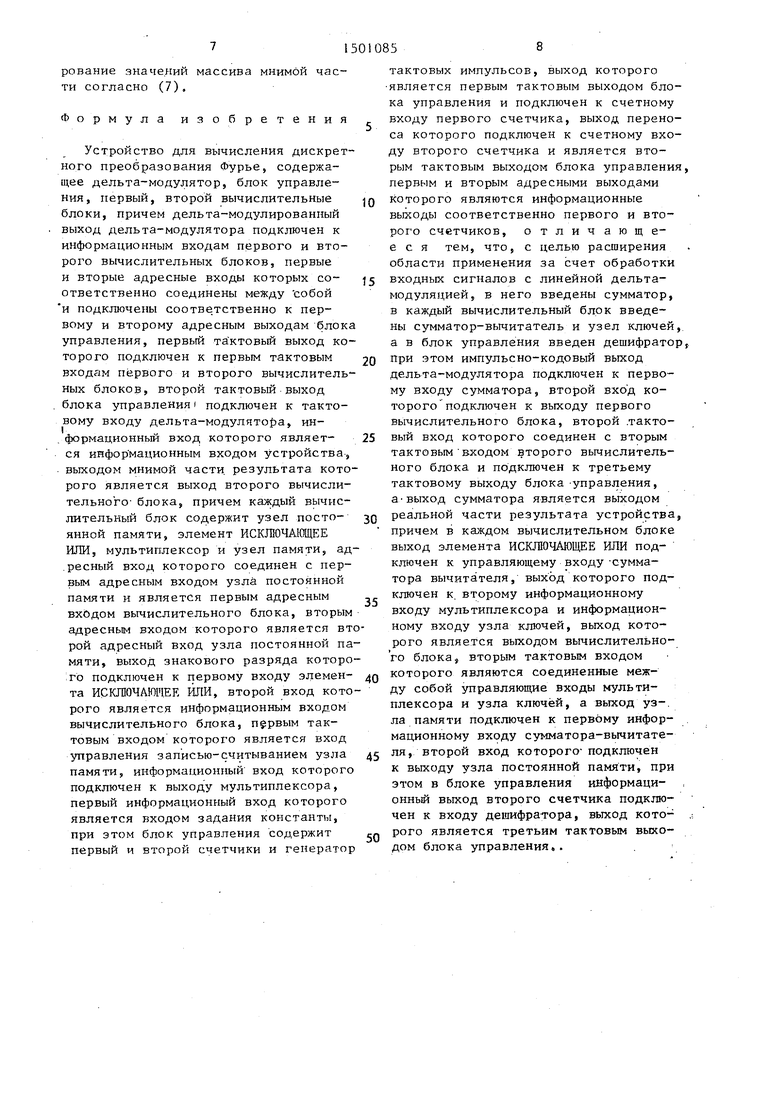

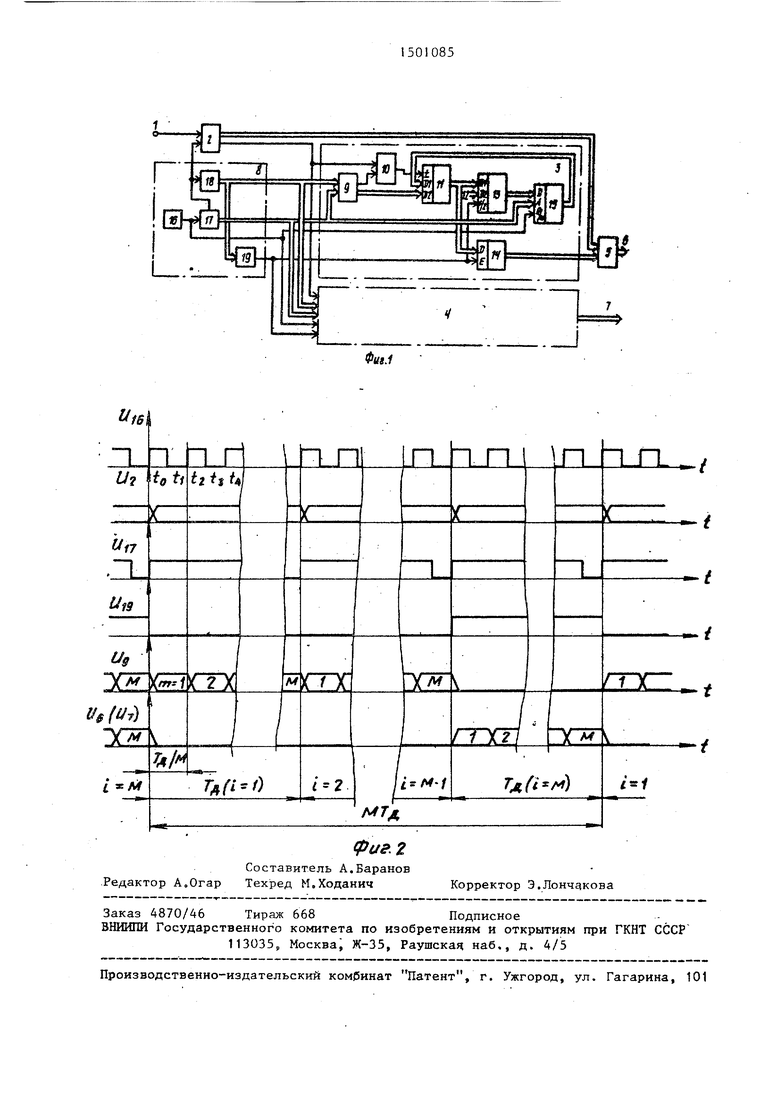

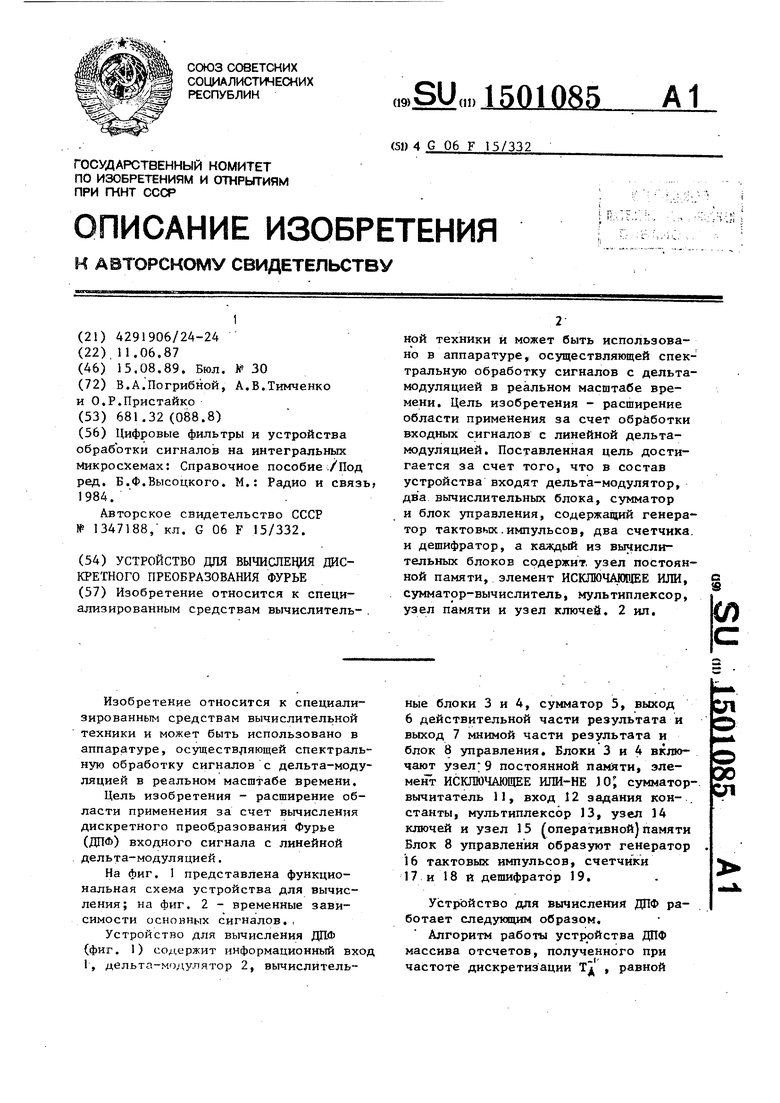

На фиг. 1 представлена функциональная схема устройства для вычисления; на фиг. 2 - временные зависимости основных сигналов.,

Устройство Для вычисления ДПФ (фиг. 1) содержит информационный вход 1, дельта-модулятор 2, вычислительные блоки 3 и 4, сумматор 5, выход 6 действительной части результата и выход 7 мнимой части результата и блок 8 управления. Блоки 3 и 4 включают узел 9 постоянной памяти, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ J0°, сумматор- вычитатель 11, вход 12 задания кон- . станты, мультиплексор 13, узел 14 ключей и узел 15 (оперативной)памяти Блок 8 управления образуют генератор

16тактовых импульсов, счетчики

17и 18 и дешифратор 19.

Устройство для вычисления ДПФ работает следующие образом.

Алгоритм работы устрюйства ДПФ массива отсчетов, полученного при частоте дискретизации Тд , равной

:л

о

00

ел

31501085

частоте дискретизации входного сигнала с ся в виде

X(muf)

1 Ц.ЭС1ЦИ1И илидми U uni -(-, , ,1-1, X

Гл//™ ЛTVT (1 N ll I Р h) //7%

дельта-модуляцией, записывает- ira Х(,пЛ -(L. ©L , )Ц Ь, /. (,/;

® М

kr|

(-j -- mk) , (1)

Приведенные алгоритмы реализуются в устройстве следующим образом.

Значения элементов последовательности , ,M-I, записаны в узле 9 постоянной памяти, причем

,- (

где &f(MT.i ) - разрешение по частоте;(®/Тд) число отсчетов;

® - интервал реализации. Примем и заменим отсчеты входного сигнала апроксимациями, характеризующими сигнал в формате дельта-модуляции:к

. .Z:ef;e 6 -l.l.

Х(|)

Z2.e exp(-j ), (2)

Тогда ДПФ (1) записываем в виде м k е

;-1

где k,m,,М.

Для получения алгоритма функционирования предлагаемого устройства заменим порядок суммирования в. (2), Область изменения значений индексов суммирования на плоскости (k,- i), как следует из (2), ограничена пряМ(М-1), а в элементы памяти с номера ми м(М-1)+1, м , т,е, для , записывается нулевое значение сигнала. Выходы узла 9 памяти разделены на дв

20 поля, В первое поле, имеющее один

разряд, записывается значение L . , а

во второе поле записывается значение

)) L . (.

Аналогично производится запись 25 значений элементов последовательност S.B блоке 4.

Перед началом работы устройства необходимо обнулить узел 13 памяти и.установить счетчики 17 и 18 в намыми , , . Поэтому при изме-30 чальное (единичное) состояние (цепи

Приведенные алгоритмы реализуются в устройстве следующим образом.

Значения элементов последовательности , ,M-I, записаны в узле 9 постоянной памяти, причем

первые адресные входы блока 3 соот- ве-тствуют индексу т, а вторые адресные входы блока 3 - индексу i. Запись значений С j производится подряд, начиная с нулевого элемента памяти с

номером и заканчивая номером

М(М-1), а в элементы памяти с номерами м(М-1)+1, м , т,е, для , записывается нулевое значение сигнала. Выходы узла 9 памяти разделены на два

поля, В первое поле, имеющее один

разряд, записывается значение L . , а

во второе поле записывается значение

)) L . (.

Аналогично производится запись значений элементов последовательности S.B блоке 4.

Перед началом работы устройства необходимо обнулить узел 13 памяти и.установить счетчики 17 и 18 в на

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления дискретного преобразования Фурье | 1990 |

|

SU1727131A1 |

| Дельта-модулятор | 1989 |

|

SU1649666A1 |

| Цифровой фильтр | 1990 |

|

SU1736002A2 |

| Цифровой фильтр | 1986 |

|

SU1387174A1 |

| Цифровой фильтр с дельта-модуляцией | 1988 |

|

SU1527713A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1988 |

|

SU1510091A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1986 |

|

SU1424119A1 |

| Цифровой фильтр | 1987 |

|

SU1425840A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1987 |

|

SU1494210A1 |

| Цифровой фильтр | 1989 |

|

SU1695492A2 |

Изобретение относится к специализированным средствам вычислительной техники и может быть использовано в аппаратуре, осуществляющей спектральную обработку сигналов с дельта-модуляцией в реальном масштабе времени. Цель изобретения - расширение области применения за счет обработки входных сигналов с линейной дельта-модуляцией. Поставленная цель достигается за счет того, что в состав устройства входят дельта-модулятор, два вычислительных блока, сумматор и блок управления, содержащий генератор таковых импульсов, два счетчика и дешифратор, а каждый из вычислительных блоков содержит узел постоянной памяти, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, сумматор-вычитатель, мультиплексор, узел памяти и узел ключей. 2 ил.

нении порядка суммирования индекс i будет меняться от 1 до М, а индекс k от i до М, На основании этого получим, г

м м

(3)

Т(2)

-v

.2,(-3 |- mk).

Действительную и мнимую части (3) преобразуем следующим образом:

KefX(|) i:er.|:eosf Л„...

. i е Г сГ;

Мм

Im

Ф1

,-(х)

М-1

с 1

7 sin -- Tnk

kTT- . М

(4)

(5)

суммы соответствующих JQ

45

величин. , что е; 2L; -I,

и , поступают на счетчик 18 с коэффициентом пересчета М, и на тактовый вход дельта-модулятора 2, Модулятор 2 преобразует поступающий с шины 1

(4) и (5) дает 55 вводной сигнал x(t), причем на одном выходе дельта-модулятора 2 форми- уется дельта-последовательность

а на другом выходе - последовательность

(1 г (т)

L, €|0,п, представим значения С;

(2Lf -1) I С ; /, S7 (2ЬТ -1) / S , подстановка которых в

следующие алгоритмы; .

Iруется дель.та-прследовательН1

еГх() „ + Г Г2(1.;%1;Я)-1Т|сГ|.(6) г фиг- 2), L J ; L-1 другом выходе - последовател:

сброса на фиг. 1 не показаны).

т.

Вычисление массива. ДПФ X С) ,,M

производится раздельно для. действи- тельнрй и мнимой частей блоками 3 и 4, Различия в функционирований указанных блоков отсутствуют, поэтому рассмотрим реализацию вычислений массива отсчетов действительной части ДПФ, которые производятся в режиме реального времени следующим образом.

Тактовый генератор 16 генерирует непрерывную последовательность импульсов и, (фиг.2) с .частотой, кратной частоте дискретизации T-l входного сигнала в формате дельта- модуляции, , Импульсы U,g поступают на счетчик 17, имеющей коэффи- циент пересчета М, Импульсы переноса

и , поступают на счетчик 18 с коэффициентом пересчета М, и на тактовы вход дельта-модулятора 2, Модулятор 2 преобразует поступающий с шины 1

ГхД , i о, соответствующая аппроксимирующему сигналу дельта-модулято ра 2 о По переднему фронту сигнала и., на соответствующих выходах дельта-модулятора 2 устанавливаются зна Значение сигнала

т (Vl

чения LI и X

(XI

М

поступает на информацконньй вхо блока 3, т.е. на вход элемента ИС- КЛЮЧАЮЩЕЕ ИЛИ-НЕ 10, на другой вход которого с выхода узла 9 в циклическом порядке, задаваемом значениями кода на разрядных выходах

fc счетчика 17, поступают значения L.

п)1,М, (и на фиг. 2) каждый на протяжении времени Ti/M. Элемент 10 выполняет операцию перемножения сигналов результат которой поступает на управляющий вход сумма- тора-вычитателя 11. Сигнал является управляющим для узла 15 памяти: при высоком уровне сигнала U производится чтение из узла 15 записанного в нем значения сигнала, а при низком уровне сигнала U,g - запись в узел 15. Поэтому с учетом-установки начальных значений в интервале времени It, t,j нулевое значение сигнала из 1-й ячейки узла 15 подается .на входы сумматора-вычитателя 11, на другие входы которого поступает сигнал с выхода узла 9. В результа- те этого сумматор-вычитатель 11 выполняет операцию суммирования содержимого 1-й ячейки узла 15 со значе- .нием 2(L f©Li ), , при- чем первый интервал дискретизации Т имеет индекс з.1, который опред еля- ется значением кода на разрядных выходах счетчика 18.

Дешифратор 19 выделяет состояние счетчика 18, поэтому, вследствие отсутствия в данном периоде дискретизации Tj в интервале времени -гЗ сигнала с выхода дешифратора 19 узел 14 ключей находится в закрытом состоянии, а мультиплексор 13 передает сигнал с выхода сумматора-вычитателя I1 на информационный вход узла 15 и в интервале- времени Ct.,, tj П производится запись значения сигнала из сумматора-вычитателя 11 в 1-ю ячейку узла 15. Аналогичные операции производятся для интервалов времени t, Ц и т.д., в результате чего в ячейках ,М -узла 15 памяти записывается соответствующее значение сигнала

01083

. R.2(U), , .

В следующем периоде дискретизации с Тд значение кода на разрядных выходах счетчика 18 увеличивается на единицу () и поэтому в интервалы времени t, tj, t,, t,) и т.д. указанного периода дискретизации проис- 10 ходит накопление значений сигналов:

к,--,,.-Г2аГ0ьГ:), ,, .

,M. В результате этого после М-1-го интервала дискретизации Тд в ячейках узла 15 накоплено значение 5 .сигнала равное сумме в (6) для , М-1.

В М-м интервале дискретизации Тд на выходе дешифратора 19 появляется

сигнал и , в результате чего открывается узел 14 ключей, а мультиплексор 13 переводится в положение, при котором информационные входы узла 15 подключаются к входу 12 задания логического нуля. Поэтому в интервалы времени , t|, t, т.д. выходной сигнал узла 15 через сумматор-вы- читатель 1I (с учетом записи в соответствующие ячейки узла 9 нулевого

значения сигнала) и через открытый

узел 14 ключей поступает на входы сумматора 5. На другие входы последнего в этом интервале дискретизации поступает значение сигнала х с выходм модулятора 2. В результате этого на выходе 6 формируется последовательность элементов действительной части массива ДПФ (6) RefxC), , (Ug

на фиг. 2)1 В интервалы времени

t,, tj, t, t и т.д., т.е. при низком уровне сигнала U, , узел 15 переводится в режим записи и в ячейки ,M записывается нулевое значеi ne сигнала, в результате чего устройство приводится в исходное состся- ние.

Аналогично происходит вычисление массива отсчетов мнимой части ДПФ.

Выдача массива Imj ХС) , ,М (.

на фиг. 2) на выход 7 производится непосредственно с выходов открытого (в М-м периоде дискретизации) узла 14 ключей одновременно с формированием массива действительной части

ДПФ RelxC-), что обеспечивает формирование значений массива мнимой части согласно (7).

Формула изобретения

Устройство для вычисления дискретного преобразования Фурье, содержащее дельта-модулятор, блок управления, первый, второй вычислительные блоки, причем дельта-МОдулированный выход дельта-модулятора подключен к информационным входам первого и второго вычислительных блоков, первые и вторые адресные входы которых со- ответственно соединены между собой и подключены соотве.тственно к первому и второму адресным выходам блока управления, первьгй та ктовьм выход которого подключен к первым тактовым входам первого и второго вычислительных блоков, второй тактовый выход блока управленияi подключен к тактовому входу дельта-модулято|5а, ин- формационньй вход, которого являет- ся инфор мационным входом устройства-, - выходом мнимой части, результата которого является выход второго вычислительного- блока, причем каждый вычислительный блок содержит узел посто- НИНОЙ памяти, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, мультиплексор и узел памяти, ад .ресный вход которого соединен с первым адресным входом узла постоянной памяти и является первым адресным вхйдом вычислительного блока, вторым адресным входом которого является втрой адресный вход узла постоянной памяти, выход знакового разряда которо го подключен к первому входу элемен- та ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого является информационным входом вычислительного блока, первым тактовым входом которого является вход управления записью-считыванием узла памяти, информационный вход которого подключен к выходу мультиплексора, первый информационный вход которого является входом задания константы, при этом блок управления содержит первый и второй счетчики и генератор

тактовых импульсов, выход которого является первым тактовым выходом блока управления и подключен к счетному входу первого счетчика, выход переноса которого подключен к счетному входу второго счетчика и является вторым тактовым выходом блока управлени первым и вторым адресными выходами которого являются информационные выходы соответственно первого и второго счетчиков, отличающееся тем, что, с целью расширения области применения за счет обработки входных сигналов с линейной дельта- модуляцией, в него введены сумматор, в каждый вычислительный блок введены сумматор-вычитатель и узел ключей а в блок управления введен дешифрато При этом импульсно-кодовый выход дельта-модулятора подключен к первому входу сумматора, второй вход которого подключен к выходу первого вычислительного блока, второй .тактовый вход которого соединен с вторым тактовым входом второго вычислительного блока и подключен к третьему тактовому выходу блока -управления, а-выход сумматора является выходом реальной части результата устройства причем в каждом вычислительном блоке выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к управляющему входу -сумматора вычитателя, выход которого подключен к. второму информационному входу мультиплексора и информационному входу узла ключей, выход которого является выходом вычислительно- го блока, вторым тактовым входом которого являются соединенные между собой управляющие входы мультиплексора и узла ключей, а выход уз-, ла памяти подключен к первому информационному входу сумматора-вычитате- ля, второй вход которого-подключен к выходу узла постоянной памяти, при этом в блоке управления информационный выход второго счетчика подключен к входу дешифратора, выход кото- рого является третьим тактовым выходом блока управления,.

1

т

nn

г/г

iob

ii s

Urr

.ZL

u-fj

M

Us {U-,} TM

TAJM

xM

ГлЛ )

/--г

П

XL

rui

-/

UJL

ATJCI

1-1

| Цифровые фильтры и устройства обработки сигналов на интегральных микросхемах: Справочное пособие ./Под ред | |||

| Б.Ф.Высоцкого | |||

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Цифровой фильтр с дельта-модуляцией | 1985 |

|

SU1347188A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1987-06-11—Подача