Изобретение относится к автоматике и вычислительной технике и может быть использовано для выполнения кольцевого сдвига на частях формата операнда.

Целью изобретения является повышение технологичности за счет регулярности структуры.

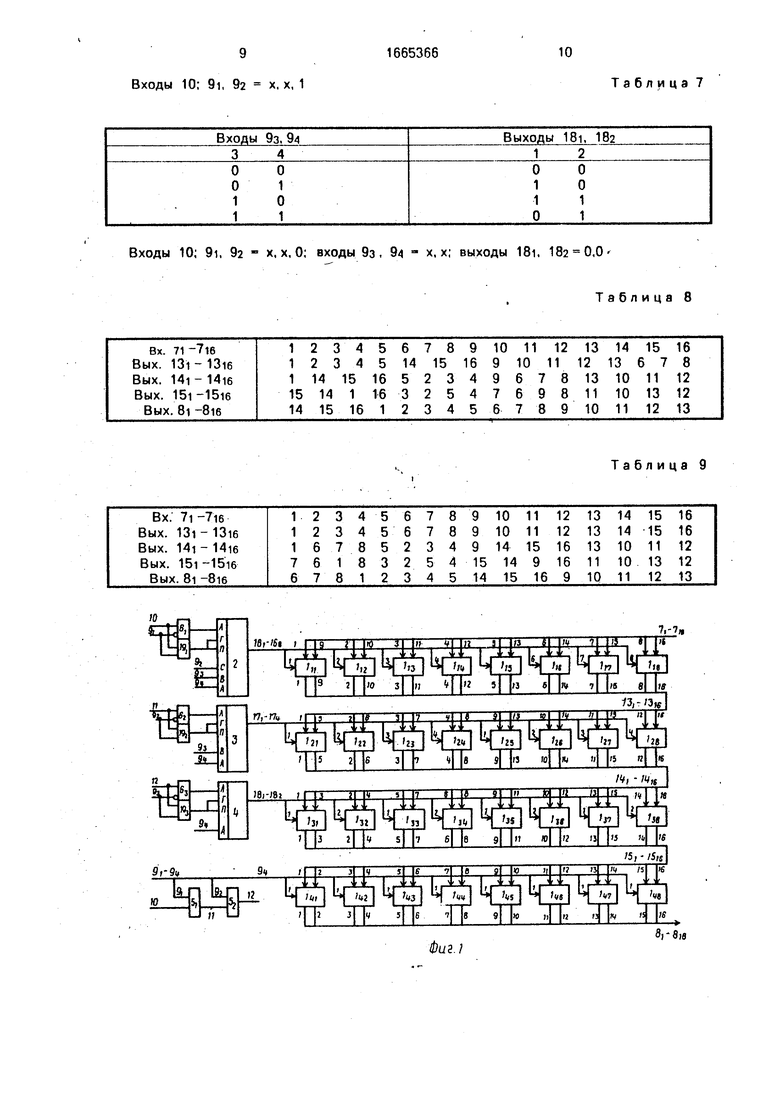

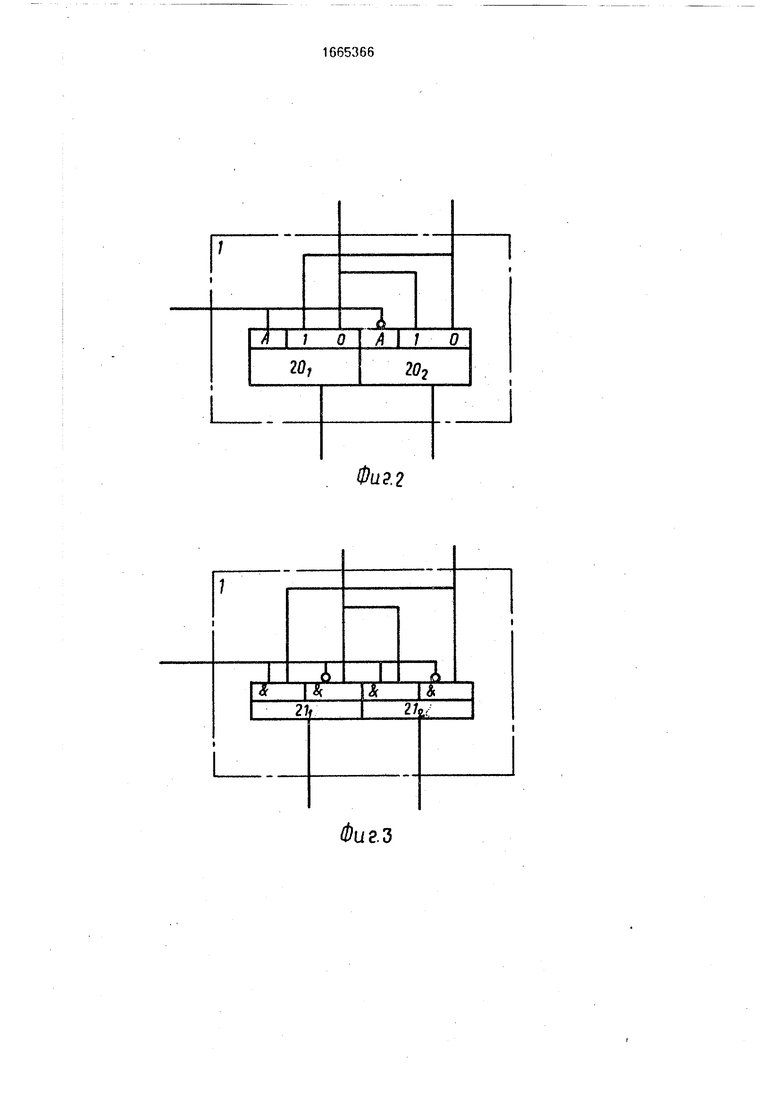

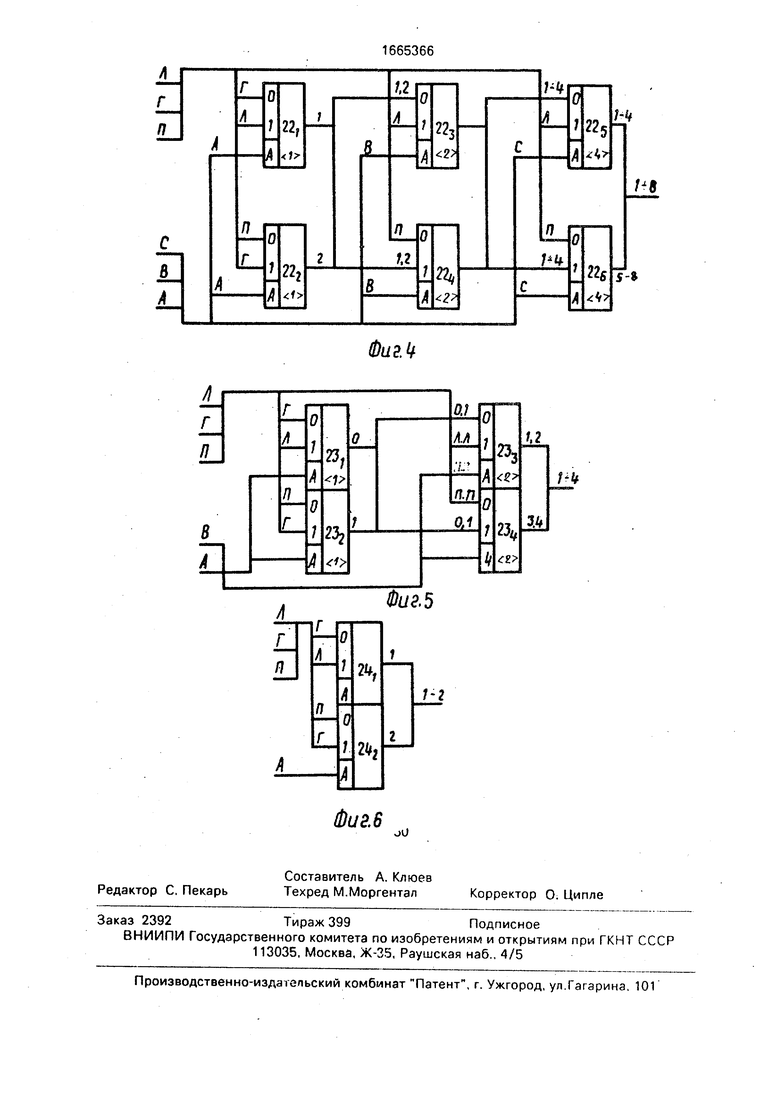

На фиг. 1 представлена схема устройства для сдвига; на фиг. 2 и 3 - примеры реализации коммутатора; на фиг. 4-6- примеры реализации с первого по третий дешифраторов соответственно.

Устройство (фиг. 1) содержит матрицу коммутаторов 1ц-148, с первого по третий дешифраторы 2-4 соответственно, первый и второй элементы ИЛИ 5i и 5а, с первого по третий элементы 61-63 запрета, входы 7i-7i6 разрядов информационного входа устройства, выходы 81-816 разрядов выхода устройства, входы 9i-94 разрядов входа кода сдвига устройства, вход 10 признака формата сдвига устройства, выход 11 первого элемента ИЛИ 5i, выход 12 второго элемента ИЛИ 5а, выходы коммутаторов 111-118 первой строки матрицы соответственно, выходы 14i-14ie коммутаторов

ВТОРОЙ СТРОКИ МЗТрИЦЫ СООТВ6ТСТвенно, выходы 15i-15ie коммутаторов 1з1-1з8 третьей строки матрицы соответственно, выходы 16i-16s первого дешифратора 2. выходы 17i-174 второго дешифратора 3, выходы 181-182 третьего дешифратора 4, с первого по третий элементы И 19i-19s соответственно.

Коммутаторы 1 (фиг. 2 и 3) содержат мультиплексоры 20i и 202 и элементы И- ИЛИ211И212

Первый дешифратор 2 (фиг. 4) содержит с первого по шестой мультиплексоры 22i-226.

Второй дешифратор 3 (фиг 5) содержит с первого по четвертый мультиплексоры 231-234.

Третий дешифратор 4 (фиг. 6) содержит первый и второй мультиплексоры 24i и 24г.

Принцип построения устройства заключается в следующем. Операция кольцевого сдвига на массиве из П элементов разбивается по строкам матрицы на N (N Iog2 П) более простых операций обмена, а именно - в 1-й. 2-йN-й строке матрицы производится формирование подмассивов,

О

о ел

Сл)

о

О

сдвинутых по кольцу, форматом 2, 4 П

элементов путем обмена группами плотно расположенных элементов в парах соседних подмассивов меньшего формата. Эти группы элементов берутся от левого края до позиции, определяемой кодом сдвига, причем вторые группы элементов остаются на своих местах без изменений, либо, наоборот, в зависимости от кода сдвига обмен производится вторыми группами элемен- тов, а первые группы остаются без изменения.

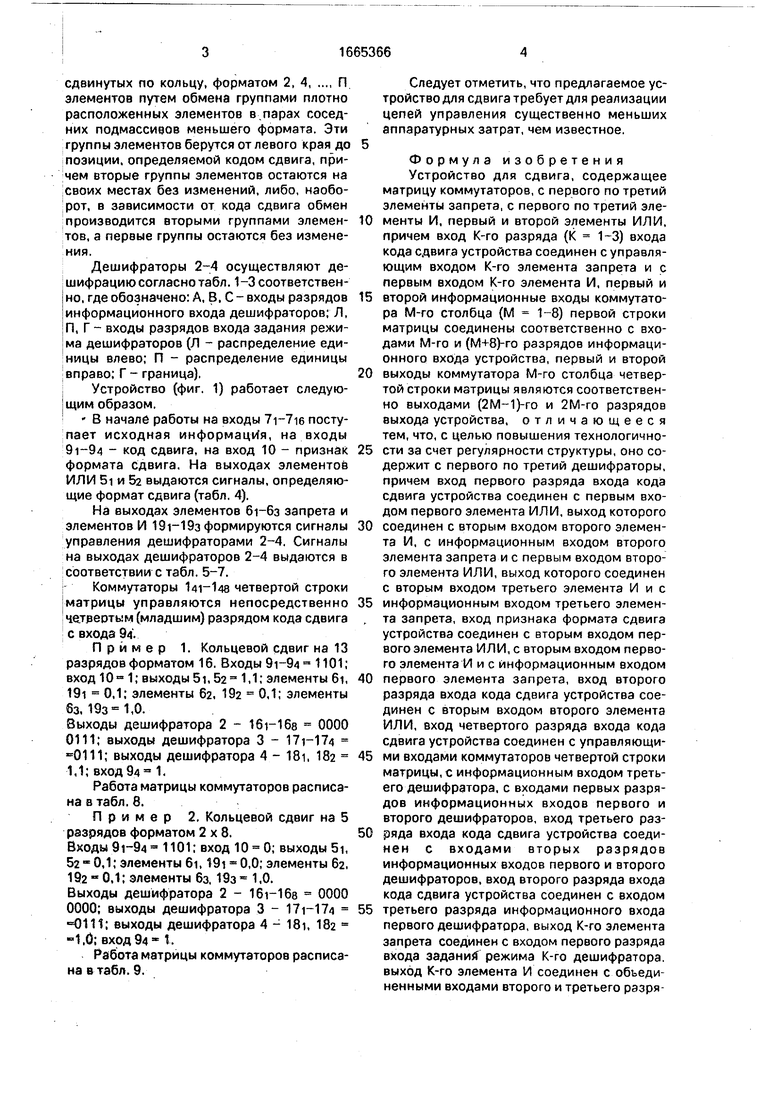

Дешифраторы 2-4 осуществляют дешифрацию согласно табл. 1-3 соответственно, где обозначено: А, В. С - входы разрядов информационного входа дешифраторов; Л, П, Г - входы разрядов входа задания режима дешифраторов (Л - распределение единицы влево; П - распределение единицы вправо; Г - граница),

Устройство (фиг. 1) работает следую- щим образом.

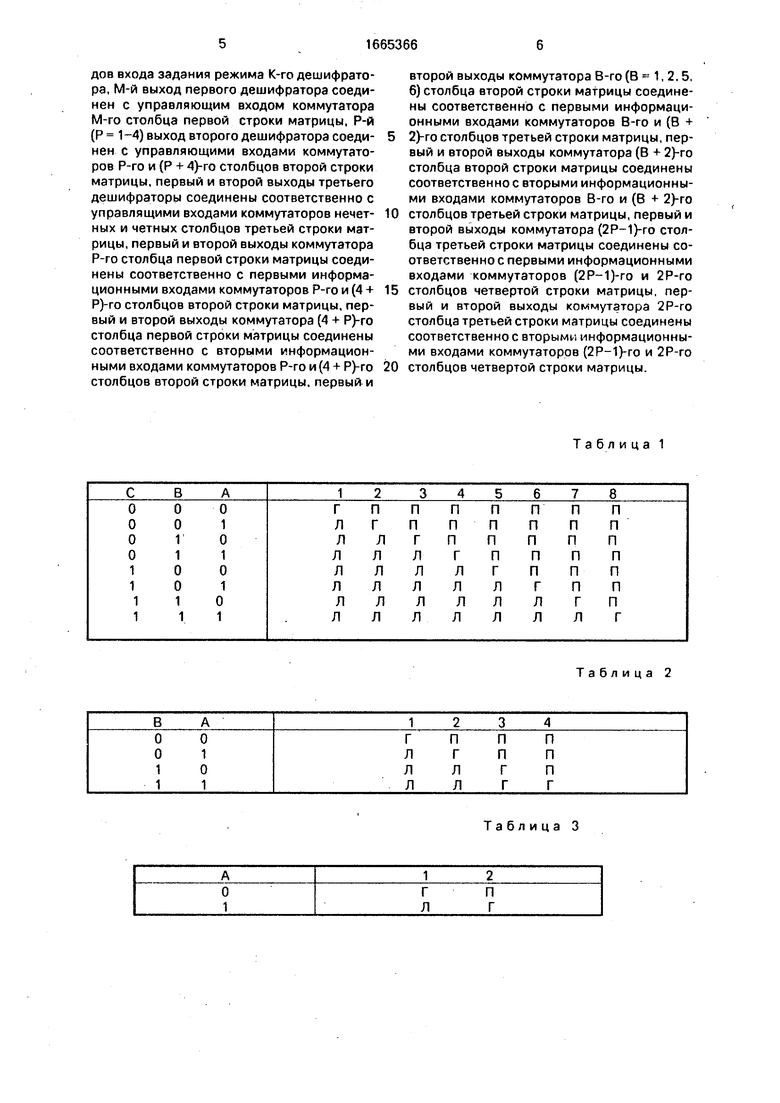

В начале работы на входы 7i-7ie поступает исходная информация, на входы 91-94 - код сдвига, на вход 10 - признак формата сдвига. На выходах элементов ИЛИ 5i и 52 выдаются сигналы, определяющие формат сдвига (табл, 4).

На выходах элементов 61-63 запрета и элементов И 191-19з формируются сигналы управления дешифраторами 2-4. Сигналы на выходах дешифраторов 2-4 выдаются в соответствии с табл. 5-7.

Коммутаторы 141-148 четвертой строки матрицы управляются непосредственно четвертым (младшим) разрядом кода сдвига с входа 94.

Пример 1. Кольцевой сдвиг на 13 разрядов форматом 16. Входы 9i-94 1101; вход 10ет 1; выходы 5i, 52 1,1; элементы 6i, 19i 0,1; элементы 62, 192 0,1; элементы 6з,

Выходы дешифратора 2 - 16i-16e 0000 0111; выходы дешифратора 3 - 0111; выходы дешифратора 4 - 18i, 182 1,1; вход 94 1.

Работа матрицы коммутаторов расписана в табл. 8.

Пример 2, Кольцевой сдвиг на 5 разрядов форматом 2x8.

Входы 91-94 1101; вход 10 0; выходы 5i, 62 - 0,1; элементы 61,19i 0,0; элементы 62, 192-0,1; элементы 6з. 19з 1,0. Выходы дешифратора 2 - 16i-16e 0000 0000; выходы дешифратора 3 - 171-174 0111; выходы дешифратора 4 - 18i, 182 -1,0: вход 94 1.

Работа матрицы коммутаторов расписана в табл. 9.

Следует отметить, что предлагаемое устройство для сдвига требует для реализации цепей управления существенно меньших аппаратурных затрат, чем известное.

Формула изобретения Устройство для сдвига, содержащее матрицу коммутаторов, с первого по третий элементы запрета, с первого по третий элементы И, первый и второй элементы ИЛИ, причем вход К-го разряда (К 1-3) входа кода сдвига устройства соединен с управляющим входом К-го элемента запрета и с первым входом К-го элемента И, первый и второй информационные входы коммутатора М-го столбца (М 1-8) первой строки матрицы соединены соответственно с входами М-ro и (М+8)-го разрядов информационного входа устройства, первый и второй выходы коммутатора М-го столбца четвертой строки матрицы являются соответственно выходами (2М-1)-го и 2М-го разрядов выхода устройства, отличающееся тем, что, с целью повышения технологичности за счет регулярности структуры, оно содержит с первого по третий дешифраторы, причем вход первого разряда входа кода сдвига устройства соединен с первым входом первого элемента ИЛИ, выход которого соединен с вторым входом второго элемента И, с информационным входом второго элемента запрета и с первым входом второго элемента ИЛИ, выход которого соединен с вторым входом третьего элемента И и с информационным входом третьего элемента запрета, вход признака формата сдвига устройства соединен с вторым входом первого элемента ИЛИ, с вторым входом первого элемента И и с информационным входом первого элемента запрета, вход второго разряда входа кода сдвига устройства соединен с вторым входом второго элемента ИЛИ, вход четвертого разряда входа кода сдвига устройства соединен с управляющими входами коммутаторов четвертой строки матрицы, с информационным входом третьего дешифратора, с входами первых разрядов информационных входов первого и второго дешифраторов, вход третьего разряда входа кода сдвига устройства соединен с входами вторых разрядов информационных входов первого и второго дешифраторов, вход второго разряда входа кода сдвига устройства соединен с входом третьего разряда информационного входа первого дешифратора, выход К-го элемента запрета соединен с входом первого разряда входа задания режима К-го дешифратора, выход К-го элемента И соединен с объединенными входами второго и третьего рэзрядов входа задания режима К-ro дешифратора, М-й выход первого дешифратора соединен с управляющим входом коммутатора М-го столбца первой строки матрицы. Р-й (Р 1 -4) выход второго дешифратора соеди- нен с управляющими входами коммутаторов Р-го и (Р + 4)-го столбцов второй строки матрицы, первый и второй выходы третьего дешифраторы соединены соответственно с управлящими входами коммутаторов нечет- ных и четных столбцов третьей строки матрицы, первый и второй выходы коммутатора Р-го столбца первой строки матрицы соединены соответственно с первыми информационными входами коммутаторов Р-го и (4 + Р)-го столбцов второй строки матрицы, первый и второй выходы коммутатора (4 + Р)-го столбца первой строки матрицы соединены соответственно с вторыми информационными входами коммутаторов Р-го и (4 + Р)-го столбцов второй строки матрицы, первый и

второй выходы коммутатора В-ro (В - 1,2.5, 6) столбца второй строки матрицы соединены соответственно с первыми информационными входами коммутаторов В-ro и (В + 2)-го столбцов третьей строки матрицы, первый и второй выходы коммутатора (В + 2)-го столбца второй строки матрицы соединены соответственно с вторыми информационными входами коммутаторов В-го и (В + 2)-го столбцов третьей строки матрицы, первый и второй выходы коммутатора (2Р-1}-го столбца третьей строки матрицы соединены соответственно с первыми информационными входами коммутаторов (2Р-1)-го и 2Р-го столбцов четвертой строки матрицы, первый и второй выходы коммутатора 2Р-го столбца третьей строки матрицы соединены соответственно с вторыми информационными входами коммутаторов (2Р-1)-го и 2Р-го столбцов четвертой строки матрицы.

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| СИСТЕМА КОММУТАЦИИ ПРОЦЕССОРОВ | 1991 |

|

RU2006931C1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1785041A1 |

| Дисплейный процессор | 1981 |

|

SU1292031A1 |

| Устройство для умножения | 1987 |

|

SU1501043A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1275521A1 |

| Устройство для исследования параметров графов | 1986 |

|

SU1508229A1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2185656C2 |

| Устройство для ввода цифровой информации | 1978 |

|

SU769519A1 |

| Устройство для моделирования процесса выбора товара | 2017 |

|

RU2666617C1 |

Изобретение относится к вычислительной технике и предназначено для выполнения кольцевого сдвига на частях формата операнда. Целью изобретения является повышение технологичности за счет регулярности структуры. Устройство содержит матрицу коммутаторов, с первого по третий дешифраторы, первый и второй элементы ИЛИ, с первого по третий элементы запрета, с первого по третий элементы И со связями. 6 ил., 9 табл.

Таблица 1

Таблица 2

Примечание. X - произвольное состояние. Вход

Выходы 10 0; 9i -94 хххх ; выходы 16i - 16а 0000 0000. Входы 10; 9i х, 1

Выходы 10;9i x, 0; Входы 9а - 94 ххх ; выходы - 0000.

Таблица 4

Таблица 5

Таблица 6

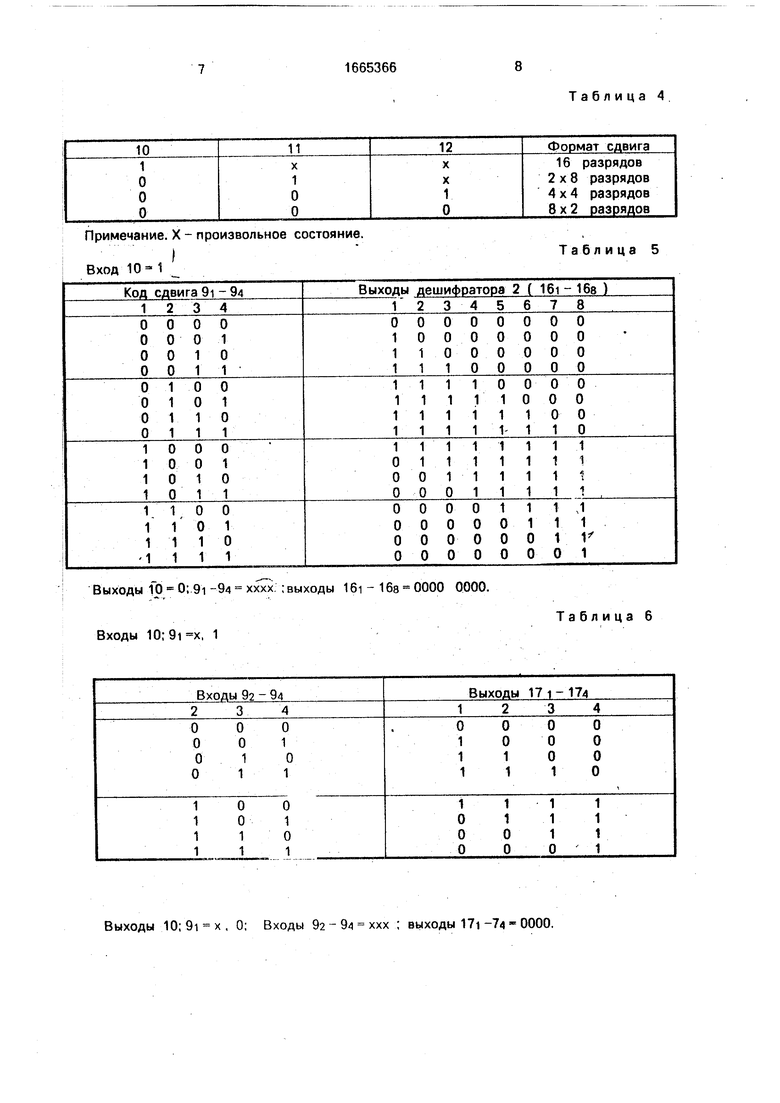

Входы 10; 9i, 92 х, х, 1

Входы 10; 9i, 92 - х, х, 0; входы 9з, 94 - х, х; выходы 18i. 182 0,0

ю

Mrtfl. I П9 | 10 31 |№ VI 1 31 U3 61 I) 71 | lit

7,Эг

93

г ю з п Ч « 5 « 6 « в U

9

г№,Щ

тата

5 г 9

таЦ чзтатата

ПТ TF ИУ 7ПГ ТЬ ЯТ Th TF

«Г/5ц|

Таблица 7

Таблица 8

Таблица 9

lit

7,7„

г I Ч г з I Ч я I Ч., I .bt.

/ - Ц« I

г№,Щ

тата

тата

Th TF

Фиа /

о г 1 у

г

Ж

JL

гог

1ог

о t У

99CS991

А

Ляят

Г

MBW

п

с

мм

JL

А

1-k

5-

0иг

| Авторское свидетельство СССР N51187160, кл.С 06 F 7/38 | |||

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Устройство для сдвига | 1983 |

|

SU1164695A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-23—Публикация

1989-05-12—Подача