:t

JTF1 -

Т .- - - - -

4W

е

| название | год | авторы | номер документа |

|---|---|---|---|

| Вероятностный интегратор | 1984 |

|

SU1242941A1 |

| Вероятностный интегратор | 1986 |

|

SU1328814A1 |

| Коррелометр | 1986 |

|

SU1451722A1 |

| Устройство коррекции | 1987 |

|

SU1499507A1 |

| Способ коррекции межсимвольной интерференции и устройство для его осуществления | 1985 |

|

SU1300646A1 |

| Цифровой Фурье-преобразователь | 1982 |

|

SU1043663A1 |

| Аналого-цифровой инкрементный умножитель | 1982 |

|

SU1057971A1 |

| Устройство для вычисления функции арктангенса отношения | 1988 |

|

SU1615709A1 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1983 |

|

SU1152016A1 |

| Устройство для вычисления дискретного преобразования Фурье в модулярной системе счисления | 1988 |

|

SU1633423A1 |

Изобретение относится к измерительной технике. Цель изобретения - повышение точности. Изобретение позволяет повысить точность измерения математического ожидания методом статистических испытаний. При этом повышение точности достигается адаптацией диапазона вспомогательного случайного процесса к математическому ожиданию измеряемого случайного сигнала с центрированием этого процесса на величину текущей оценки математического ожидания измеряемого случайного сигнала параллельно с использованием знакового метода оценивания среднего в зоне нечувствительности метода статистических испытаний. Интегратор содержит блок сравнения 1, блоки усреднения 2, 4, блок 3 масштабирования, блок умножения 5, блок 6 вычисления диапазона вспомогательного сигнала, аналоговые блоки 8, 9 памяти, блоки 10, 12 сложения, блок 11 вычитания, ключ 13, блок 14 знаковой оценки среднего, генератор 15 тактовых импульсов. 3 ил.

о о VI

о о

Јь

4cmAwu

Изобретение относится к области измерений, контроля и управления и может найти применение в информационно-измерительной технике, радиотехнике и приборостроении.

Цель изобретения - повышение точности.

Принцип действия интегратора заключается в следующем. Заданному отклонению б середины диапазона А генерируемого вспомогательного равномерно распределенного процесса, от математического ожидания измеряемого случайного сигнала, соответствует оптимальное значение А Aopt при котором погрешность стохастического интегрирования (усреднения) минимальна. Поэтому, используя центрирование вспомогательного процесса по текущей оценке математического ожидания измеряемого случайного сигнала, можно повысить точность стохастического интегрирования. Однако по мере уменьшения д соответственно будет уменьшаться Л Aopt и при некотором А Aopt близком к нулю процесс интегрирования практически остановится. Чтобы обеспечить интегрирование при малых значениях Арсогда текущие наблюдения не попадают в пределы A Aopt необходим учет этих наблюдений с помощью метода, не связанного с шириной диапазона А (например, метода знакового интегрирования). С этой целью в интеграторе одновременно реализованы оба метода усреднения: при попадании текущих значений измеряемого процесса в пределы диапазона они обрабатываются методом статистических испытаний, а при попадании вне предела указанного диапазона - знаковым методом; в качестве результирующего значения используется взвешенная сумма обоих типов оценок.

Эмпирическая зависимость между А и отклонением 6 получена экспериментальным путем и описывается регрессионным уравнением Aopt 0,27 + 5,6 6 - 1,54 .

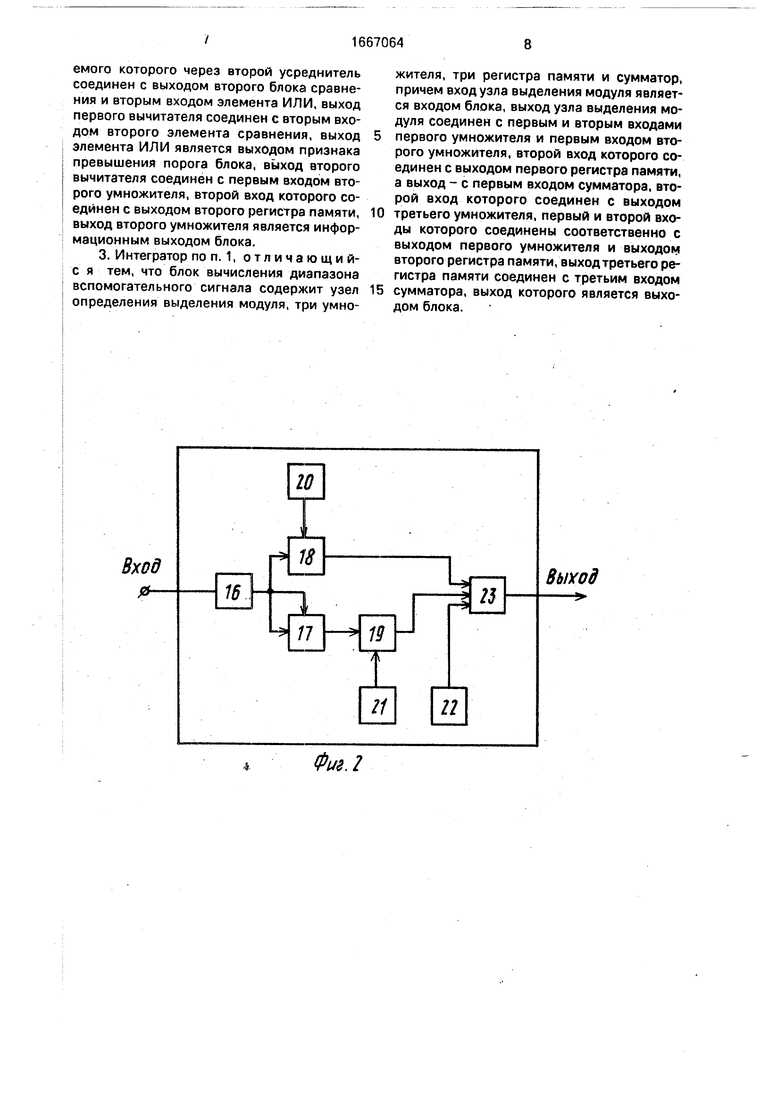

На фиг, 1 приведена структурная схема интегратора; на фиг. 2 - функциональная схема блока вычисления диапазона вспомогательного сигнала; на фиг. 3 - функциональная схема блока знаковой оценки среднего.

Интегратор содержит (фиг. 1)блок 1 сравнения, блок 2 усреднения, блок 3 масштабирования, блок4 усреднения, блок 5 умножения, блок 6 вычисления диапазона вспомогательного сигнала, генератор 7 шума, аналоговые блоки 8-9 памяти, блок 10 сложения, блок 11 вычитания, блок 12 сложения, ключ 13, блок 14 знаковой оценки среднего, генератор 15 тактовых импульсов.

Блок 6 (фиг. 2) содержит узел 16 определения абсолютного значения, умножители

17-19, регистры 20-22 памяти, сумматор 23, блок 14 (фиг. 3) содержит умножители 24,25, вычитатель 26, сумматор 27, элементы 28,29 сравнения, элемент ИЛИ 30, усреднители

31, 32, вычитатель 33, регистры 34, 35 памяти.

Интегратор работает следующим образом.

Измеряемый сигнал поступает одновре0 менно на вход ключа 13 и на вход блока 14. В случае, когда измеряемый сигнал rt в зоне диапазона А Aopt а логический сигнал ft с выхода блока 14 отсутствует, тем самым разрешая работу метода статистических ис5 пытаний и запрещая знаковый метод, It проходит через ключ 13 на вход блока 1 сравнения. При этом на другой вход блока 1 с выхода блока 10 сложения поступает равномерно распределенный в диапазоне

0 A Aopt/2 + Sti- Aopt/2+St центрированный на величину St случайный yt сигнал. На другой вход блока 10 сложения поступает напряжение St с выхода блока 9, который хранит текущую оценку математического ожидания

5 измеряемого сигнала. Блок 1 выполняет следующую логическую операцию

(0; rt yt х

U;r,yt

0 Логический сигнал х с выхода сравнивающего устройства 1 поступает на вход блока 2 усреднения, работающего по принципу усредняющего звена с постоянной времени П, где т - время скользящего интервала

5 усреднения измеряемого сигнала при условии, что Aopt на этом интервале остается практически неизменным.

Значение с выхода блока 2 усреднения поступает на первый вход блока 3 масштаби® рования, осуществляющего масштабирование усредненного на интервале rt значения измеряемого сигнала в соответствии с А Aopt .выходное значение которого поступает на второй вход блока 3 масштабирования с выхода блока 8. Напряжение с выхода блока 3 масштабирования равно иВЫхЗ (иВхЗ/иВых2тах - 0.5) Aopt. Напряжение с выхода блока 4 усреднения поступает

0 на вход блока 11 вычитания и на вход блока 9. На другой вход блока 11 вычитания поступает напряжение с выхода блока 9, равное значению текущей оценки St-1 на предыдущем участке интервала скользящего усреднения п. Напряжение с выхода блока 11 вычитания поступает на вход блока б вычитания.

Блок 6 работает, непосредственно реализуя вычисления в соответствии с указанным выражением.

5

Случай запрещения метода статистических испытаний и разрешения знакового метода наступает при условии I гч - St I Aopt 12. При этом на вход первый блока 1 через ключ 13 под управлением сигнала, вырабатываемого с выхода блока 14, поступает напряжение с выхода блока 9, равное величине центрирования St.

В блоке 14 элемент 28 сравнения выполняет следующую логическую операцию

/И;-Aopt

0;Aopt /2 + St n/t

Элемент 29 сравнения выполняет следующую логическую операцию

-Aopt /2 + St rt i.2-4

10; Aopt/2 + St rt

Напряжение с выхода умножителя 25, равное

U

вых25

Л. (л Г11 Г1

U/Lldt-Ј/L2dt, О I И 0И оI

является выходным напряжением блока 14, которое поступает на выход блока 14 и с него поступает на вход блока 12 сложения. В момент включения в блок 8 заносится начальное значение (возможно максимальное) А, а блок 9 обнуляется. Синхронно включается и генератор 15 тактовых импульсов, который выдает строго синхронизированную регулярную последовательность импульсов с периодом повторения, равным интервалу скользящего усреднения TI поступающих на синхровходы блоков 8 и 9.

Формула изобретения 1. Вероятностный интегратор, содержащий блок сравнения, два блока усреднения, блок масштабирования, два аналоговых блока памяти, первый блок сложения, блок вычитания, генератор шума, генератор тактовых импульсов, блок умножения, блок вычисления диапазона вспомогательного сигнала, причем выход Больше блока сравнения через первый блок усреднения соединен с информационным входом блока масштабирования, вход задания коэффициента масштабирования которого соединен с выходом первого аналогового блока памяти и первым входом первого блока умножения, второй вход и выход которого соответственно соединены с выходом генератора шума и первым входом блока сложения, выход которого соединен с первым входом блока сравнения, а второй вход блока сложения соединен с выходом второго аналогового блока памяти и входом вычитаемого блока вычитания, вход уменьшаемого которого соединен с информационным входом второго

аналогового блока памяти и выходом второго блока усреднения, являющимся выходом интегратора, выход генератора тактовых импульсов соединен с синхровходами пер- 5 вого и второго аналоговых блоков памяти, вход обнуления второго аналогового блока памяти и вход задания начального значения первого аналогового блока памяти являются соответственно входами обнуления и за- 10 дания начального значения диапазона вспомогательного сигнала интегратора, выход блока вычитания соединен с входом блока вычисления диапазона вспомогательного сигнала, выход которого соединен с 5 информационным входом первого аналогового блока памяти, отличающийся тем, что, с целью повышения точности, в него дополнительно введены второй блок сложения, блок знаковой оценки среднего и 0 ключ, причем первый информационный вход ключа соединен с информационным входом блока знаковой оценки среднего и является информационным входом интегратора, вход задания порога и информацион- 5 ный выход блока знаковой оценки среднего соединены соответственно с выходом первого аналогового блока памяти и первым входом второго блока сложения, второй вход и выход которого соединены соответ- 0 ственно с выходом блока масштабирования и входом второго блока усреднения, выход второго аналогового блока памяти соединен с вторым информационным входом ключа и входом опорного сигнала блока знаковой 5 оценки среднего, выход признака превышения порога которого соединен с управляющим входом ключа, выход которого соединен с вторым входом блока сравнения.

0

5

жителя, три регистра памяти и сумматор, причем вход узла выделения модуля является входом блока, выход узла выделения модуля соединен с первым и вторым входами первого умножителя и первым входом второго умножителя, второй вход которого соединен с выходом первого регистра памяти, а выход - с первым входом сумматора, второй вход которого соединен с выходом третьего умножителя, первый и второй входы которого соединены соответственно с выходом первого умножителя и выходом второго регистра памяти, выход третьего регистра памяти соединен с третьим входом сумматора, выход которого является выходом блока.

VO

«NI

т

Ч

И

Ј2

Г

J

| Вероятностный интегратор | 1986 |

|

SU1328814A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-30—Публикация

1989-06-23—Подача