о ю

Изобретение относится к вычислительной технике и предназначено для аппаратурной реализации устройств вычисления функции arctg(y/x) в быстродействующих цифровых специализированных вычислительных устройствах и системах,

Целью изобретения является повышение быстродействия за счет работы с фиксированной запятой и повышение точности за счет аппроксимации коэффициентами параболической аппроксимации.

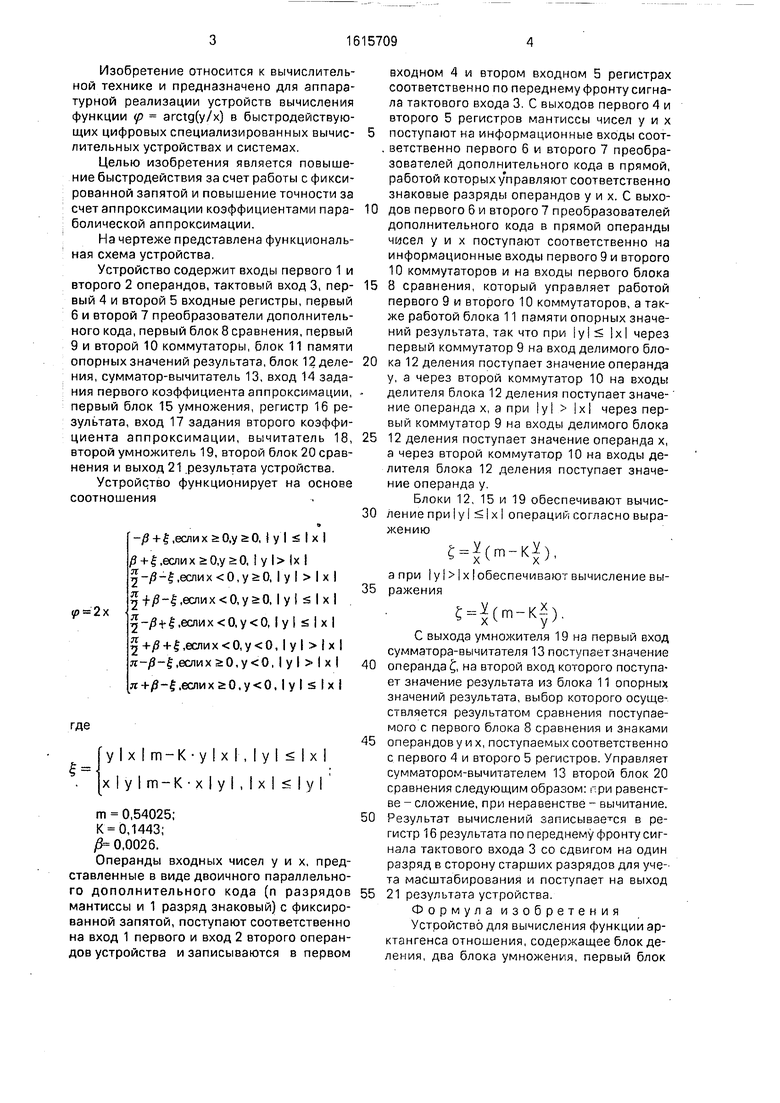

На чертеже представлена функциональная схема устройства,

Устройство содержит входы первого 1 и второго 2 операндов, тактовый вход 3, первый 4 и второй 5 входные регистры, первый 6 и второй 7 преобразователи дополнительного кода, первый блок 8 сравнения, первый 9 и второй 10 коммутаторы, блок 11 памяти опорных значений результата, блок 12 деления, сумматор-вычитатель 13, вход 14 задания первого коэффициента аппроксимации, первый блок 15 умножения, регистр 16 результата, вход 17 задания второго коэффициента аппроксимации, вычитатель 18, второй умножитель 19, второй блок 20 сравнения и выход 21 .результата устройства.

Устройство функционирует на основе соотношения

2х

-/3 + 1 .если X & О.у г О, у I I X I

/ + § .еслиX О.у О, I у I |х I 2-/3-.еспих 0,угО. |у I |х I

уЗ-§,еспих 0.уаО. |у I s 1x1 ,еслих 0., |у1 s 1x1

.еслих 0,, |у I |х я-Д-.еслих sO,,

.если X 2:0.,lylslxi

где

ylxlm-K-ylxl, х|у1т-К-х|у|,

m 0,54025;

К 0,1443;

0,0026.

Операнды входных чисел у и х, представленные в виде двоичного параллельного дополнительного кода (п разрядов мантиссы и 1 разряд знаковый) с фиксированной запятой, поступают соответственно на вход 1 первого и вход 2 второго операндов устройства и записываются в первом

входном 4 и втором входном 5 регистрах соответственно по переднему фронту сигнала тактового входа 3, С выходов первого 4 и второго 5 регистров мантиссы чисел у и х

5 поступают на информационные входы соот- . ветственно первого 6 и второго 7 преобразователей дополнительного кода в прямой, работой которыху правляют соответственно знаковые разряды операндов у и х. С выхо0 дов первого 6 и второго 7 преобразователей дополнительного кода в прямой операнды чисел у и X поступают соответственно на информационные входы первого 9 и второго 10 коммутаторов и на входы первого блока

5 8 сравнения, который управляет работой первого 9 и второго 10 коммутаторов, а также работой блока 11 памяти опорных значений результата, так что при |у| 1x1 через первый коммутатор 9 на вход делимого бло0 ка 12 деления поступает значение операнда у, а через второй коммутатор 10 на входы делителя блока 12 деления поступает значе- ние операнда х, а при iyl |х| через первый коммутатор 9 на входы делимого блока

5 12 деления поступает значение операнда х, а через второй коммутатор 10 на входы делителя блока 12 деления поступает значение операнда у.

Блоки 12, 15 и 19 обеспечивают вычис0 ление при I у I | х i операций согласно выражению

t |(m-K).

а при I у I IXI обеспечивают вычисление вы- 5 ражения

С-(т-К).

С выхода умножителя 19 на первый вход сумматора-вычитателя 13 поступает значение

0 операнда , на второй вход которого поступает значение результата из блока 11 опорных значений результата, выбор которого осуществляется результатом сравнения поступае- мого с первого блока 8 сравнения и знаками

5 операндов у и х, поступаемых соответственно с первого 4 и второго 5 регистров. Управляет сумматором-вычитателем 13 второй блок 20 сравнения следующим образом: при равенстве - сложение, при неравенстве - вычитание.

0 Результат вычислений записываемся в регистр 16 результата по переднему фронту сигнала тактового входа 3 со сдвигом на один разряд в сторону старших разрядов для учета масштабирования и поступает на выход

5 21 результата устройства.

Формула изобретения Устройство для вычисления функции арктангенса отношения, содержащее блок деления, два блока умножения, первый блок

ления, два блока умножения, первый блок сравнения, два коммутатора, вычитатель, сум- матор-вычитатель, причем выходы первого и второго коммутаторов соединены с входами соответственно делимого и делителя блока де- ления, вход первого коэффициента аппроксимации устройства соединен с входом первого сомножителя первого умножителя, вход второго коэффициента аппроксимации устройства соединен с входом уменьшаемого вычитателя, выход которого соединен с входом первого сомножителя второго умножителя, вход второго сомножителя которого соединен с выходом блока деления, выход второго умножителя соединен с пер- вым информационным входом сумматора - вычитателя, отличающееся тем, что, с целью повышения быстродействия за счет работы с фиксированной точкой и повышения точности за счет аппроксимации коаффици- ентами параболической аппроксимации, в него дополнительно введены блок памяти опорных значений результата, второй блок сравнения и регистр результата,.причем входы первого и второго операндов устройства соединены с входами соответственно первого и второго операндов первого блока сравнения, вход первого операнда устройства

соединен- с первыми информационными входами первого и второго коммутаторов, вход второго операнда устройства соединен с вторыми информационными входами первого и второго коммутаторов, управляющие входы которых объединены и соединены с выходом первого блока сравнения, входы знаковых разрядов первого и второго операндов устройства и выход первого блока сравнения соединены с адресным входом блока памяти опорных значений результата, выход которого соединен с вторым информационным входом сумматора-вычитателя, выход которого со сдвигом на один разряд в сторону.старших разрядов соединен с информационным входом регистра результата, вход выбора операции сумматора-вычитателя соединен с выходом второго блока сравнения, входы первого и второго операндов которого соединены с входами знаковых разрядов первого и второго операндов устройства соответственно, тактовый вход устройства соединен с синхронизирующим входом регистра результата, выход которого соединен с одноименным выходом устройства, выход блока деления соединен с входом второго сомножителя первого умножителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство вычисления функции арктангенс отношения | 1988 |

|

SU1585793A1 |

| Устройство для вычисления модуля и аргумента вектора | 1986 |

|

SU1403063A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| Устройство для деления | 1985 |

|

SU1283752A1 |

| Устройство для вычисления функций Z @ = @ @ @ / @ и Z @ = @ @ @ / @ | 1988 |

|

SU1539771A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1619300A1 |

| Вычислительное устройство | 1989 |

|

SU1691837A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Устройство для контроля величины методической ошибки в системах обработки информации | 1988 |

|

SU1552209A1 |

Изобретение относится к вычислительной технике и предназначено для вычисления функции φ=ARCTG (Y/X) в быстродействующих цифровых специализированных вычислительных устройствах и системах. Целью изобретения является повышение быстродействия за счет работы с фиксированной точкой и повышение точности за счет аппроксимации коэффициентами параболической аппроксимации. Устройство содержит входы 1 первого и 2 второго операндов, тактовый вход 3, первый 4, второй 5 входные регистры, первый 6 и второй 7 преобразователи дополнительного кода в прямой, первый блок сравнения 8, первый 9 и второй 10 коммутаторы, блок 11 памяти опорных значений результата, блок деления 12, сумматор - вычитатель 13, вход задания первого коэффициента аппроксимации 14, первый блок умножения 15, регистр результата 16, вход задания второго коэффициента аппроксимации 17, вычислитель 18, второй блок умножения 19, второй блок сравнения 20, выход результата устройства 21. 1 ил.

| Устройство для вычисления функции арктангенса | 1984 |

|

SU1221651A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления функции арктангенса | 1985 |

|

SU1273920A1 |

Авторы

Даты

1990-12-23—Публикация

1988-09-26—Подача