Изобретение относится к вычислительной технике и может быть использовано в системах ввода-вывода информации универсальных ЭВМ.

Цель изобретения - упрощение устройства и повышение быстродействия за счет организации поиска свободного подканала путем анализа его управляющей последовательности в промежутках между запросами параллельно с работой центрального процессора, что повышает производительность системы ввода-вывода и эффективность ее работы.

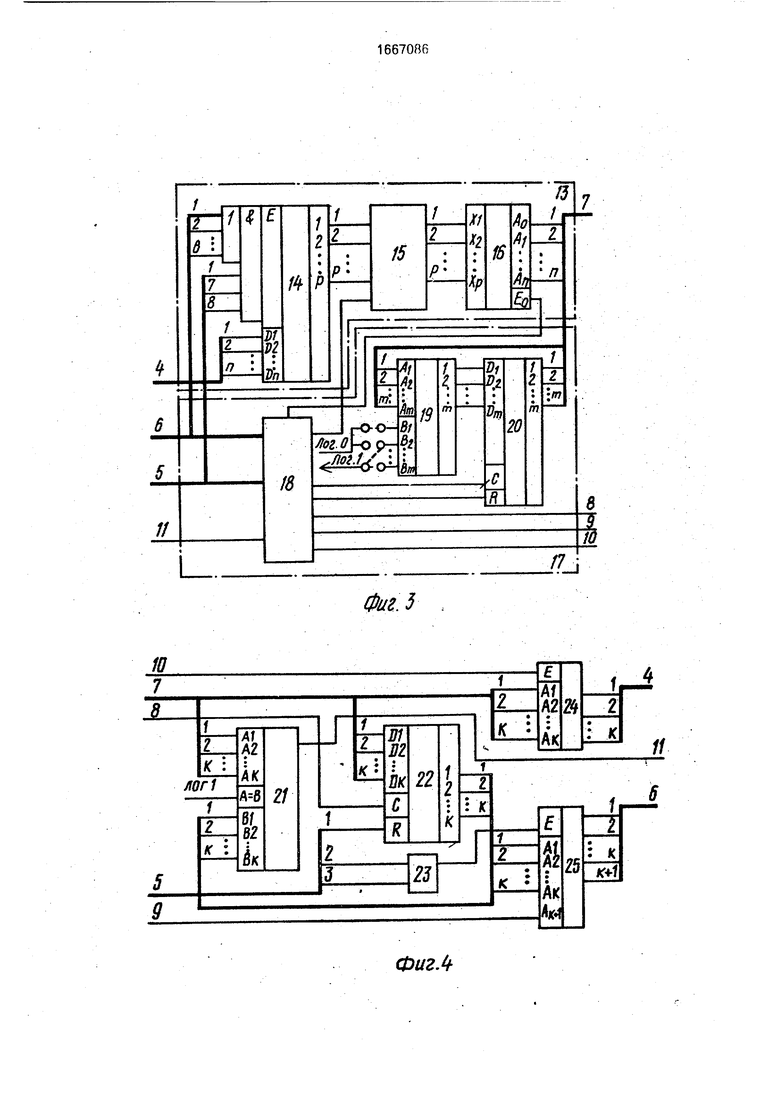

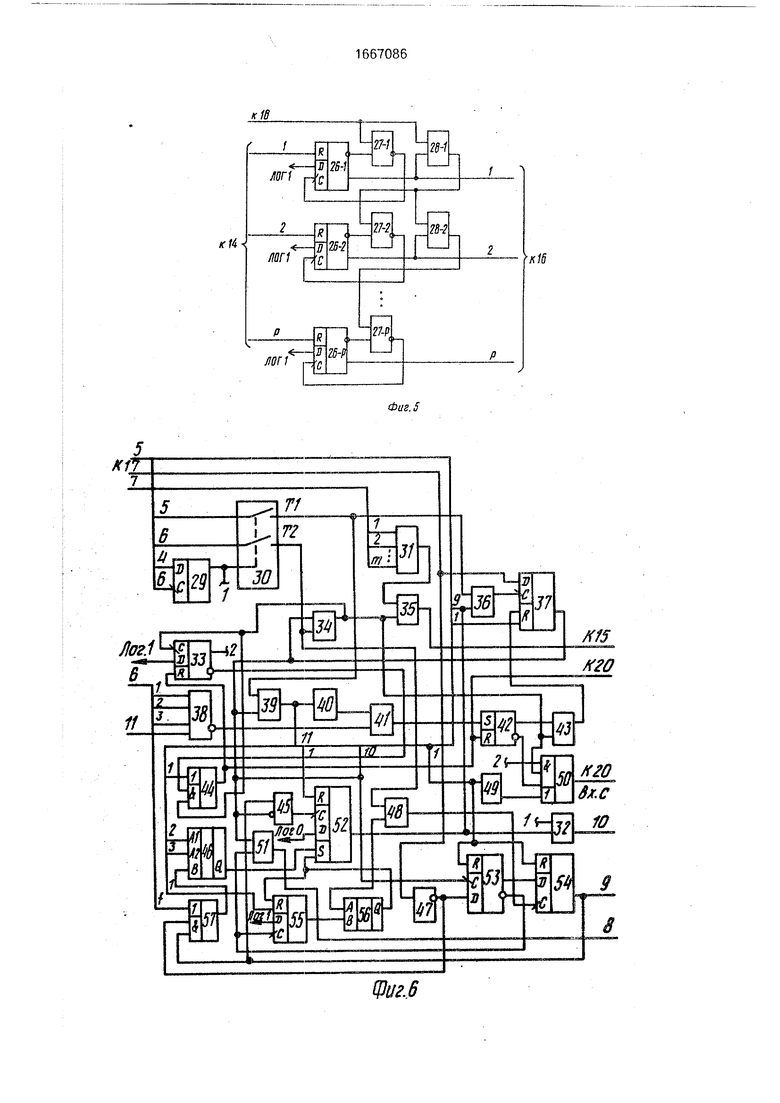

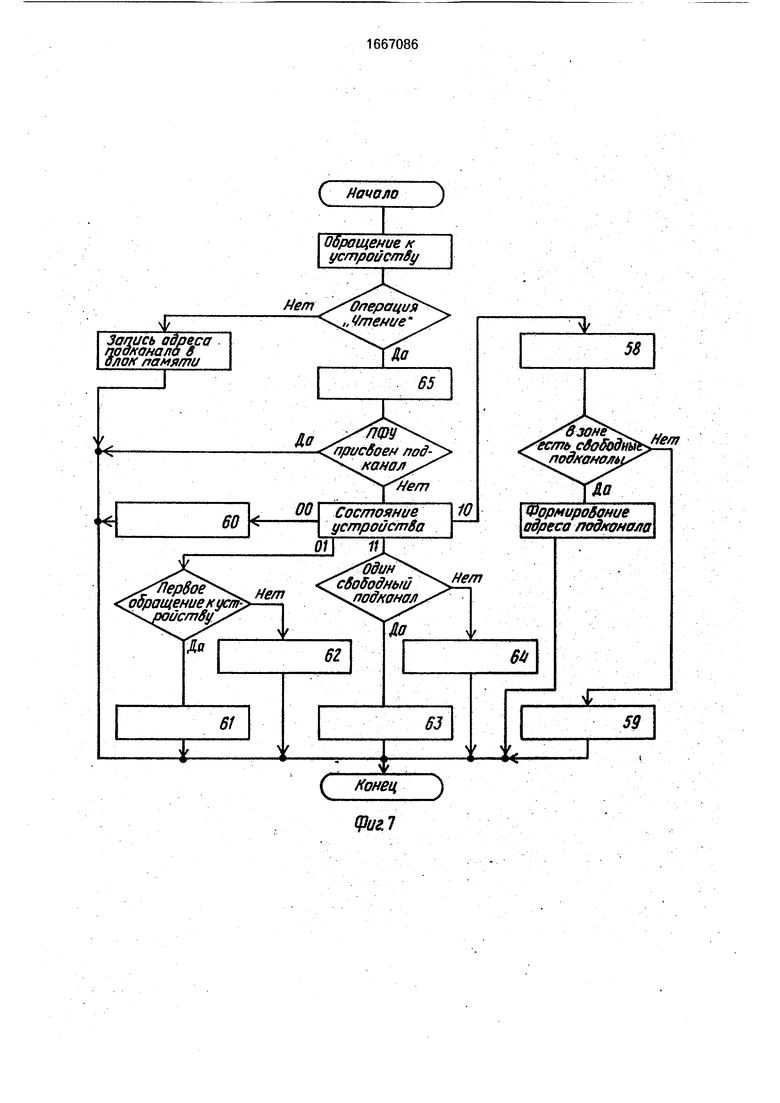

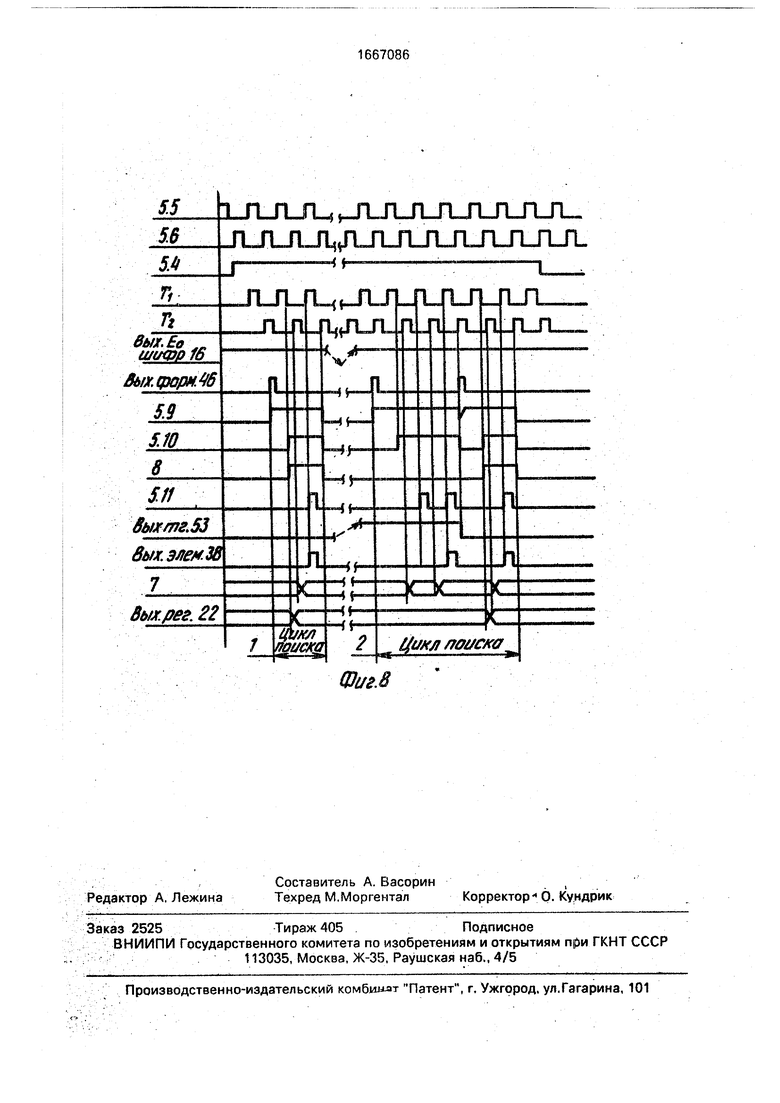

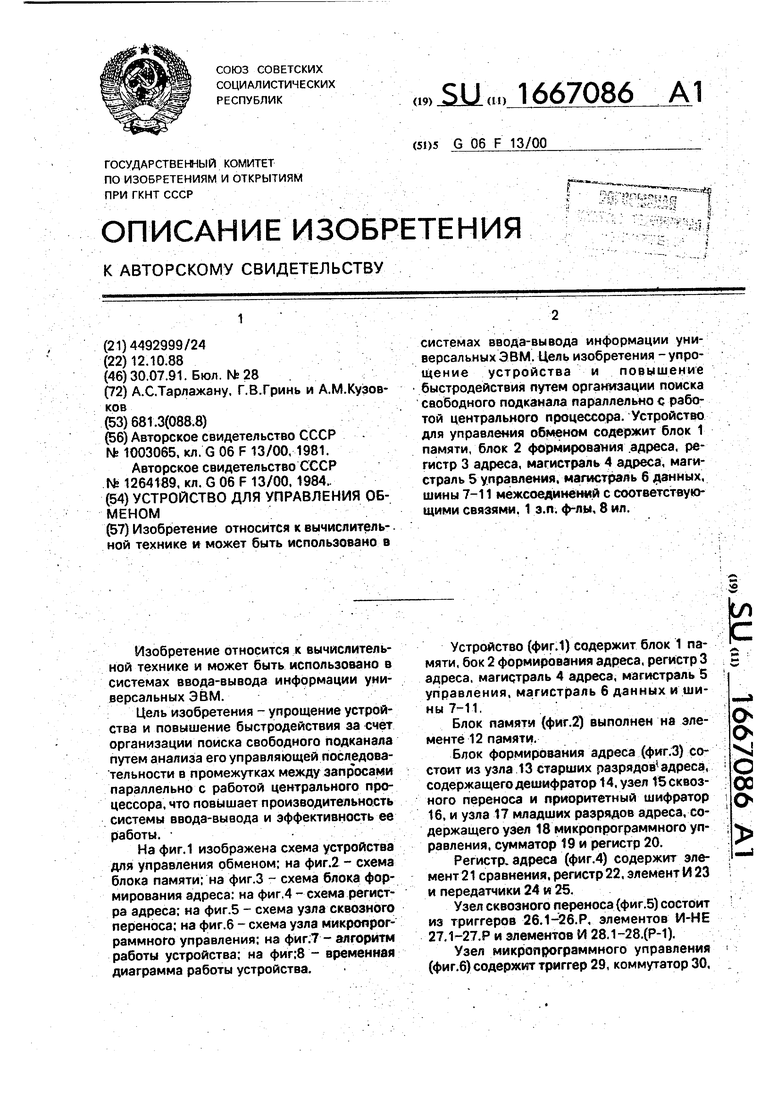

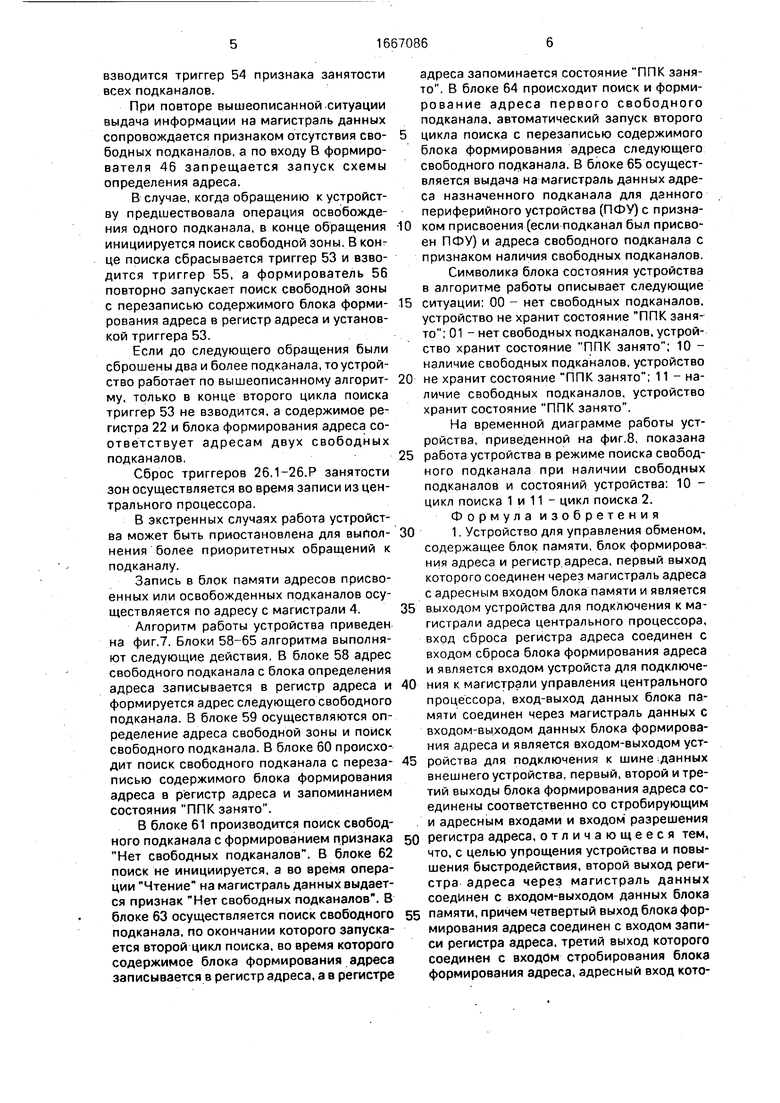

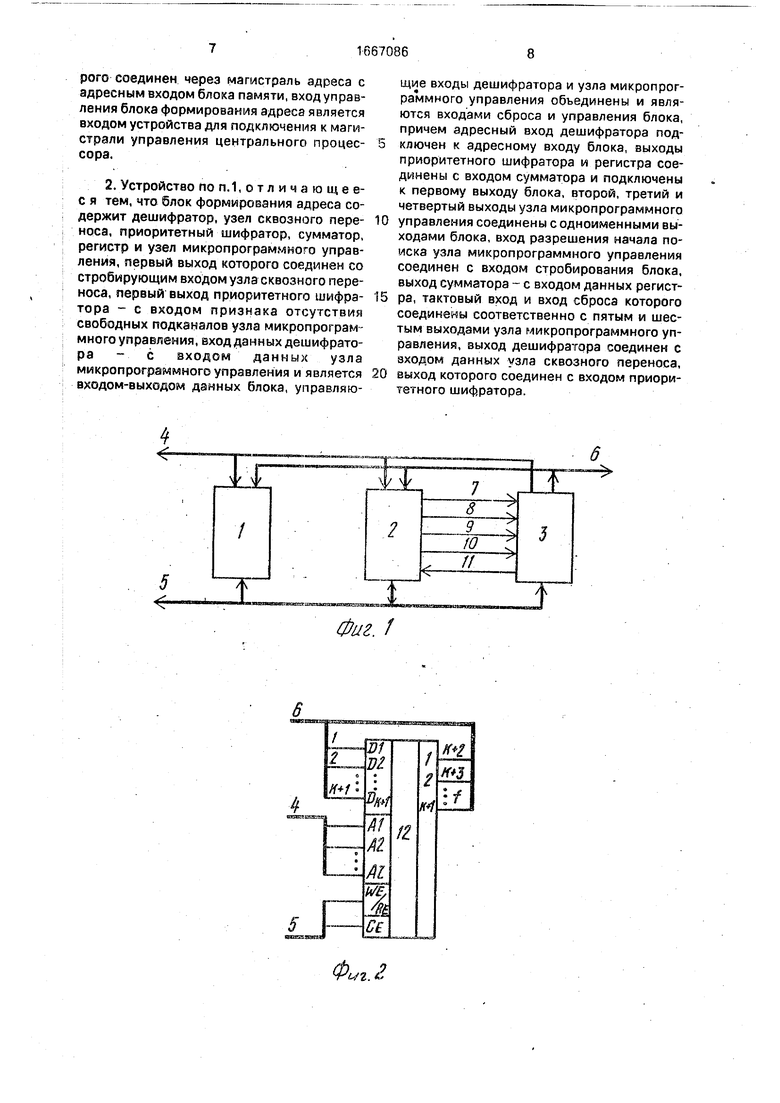

На фиг.1 изображена схема устройства для управления обменом; на фиг.2 - схема блока памяти; на фиг.З - схема блока формирования адреса: на фиг.4 - схема регистра адреса; на фиг.5 - схема узла сквозного переноса; на фиг.6 - схема узла микропрограммного управления; на фиг.7 - алгоритм работы устройства; на фиг;8 - временная диаграмма работы устройства.

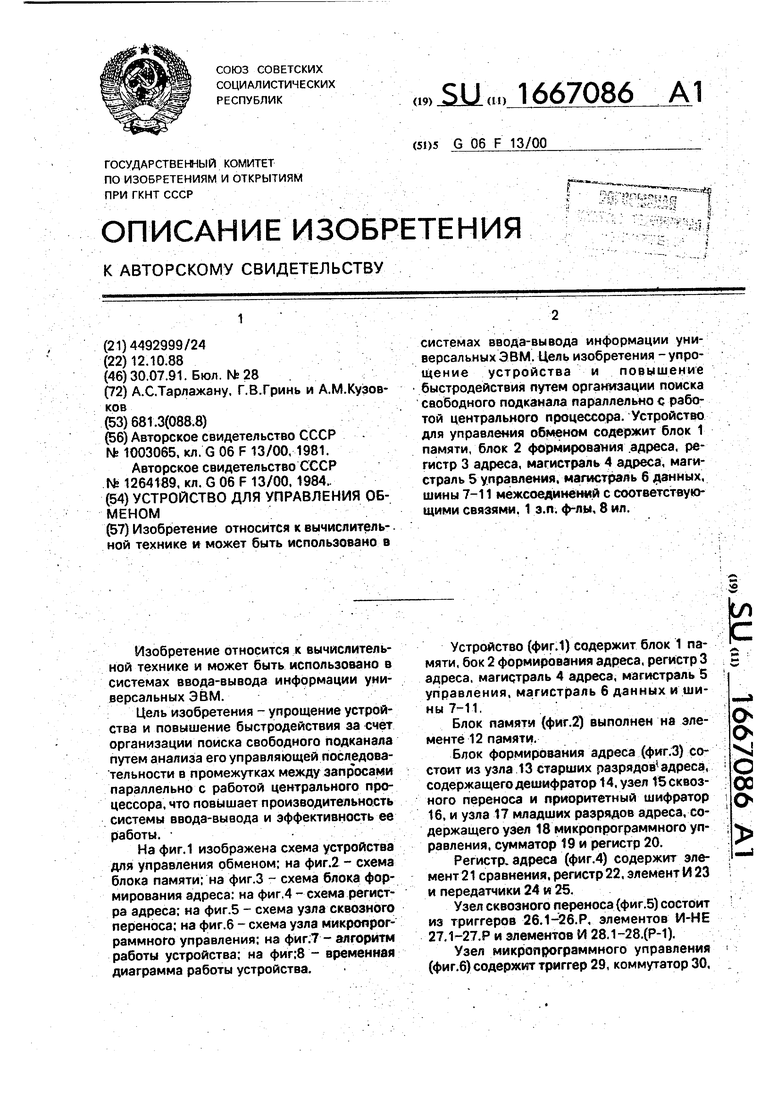

Устройство (фиг.1) содержит блок 1 памяти, бок 2 формирования адреса, регистр 3 адреса, магистраль 4 адреса, магистраль 5 управления, магистраль 6 данных и шины 7-11.

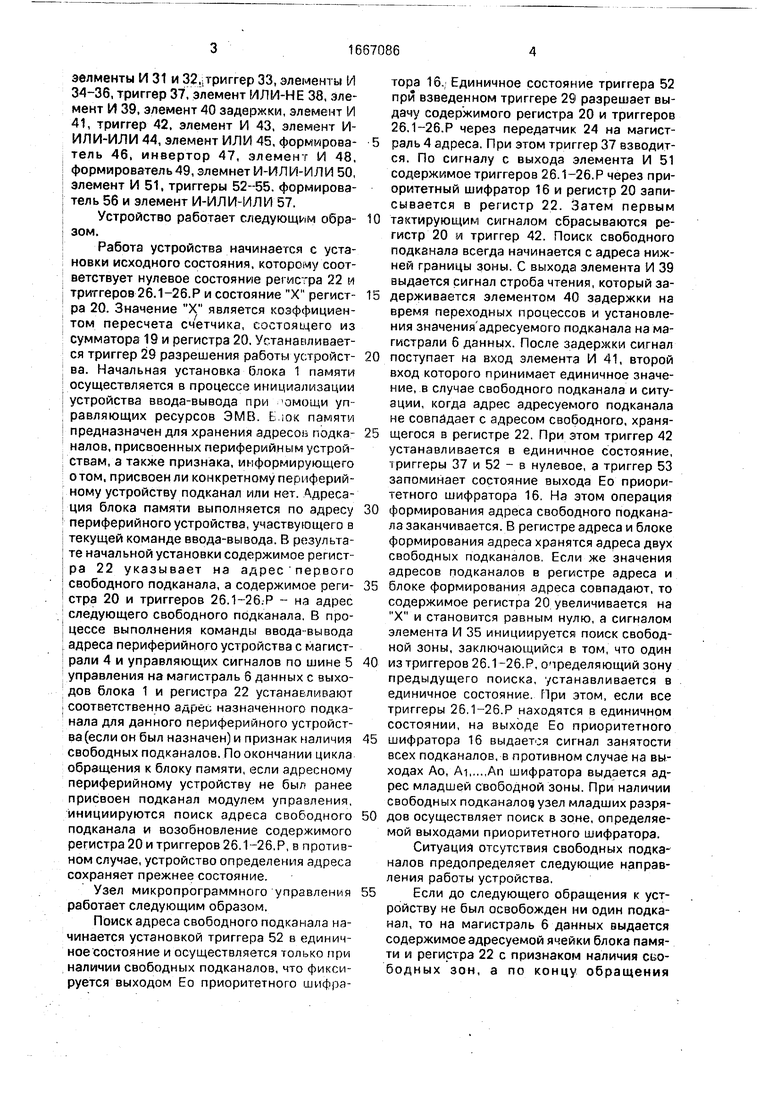

Блок памяти (фиг.2) выполнен на элементе 12 памяти.

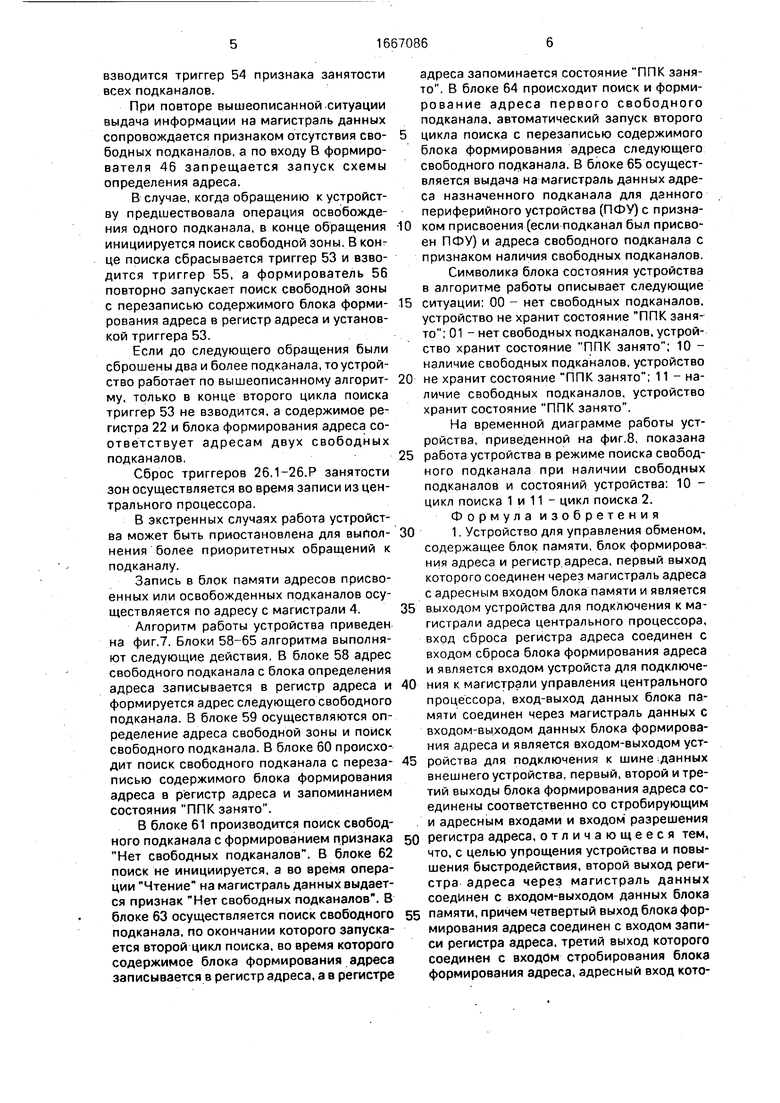

Блок формирования адреса (фиг.З) состоит из узла 13 старших разрядов адреса, содержащего дешифратор 14, узел сквозного переноса и приоритетный шифратор 16, и узла 17 младших разрядов адреса, содержащего узел 18 микропрограммного управления, сумматор 19 и регистр 20.

Регистр, адреса (фиг.4) содержит элемент 21 сравнения, регистр 22, элемент И 23 и передатчики 24 и 25.

Узел сквозного переноса (фиг.5) состоит из триггеров 26.1-26.Р, элементов И-НЕ 27.1-27.Р и элементов И 28.1-28.(Р-1).

Узел микропрограммного управления (фиг.6) содержит триггер 29, коммутатор 30,

V

Ј

о

о

о

ОС

о

эелменты И 31 и 32,.триггер 33, элементы И 34-36, триггер 37, элемент ИЛИ-НЕ 38, элемент И 39, элемент 40 задержки, элемент И 41, триггер 42, элемент И 43, элемент И- ИЛИ-ИЛИ 44, элемент ИЛИ 45, формирователь 46, инвертор 47, элемент И 48, формирователь 49, элемнетИ-ИЛИ-ИЛИ 50, элемент И 51, триггеры 52-55. формирователь 56 и элемент И-ИЛИ-ИЛИ 57.

Устройство работает следующим образом.

Работа устройства начинается с установки исходного состояния, которому соответствует нулевое состояние регистра 22 и триггеров 26.1-26.Р и состояние X регистра 20. Значение X является коэффициентом пересчета счетчика, состоящего из сумматора 19 и регистра 20. Устанавливается триггер 29 разрешения работы устройства. Начальная установка блока 1 памяти осуществляется в процессе инициализации устройства ввода-вывода при омощи управляющих ресурсов ЭМВ. L ,ок памяти предназначен для хранения адресов подканалов, присвоенных периферийным устройствам, а также признака, информирующего отом, присвоен ли конкретному периферийному устройству подканал или нет. Адресация блока памяти выполняется по адресу периферийного устройства, участвующего в текущей команде ввода-вывода. В результате начальной установки содержимое регист ра 22 указывает на адрес первого свободного подканала, а содержимое регистра 20 и триггеров 26.1-26.Р - на адрес следующего свободного подканала. В процессе выполнения команды ввода-вывода адреса периферийного устройства с магистрали 4 и управляющих сигналов по шине 5 управления на магистраль 6 данных с выходов блока 1 и регистра 22 устанавливают соответственно адреи назначенного подканала для данного периферийного устройст- ва(если он был назначен) и признак наличия свободных подканалов. По окончании цикла обращения к блоку памяти, если адресному периферийному устройству не был ранее присвоен подканал модулем управления, инициируются поиск адреса свободного подканала и возобновление содержимого регистра 20 и триггеров 26.1-26.Р, в противном случае, устройство определения адреса сохраняет прежнее состояние.

Узел микропрограммного управления работает следующим образом.

Поиск адреса свободного подканала начинается установкой триггера 52 в единичное состояние и осуществляется только при наличии свободных подканалов, что фиксируется выходом Ео приоритетного шифратора 16. Единичное состояние триггера 52 при взведенном триггере 29 разрешает выдачу содержимого регистра 20 и триггеров 26.1-26.Р через передатчик 24 на магист- раль 4 адреса. При этом триггер 37 взводится. По сигналу с выхода элемента И 51 содержимое триггеров 26.1-26.Р через приоритетный шифратор 16 и регистр 20 записывается в регистр 22. Затем первым

0 тактирующим сигналом сбрасываются регистр 20 и триггер 42. Поиск свободного подканала всегда начинается с адреса нижней границы зоны. С выхода элемента И 39 выдается сигнал строба чтения, который за5 держивается элементом 40 задержки на время переходных процессов и установления значения адресуемого подканала на магистрали 6 данных. После задержки сигнал

0 поступает на вход элемента И 41, второй вход которого принимает единичное значение, в случае свободного подканала и ситуации, когда адрес адресуемого подканала не совпадает с адресом свободного, храня5 щегося в регистре 22. При этом триггер 42 устанавливается в единичное состояние, триггеры 37 и 52 - в нулевое, а триггер 53 запоминает состояние выхода Ео приоритетного шифратора 16. На этом операция

0 формирования адреса свободного подканала заканчивается. В регистре адреса и блоке формирования адреса хранятся адреса двух свободных подканалов. Если же значения адресов подканалов в регистре адреса и

5 блоке формирования адреса совпадают, то содержимое регистра 20 увеличивается на X и становится равным нулю, а сигналом элемента И 35 инициируется поиск свободной зоны, заключающийся в том, что один

0 изтриггеров 26.1-26.Р, определяющий зону предыдущего поиска, устанавливается в единичное состояние. При этом, если все триггеры 26.1-26.Р находятся в единичном состоянии, на выходе Ео приоритетного

5 шифратора 16 выдается сигнал занятости всех подканалов, в противном случае на выходах АО, AIAn шифратора выдается адрес младшей свободной зоны. При наличии свободных подканалов узел младших рэзря0 дов осуществляет поиск в зоне, определяемой выходами приоритетного шифратора.

Ситуация отсутствия свободных подканалов предопределяет следующие направления работы устройства.

5Если до следующего обращения к устройству не был освобожден ни один подканал, то на магистраль 6 данных выдается содержимое адресуемой ячейки блока памяти и регистра 22 с признаком наличия свободных зон, а по концу обращения

взводится триггер 54 признака занятости всех подканалов.

При повторе вышеописанной ситуации выдача информации на магистраль данных сопровождается признаком отсутствия свободных подканалов, а по входу В формирователя 46 запрещается запуск схемы определения адреса.

В случае, когда обращению к устройству предшествовала операция освобождения одного подканала, в конце обращения инициируется поиск свободной зоны. В конце поиска сбрасывается триггер 53 и взводится триггер 55, а формирователь 56 повторно запускает поиск свободной зоны с перезаписью содержимого блока формирования адреса в регистр адреса и установкой триггера 53.

Если до следующего обращения были сброшены два и более подканала, то устройство работает по вышеописанному алгоритму, только в конце второго цикла поиска триггер 53 не взводится, а содержимое регистра 22 и блока формирования адреса соответствует адресам двух свободных подканалов.

Сброс триггеров 26.1-26.Р занятости зон осуществляется во время записи из центрального процессора.

В экстренных случаях работа устройства может быть приостановлена для выполнения более приоритетных обращений к подканалу.

Запись в блок памяти адресов присвоенных или освобожденных подканалов осуществляется по адресу с магистрали 4.

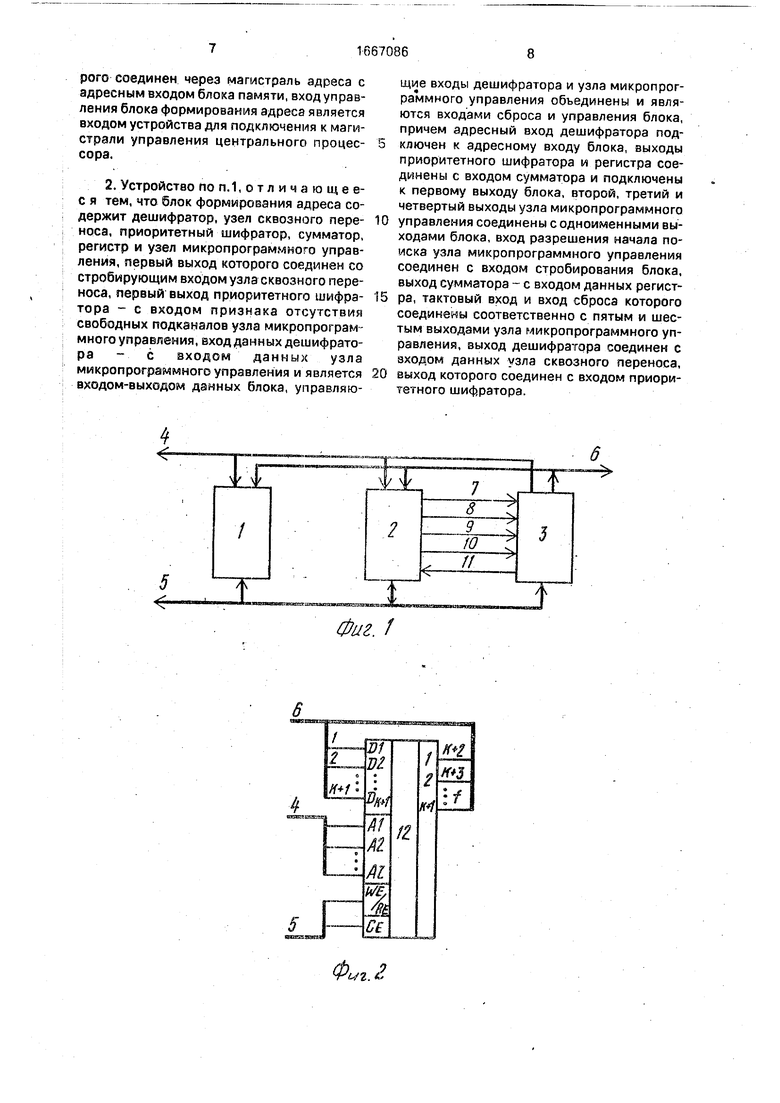

Алгоритм работы устройства приведен на фиг.7. Блоки 58-65 алгоритма выполняют следующие действия, В блоке 58 адрес свободного подканала с блока определения адреса записывается в регистр адреса и формируется адрес следующего свободного подканала. В блоке 59 осуществляются определение адреса свободной зоны и поиск свободного подканала. В блоке 60 происходит поиск свободного подканала с перезаписью содержимого блока формирования адреса в регистр адреса и запоминанием состояния ППК занято.

В блоке 61 производится поиск свободного подканала с формированием признака Нет свободных подканалов. В блоке 62 поиск не инициируется, а во время операции Чтение на магистраль данных выдается признак Нет свободных подканалов. В блоке 63 осуществляется поиск свободного подканала, по окончании которого запускается второй цикл поиска, во время которого содержимое блока формирования адреса записывается в регистр адреса, а в регистре

адреса запоминается состояние ППК занято. В блоке 64 происходит поиск и форми- рование адреса первого свободного подканала, автоматический запуск второго

цикла поиска с перезаписью содержимого блока формирования адреса следующего свободного подканала. В блоке 65 осуществляется выдача на магистраль данных адреса назначенного подканала для данного периферийного устройства (ПФУ) с призна0 ком присвоения (если подканал был присвоен ПФУ) и адреса свободного подканала с признаком наличия свободных подканалов. Символика блока состояния устройства в алгоритме работы описывает следующие

5 ситуации: 00 - нет свободных подканалов, устройство не хранит состояние ППК занято : 01 - нет свободных подканалов, устройство хранит состояние ППК занято ; 10 - наличие свободных подканалов, устройство

0 не хранит состояние ППК занято : 11 - наличие свободных подканалов, устройство хранит состояние ППК занято.

На временной диаграмме работы устройства, приведенной на фиг.8, показана

5 работа устройства в режиме поиска свободного подканала при наличии свободных подканалов и состояний устройства: 10 - цикл поиска 1 и 11 - цикл поиска 2. Формула изобретения

01. Устройство для управления обменом,

содержащее блок памяти, блок формирования адреса и регистр адреса, первый выход которого соединен через магистраль адреса с адресным входом блока памяти и является

5 выходом устройства для подключения к магистрали адреса центрального процессора. вход сброса регистра адреса соединен с входом сброса блока формирования адреса и является входом устройста для подключе0 ния к магистрали управления центрального процессора, вход-выход данных блока памяти соединен через магистраль данных с входом-выходом данных блока формирования адреса и является входом-выходом уст5 ройства для подключения к шине данных внешнего устройства, первый, второй и третий выходы блока формирования адреса соединены соответственно со стробирующим и адресным входами и входом разрешения

0 регистра адреса, отличающееся тем, что, с целью упрощения устройства и повышения быстродействия, второй выход регистра адреса через магистраль данных соединен с входом-выходом данных блока

5 памяти, причем четвертый выход блока формирования адреса соединен с входом записи регистра адреса, третий выход которого соединен с входом стробирования блока формирования адреса, адресный вход которого соединен через магистраль адреса с адресным входом блока памяти, вход управления блока формирования адреса является входом устройства для подключения к магистрали управления центрального процес- сора.

2. Устройство по п.1, о т л и ч а ю щ е е- с я тем. что блок формирования адреса содержит дешифратор, узел сквозного пере- носа, приоритетный шифратор, сумматор, регистр и узел микропрограммного управления, первый выход которого соединен со стробирующим входом узла сквозного переноса, первый выход приоритетного шифра- тора - с входом признака отсутствия свободных подканалов узла микропрограммного управления, вход данных дешифратора - с входом данных узла микропрограммного управления и является входом-выходом данных блока, управляющие входы дешифратора и узла микропрограммного управления объединены и являются входами сброса и управления блока, причем адресный вход дешифратора подключен к адресному входу блока, выходы приоритетного шифратора и регистра соединены с входом сумматора и подключены к первому выходу блока, второй, третий и четвертый выходы узла микропрограммного управления соединены с одноименными выходами блока, вход разрешения начала поиска узла микропрограммного управления соединен с входом стробирования блока, выход сумматора - с входом данных регистра, тактовый вход и вход сброса которого соединены соответственно с пятым и шестым выходами узла микропрограммного управления, выход дешифратора соединен с входом данных узла сквозного переноса, выход которого соединен с входом приоритетного шифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для распределения подканалов | 1981 |

|

SU1003065A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| Устройство для сопряжения каналов ввода-вывода с внешними устройствами | 1985 |

|

SU1277128A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1985 |

|

SU1305698A1 |

| Устройство для назначения подканалов | 1984 |

|

SU1264189A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах ввода-вывода информации универсальных ЭВМ. Цель изобретения - упрощение устройства и повышение быстродействия за счет организации поиска свободного подканала параллельно с работой центрального процессора. Устройство для управления обменом содержит блок памяти 1, блок 2 формирования адреса, регистр 3 адреса, магистраль 4 адреса, магистраль 5 управления, магистраль 6 данных, шины 7 - 11 межсоединений с соответствующими связями. 1 з.п. ф-лы, 8 ил.

Фиг. 2

IN

О...1ЭОП

Na

jk...3fc ж:

IS

CjU

fv

°

4 -feЈ2

NO N3

isa-

f

l

i

S,

rn

Й

IS

сч

00

п

п

5

гг,

Хд. . .

rs

is

Ј2

I

о

.

.- щ

-1

a

CT)

-j

о

vS

rs

Э-

гч

N

«о

is

- I

tv

Oa

CJ|

Щи г. 6

фиг.1

Фиг.8

| Устройство для распределения подканалов | 1981 |

|

SU1003065A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Устройство для назначения подканалов | 1984 |

|

SU1264189A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1991-07-30—Публикация

1988-10-12—Подача