о о XI

СА

СЛ

Изобретение относится к радиотехнике, в частности к радиоэлектронным устройствам, обеспечивающим управление каналообразующей радиоаппаратурой на расстоянии.

Цель изобретения - повышение функциональной надежности и достоверности принимаемой информации.

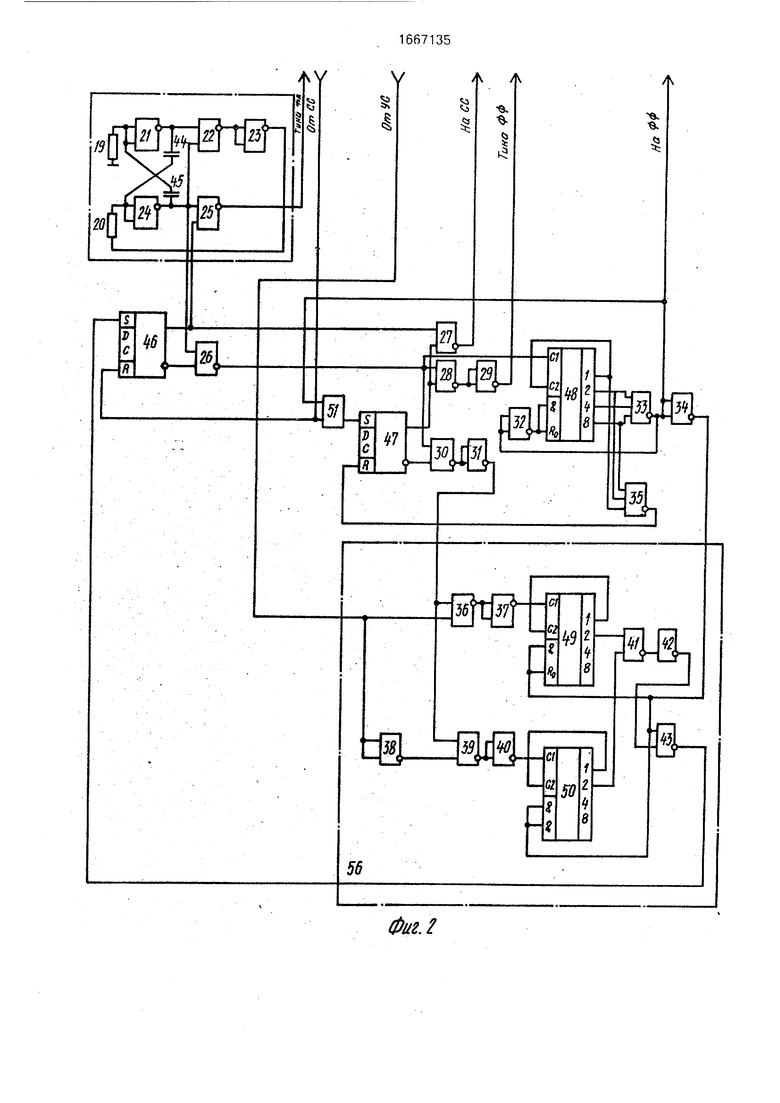

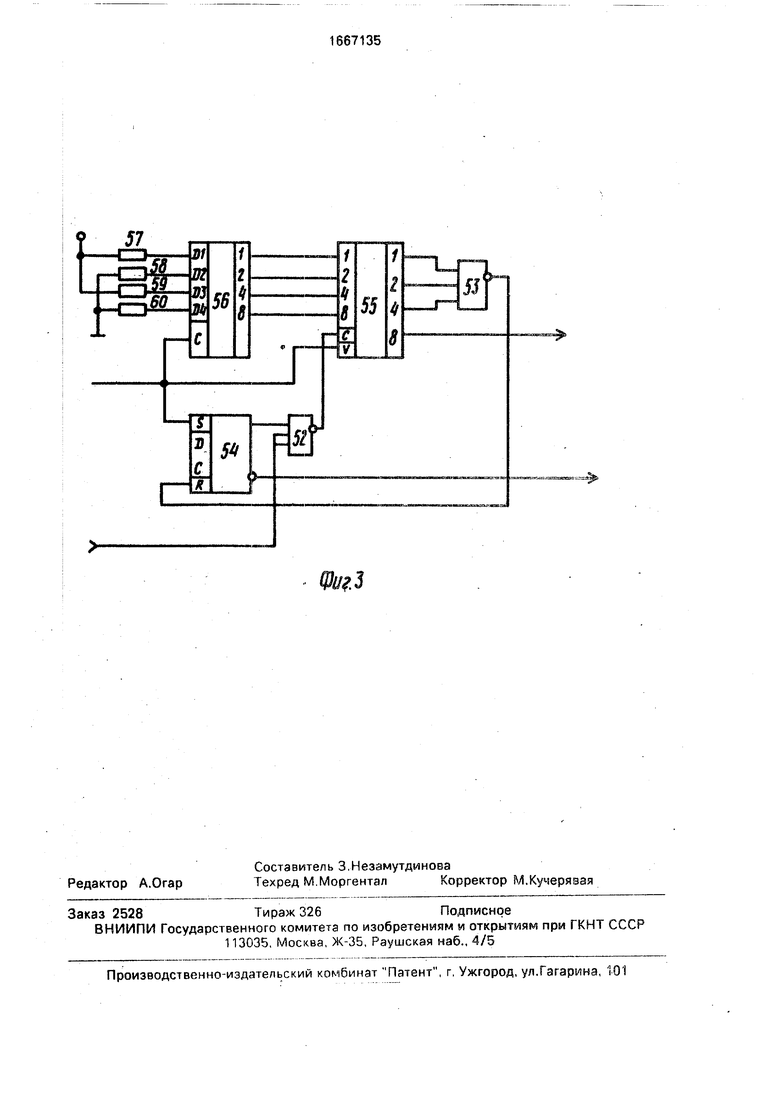

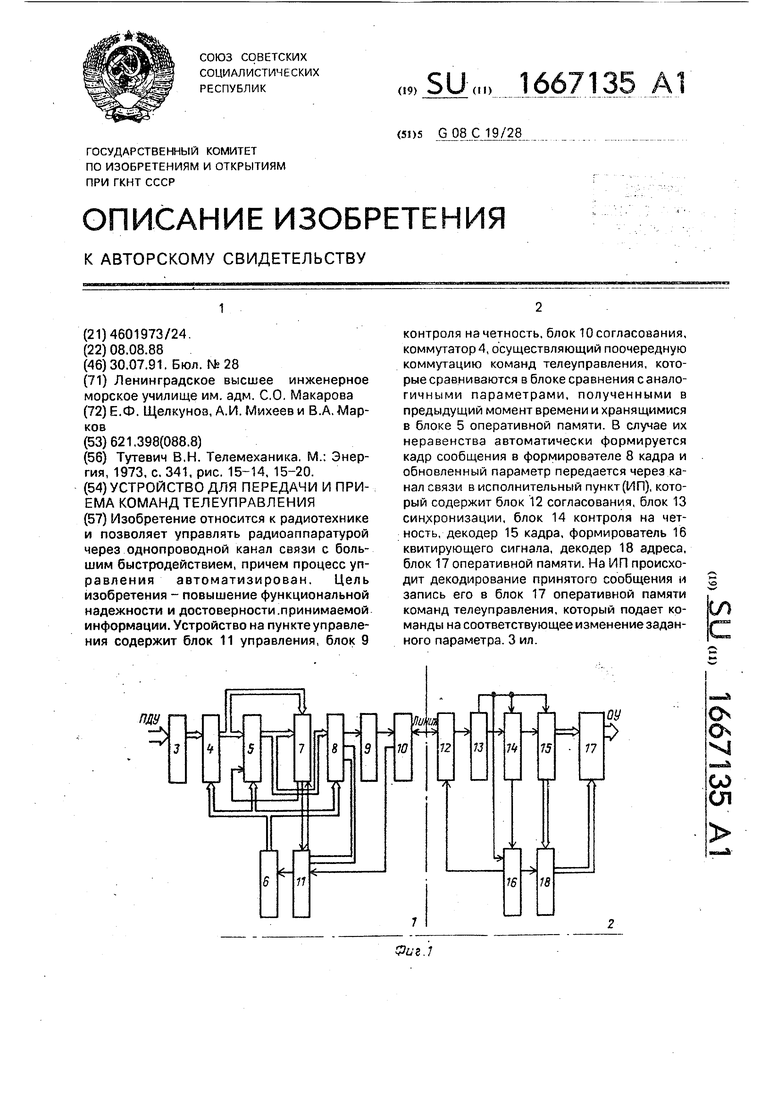

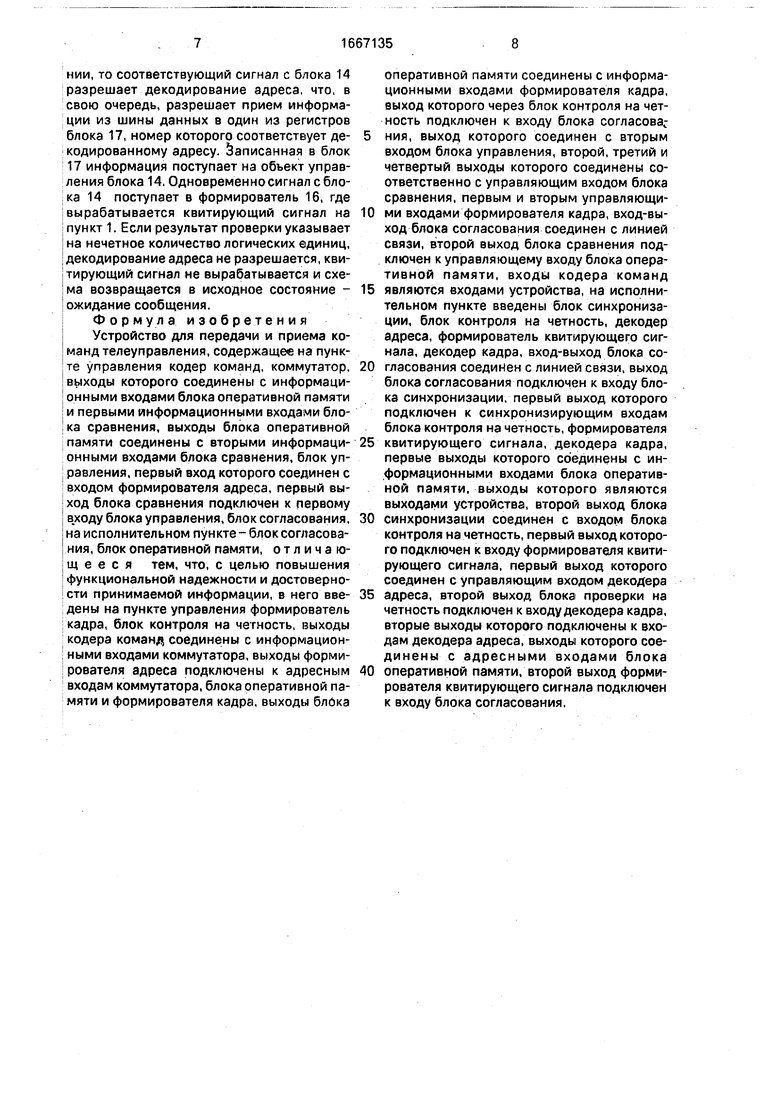

На фиг. 1 изображена блок-схема устройства; на фиг. 2 - принципиальная схема блока управления; на фиг. 3 - принципиальная схема формирователя квитирующего сигнала.

Устройство содержит пункт 1 управления и исполнительный пункт 2.

Пункт 1 управления состоит из кодера 3 команд (выходы кодера 3 команд образуют 16 4-разрядных шин, адресный вход коммутатора 4 представляет собой 4-разрядную шину), блока 5 оперативной памяти, формирователя б адреса, блока 7 сравнения, формирователя 8 кадра, блока 9 контроля на четность, блока 10 согласования и блока 11 управления. На исполнительном пункте устройство содержит блок 12 согласования, блок 13 синхронизации, блок 14 контроля на четность, декодер 15 кадра, формирователь 16 квартирующего сигнала, блок 17 оперативной памяти и декодер 18 адреса.

Блок 11 управления (фиг. 2) выполнен на резисторах 19 и 20, элементах И 21-43, конденсаторах 44 и 45, триггерах 46 и 47, счетчиках 48-50 и элементе ИЛИ 51.

Формирователь 16 (фиг. 3) содержит элементы И 52 и 53, триггер 54, регистр 55, счетчик 56 и регистры 57-60,

Устройство работает следующим образом.

Генератор тактовых импульсов, входящий в состав блока 11 и собранный на элементах И 21-25, резисторах 19 и 20 и конденсаторах 44 и 45, при наличии разрешающего сигнала на выходе триггера 46 вырабатывает тактовые импульсы, поступающие на формирователь 8, При поступлении сигнала с блока 10 триггер 52 устанавливается в нулевое положение, запрещая прохождение тактовых импульсов через элемент И 25 на формирователь 8, а также запрещая работу блока 10, и разрешает прохождение тактовых импульсов через элемент И 26 на счетчик 48. Одновременно триггер 47, опрокидываясь в единичное состояние, разрешает прохождение тактовых импульсов через элементы И 28 и 29 на формирователь 8. Счетчик 48 осуществляет подсчет тактовых импульсов, поступающих на формирователь 8, и при прохождении одиннадцатого импульса переводит триггер 47 в нулевое состояние

Далее начинает работать узел декодирования, собранный на элементах И 36-43 и счетчиках 49 и 50. Квитирующий сигнал состоит из комбинации 1010. Происходит это

следующим образом: установившись в нулевое состояние, триггер 47 разрешает прохождение тактовых импульсов через элементы И 30 и 31 на элемент И 36, на второй вход которого поступает прямой кви0 тирующий сигнал, и на элемент И 39, на второй вход которого поступает проинвер- тированный в инверторе квитирующий сигнал. Счетчики 49 и 50 подсчитывают нулевые и единичные импульсы в квитирую5 щем сигнале соответственно и при их соотношении 2:2 в принятой комбинации квитирующего сигнала после четырнадцатого тактового импульса, подсчитанного в счетчике 48, происходит опрокидывание

0 триггера 46 в единичное состояние, разрешающее прохождение тактового импульса на формирователь 8. Если соотношение 2:2 в принятой комбинации нарушено, то вновь тактовые импульсы начинают поступать на

5 формирователь 8, и работа схемы начинает повторяться с этого момента.

Формирователь 16 работает следующим образом. С приходом импульса от блока 14, индицирующего верность проверки

0 на четность принятого сообщения, триггер 54 опрокидывается в единичное состояние, разрешая прохождение тактовых импульсов на регистр 55. Кроме того, импульс с блока 14 дает команду регистру 55 на прием

5 информации от счетчика 56, на входе которого установлена комбинация 1010 квитирующего сигнала. После сдвига всей информации в линию триггер 54 устанавливается в нулевое состояние и прохождение

0 тактовых импульсов к регистру 55 прерывается.

При подаче питания на пункт управления устройство работает следующим образом.

5 На выходном разъеме кодер 3 устанавливает комбинации логических нулей и единиц соответственно положению органов управления на передней панели, К этому разъему подключена плата пункта управле0 ния, Цифровые сигналы через эти разъемы поступают на входы четырех мультиплексоров коммутатора 4, входы которых скомму- тированы таким образом, что образуют 16 4-разрядных шин, На пункте 1 происходит

5 установка всех схем и блоков в начальное состояние: формирователь 6 формирует на своем выходе сигнал, соответствующий первому из 16 адресов; блок 19 формирует сигналы, разрешающие прохождение тактовых импульсов на формирователь 6, включает блок 7, обнуляет счетчик формирователя 8. Непосредственная работа диспетчерского пункта 1 начинается с заполнения ячеек памяти массивом данных, отражающих положение органов управления. Происходит это следующим образом: формирователь 6 формирует сигнал, соответствующий первому адресу, и передает его в адресную шину. Согласно этому адресу на выходы четырех мультиплексоров коммутируются первые входы мультиплексоров, скоммутирован- ные данные по шине данных поступают в блок 7 и на вход блока 5, на второй вход блока 7 в начальный момент времени поступает произвольная комбинация, так как в памяти блока 5 после включения аппаратуры устанавливается произвольный массив данных, в случае равенства логических комбинаций на обоих входах блока 7 она не вносит никаких изменений в работу схемы и по-прежнему удерживает на своем выходе сигнал, обеспечивающий выборку данных из блока 5. В начальный момент времени работы устройства наиболее вероятен другой вариант: блок 7 обнаруживает неравенство комбинаций в шине данных и ячейках памяти блока 5. В этом случае блок 7 сигнализирует об этом блоку 11, который вырабатывает сигнал остановки формирования сигналов адреса формирователя 6, т.е. запрещает прохождение тактов на вход формирователя б до момента прихода квитирующего сигнала, сигнал записи информации из шины данных в соответствующие сформированному в настоящий момент адресу ячейки памяти блока 5, сигнал записи информации из шины данных и адресной шины в регистры формирователя 8, сигнал на полшаговый сдвиг записанной в формирователе 8 информации через блок 9 и блок 10 в линию связи, кроме того, блок 11 запрещает работу блока 7 до момента получения квитирующего сигнала от исполнительного пункта, тактирует работу блока 9, который осуществляет пересчет логических единиц в формируемом сообщении и в случае нечетного их количества добавляет на 10-езнакоме

сто в сообщении логическую единицу.

После получения квитирующего сигнала блок 11 разрешает формирование формирователем 6 сигнала, соответствующего следующему по порядку номеру адреса. На выходы мультиплексоров коммутатора 4 коммутируются их вторые входы, сигналы поступают в шину данных. Далее работа аналогична описанному алгоритму.

После запонения всех ячеек памяти блока 5, соответствующих 16 адресам (с 1-го по 16-й), формирователь 6 вновь формирует сигнал, соответствующий первому по порядку адресу. Если положение органов уп- равления на пункте 1 не меняется за время цикла, равное времени между формированием сигнала адреса №1 в предыдущий и в 5 нынешний циклы осмотра выходов кодера 3. то данные в блоке 5 отражают состояние пункта 1 верно и схема ничего больше не передает в линию связи, а лишь осуществляет постоянный контроль всех параметров

0 пункта 1 путем опроса всех сигналов на выходе кодера 3. В случае обнаружения схемой какого-либо изменения положения органов управления на пункте 1, которое влечет за собой изменение сигналов на вы5 ходе кодера 3, данные в блоке 5 обновляются и одновременно происходит передача изменившегося параметра на исполнительный пункт 2 по описанному алгоритму. При подаче питания на схему исполни0 тельного пункта 2 обнуляются счетчик блока 13 и регистры блока 17. начинает работу тактовый генератор. Данные из блока 17 поступают через блок согласования на вход пункта 2, выход которого подключен к обье5 кту управления через его стандартные разъ- емы для подключения пункта 1. Соответственно установленным нулевым комбинациям в блоке 17 отрабатывают обь- екты управления. До момента получения

0 первого сигнала управления пункт 2 находится в описанном состоянии.

При получении сигнала управления сообщение проходит через блок 12, в котором параметры сигнала в линии передачи связи

5 согласуются с параметрами сигнала в схеме пункта 2, и поступает на вход блока 13. С приходом стартовой посылки уровня О происходит синхронизация импульсов местного тактового генератора по центру стар0 товой посылки. После синхронизации генератора полный формат сообщения проходит через узел проверки на содержание в нем четного числа логических единиц блока 14, работа которого тактируется синхрони5 зированными тактовыми импульсами. Одновременно информационные элементы последовательно заполняют 8-разрядный декодер 15, работа которого также тактируется синхронизированными тактовыми им0 пульсами. После заполнения всех восьми разрядов декодера 15 в блок 14 приходит десятый проверочный элемент, который позволяет определить с известной вероятностью искаженность принятой комбинации.

5 В это время декодер 15 полностью заполнен. С его выходов четыре первых элемента (адресные) считываются в декодер 18, а четыре следующих (данные) - в шину данных блока 17. Если результат указывает на четное количество единиц в принятом сообщении, то соответствующий сигнал с блока 14 разрешает декодирование адреса, что, в свою очередь, разрешает прием информации из шины данных в один из регистров блока 17, номер которого соответствует де- кодированному адресу. Записанная в блок 17 информация поступает на объект управления блока 14. Одновременно сигнал с блока 14 поступает в формирователь 16, где вырабатывается квитирующий сигнал на пункт 1. Если результат проверки указывает на нечетное количество логических единиц, декодирование адреса не разрешается, квитирующий сигнал не вырабатывается и схема возвращается в исходное состояние - ожидание сообщения.

Формула изобретения Устройство для передачи и приема команд телеуправления, содержащее на пункте управления кодер команд, коммутатор, выходы которого соединены с информационными входами блока оперативной памяти и первыми информационными входами блока сравнения, выходы блока оперативной памяти соединены с вторыми информаци- онными входами блока сравнения, блок управления, первый вход которого соединен с входом формирователя адреса, первый выход блока сравнения подключен к первому входу блока управления, блок согласования, на исполнительном пункте - блок согласования, блок оперативной памяти, отличающееся тем, что, с целью повышения функциональной надежности и достоверности принимаемой информации, в него вве- дены на пункте управления формирователь кадра, блок контроля на четность, выходы кодера команд соединены с информационными входами коммутатора, выходы формирователя адреса подключены к адресным входам коммутатора, блока оперативной памяти и формирователя кадра, выходы блока

оперативной памяти соединены с информационными входами формирователя кадра, выход которого через блок контроля на четность подключен к входу блока согласовав ния, выход которого соединен с вторым входом блока управления, второй, третий и четвертый выходы которого соединены соответственно с управляющим входом блока сравнения, первым и вторым управляющими входами формирователя кадра, вход-выход блока согласования соединен с линией связи, второй выход блока сравнения подключен к управляющему входу блока оперативной памяти, входы кодера команд являются входами устройства, на исполнительном пункте введены блок синхронизации, блок контроля на четность, декодер адреса, формирователь квитирующего сигнала, декодер кадра, вход-выход блока согласования соединен с линией связи, выход блока согласования подключен к входу блока синхронизации, первый выход которого подключен к синхронизирующим входам блока контроля на четность, формирователя квитирующего сигнала, декодера кадра, первые выходы которого соединены с информационными входами блока оперативной памяти, выходы которого являются выходами устройства, второй выход блока синхронизации соединен с входом блока контроля на четность, первый выход которого подключен к входу формирователя квитирующего сигнала, первый выход которого соединен с управляющим входом декодера адреса, второй выход блока проверки на четность подключен к входу декодера кадра, вторые выходы которого подключены к входам декодера адреса, выходы которого соединены с адресными входами блока оперативной памяти, второй выход формирователя квитирующего сигнала подключен к входу блока согласования,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема информации | 1988 |

|

SU1684799A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ ИНФОРМАЦИИ НА ВИДЕОМАГНИТОФОНЕ | 1993 |

|

RU2042218C1 |

| Система телемеханики | 1984 |

|

SU1257686A1 |

| Система телемеханики | 1990 |

|

SU1711216A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Контролируемый пункт системы телемеханики | 1988 |

|

SU1524080A1 |

Изобретение относится к радиотехнике и позволяет управлять радиоаппаратурой через однопроводной канал связи с большим быстродействием, причем процесс управления автоматизирован. Цель изобретения - повышение функциональной надежности и достоверности принимаемой информации. Устройство на пункте управления содержит блок управления 11, блок 9 контроля на четность, блок согласования 10, коммутатор 4, осуществляющий поочередную коммутацию команд телеуправления, которые сравниваются в блоке сравнения с аналогичными параметрами, полученными в предыдущий момент времени и хранящимися в блоке 5 оперативной памяти. В случае их неравенства автоматически формируется кадр сообщения в формирователе 8 кадра и обновленный параметр передается через канал связи в исполнительный пункт /ИП/, который содержит блок 12 согласования, блок синхронизации 13, блок 14 контроля на четность, декодер 15 кадра, формирователь 16 квитирующего сигнала, декодер 18 адреса, блок 17 оперативной памяти. На ИП происходит декодирование принятого сообщения и запись его в блок 17 оперативной памяти команд телеуправления, который подает команды на соответствующее изменение заданного параметра. 3 ил.

Фиг. 2

аил

| Тутевич В.Н | |||

| Телемеханика | |||

| М : Энергия, 1973 | |||

| с | |||

| Кардочесальная машина | 1923 |

|

SU341A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1991-07-30—Публикация

1988-08-08—Подача