СО

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1559405A2 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1676103A1 |

| Цифровой измеритель RLC-параметров | 1986 |

|

SU1337820A1 |

| Третьоктавный спектральный анализатор | 1985 |

|

SU1308927A1 |

| Устройство для измерения и контроля параметров аналого-цифровых преобразователей | 1981 |

|

SU1005297A1 |

| Устройство для измерения мощности | 1990 |

|

SU1751685A1 |

| Устройство коррекции телевизионного сигнала | 1988 |

|

SU1628224A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1569590A1 |

| Система экстремального регулирования квадрупольного масс-спектрометра | 1989 |

|

SU1795419A1 |

| Цифровой омметр | 1990 |

|

SU1784925A1 |

Изобретение относится к измерительной технике и может быть использовано в цифровых измерительных приборах и информационно-измерительных системах при кодировании электрических сигналов. Изобретение позволяет повысить точность преобразования за счет подавления мультипликативной составляющей погрешности. Это достигается тем, что в устрйство, содержащее переключатель 2, источник 1 образцового напряжения, интегратор 3, компаратор 5, генератор 4 образцовой частоты, элемент И 6, блок 17 управления, элемент ИЛИ 11, элемент И 9, счетчик 10, введены элементы НЕ 7, 8, реверсивный счетчик 12, формирователь 14 импульсов, цифровой компаратор 13, регистр 16, постоянное запоминающее устройство 15. 1 з.п.ф-лы, 3 ил.

с ч о

ч

XI

Изобретение относится к измерительной технике и может быть использовано в цифровых -измерительных приборах и информационно-измерительных системах при кодировании электрических сигналов,

Целью изобретения является повышение точности преобразования за счет подавления мультипликативной составляющей погрешности.

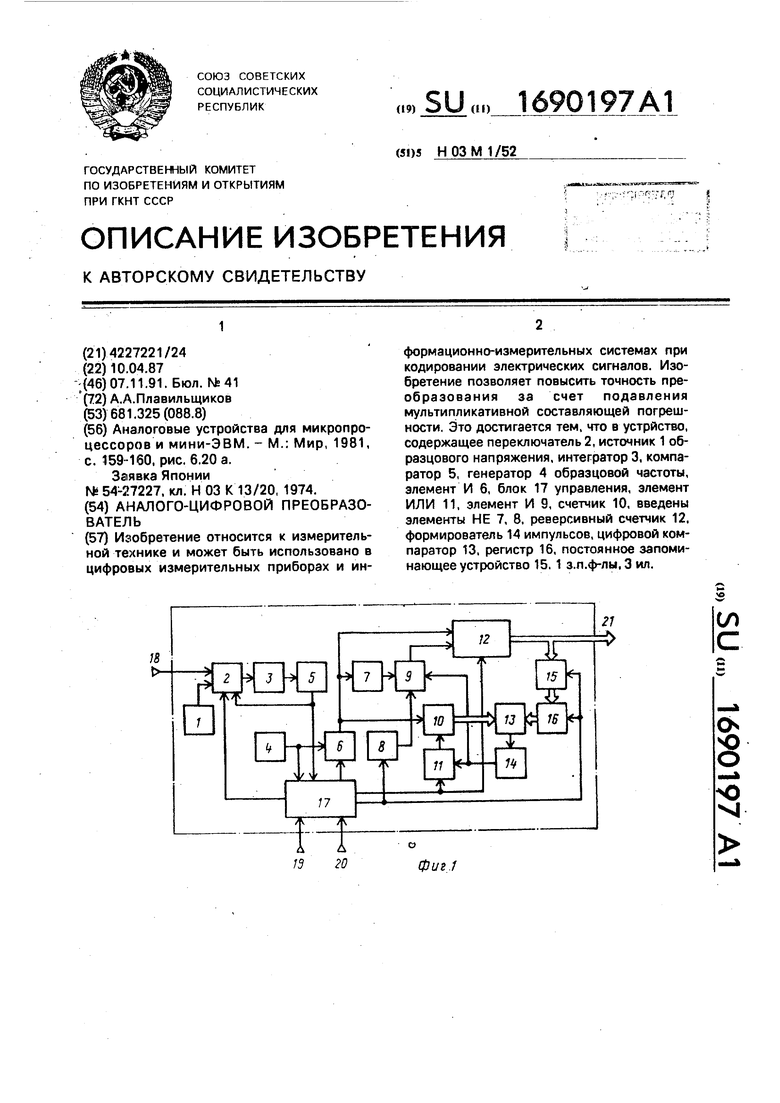

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - характеристики преобразования.

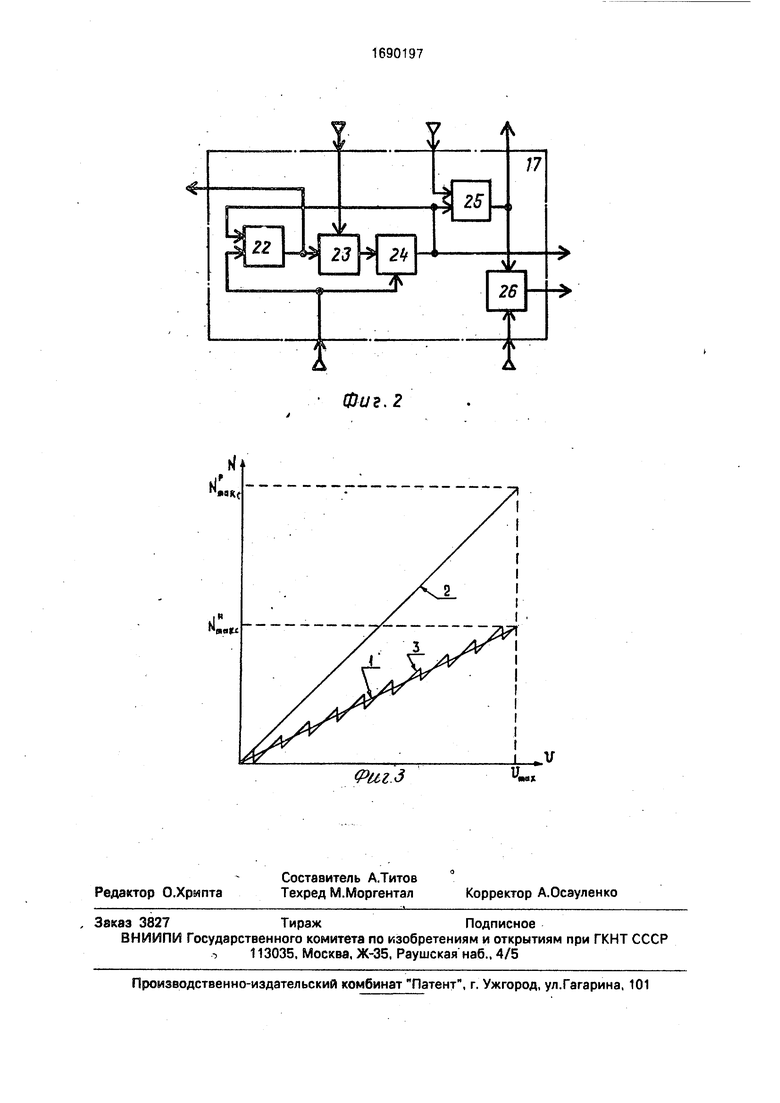

Устройство содержит источник 1 образцового напряжений, переключатель 2, интегратор 3, генератор А образцовой частоты Г04, компаратор 5, элемент И б, элементы НЕ 7 и 8, элемент И 9, счетчик 10, элемент ИЛИ 11, реверсивный счетчик 12, цифровой компаратор 13, формирователь 14 импульсов, постоянное запоминающее устройство (ПЗУ) 15, регистр 16, блок 17 управления, информационный вход 18, вход 19 запуска, вход 20 обеспечения режима, выход 21, блок управления (фиг, 2) содержит триггер 22, элемент И 23, счетчик 24, триггер 25, элемент И 26.

Аналого-цифровой преобразователь (АЦП), в зависимости от сигнала, поступающего на его вход 20, работает в одном из 2-х режимов. В режиме 1 оценивается значение мультипликативной составляющей погрешности преобразования, а в режимэ 2 осуществляется кодирование измеряемой величины с коррекцией мультипликативной составляющей погрешности.

Режим 1 используется периодически при колибровке АЦП и задается сигналом 1, подаваемым на вход 20 и далее на четвертый вход блока 17. При этом на вход 18 АЦП подается эталонное напряжение, соответствующее максимальному коду на выходе 21. Запуск АЦП осуществляется импульсом, подаваемым на вход 19. По переднему фронту этого импульса на первом выходе блока 17 формируется сигнал 1, который поступает на третий вход переключателя 2. Переключатель 2 подключает входное напряжение к входу интегратора 3, который интегрирует его в течение заданного интервала времени. По окончании указанного интервала на выходах блока 17 формируются сигналы: на первом - О, на втором - 1, на третьем - короткий импульс; на четвертом . В результате этого переключатель 2 отключает от входа интегратора 3 входное напряжение и подключает к его входу напряжение противоположной полярности с выхода источника 1, вызывая линейный спад напряжения на выходе интегратора 3; счетчик 10 импульсом, поступающим на его первый вход через элемент 11, устанавливается в счетчик 12 импульсом, поступающим на его третий

вход, устанавливается в элемент 6 разблокируется по второму входу и импульсы, поступающие на его первый вход, начинают поступать на выход и дглее на первый (суммирующий) вход счетчика 12.

Линейный спад до нуля напряжения на выходе интегратора 3 занимает интервал времени, пропорциональный величине входного напряжения. Окончание этого процесса фиксируется компаратором 5, который в момент равенства нулю напряжения на выходе интегратора 3 формирует на своем выходе импульс, поступающий на четвертый вход переключателя 2 и на первый вход блока 17, Переключатель 2 отключает

вход интегратора 3 от выхода источника 1 и подключает его к нулевому потенциалу, а блок 17 на своем втором выходе формирует сигнал О и блокирует элемент 6. При этом прекращается поступление импульсов на

первый вход счетчика 12, и на его выходе фиксируется код результата. При проектировании реальная крутизна характеристики преобразования АЦП (фиг. 3, характеристика 2) выбирается (соответствующей величиной напряжения источника 1 или частоты следования импульсов генератора 4) такой, чтобы она, несмотря нэ возможные флуктуации (температурную и временную), превышала крутизну идеальной характерстики

преобразования (фиг. 3, характеристика 1). Это превышение оценивается величиной:

Nn МмаксР - NMaKCM,(1)

где - код максимального входного

напряжений при реальной характеристике преобразования;

Ммакси - код максимального входного напряжения при идеальной характеристике преобразования.

Емкость счетчика 12 - МСч выбирается равной величине ЫМакси, поэтому при кодировании эталонного максимального напряжения счетчик 12 переполняется и вновь заполняется импульсами, При этом результирующее значение кода на выходе счетчика 12 будет равно Nn. Код Nn, занимающий несколько младших разрядов счетчика 12, поступает на первый (адресный) вход ПЗУ 15 и осуществляет выбор соответствующей

ячейки памяти последнего,

В режиме 1 ПЗУ 15 и регистр 16 сигналом 1, поступающим на второй и первый входы, устанавливаются соответственно в режимы Чтение и Запись.

При этом в процессе кодирования эталонного напряжения происходит последовательный выбор ячеек ПЗУ 15, считывание их содержимого и запись его в регистр 16. По окончании указанного процесса в реги- 5 стре 16 будет записано содержимое ячейки памяти, код адреса которой равен Nn. На этом работа в режиме 1 заканчивается,

В режиме 2 кодируется исследуемое напряжение, поступающее на вход 18 АЦП. 10 Этот режим задается сигналом О, подаваемым на вход 20 АЦП, Запуск АЦП осуществляется импульсом, подаваемым на вход 19. По переднему фронту этого импульса на первом выходе блока 17 формируется сиг- 15 нал Г, который поступает на третий вход переключателя 2. Переключатель 2 подключает входное напряжение к входу интегратора 3, который интегрирует его в течение заданного интервала времени. По оконча- 20 нии указанного интервала на выходах блока 17 формируются сигналы на первом - О, на втором - 1, на третьем - короткий импульс, на четвертом - О.

В результате этого переключатель 2 от- 25 ключает от входа интегратора 3 входное напряжение и подключает к его входу напряжение противоположной полярности с выхода источника 1, вызывая линейный спад напряжения на выходе интегратора 3; 30 счетчик 10 импульсом, поступающим на его первый вход через элемент 11, устанавливается в счетчик 12 импульсом, поступающим на его третий вход устанавливается в элемент 6 разблокируем по второму 35 входу, и импульсы, поступающие на его первый вход с выхода генератора 4, начинают поступать на ее выход и далее на первый вход счетчика 12.

При этом в процессе заполнения счет- 40 чика 12 импульсами образцовой частоты, в отличие от режима 1, осуществляется периодическая коррекция текущего значения крутизны преобразования. Указанная коррекция осуществляется подачей импульсов 45 на второй (вычитающий) вход счетчика 12. Корректирующие импульсы, во избежание сбоя счетчика 12, формируются в паузах между импульсами образцовой частоты, по- ступающих на первый вход счетчика 12. При 50 этом период следования этих импульсов в определенное число (D) оаз превышает период следования импульсов образцовой частоты.

Процедура коррекции осуществляется 55 следующим образом.

При заполнении счетчика 12 импульсы с выхода элемента, 6 поступают также и на вход счетчика 10, код с выхода которого сравнивается с содержимым регистра 16

цифровым компаратором 13. В моменты оа- венства кодов, поступающих на его входы, компаратор 13 срабатывает и запускает формирователь импульсов 14. При запуске формирователь 14 формирует на своем выходе короткий импульс, длительность которого в 1,5 раза превышает длительность импульсов образцовой частоты, Этот импульс через элемент 11 поступает на первый вход счетчика 10 и устанавливает его в состояние О. Кроме того, указанный импульс поступает на третий вход элемента 9. По второму входу этот элемент разблокируется сигналом О, поступающим с четвертого выхода блока 17 через элемент 8. По первому входу элемент 9 разблокируется в паузах между импульсами образцовой частоты. Таким образом, импульс с выхода формирователя 14 поступает на второй вход счетчика 12 и уменьшает на единицу его содержимое. В дальнейшем описанная процедура периодически повторяется. В итоге результирующая характеристика преобразования АЦП принимает линейно-ступенчатый вид (фиг/ 3, характеристика 3),

Блок 17 работает следующим образом.

В режиме 1 на четвертый вход блока 16 подается сигнал 1 который разблокирует элемент 26. На третий вход блока 17 подается импульс, запуска, который устанавливает счетчик 24 в 0, а триггер 22 - в 1. Сигнал с выхода триггера 22 поступает на первой выход блока 17 и на первый вход элемента 23, разблокируя последний. В результате этого импульсы обоазцовой частоты, поступающие на второй вход блока 17, через разблокированный элемент 23 подаются на счетный вход счетчика 24. При этом время заполнения счетчика 24 определяет величину времени интегрирования входного напряжения. При переполнении счетчика 24 импульс переполнения с выхода последнего поступает на третий выход блока 17 и на второй вход триггера 22, устанавливая его в О. При этом сигнал 1 с первого выхода блока 17 снимается, а элемент 23 блокируется, и поступление импульсов образцовой частоты на первый вход счетчика 24 прекращается. Импульс переполнения поступает также на первый вход триггера 25, устанавливая его в 1. Сигнал с выхода триггера 25 поступает на второй выход блока 17 и через разблокированный элемент 26 - на четвертый выход последнего. По окончании процесса кодирования входного напряжения на первый вход блока 17 поступает импульсный сигнал, который устанавливает триггер 25 в О. Сигнал О блокирует элемент 26, а также поступает на второй выход блока 17.

В режиме 2 блок 17 работает аналогично режиму 1, Отличие заключается в том, что на четвертуй вход блока 17 вместо 1 подается О. При этом в режиме 2 на четвертом выходе блока 17 формируется постоянный сигнал 0й.

Формула изобретения 1. Аналого-цифровой преобразователь, содержащий переключатель, первый вход которого является входной шиной, второй вход соединен с выходом источника образцового напряжения, третий вход соединен с первым выходом блока управления, а выход через интегратор - с входом компаратора, генератор образцовой частоты, выход которого соединен с первым входом первого элемента И, счетчик, первый вход которого соединен с выходом элемента ИЛИ, второй элемент И, отличающийся тем, что, с целью повышения точности преобразования за счет подавления мультипликативной составляющей погрешности преобразования, в него введены два элемента НЕ, реверсивный счетчик, формирователь импульсов, цифровой компаратор, регистр. постоянное запоминающее устройство, при этом выход компаратора соединен с четвертым входом переключателя и с первым входом блока управления, второй выход которого подключен к второму входу первого элемента И, выход которого соединен с вторым входом счетчика и первым входом реверсивного счетчика и через первый элемент НЕ - с первым входом второго элемента И, второй вход которого соединен с выходом второго элемента НЕ, третий вход обьединен с первым входом элемента ИЛИ и через формирователь импульсов соединен с выходом цифрового компаратора, а выход второго элемента И соединен с вторым входом реверсивного счетчика, третий вход которого

объединен с вторым входом элемента И и соединен с третьим выходом блока управления, выходы реверсивного счетчика соединены с соответствующими первыми

входами постоянного запоминающего устройства и являются выходной шиной, второй вход постоянного запоминающего устройства объединен с первым входом регистра, входом второго элемента НЕ и соединен с четвертым выходом блока управления, выходы постоянного запоминающего устройства соединены с соответствующими вторыми входами регистра, выходы которого соединены с соответствующими

первыми входами цифрового компаратора, вторые входы которого соединены с соответствующими выходами счетчика, выход генератора образцовой частоты соединен с вторым входом блока управления, третьим

и четвертым входами которого являются соответственно вход запуска и вход обеспечения режима.

на двух триггерах, двух элементах И и счетчике, первый вход которого соединен с выходом первого элемента И, второй вход объединен с первым входом первого триггера и является третьим входом блока, выход

счетчика соединен с вторым входом первого триггера, первым входом второго триггера и является третьим выходом блока, четвертым выходом которого является выход второго элемента И, первый вход которого является

четвертым входом блока, второй вход соединен с выходом второго триггера и является вторым выходом блока, второй вход второго триггера является первым входом блока, первый вход первого элемента И соединен

с выходом первого триггера и является первым выходом блока, второй вход первого элемента И является вторым входом блока.

Фиг. 2

ФигЗ

| Аналоговые устройства для микропроцессоров и мини-ЭВМ | |||

| - М.: Мир, 1981, с | |||

| Катодное реле | 1918 |

|

SU159A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-11-07—Публикация

1987-04-10—Подача