Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах автоматического управления и в устройствах преобразования и кодирования информации.

Цель изобретения - расширение области применения преобразователя за счет рбеспечения непрерывного формирования параллельно-последовательных временных интервалов.

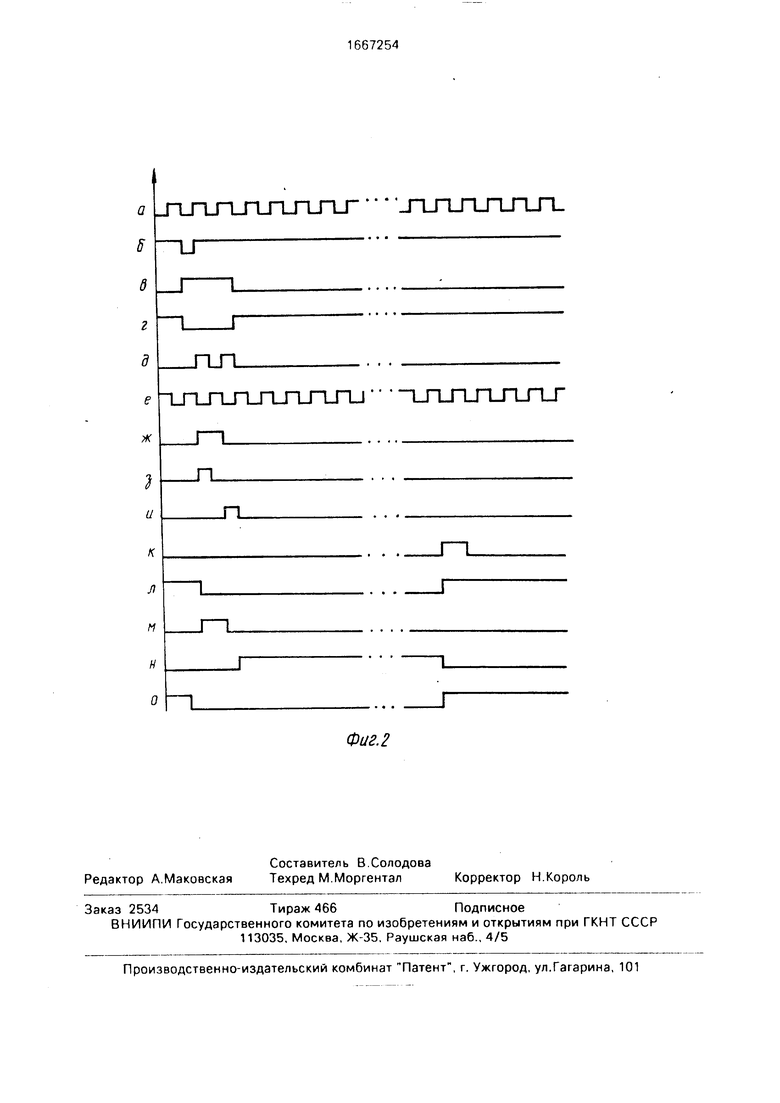

Нафиг. 1 представленэструкгурная схема преобразователя код - временной сигнал, на фиг. 2 - диаграммы, поясняющие его работу.

Преобразователь код - временной интервал содержит генератор 1 импульсов, счетчик 2 импульсов, регистр 3, элемент 4 сравнения кодов, триггер 5 управления, первый D-триггер 6, первый 7, второй 8 и третий 9 элементы И, шину 10 входного кода, первую 11 и вторую 12 выходные шины, четвертый 13, пятый 14 и шестой 15 элементы И, второй 16 и третий 17 D-триггеры, инвертор 18, группу из первого 19 и второго 20 элементов И, элемент ИЛИ 21, третью выходную шину 22, выходную шину 23 разрешения записи, входную шину 24 записи. Работу преобразователя код - временной интервал поясняет диаграмма на фиг. 2, где а - выход генератора 1 импульсов; б - выход переноса счетчика ; в - выход третьего D-триггера 17; г - третья выходная шина 22; д- выход пятого элемента И 14; е-выход инвертора 18; ж- выход второго D-триггера 16; з - выход первого элемента И 19; и - выход второго элемента И 20; к - выход второго элемента И 20; к - выход элемента 4 сравнения; л - первая выходная шина 11; м - выход первого D-триггера 6; н - вторая выходная шина 12; о эыход- ная шина 23 разрешения записи.

со

с

Os

о XI ю

(Л

Преобразователь код-временной сиг нал работает следующим образом

На выходе счетчика 2 импульсов появляются все кодовые комбинации (в количестве 2П, где п - количество разрядов счетчика 2) При состоянии 11 ..1 во втором полупериоде тактовой частоты генератора 1 вырабатывается активный сигнал переноса (б) Активный низкий уровень сигнала переноса разрешает счет второго D-триггера через элемент И 15, установив в 1 третий D-триггер 17 (в). Второй D-триггер 16 вырабатывает импульс (ж) длительностью в период тактовой частоты, так как он включен как делитель на два. Третий D-триггер 17 будет переключаться со сдвигом на полпериода тактовой частоты, так как тактовые импульсы будут проходить через инвертор 18 (е) Он будет установлен в 1 два периода тактовой частоты генератора 1 потому, что второй D-триггер 16 установится в О через период тактовой частоты Инверсный выход третьего D-триггера является третьей выходной шиной Сигнал, который сформирует элемент И 19 группы (з) в результате логического умножения второго 16, третьего 17 D-триггеров и генератора 1 импульсов через элемент ИЛИ 21 установит первый D- триггер 6 в 1 (м) Активная 1 первого D-триггера 6 сбросит в О триггер 5 управления После того, как ёторой D-триггер 16 установится в О, на втором элементе И 20 группы сформируется импульс (и) длительностью в половину периода тактового генератора 1, который сбросит в О первый D-триггер 6 Следовательно, за время когда на шине 22 О, произошла наел ройка схемы на новое преобразование кода после активного сигнала переноса сформирован счет ный импульс на первый D-триггер 6 через период тактовой частоты генератора 1 формируется импульс сброса на тот же D-триггер 6 Логическая 1 на третьей выходной шине 22 означает что схема выполняет преобразование кода, при этом переход этой шины из О в 1 означает, что счетчик 2 импульсов начал отсчет от кода 00 О

При коде счетчика 2 импульсов, равном коду регистра 3, схема 4 сравнения кодов сформирует импульс длительностью в период тактовой частоты (к), который установит в 1 триггер 5 управления, и на первой выходной шине 11 произойдет перепад с высокого уровня на низкий, а на второй выходной шине 12 - наоборот, с низкого на высокий Логическая 1 на выходе триггера 5 управления сформирует сигнал разрешения записи шины 23 на устройство, которое формирует сигнал записи по шине 24 Если в это время устройство сформирует сигнал

записи, то он через четвертый элемент И 13 запишет в регистр 3 код шины 10, и новое преобразование схема будет производить по новому коду Блокировка записи необходима для того, чтобы исключить неправильную работу преобразователя, которая может возникнуть, если в регистр 3 записать код до того, как сработает элемент сравнения кодов

В общем случае на выходах преобразователя будут реализованы временные соотношения

15

t(1) t(0)N(a) 1/2,

t (2) t (0) N (b) N(a)-1/2

t (3) - t (0) N (b) -1

где N (b) - разрядность счетчика 2 N (a) - код регистра 3 Необходимо помнить, что время (1) (2), (3) прямо пропорционально коду регистра 3 с коррекцией на 1/2 периода тактовой частоты генератора 1 для первой 11 и второй 12 выходных шин и на период для третьей выходной шины 22 Это вызвано тем, что сигнал переноса отключает выходные шины а сигнал сброса, который формируется

на втором элементе И 20, устанавливает вы- ходнь.е шины в соответствующее положение

Точность преобразования код - времен ной интервал будет определяться погрешиостью тактового генератора 1 и погрешностью переключения второго В, третьего 9 элементов И и третьего D-тригге ра 17

Данный преобразователь позволяет

формировать параллельно последовательные временные интервалы автоматически, без поддержки внешнего устройства, что в сложных устройствах где много таких пре образователен, облегчает работу контролирующей микроЭВМ

Формула изобретения

Преобразователь код - временной ин- тервал, содержащий регистр, триггер управ ления, первый, второй и третий D-триггеры и счетчик импульсов, счетный вход которого соединен с выходом первого элемента И первый вход которого подключен к выходу генератора импульсов, информационные входы регистра являются шиной входного кода а выходы подключены к первым входам элемента сравнения кодов соответст венно вторые входы которого соединены с соответствующими информационными выходами счетчика импульсов, вход сброса которого объединен с входом сброса первого D-триггера. счетный вход которого объединен со счетным входом триггера управления вход сброса которого соединен с выходом первого D-триггера, информационный вход которого подключен к прямому выходу триггера управления, инверсный выход которого соединен с первым входом второго элемента И, второй вход которого объединен с первым входом третьего элемента И, второй вход которого соединен с прямым выходом триггера управления, выходы второго и третьего элементов И являются соответственно первой и второй выходными шинами, отличающийся тем, что, с целью расширения области применения преобразователя за счет обеспече- ния непрерывного формирования параллельно-последовательных временных интервалов, в него введены элемент ИЛИ, четвертый, пятый и шестой элементы И, группа элементов И и инвертор, вход которого объединен с первым входом пятого элемента И, первым входом первого элемента И групп.ы и первым входом первого элемента И, второй вход которого объединен с первыми входами третьего и шестого элементов И. третьей выходной шиной и подключен к инверсному выходу третьего

D-триггера, прямой выход которого соединен с вторыми входами пятого элемента И и первого элемента И группы и первым входом второго элемента И группы, второй вход

которого объединен с информационным входом второго D-триггера и соединен с инверсным выходом второго D-триггера, прямой выход которого соединен с третьим входом первого элемента И группы и с информационным входом третьего D-триггера, счетный вход которого подключен к выходу инвертора, а установочный вход объединен с третьим входом второго элемента И группы, вторым входом шестого элемента

И и подключен к выходу переноса счетчика импульсов, причем выходы пятого и шестого элементов И соединены соответственно со счетным входом и входом сброса второго D-триггера, выходы элемента сравнения кодов и первого элемента И группы соединены соответственное первым и вторым входами элемента ИЛИ. выход которого соединен со счетным входом первого D-триггера, вход сброса которого соединен с выходом второго элемента И группы, при этом вход записи регистра соединен с выходом четвертого элемента И, первый вход которого является шиной записи, второй вход соединен с прямым выходом триггера управления и является выходной шиной разрешения записи,

а 6 д г д

JTJ-TjnJ Lnjn rLJJ JT-rLrLrLTL

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения потери импульса | 1989 |

|

SU1709509A1 |

| Преобразователь код - широтно-импульсный сигнал | 1990 |

|

SU1793545A1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

| Устройство для телеизмерения давления скважинных штанговых насосов | 1990 |

|

SU1711218A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Селектор серий импульсов | 1989 |

|

SU1670781A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Преобразователь интервалов времени в цифровой код | 1984 |

|

SU1255984A2 |

| Формирователь серий задержанных импульсов | 1985 |

|

SU1361706A1 |

| ИОНИЗАЦИОННЫЙ ФИЛЬТР ДЛЯ ОЧИСТКИ ВОЗДУХА | 1992 |

|

RU2009717C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах автоматического управления и в устройствах преобразования и кодирования информации. Цель изобретения - расширение области применения преобразователя за счет обеспечения непрерывного формирования параллельно-последовательных временных интервалов. С этой целью в преобразователь код-временной интервал, содержащий генератор импульсов, счетчик импульсов, регистр, триггер управления, три D - триггера, элемент сравнения кодов и три элемента И, введены инвертор, элемент ИЛИ, четвертый, пятый и шестой элементы И, а также группа элементов И (на три входа). 2 ил.

nj jn-jTJOjnj LTTjи1 ггп п гг г

Фиг. 2

| Гитис Э.Л | |||

| и др Аналого-цифровые преобразователи | |||

| М.: Энергоатомиздат, 1981, с 168, рис | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Преобразователь код-временной интервал | 1985 |

|

SU1298921A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-07-30—Публикация

1989-08-28—Подача