(54) ДЕСЯТИЧНОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения десятичных чисел | 1984 |

|

SU1182514A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Устройство для умножения | 1983 |

|

SU1180881A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения чисел | 1989 |

|

SU1817091A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1236462A1 |

| Устройство для умножения | 1989 |

|

SU1668979A1 |

| Устройство для умножения десятичных чисел | 1976 |

|

SU652560A1 |

1

Изобретение касается вычислительной техники и может быть применено в Щ1фровых вычислительных машинах и настольных электронных арифмометрах,

Известно десятичное множительно устройство, состоящее из двоично-десятичного регистра множителя, ик:еюшего tn десятичных разрядов, двоично-десятичного регистра множимого, имеющего П десятичных разрядов, двои но-десятичного регистра частичных произведений, имеющего Ш -f tl десятичных разрядов, и двоично-десятичного промежуточного регистра, состоящего кз Ш + П-i

, десятичных разрядов, причем выходы десятичных разрядов регистра частичных произведений, начиная с первого разряда, соединены с одноименными входами десятичных разрядов промежуточного регистра.

I Известное десятичное множительное устройство затрачивает для умножения на одну Щ1ФРУ множителя два такта сложения сопровождающегося сквозным переносом, при этом происходит трехкратное преобразование из двоичной системы счЙ1 ления в десятичную.

Целью изобретения является увеличение быстродействия устройства,

В предложенное устройство введень множительных блоков, каждый из которых состоит из сумматора результата,. умно жителя, сумматора т-етрад и преобразователей старших и младших разрядов. при чем первый вход сумматора результата соединен с выходом умножителя, а второйс выходом сумматора тетрад, первый выход сумматора результата соединен со входом преобразователя старших разрядов, а второй выход - со входом преобразовав теля младших разрядов, первый вход ум ножителя L -того множительного блока соединен с выходом первого разряда регистра множителя, второй вход умножителя соединен с выходом (, -того разряда регистра множителя, первый вход сумматора тетрад соединен с (, -тым выходом промежуточного регистра, второй вход сумматора тетрад соединен с эыходом преобразователя старших разрядов t + 1 множительного блока, выход преобразователя младших разрядов соединен с i, + 1 входом. регистра частичных произведений, выход преобразователя старших разрядов первого множительного блоке соединен с первым входом регистра частичных произведений, выход р -того разряда промежуточного регистра (Н 14р4Ш+11-1) соединен с р + 1 разрядом регистра частичных произведений.

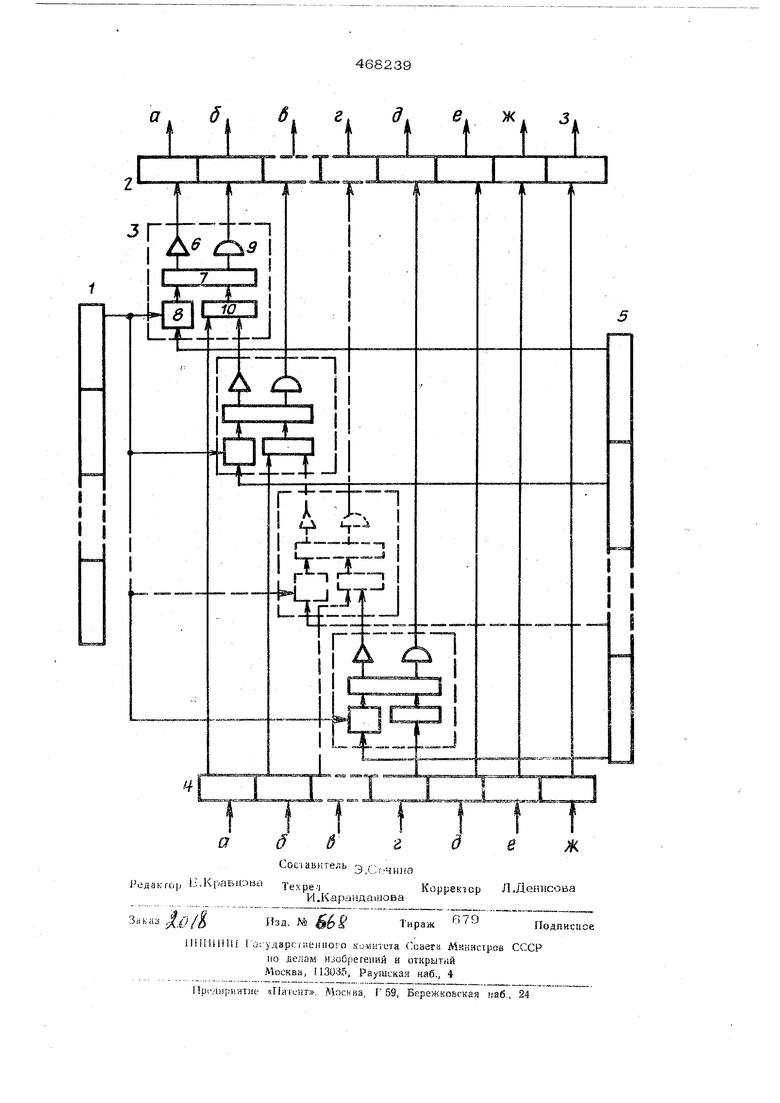

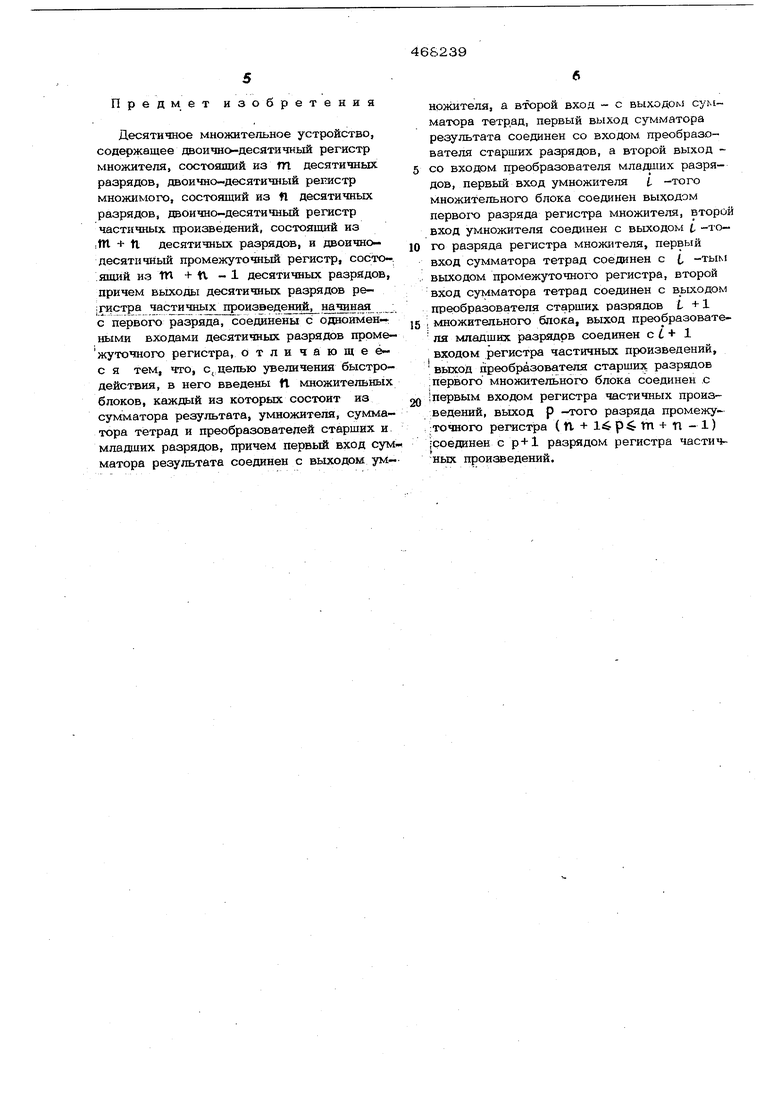

На чертеже представлена схема десятичного множительного устройства, содержащая регистр 1 множителя, регистр 2 частиных произведений , множительный блок 3, промежуточный регистр 4, регистр 5 мно- .жимого, преобразователь 6 старших разрядов, сумматор 7 результата, у множитель 8, преобразователь 9 младших разрядов 4, сумматор 1О тетрад.

Выходы регистра 2 обозначены стред ками а- 3 а в регистре 4 одноименные стрелки показывают,к входам каких имен- :но разрядов этого регистра должны быть присоединены выходы регистра 2, Линия, соединяющая выход одного блока со входом другого, обозначает столько проводов, сколько необходимо для представления всех Ш1ФР в заданной системе счисления и заданном способе представления цифр, причем подразумевается, что все соединения выполнены именно так, как это требует данное представление сигналов цифр. Старшие разряды размещены в регистре частичных произведений слева, в регистре множимого 5 сверху и в регистре множителя 1 - снизу. ,

Необходимое количество оборудования выбирсПэт из следующих соображений: количество множительных блоков 3 должно соответствовать разрядности (здесь и ниже имеется в виду десятичная разрядность) множимого fl (и соответственно разрядности регистра к ножимогх) 5), разрядность ретастра множителя 1 должна быть равна заданной tTl , разрядность регистра частичных произведений 2 должна быть равна сумме разрядностей множителя и множимого, т. е. (W + tl), а разрядность промежуточного регистра 4 на единицу меньше, т. е. (ш + tl - 1). В случае умножения с округлением разрядности регистров 2 и 4 могут быть уменьшены в соответствии с известными правилами.

На чертеже отдельно показан промежуточный регистр 4. Этот регистр, как правило, составляет неотделимую часть регистра частичных произведений и его основная заключается в запоминавши содержимого регистра частичных произведений 2 во время сдвигов. Регистр множителя 1 имеет цепи сдвигов. На чертеже показан мноядательный блок 3, состоящий из преобразователя старших разрядов 6, 5 преобразователя младших разрядов 9 и сумматора тетрад 1О,. Фактически сумматоры 7 и 10 составляют одну дополнительную линейку сумматоров к пирамиде сумматоров умножителя 8. 10 Работает устройство следующим обра,

Сигналь сомножителей передают в рё I гистры 1 и 5. Регистры 2 и 4 перед нача.: лом операции устанавливают в нулевое со-

15; стояние Выберем, nanpnMepj способ умножения от младших разрядов множителя и неподвижного множимого, тогда содержимое регистра множимого неподвижно, сдвиги в регистре множителя имеют направле20. ние снизу вверх, а соединение регистров 2 частичных произведений с промежуточным регистром 4 обеспечивает сдвиги слева (направо. После установки сомножителей в первом такте умножения внаЧале перемно25, жают двоичные эквиваленты младшей цифры множителя на цифры множимого с помощью умножителей 8 во всех множительных блоках 3. С помощью сумматора тетрад 10 в каждом из множительных блоков

30 суммируют сигнал с выхода преобразовате, ля старшего разряда 6 предыдущего мноI жительного блока с сигналом соответствующего разряда регистра 4 и полученную сумму складатают с результатом, получен-

35 ным на выходе множительного блока 8 с помощью сумматора 7. Затем осуществля:ют преобразование двоичного кода .в десятичный, при этом на выходе преобразователя младших разрядов 9 получают деся40 тичный код данного разряда частичных .произведений, который записывают в регистр 2, Полученный на выходе преобразователя старших разрядов 6 суммарный десятичный код переноса передают на вход

45 доследующего множительного блока 3

(сумматор 1О). После завершения переносов в регистре 2 получают очередное частичное произведение. Затем код из регистра 2 передают в регистр 4, и последовательность микроопераций повторяют. Когда будет произведено умножение на последнюю ци4ру множителя в регистре 2 будет получено искомое произведение. При умно жении на последнюю цифру передачу из реSSirncTpa 2 в регистр 4 не делают, если

конструкгдая регистра 2 такова, что при передаче гасится содержимое этого регистр

Предмет изобретения

Десятичное множительное устройство, содержащее двоично-десятичный регистр множителя, состо шшй из m десятичных разрядов, двоично-десятичный регистр множимого, состоящий из fl десятичных разрядов, двоично-десятичный регистр частичных произведений, состоящий из ,1Т1 + U десятичных разрядов, и двоичнодесятичНый промежуточный регистр состо- яший иа tn + tX - 1 десятичных разрядов, причем выходы десятичных разрядов ре;гистра частичных произведений:, начиная с первого разряда, соеданены с одноймен-: ными входами десятичных разрядов пррме- жуточного регистра, отличающее- с я тем, что, Cj целью увеличения быстродействия, в него введены tl множительных блоков, каждый из которых состоит из сумматора результата, умножителя, сумматора тетрад и преобразователей старших и младших разрядов, причем первый вход сумматора результата соединен с выходом умножителя, а второй вход - с выходом сумматора тетрад, первый выход сумматора результата соединен со входом преобразователя старших разрядов, а второй выход 5 со входом преобразователя младших разрядов, первый вход умножителя i -того множительного блока соединен выходом первохх разряда регистра множителя, второ вход умножителя соединен с выходом i -то10 го разряда регистра множителя, первый

вход сумматора тетрад соединен с i -тым . выходом промежуточного регистра, второй вход сумматора тетрад соединен с выходом преобразователя старших разрядов L +1

15 ; множительного блока, выход преобразовате ля младших разрядов соединен с L+ i входом регистра частичных произведений, выход преобразователя старших разрядов :первого множительного блока соединен с

2Q ;первым входом регистра частичных произведений, выход р -того разряда промежу:точного регистра (tl + 16 р ТП + П - 1) соединен с р+1 разрядом регистра частичных произведений.

t I I t t t 1

а

Авторы

Даты

1975-04-25—Публикация

1972-04-24—Подача