31545215

Изобретение относится к области

вычислительной техники, а именно к двоичным и десятичным арифметическим и логическим устройствам для выполнения операций с фиксированной и плавающей запятой.

Целью изобретения является повышение быстродействия.

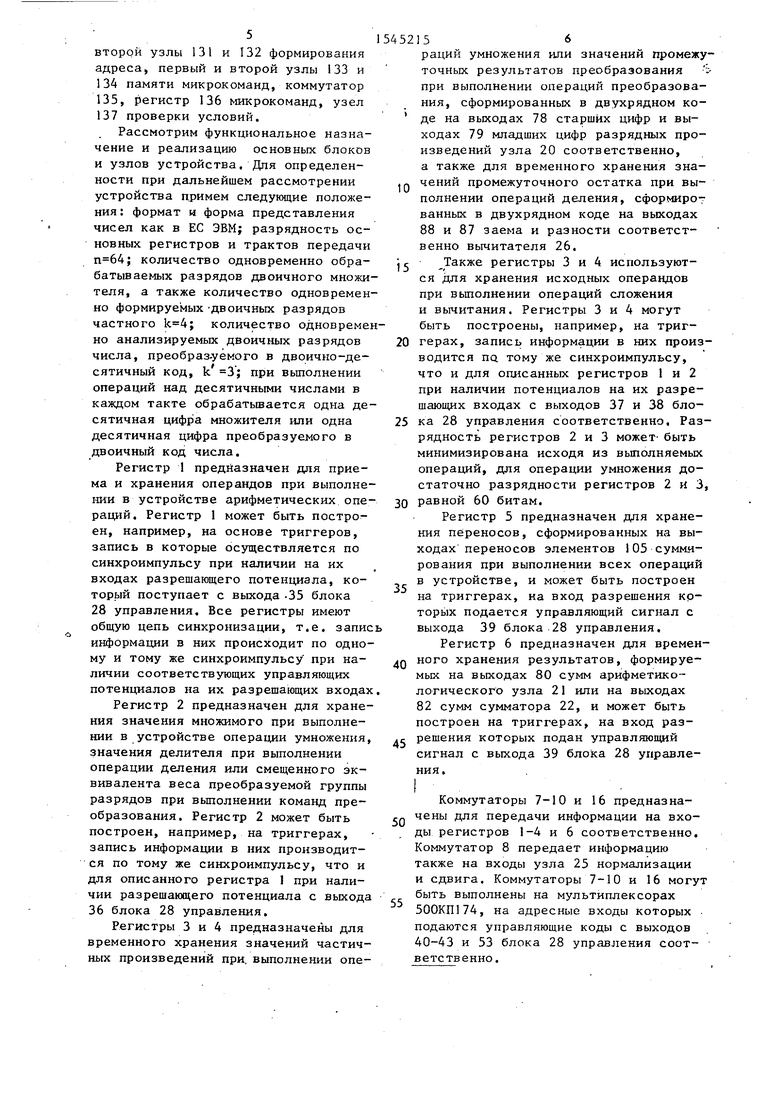

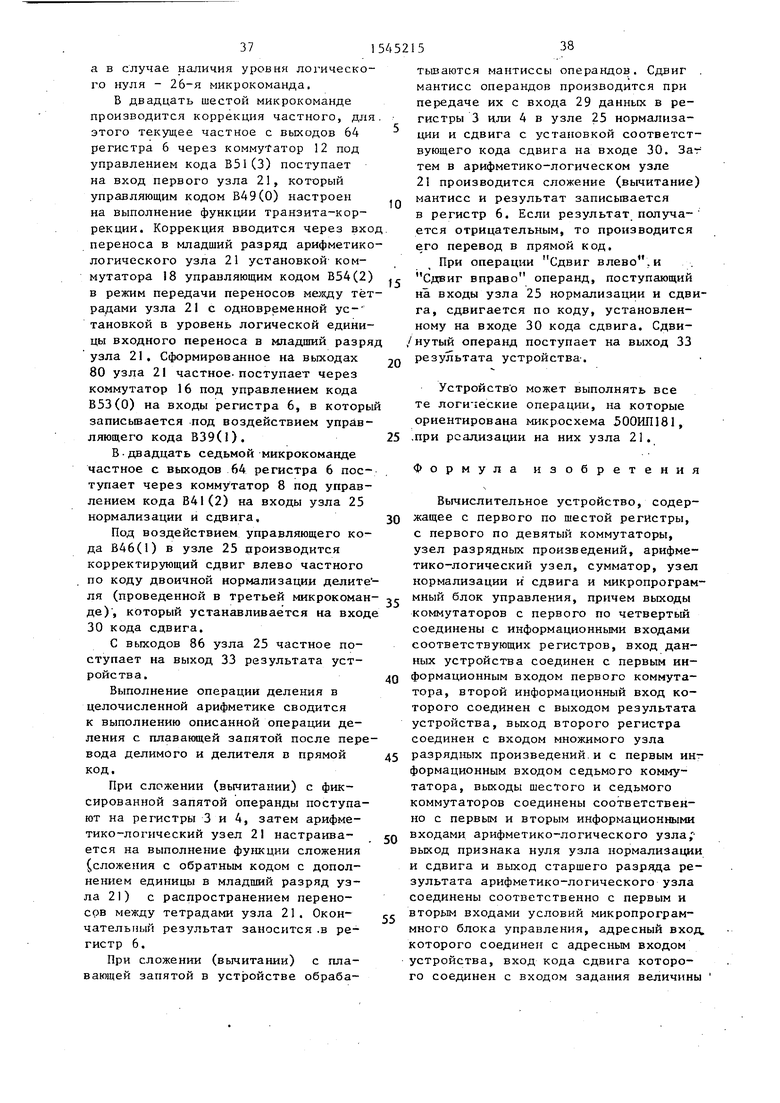

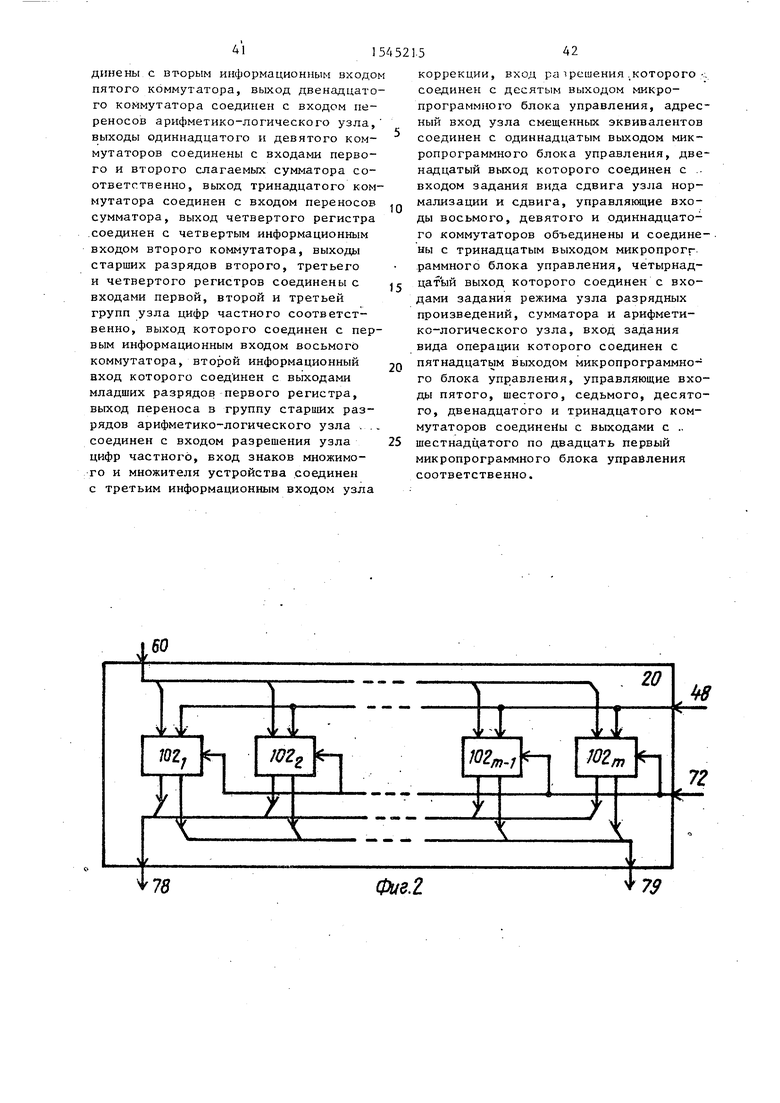

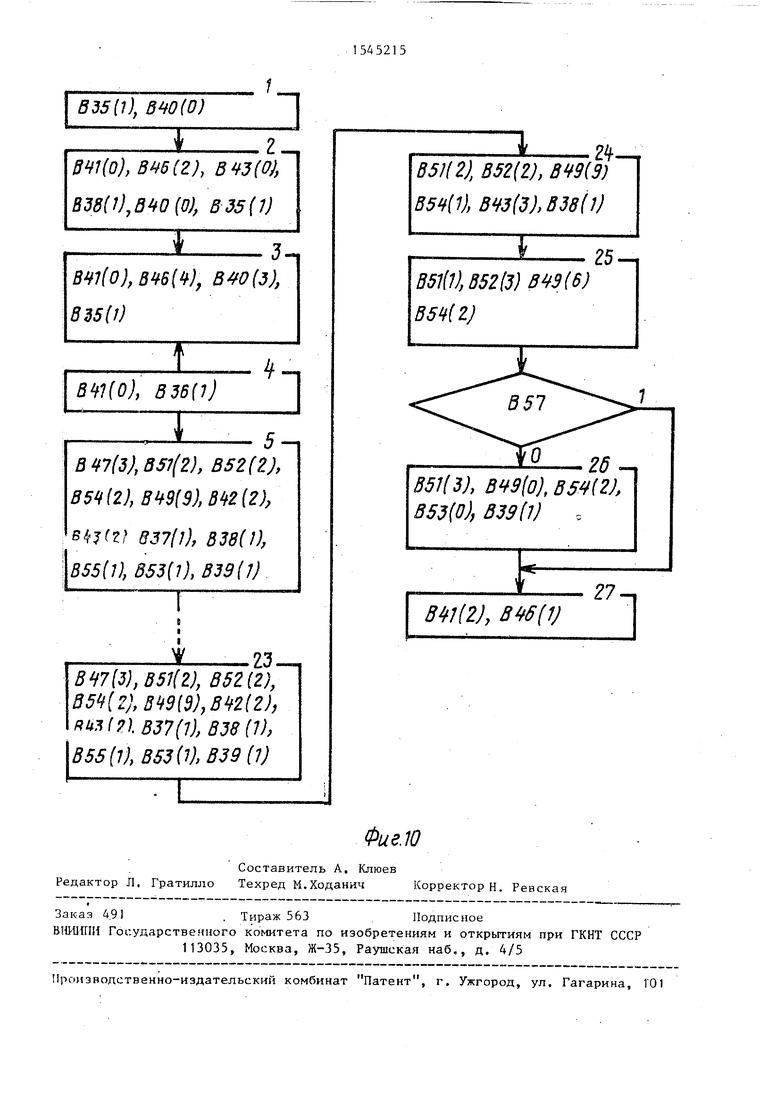

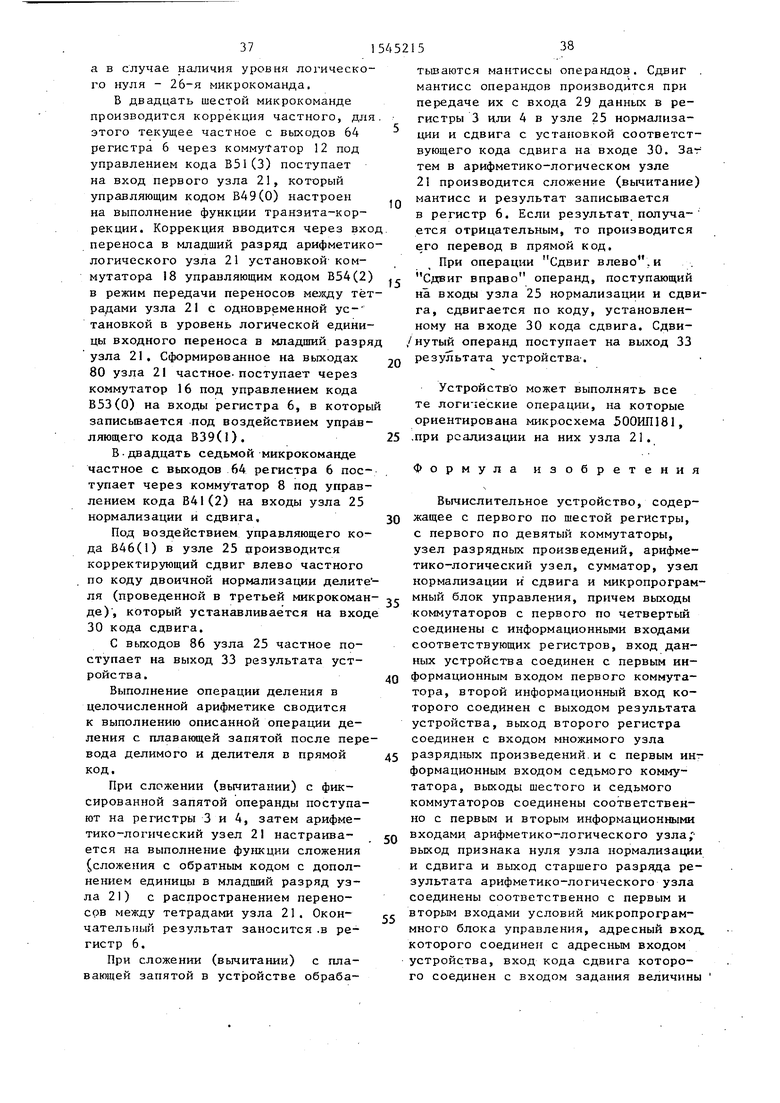

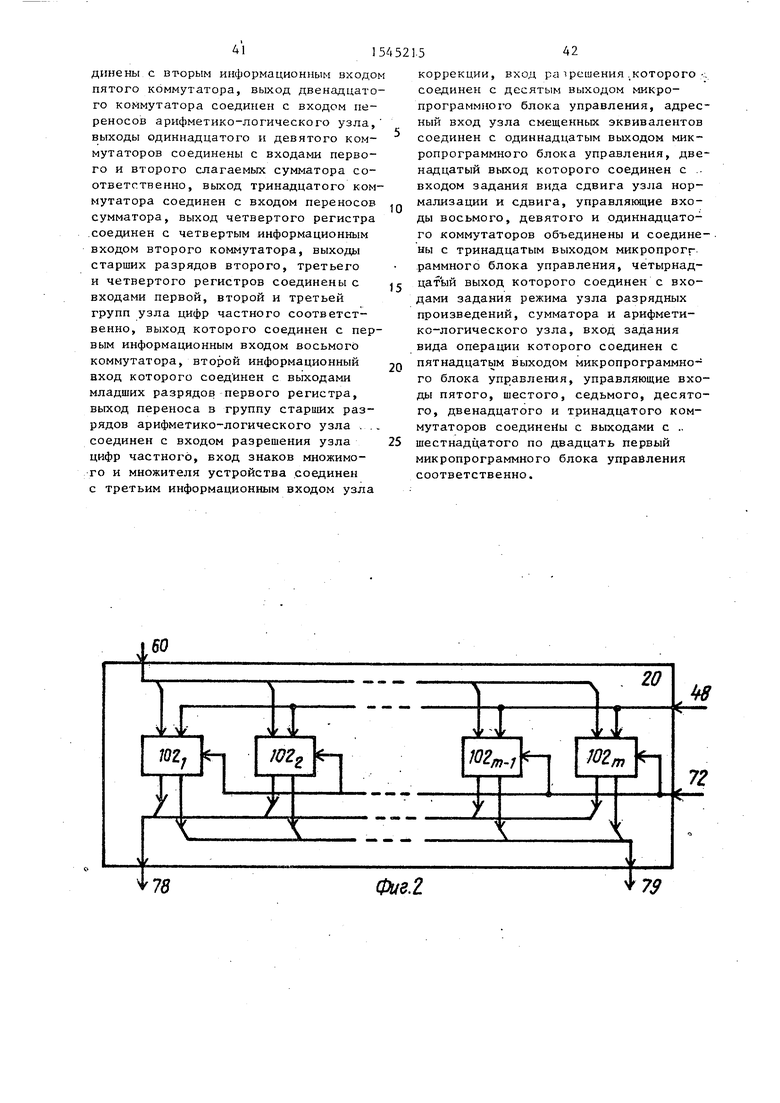

На фиг. 1 показана структурная схема вычислительного устройства; на фиг. 2 - структурная схема узла разрядных произведений; на фиг, 3 - организация передачи и сохранения переносов при совместной работе арифметико-логического узла и сумматора; на фиг. 4 - структурная схема узла коррекции; на фиг. 5 - структурная схема узла нормализации и сдвига; на фиг. 6 - структурная схема узла цифр частного; на фиг. 7 - структурная схема микропрограммного блока управления; на фиг, 8-10 - микропрограммы выполнения в устройстве операций двоичного умножения, преобразования двоичного кода в двоично-десятичный и двоичного деления соответственно .

Вычислительное устройство содержит (фиг. 1) регистры 1-6 с первого по шестой соответственно, коммутаторы 7-J9 с первого по тринадцатый соответственно, узел 20 разрядных произведений, арифметико-логический узел 21, сумматор 22, узел 23 коррекции, узел 24 смещенных эквивалентов, узел 25 нормализации и сдвига, вычнтатель 26, узел 27 цифр частного, микропрограммный блок 28 управления, вход 29 данных устройства, вход 30 кода сдвига устройства, вход 31 знаков множимого и множителя устройства, адресный вход 32 устройства, выход 33 результата устройства, выход 34 нормализации устройства, выходы 35-55 с первого по двадцать первый блока 28 управления соответственно, выход 56 признака нуля узла 25 нормализации и сдвига, выход 57 старшего разряда и выход 58 переноса в старшую группу разрядов арифметико-логического узла 21, выходы 59-64 регистров 1-6 соответственно, выходы 65-77 коммутаторо 7-15 соответственно, выходы 78 и 79 старших и младших цифр узла 20 разрядных произведений, выходы 80 и 81 результата и переносов арифметико- логического узла 21, выходы 82 и 83 сумм, п переносов сумматора 22, выход

0

5

0

5

0

5

0

5

0

5

84 узла 23 коррекции, выход 85 узла 24 смещенных эквивалентов, информационный выход 86 узла 25 нормализации и сдвига, выходы 87 и 88 разности и заема вычитателя 26, выход 89 узла 27 цифр частного, выходы 90 младших k разрядов, выходы 91 младших k разрядов старшей части, выходы 92 старших (n-k) разрядов и выходы 93 старших (n-k ) разрядов регистра 1 (где п - количество двоичных разрядов операнда, bi-kij , ), выходы 94

младших k разрядов коммутатора 11, входы 95 младших k разрядов входа 29 данных, выходы 96 старших (k+3) разрядов регистра 2, выходы 97 и 98 старших (k+4) разрядов регистров 3 и 4 соответственно, выходы 99 старших (n-k) разрядов регистра 4, выходы 100 младших (п-k+l) разрядов и выходы 101 старших (n-k) разрядов регистра 6, и выходы 1011 младших k разрядов суммы сумматора 22.

Узел 20 разрядных произведений содержит (фиг. 2) элементы 1021-Ю2Гп

умножения (т - I , где X - ближайшее целое, большее льбо равное X).

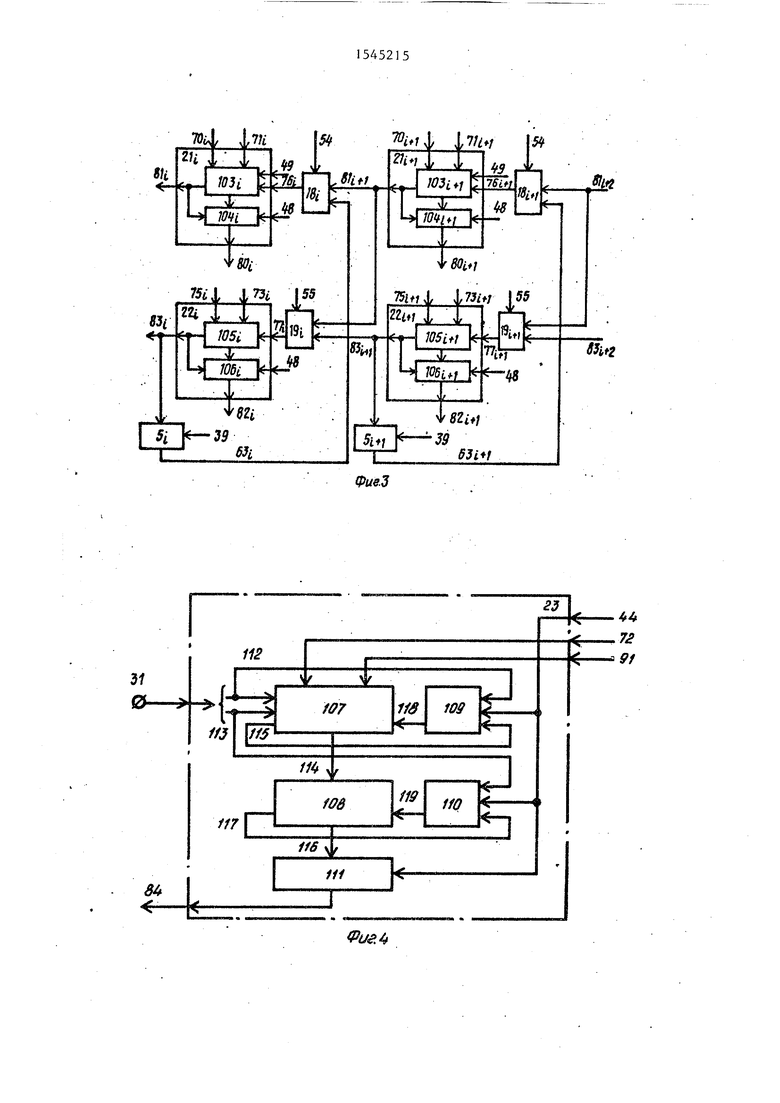

Арифметико-логический узел 21 содержит (фиг. 3) m арифметико-логических элементов 103, m корректоров 104,-104ГЛ.

Сумматор 22 содержит (фиг. 3) m элементов суммирования m корректо.ров 1061-106П).

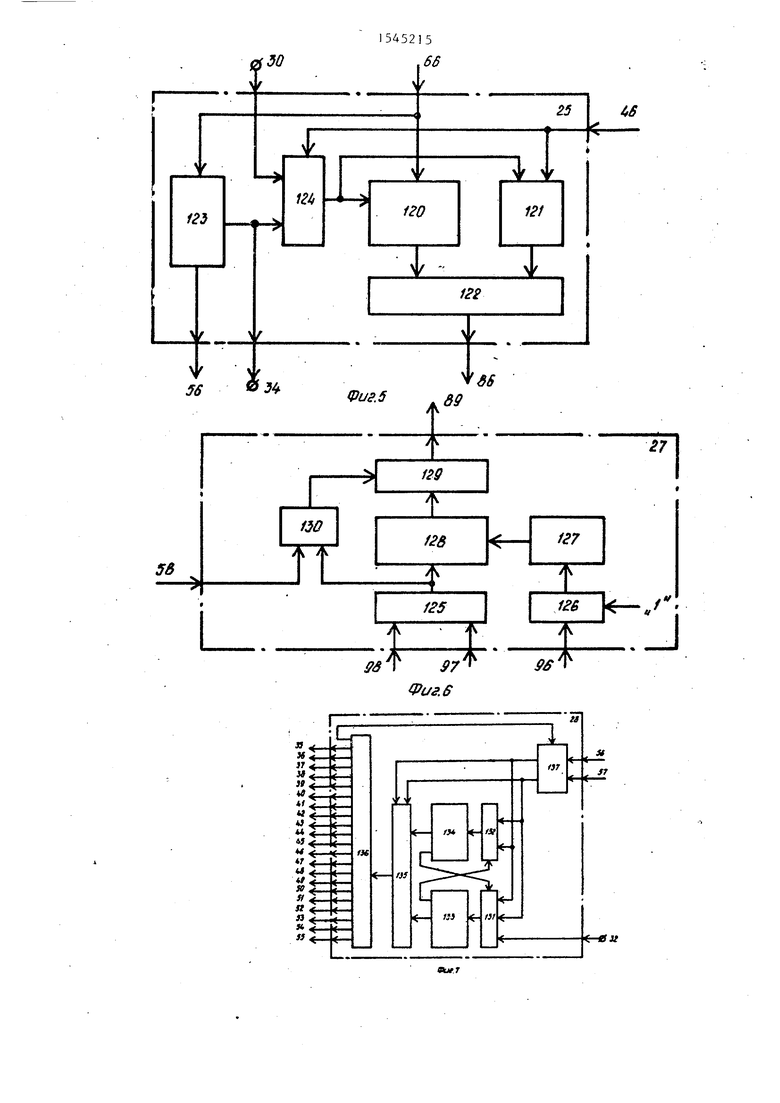

Узел 23 коррекции содержит (фиг.4) сумматоры 107 и 108, триггеры 109 и 110, регистр 111 коррекции, вход 112 знака множимого и вход 113 знака множителя, выходы 114 и 115 суммы и переноса сумматора 107, выходы 116 и 117 суммы и переноса сумматора 108 и выходы 118 и 119 триггеров 109 и 110 соответственно,

Узел 25 нормализации и сдвига содержит (фиг, 5) циклический сдвига- тель 120, формирователь 121 кода маски, формирователь 122 результата, нормализатор 123 и коммутатор 124.

Узел 27 цифр частного содержит (фиг. 6) сумматор 125, сумматор 126 округления, формирователь 127 обратной величины, умножитель 128, группу элементов И 129 и элемент 130 И-НЕ.

Микропрограммный блок 28 управления содержит (фиг. 7) первый и

5

второй узлы 131 и 132 формирования адреса, первый и второй узлы 133 и 134 памяти микрокоманд, коммутатор 135, регистр 136 микрокоманд, узел 137 проверки условий.

Рассмотрим функциональное назначение и реализацию основных блоков и узлов устройства. Для определенности при дальнейшем рассмотрении устройства примем следующие положения: формат форма представления чисел как в ЕС ЭВМ; разрядность основных регистров и трактов передачи количество одновременно обра- батываемых разрядов двоичного множителя, а также количество одновременно формируемых двоичных разрядов частного количество одновременно анализируемых двоичных разрядов числа, преобразуемого в двоично-десятичный код, k 3; при выполнении операций над десятичными числами в каждом такте обрабатывается одна десятичная цифра множителя или одна десятичная цифра преобразуемого в двоичный код числа.

Регистр 1 предназначен для приема и хранения операндов при выполнении в устройстве арифметических one- раций. Регистр 1 может быть построен, например, на основе триггеров, запись в которые осуществляется по синхроимпульсу при наличии на их входах разрешающего потенциала, который поступает с выхода .35 блока 28 управления. Все регистры имеют общую цепь синхронизации, т.е. запис информации в них происходит по одному и тому же синхроимпульсу при на- личии соответствующих управляющих потенциалов на их разрешающих входах

Регистр 2 предназначен для хранения значения множимого при выполнении в устройстве операции умножения, значения делителя при выполнении операции деления или смещенного эквивалента веса преобразуемой группы разрядов при выполнении команд преобразования. Регистр 2 может быть построен, например, на триггерах, запись информации в них производится по тому же синхроимпульсу, что и для описанного регистра 1 при наличии разрешающего потенциала с выхода 36 блока 28 управления.

Регистры 3 и 4 предназначены для временного хранения значений частичных произведений при выполнении опе0

2

5 5

156

раций умножения или значений промежуточных результатов преобразования при выполнении операций преобразования, сформированных в двухрядном коде на выходах 78 старших цифр и выходах 79 младших цифр разрядных произведений узла 20 соответственно, а также для временного хранения значений промежуточного остатка при выполнении операций деления, сформированных в двухрядном коде на выходах 88 и 87 заема и разности соответственно вычитателя 26.

Также регистры 3 и 4 используются для хранения исходных операндов при выполнении операций сложения и вычитания. Регистры 3 и 4 могут быть построены, например, на триггерах, запись информации в них производится по. тому же синхроимпульсу, что и для описанных регистров 1 и 2 при наличии потенциалов на их разрешающих входах с выходов 37 и 38 блока 28 управления соответственно. Разрядность регистров 2 и 3 может быть минимизирована исходя из выполняемых операций, для операции умножения достаточно разрядности регистров 2 и J, равной 60 битам.

Регистр 5 предназначен для хранения переносов, сформированных на выходах переносов элементов 105 суммирования при выполнении всех операций в устройстве, и может быть построен на триггерах, на вход разрешения которых подается управляющий сигнал с выхода 39 блока 28 управления.

Регистр 6 предназначен для временного хранения результатов, формируемых на выходах 80 сумм арифметико- логического узла 21 или на выходах 82 сумм сумматора 22, и может быть построен на триггерах, на вход разрешения которых подан управляющий сигнал с выхода 39 блока 28 управления.

Коммутаторы 7-10 и 16 предназначены для передачи информации на входы регистров 1-4 и 6 соответственно. Коммутатор 8 передает информацию также на входы узла 25 нормализации и сдвига. Коммутаторы 7-10 и 16 могут быть выполнены на мультиплексорах 500КП174, на адресные входы которых подаются управляющие коды с выходов 40-43 и 53 блока 28 управления соответственно .

Коммутатор 11 предназначен для передачи в старшие освобождающиеся разряды при выполнении операции сдвига на 4 бита или на 3 бита вправо информации с выхода регистра 1. Коммутатор 11 может быть выполнен на элементах И-ИЛИ или мультиплексорах (), на адресный вход которых подается управляющий код с выхода 50 блока 28 управления.

Коммутаторы 12 и 13 предназначены для передачи информации на входы первого и второго операндов арифметико- логического узла 21 соответственно и могут быть выполнены на мультиплексорах 500КП174, на адресные входы которых подаются управляющие коды с выходов 51 и 52 блока 28 управления соответственно.

Коммутатор 14 предназначен для подачи информации на вход множителя утла 20 разрядных произведений и может быть выполнен на элементах И-ИЛИ или, например, на мультиплексорах 500КП174, на адресные входы которых подается управляющий код с выхода 47 блока 28 управления.

Коммутаторы 17 и 15 предназначены для передачи информации на входы первого и второго слагаемых сумматора 22 соответственно и могут быть выполнены на элементах И-ИЛИ или, например, на двухвходовых регистрах 500ТМ173, на синхровходы которых

0

5

0

5

подается уровень логической единицы, а на адресные входы - управляющий код с выхода 47 блока 28 управления, что и на коммутатор 14.

Коммутаторы 18 и 19 предназначены для управления передачей переносов в арифметико-логическом узле 21 и сумматоре 22 соответственно, а также для организации совместной работы, причем они могут быть выполнены на элементах И-ИЛИ или, например, на двухвходовых регистрах 500TMI73 аналогично описанным коммутатора 4 17 и 15 с подачей на адресные входы управляющих кодов с выходов 54 и 55 блока 28 управления.

i

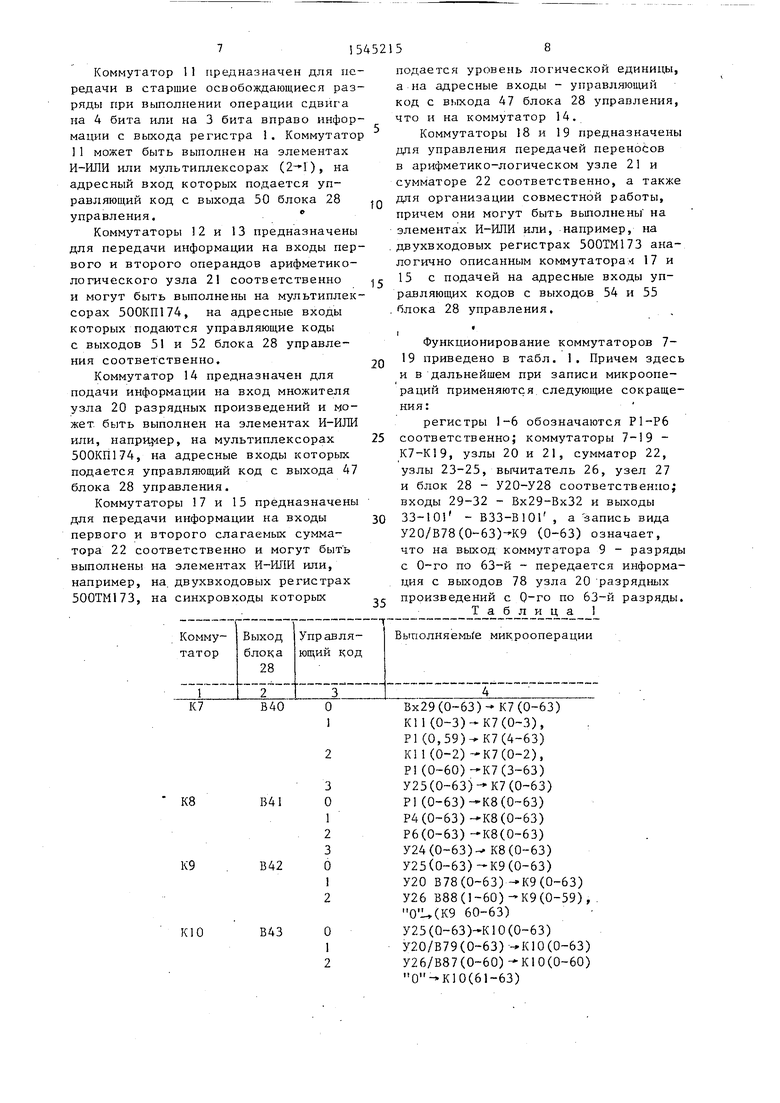

Функционирование коммутаторов 7- 19 приведено в табл. 1. Причем здесь и в дальнейшем при записи микроопераций применяются следующие сокращения:

регистры 1-6 обозначаются Р1-Р6 соответственно; коммутаторы 7-19 - К7-К19, узлы 20 и 21, сумматор 22, узлы 23-25, вычитатель 26, узел 27 и блок 28 - У20-У28 соответственно; входы 29-32 - Вх29-Вх32 и выходы 33-101 - ВЗЗ-В10Г , а запись вида У20/В78(0-63)-К9 (0-63) означает, что на выход коммутатора 9 - разряды с 0-го по 63-й - передается информация с выходов 78 узла 20 разрядных произведений с 0-го по 63-й разряды. Таблица

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1285604A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| Устройство для умножения | 1982 |

|

SU1229758A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для деления | 1985 |

|

SU1322264A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

Изобретение относится к вычислительной технике и может быть применено для выполнения арифметических операций над двоичными числами. Особенно эффективно его использование в средних ЭВМ. Целью изобретения является повышение быстродействия. Устройство содержит регистры 1 - 6, коммутаторы 7 - 19, узел 20 разрядных произведений, арифметико-логический узел 21, сумматор 22, узел 23 коррекции, узел 24 смещенных эквивалентов, узел 25 нормализации и сдвига, вычитатель 26, узел 27 цифр частного и микропрограммный блок 28 управления. 10 ил., 2 табл.

B4I

В42

В43

3 О I

2 3 О I 2

О

1

2

Р1 (0,59)- К7(4-63) К1 1 (0-2) К7(0-2), Р1 (0-60) -К7(3-63) У25(0-63)-К7(0-63) Р1 (0-63)(0-бЗ) Р4(0-63) (0-63) Р6(0-63) -К8(0-63) У24(0-63)- К8(0-63) У25(0-63) -К9(0-63) У20 В78(0-63) (0-63) У26 В88(1-60)(0-59), 01(К9 60-63) У25(0-63)-К10(0-63) У20/В79(0-63) -КЮ(О-бЗ) У26/В87(0-60) 0(0-60) (61-63)

В50 B5I

В52

3 О 1

О 1 2 3 О 1 2

В47

В47

В53

В47

В54

В55

О 1 2

3

0-2

3

О 1 0-2

О 1

2 О

Каждый из элементов 102 -1021С умножения узла 20 разрядных произведений осуществляет умножение соответствующей тетрады множимого., поступающей с выходов 60 регистра 2, на тетраду множителя, поступающую с выходов 72 коммутатора 14. В зависимости от управляющего потенциала, поступающего с выхода 48 блока 28 управления на вход режима узла 20, на выходах 78 старших цифр и выходах 79 младших цифр разрядных произведений появляется результат умножения либо в двоичном, либо в двоично-десятичном коде. Предполагается, что потенциал логической единицы на выходе 48 блока 28 управления обеспечивает работу устПродолжение табл.1

У21 (0-63)- КЮ(О-бЗ)

У22(60-63)-К1 1 (0-3)

Вх29(60-63)- KI1(0-3

У25(0-63) К12(0-63)

Р4(0-63)-К12(0-63)

РЗ(0-63)-К12(0-63)

Р6(0-63)-К12(0-63)

У25(0-63)- К13(0-63)

Р4 (0-63) К1 3(0-63)

Р4(0-59) -К13(4-63),

3(0-3)

Р2 (0-59)-К13(1-60),

(0, 61-63)

(0-3)

Р1 (60-63)К14(0-3)

PI(61-63)-tKI4(l-3),

(0)

У27(0-3)(0-3)

У21 (0-63) К15(0-63)

(0-59),

К14(0-3) -К15(60-63)

У21(0-63) -К16(0-63)

У22(0-63)-К 16(0-63

Р6(0-59)(),

У23(0-3)(0-3)

Р6(3-63)(0-60),

(61-63)

Р5(0-15) (0-15)

У21/В81 (1-15) -К18(0

)

У21/В81 ()-15)-К18(0

(J5)

У21/В81 (J-15)-KI9(0

(J5)

У22/В83(1-15) (0

0 - К19(15)

5

0

5

ройства в десятичной системе счисления, а потенциал логического нуля - его работу в двоичной системе .счисления. Элементы I02f-I0216 умножения целесообразно реализовать в виде ППЗУ. В этом случае младшие или старшие цифры разрядных произведений на выходах элементов 102,-1021Ь умножения могут формироваться уже скорректированными на +6 без каких-либо дополнительных аппаратурных затрат. Такая коррекция двоично-десятичного кода произведения необходима для формирования в дальнейшем в арифметико-логическом узле 21 и сумматоре 22 десятичного результата. В дальнейшем для определенности принято

И1

то, что корректирующая гюпраька +6 вводится в старшие цифры разрядных произведений. Поскольку в рассматриваемом варианте приняты разрядность операндов и формат данных такими же, как в ЕС ЭВМ, го узел 20 разрядных произведений может содержать только 15 элементов умножения, и тогда в младшие цифры разрядных произведений должна вводиться младшая кулевая тетрада, а в старшие цифры разрядных произведений - младшая либо нулевая тетрада при выполнении операций в двоичной арифметике (на управляющем выходе 48 блока 28 управления установлен уровень логического нуля), либо код 6 при выполнении операций в десятичной арифметике (на управляющем выходе 48 блока 28 управления установлен уровень ло- ,гической едьпицы).

Арифметико-логический узел 21 предназначен для выполнения арифметических и логических операций над операндами, поступающими на его входы первого и второго операндов с выходов 70 и 71 коммутаторов 2 и 13 соответственно.

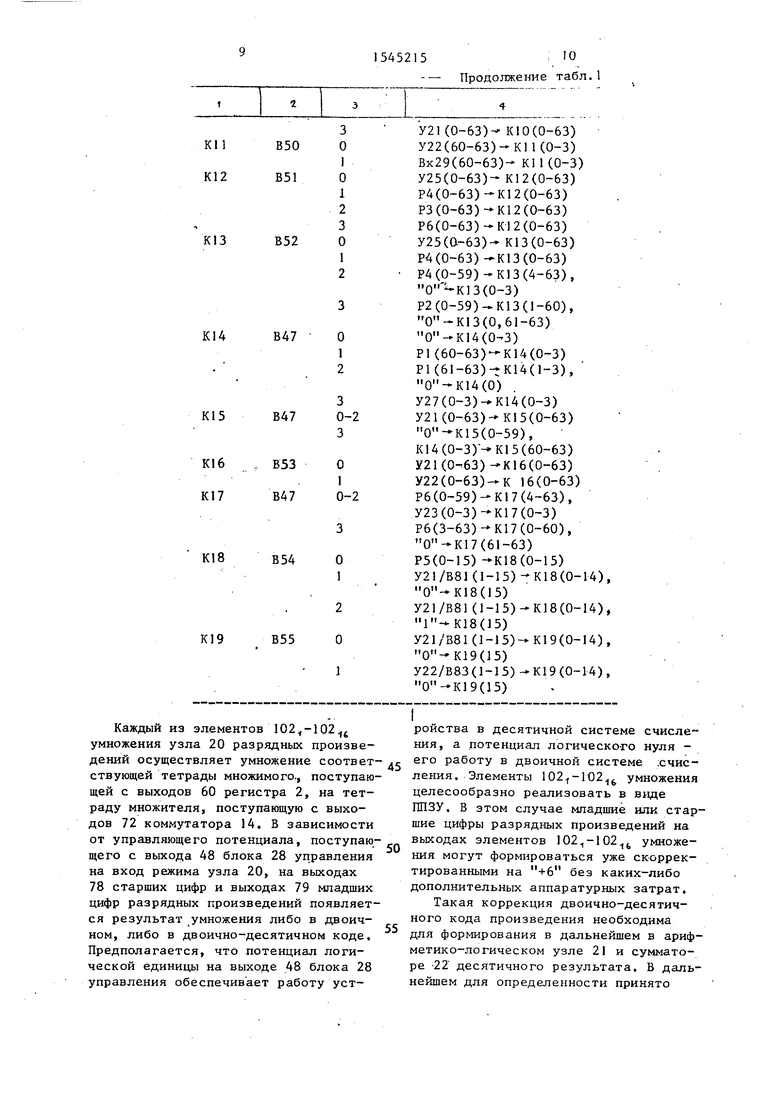

Операции над многоразрядными (64-битными) операндами осуществляются потетрадно на арифметико-логических элементах I031-I03f6, причем информация на входы переносов элементов I 03 f-I 03 поступает с. выходов

76 коммутатора 18. Арифметико-логические элементы 103,-103, могут быть выполнены, например, на микросхемах 500ИП181, на управляющие вход которых поступает управляющий код с выхода 49 блока 28 управления. В далнейшем будем считать, что код 9 соответствует формированию результата на выходах узла 21, равного сумме двух операндов, а код 6 - фор- мированию разности двух операндов при наличии входного переноса в младший разряд,код О формирует результат, равный операнду, поступающему на входы первого операнда, код С формирует результат в виде истинного нуля при наличии входного переноса в младший разряд. Кроме этих кодов допускается применение любого другог кода в соответствии с работой микросхемы 500КП181.

При выполнении в устройстве двоичных операций корректоры 104 ,-104 арифметико-лбгического узла 21 на

0

5

52

.

0

5

0

Q 5

0

5

1512

страиваются управляющим потенциалом О с выхода 48 блока 28 управления на передачу информации на выходы 80 результата транзитом.

При выполнении десятичных операций управляющим потенциалом 1 на выходе 48 блока 28 управления корректоры настраиваются на режим коррекции, при этом при наличии на соответствующих выходах 81 переносов арифметико-логических элементов I03t-I031t уровня логической единицы осущес вляется коррекция результата на +6, в противном случае передача информации через корректоры I04.,-104ft осуществляется транзитом. Корректоры 104,-10414 могут быть выполнены на элементах И, ИЛИ или, например, на одноразрядных двоичных сумматорах 500ИМ180, на первые входы которых поступает информация с выходов арифметико-логических элементов 103.,-103U, а на вторых входах формируется код коррекции 6 в случае одновременного поступления уровней логической единицы с вьсхода 48 блока 28 управления и с выхода переноса соответственно элементов 103,- ЮЗП .

Сумматор 22 предназначен для формирования промежуточных и окончательных результатов операций умножения и преобразования, а также для формирования частного при выполнении операции деления.

Информация на входы первого и вто- плго слагаемых сумматора 22 поступает с выходов коммутаторов 17 и 15 соответственно. Операция суммирования многоразрядных (64-битных) операндов осуществляется потетрадно на элементах I05t-I051t суммирования, причем информация на входы переносов поступает с выходов коммутатора 19. Элементы суммирования могут быть выполнены на микросхемах 500ИП181, на управляющие входы которых поступает код 6.

При выполнении в устройстве двоичных операций корректоры 106,-Юб, сумматора 22 настраиваются управляющим потенциалом О с выхода 48 блока 28 управления на передачу информации с выходов элементов 105,-105U суммирования на выходы 82 суммы транзитом. При выполнении десятичных операций управляющим потенциалом 1 на выходе 48 блока управления корректоры

1061-106U }1астраиваются на режим коррекции, причем при наличии на соответствующих выходах 83 переносов элементов lOSj-lOS суммирования уровня логического нуля осуществляет- ся коррекция результата на -6, в противном случае передача информации через корректоры 1 06., -106f осуществляется транзитом, корректоры 106.,- 10614 могут быть выполнены на элементах И, ИЛИ, на микросхемах 500ИП181 или, например, на одноразрядных двоичных сумматорах 500ИМ180, на первые входы которых поступает информация с выходов элементов i05jj суммирования, а на вторых входах формируется код коррекции 10 (вычитание 6 заменяется прибавлением 10) в случае поступления уровня логической единицы с выхода 48 блока 28 управления и уровня логического нуля с выходов переносов соответствующих элементов 105.,-105,. суммирования.

Рассмотрим организацию передачи и сохранения переносов при совместной работе арифметико-логического узла 2 и сумматора 22 (фиг. 3).

При установке управляющих кодов Г1 на выходах 54 и 55 блока 28 управления коммутаторы 18 и 19 соответственно настраивают арифметико-логический узел 21 и сумматор 22 на раба- ту с распространением переносов, т.е. перенос с выхода арифметико-логического элемента 103,-+1 передается через коммутатор 18 (i-й элемент коммутирования) на вход переноса арифметико-логического элемента 103 и т.д. Аналогично, выходной перенос элемента 105. ( суммирования через коммутатор 19 (1-й элемент коммутирования) передается на вход переноса элемента 1051 суммирования.

В этом случае осуществляется независимая работа арифметико-логического узла 21 и сумматора 22. При установке управляющего кода 2 на выходе 54 блока 28 управления на вход переноса младшего арифметико-логического элемента ЮЗП подастся уровень логической единицы, в остальном же работа арифметико-логического узла 21 аналогична описанной.

При установке управляющих кодов О на выходах 54 и 55 блока 28 управления арифметико-логический узел 21 н сумматор 22 настраиваются на

выполнение котетрадных операций. В .-. этом случае на входы переносов арифметико-логических элементов 103. и 103,-, поступают значения переносов с выходов 63 регистра 5 (i- и (i+lj-x триггеров соответственно, информация в которые была занесена в предыдущем такте или ранее. Значение выходного переноса арифметико- логического элемента 103, поступает через коммутатор 19 на вход переноса элемента 105. суммирования, на вход переноса элемента 105 суммирования значение переноса поступает с выхода переноса арифметикологического элемента 103t 7

Значе20

-1 ., 25

0 о 45

5Q

5

ния выходных переносов элементов 105- и заносятся в i- и (i+ I )-e триггеры регистра 5 соответственно ; и в следующем такте вновь подаются на вход арифметико-логических элементов 103. и I03itt соответственно. Таким образом, осуществляется сдвиг вправо на 4 бита значений переносов, соответствующий сдвигу вправо суммы частичных произведений при выполнении операции умножения.

Узел 23 коррекции предназначен для формирования и введения корректирующей поправки параллельно с выполнением операции умножения в дополнительных кодах. Узел 23 коррекции может быть реализован различными методами и средствами аналогично известному устройству.

Управление сумматором 107 осуществляется с входов 112 знака множимого и 113 знака множителя, причем наличие уровня логического нуля на входе 112 знака множимого (множимое положительно) и/или на входе 113 знака множителя (множитель положителен) блокирует передачу на выходы сумматора тетрады множителя с выходов 72 коммутатора 14 и/или тетрады множимого с выходов 91 младших разрядов старшей части регистра 1 соответственно. Триггеры 109 и 110 предназначены для временного хранения значений выходных переносов сумматоров 107 и 108 соответственно или на на-т чальном этапе формирования корректирующей поправки, знаков сомножителей, причем наличие уровня логической единицы на выходе 44 блока 28 управления настраивает триггеры 109 и 110 на запись выходных переносов сумматоров 107 и 108 соответственно

и регистр 111 коррекции на запись тетрады корректирующей поправки, и противном случае в триггеры 109 и 110 заносятся знаки сомножителей с входов 112 и 113 соответственно, а в регистр 111 коррекции заносятся нули.

Узел 24 смещенных эквивалентов предназначен для формирования в устройстве смещенных двоичных и двоично- десятичных эквивалентов весов преобразуемых групп разрядов. Формирование смещенных эквивалентов связано со следующим. Выполнение операции умножения требует сдвига вправо сум- мы частичных произведений относительно очередного частичного произведения. При выполнении операции преобразования суммирование очередного частичного результата (произведения преобразуемой группы разрядов на соответствующий эквивалент ее веса) с суммой частичных результатов производится без сдвига.

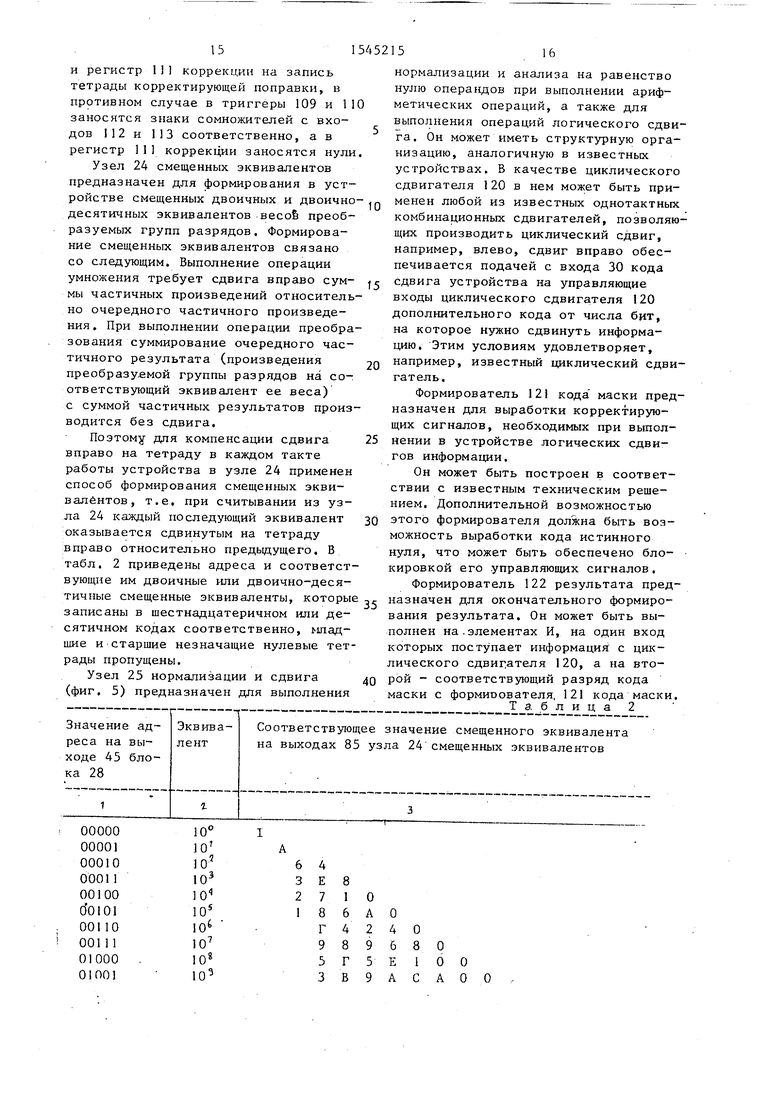

Поэтому для компенсации сдвига вправо на тетраду в каждом такте работы устройства в узле 24 применен способ формирования смещенных эквивалентов, т.е. при считывании из узла 24 каждый последующий эквивалент оказывается сдвинутым на тетраду вправо относительно предыдущего. В табл. 2 приведены адреса и соответствующие им двоичные или двоично-десятичные смещенные эквиваленты, которые записаны в шестнадцатеричном или десятичном кодах соответственно, младшие и старшие незначащие нулевые тетрады пропущены.

Узел 25 нормализации и сдвига (фиг. 5) предназначен для выполнения

10° 10

ю

103 10 10s

10

i

107

ю8

10Э

3B9ACAOO

Q 0

0

5

0

5

нормализации и анализа на равенство нулю операндов при выполнении арифметических операций, а также для выполнения операций логического сдвига. Он может иметь структурную организацию, аналогичную в известных устройствах. В качестве циклического сдвигателя 120 в нем может быть применен любой из известных однотактных комбинационных сдвигателей, позволяющих производить циклический сдвиг, например, влево, сдвиг вправо обеспечивается подачей с входа 30 кода сдвига устройства на управляющие входы циклического сдвигателя 120 дополнительного кода от числа бит, на которое нужно сдвинуть информацию. Этим условиям удовлетворяет, например, известный циклический сдви- гатель.

Формирователь 121 кода маски предназначен для выработки корректирующих сигналов, необходимых при выполнении в устройстве логических сдвигов информации.

Он может быть построен в соответствии с известным техническим решением. Дополнительной возможностью этого формирователя должна быть возможность выработки кода истинного нуля, что может быть обеспечено блокировкой его управляющих сигналов.

Формирователь 122 результата предназначен для окончательного формирования результата. Он может быть выполнен на. элементах И, на один вход которых поступает информация с циклического сдвигателя 120, а на второй - соответствующий разряд кода

маски с формиоователя, 121 кода маски. Таблица

Примечание.

Значения смещенных эквивалентов, хранимых в узле 24 по адресам от 00000 до 011)1, представленные в шестнадцатеричной системе счисления, выдаются в двоичном коде, а значения смещенных эквивалентов, хранимых в узле 24 по адресам от 10000 до 11011, представленные в десятичной системе счисления, выдаются в двоично-десятичном коде.

Нормализатор 123 служит для выработки кода нормализации поступающей информации и признака равенства ее нулю. В качестве нормализатора может быть применен известный нормализатор .

Коммутатор 124 предназначен для передачи на управляющий вход циклического сдвигателя 120 кода сдвига, поступающего на вход 30 в прямом коде (для сдвига влево) или и дополнительном коде (для сдвига вправо), или же кода нормализации (двоичной или шестнадцатеричной) в зависимости от уп- равляющего кода на выходе 46 блока 28 управления.

Будем считать, что при коде О на выходе 46 блока 28 управления узел 25 нормализации и сдвага вырабатывает код истинного нуля на выходе, при коде 1 и 2 выполняется логический сдвиг информации, поступающей с выходов 66 коммутатора 8, влево и вправо соответственно, а при кодах 3 и 4 выполняется сдвиг влево информации, поступающей с выхоПродолжение табл.2

5

0

5

0

5

дов 66 коммутатора 8 по коду нормализации шестнадцатеричной и двоичной соответственно.

Вычитатель 26 предназначен для вычитания из значения текущего остатка, полученного на выходах 80 арифметико-логического узла 21 в однорядном коде, значения произведения следующей цифры частного на делитель, подаваемого в двухрядном коде на входы вычитаемого и заема вычитателя 26 с выходов 78 и 79 старших и младших цифр соответственно разрядных произведений узла 20. Вычитатель 26 формирует остаток в двухрядном коде в виде разности и заема, которые записываются в конце такта в регистры 4 и 3 соответственно, причем в следующем такте для приведения нового текущего остатка к однорядному коду требуется выполнить функцию вычитания заема из разности на арифметико-логическом узле 21.

Вычитатель 26 может быть выполнен на одноразрядных двоичных вычитате- лях. Кроме этого, вычитатель 26 можно выполнить, например, на одноразрядных двоичных сумматорах 500ИМ180, но при этом необходимо заменить операцию вычитания на операцию сложения в дополнительных кодах. В этом случа информация на выходы вычитаемого и заема с выходов 78 и 79 старших и младших разрядных произведений узла

20должна подаваться в дополнитель- ном коде, т.е. информацию необходимо проинвертировать и прибавить единицу

в младшие разряды вычитаемого и заема. Добавление единицы ц младшие разряды можно выполнить, например, вве- дением единицы в младший разряд текущего остатка в регистр 3 на коммутаторе 9 н и ведением единицы через вход переноса арифметико-логического узла 21. При применении одноразрядны двоичных сумматоров для приведения нового текущего остатка к однорядному коду требуется выполнить функцию сложения значений заема и разности н арифметико-логическом узле 21.

В узле 27 цифр частного (фиг. 6) осуществляется деление значения определенного числа старших разрядов двухрядного кода текущего остатка, сформированного на выходах 97 и 98 старших разрядов регистров 3 и 4 соответственно, на округленное значени определенного числа старших разрядов делителя, поступающих с выходов 96 старших разрядов регистра 2. В ре- зультате этого на выходах 89 узла 27 цифр частного формируется значение k очередных бит частного, которое (за исключением случая, когда на выходе 58 переноса в старшую группу разрядов арифметико-логического узла

21образован сигнал логической единицы) либо равно истинному значению k бит частного, либо меньше его на единицу младшего разряда с весом 2 (U-0 t узел 27 цифр частного может быть реализован различными методами

и средствами. На фиг. 6 показан один из наиболее предпочтительных вариантов реализации узла 27, в котором деление усеченных чисел осуществляется умножением значения малоразрядног делимого на значение старших разрядо обратной величины малоразрядного делителя. В этом случае на входы делителя узла 27 подаются старших разрядов делителя с выходов 96 старших разрядов регистра 2, а на входы делимого подаются старших раз

j Q 5

0 5

5

рядов двухрядного кода текущего остатка с выходов 97 и 98 старших разрядов регистров 3 и 4 соответственно. На сумматоре 125 формируется однорядный код 8-ми старших разрядов текущего остатка, который поступает на первый вход умножителя 128. На сумматоре 126 округления производится округление старшей части делителя путем прибавления единицы к младшему разряду старшей части. Значение старшей части округленного делителя поступает на вход формирователя 127 обратной величины, на выходах которого формируется старших разрядов обратной величины делителя (один разряд - слева от запятой, остальные - справа), которые поступают на второй вход умножителя 128. На выходах старших разрядов умножителя 128 формируются при этом значения очередных двоичных разрядов частного (один разряд - слева от запятой, остальные - справ.чJ , которые либо равны истинному значению очередных двоичных разрядов частного или меньше его на единицу младшего разряда с весом 2-(- 2 3.

Группа элементов И 129 предназначена для устранения ошибки в определении цифр частного при отбрасывании младших разрядов текущего остатка. Если значения всех старших разрядов равны единицам и значение переноса в группу старших разрядов также равно единице, то истинным значением старших разрядов остатка является нулевая комбинация, однако на выходе сумматора 125 формируется неверный код старших разрядов текущего остатка. В этом случае на выходе элемента 130 И-НЕ формируется сигнал логического нуля, являющийся сигналом блокировки группы элементов И 129, и на выходах 89 узла 27 цифр частного устанавливается нулевая комбинация цифр частного, хотя на выходах умножителя 128 формируется ненулевой код.

I

Блок 28 управления координирует

работу всех узлов и элементов устройства при выполнении всех операций. Предполагается, что условия, которые вырабатываются в текущей микрокоманде, влияют на выбор следующей,время считывания следующей микрокоманды не увеличивает время выполнения операции в целом. Этим условиям

удовлетворяет известный блок управления .

Блок 28 управления (фиг. 7)работает следующим образом. Первый и второй узлы 131 и 132 формирования адреса формируют адреса для первого и второго узлов 133 и 134 памяти микрокоманд соответственно, из которых одновременно считываются две микрокоманды и поступают на входы коммутатора 135. В соответствии с выработанными условиями на выходе 56 признака нуля узла 25 нормализации и сдвига и на выходе 57 старшего разряда арифметико-логического узла 21. узел 137 проверки условий вырабатывает управляющий код для узлов 131 и 132 формирования адреса и для коммутатора 135, кдт орый пропускает на входы регистра 136 микрокоманд следующую микрокоманду.

На время выполнения операции в устройстве оказывает влияние время выполнения каждой микрокоманды, поэтому предполагается, что в блоке 28 управления должна быть предусмотрена возможность управления длительностью такта микрокоманд.

Опишем теперь работу вычислительного устройства (фиг. 1). Выполнение любой операции в устройстве начинается с подачи двух предварительных синхроимпульсов по цепи синхронизаци для выбора первой микрокоманды в блоке 28 управления. По ш,р:зому синхроимпульсу в первый узел 131 формирования адреса заносится начальный адрес выполняемой микропрограммы с адресного входа 32. Исходное состояние регистра 136 микрокоманд настраивает коммутатор 135 на передачу микрокоманды с выхода первого узла 133 памяти микрокоманд и по второму синхроимпульсу в регистр 136 микрокоманд заносится начальная микрокоманда, а в первом и втором узлах 131 и 132 формирования адреса формируются адреса следующих микрокоманд.

По окончании микропрограммы регистр 136 микрокоманд переводится в исходное состояние.

В дальнейшем управляющие коды, формируемые па выходах 35-55 блока 28 управления, будем записывать в ви- де BN(1), где N 35-55 и определяет обозначение выхода блока 28 управления, а 1 - собственно управляющий

4Q 45 д

0

5

0

5

5

код, выработанный на соответствующем, выходе N (значения управляющих кодов и соответствующие им микрооперации описаны выше).

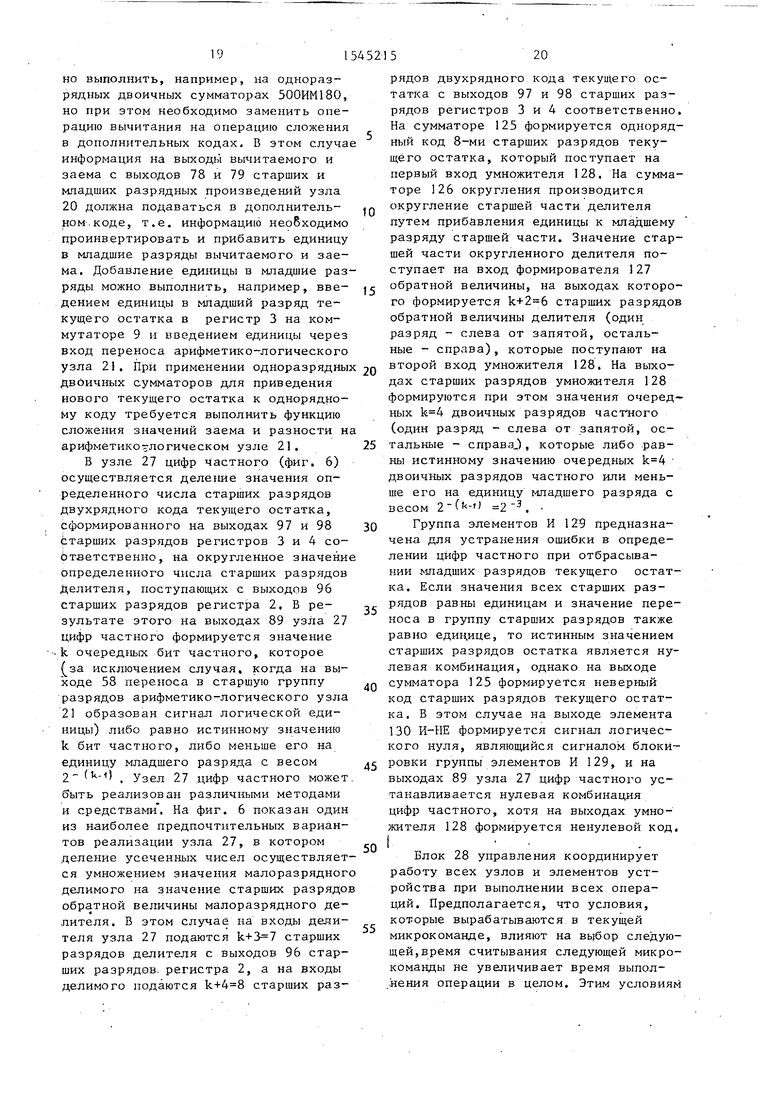

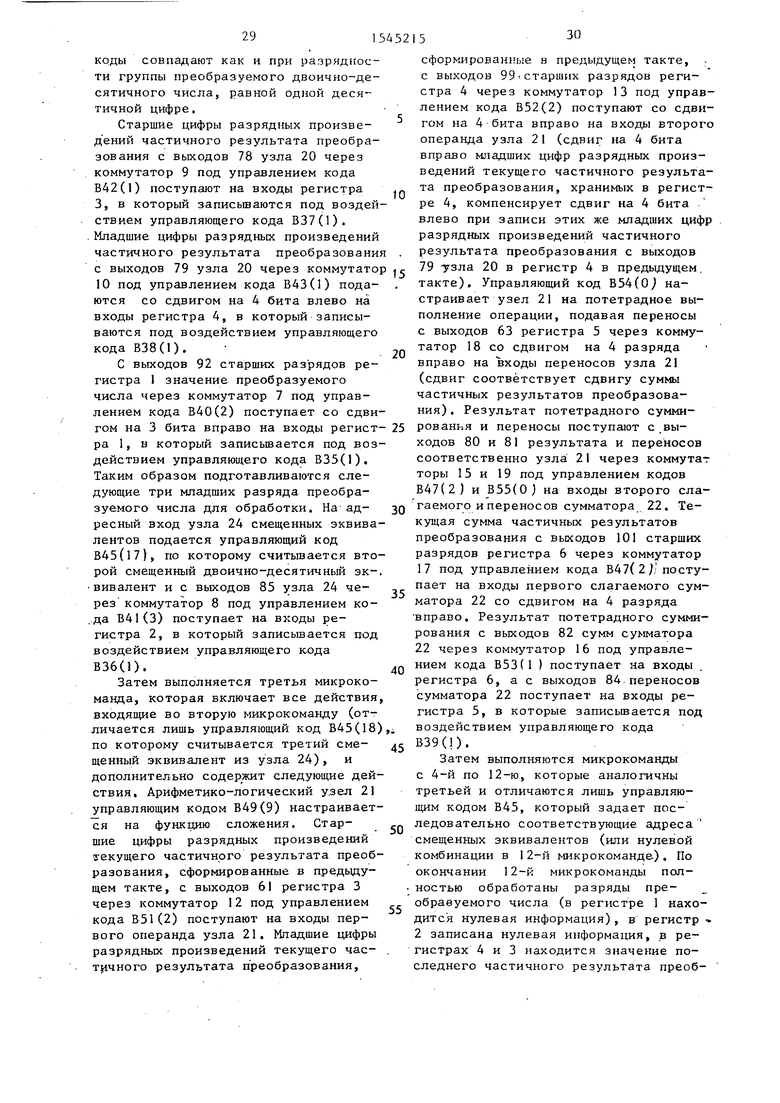

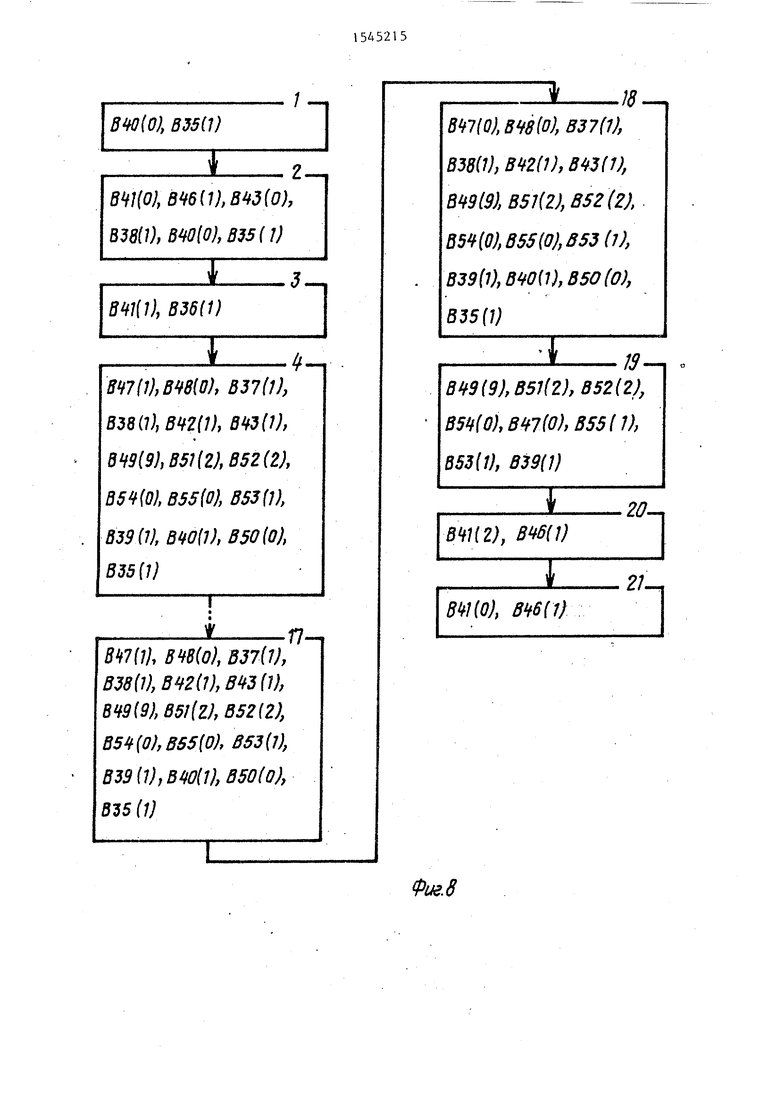

Рассмотрим выполнение операции умножения, микропрограмма которой приведена на фиг. 8. Умножение выполняется с младших разрядов множителя (одновременно обрабатываются 4 бита множителя) со сдвигом суммы частичных произведений вправо. Мантиссы длинных операндов в ЕС ЭВМ имеют 14 тетрад. Предположим, что мантиссы операндов поступают на вход 29 данных устройства нормализованными и выравненными но правой границе.

Для получения прл.чмльноп результата при выполнении операции умножения регистры 5 и 6 должны быть предварительно обнулены. Обнуление чтих регистров можно совместить с выполнением первой микрокоманды каждой микропрограммы выполнения операции умножения. Для этого первая микрокоманда должна содержать следующие управляющие коды: В46(0), под воздействием которого формируется нулевая информация на выходах 86 узла 25; B5I (О) и В52 (О), под управлением которых нулевая информация с выходов 86 узла 25 поступает на входы первого и второго операндов узла 21 через коммутаторы 12 и 13 соответственно; В54(1), который поступает в арифметико-логический узел 21 на выполнение функции сложения под управлением кода В49(9) с распространением переноса, одновременно устанавливая входной перенос Q в младший разряд узла 21 равным нулю; В53(0), который пропускает на входы регистра 6 с выходов 80 результата узла 21 нулевую информацию через коммутатор 16; В47(0) и В55(0), которые 5 позволяют сформировать на выходах 83 переносов сумматора 22 нулевую информацию независимо от информации, поступающей на входы первого слагаемого сумматора 22 с выходов регистра 6. Выполнение каждой микрокоманды (такта) завершается подачей синхроимпульса по синхронизирующей шине устройства (не показана на фиг. 1, 3, 4 и 7), по которому осуществляется запись во все регистры и триггеры устройства .

При выполнении первой микрокоманды умножения на вход 29 поступает мантисса множимого и под воздействием

0

5

0

23

управляющих кодов В40(0) и В35(1) записывается в регистр 1.

При выполнении второй микрокоманды мантисса множимого поступает из регистра 1 через коммутатор 8 на вход узла 25 нормализации и сдвига под воздействием управляющего крда В41(0) В узле 25 выполняется выравнивание мантиссы множимого по левой границе (сдвиг мантиссы влево на 8 бит), для чего на входе 30 кода сдвига должен быть установлен код сдвига 8 и управляющий код В46(1). Выравненная по левой границе мантисса с выходов 86 узла 25 заносится через коммутатор 10 в регистр 4 под воздействием управляющих кодов В43(0) и В38(1). В этой же микрокоманде на вход 29 данных поступает мантисса множителя и под воздействием управляющих кодов В40(0) и В35(1) записывается через коммутатор 7 в регистр 1.

В третьей микрокоманде мантисса множимого с выходов 62 регистра 4 за- носится через коммутатор 8 в регистр 2 под воздействием управляющих кодов В41 (1) и В36(1).

Затем выполняется четвертая микрокоманда, в которой выполняются следую щие действия.

Текущая цифра множителя с выходов 90 младших разрядов регистра подается через коммутатор 14 под управлением кода В47(1) на вход множителя уз- ла 20 разрядных произведений. Узел 20 разрядных произведений, а также арифметико-логический узел 21 и сумматор 22 настраиваются управляющим кодом В48(0) на выполнение операций в двоичной системе счисления. Сформированные на входах 78 и 79 узла 20 старшие и младшие цифры разрядных произведений записываются через коммутаторы 9 и 10 в регистры 3 и 4 соот ветственно под управлением кодов В37(1), В38Х1),В42(1) и В43(1). Управляющий код В49(9) настраивает арифметико-логический узел 21 на режим суммирования.,

Старшие цифры разрядных произведений, сформированные в предыдущем такте, с выходов 61 регистра 3 поступают через коммутатор 12 под управлением кода В51(2) на входы-первого операнда узла 21. Младшие цифры разрядных произведений, сформированные в предыдущем такте, с. выходов 99 старших разрядов регистра 4 поступают через ком

JQ J5 20

25

30

3540 45 50

55 524

мутатор 13 иод управлением кода В52(2) со сдвигом на 4 бита вправо на входы второго операнда узла 21 (сдвиг младших цифр разрядных произведений на 4 бита вправо компенсирует сдвиг на 4 бита влево при формировании этих цифр на узле 20 и записи в регистр 4 в предыдущем такте). Переносы, сформированные в предыдущем такте (нулевая информация в четвертой микрокоманде), с выходов 63 регистра 5 поступают через коммутатор 18 под управлением кода В54(0 ) со сдвигом на 4 бита вправо, соответствующим сдвигу суммы частичных произведений, на входы переносов узла 21. Результат ио- тетрадного суммирования и переносы с выходов 80 и 81 результата и переносов соответственно узла 21 поступают через коммутаторы 15 и 19 под управлением кодов В47(1) и В55(0) соответственно на входы второго слагаемого и переносов сумматора 22, где и складываются со сдвинутой вправо на 4 бита текущей суммой частичных произведений, поступающей на входы первого слагаемого сумматора 22 через коммутатор 17 под управлением кода В47(1) с выходов 101 старших разрядов регистра 6. Результат по- тетрадного суммирования с выходов 82 суммы сумматора 22 поступает на входы регистра 6 через коммутатор 16 под управлением кода В53(1), а с входов 83 переносов - на входы регистра 5..Запись новой суммы частичных произведений осуществляется под воздействием управляющего кода В39(1). Подготовка следующей цифры множителя осуществляется путем сдвига множителя, хранимого в регистре 1, на 4 бита вправо на коммутаторе 7 под управлением кода В40(1). В освобождающиеся старшие разряды регистра 1 заносятся младшие 4 бита текущей суммы частичных произведений с выходов 101 младших разрядов суммы сумматора 22 через коммутатор 11 под управлением кода В50(0). Запись.сдвинутого множителя в регистр 1 производится под управлением управляющего кода В35(1).

При выполнении этой микрокоманды с выходов 84 узла 23 коррекции подается нулевая комбинация на входы коммутатора 17 и тем самым не оказывает влияние на формирование результата.

Затем выполняются микрокоманды 5-17, аналогичные четвертой микрокоманде, общее число итераций умножения равно 14 - числу тетрад множителя.

После выполнения 17-й микрокоманды в регистрах 3 и 4 находятся последние разрядные произведения, а в регистрах 5 и 6 - сумма частичных произ ведений. В восемнадцатой микрокоманде цифра множителя заменяется нулевой комбинацией на коммутаторе 14 (управ ляющий код В47(0)), остальные деиствия совпадают с микрокомандами 4-17. По окончании выполнения этой микрокоманды в регистрах 5 и 6 хранится старшая часть произведения в двухрядном коде, в регистре 1 - младшая . часть произведения и для получения результата требуетсдрЕтаршую часть привести к однорядному коду, -что осуществляется следующим образом. В девятнадцатой микрокоманде в арифметико-логическом узле 21 производится суммирование (управляющий код В49(9)) нулевой информации, хранящейся в регистрах 3 и 4 и поступающей на входы операндов под управлением кодов Ь51(2) и В52(2) через коммутаторы 12 и 13 соответственно с переносами, поступающими с выходов 63 регистра 5 через коммутатор 18 (управляющий код В54(0)). На выходах 80 результата арифметико-логического узла 21 оказы- ваются, таким образом, значения переносов из регистра 5, а на выходах 81 переносов узла 21 - нулевая информация. На сумматоре 22 двухрядный код результата выполнения операции умно- жения приводится к однорядному, причем на вход первого слагаемого поступает сдвинутая на 4 бита вправо сумма частичных произведений с выходов 101 старших разрядов регистра 6 через коммутатор 17 под управлением кода В47(0), а через коммутатор 15 под управлением кода В47(0) на вход второго слагаемого сумматора 22 поступают переносы предыдущего такта с . выходов 80 результата арифметико-логического узла 21. Коммутатор 19 под управлением кода Е55() настраивает сумматор 22 на выполнение операции сложения с передачей (распростране- нием) переносов между тетрадами. На выходах 82 суммы сумматора 22 формируется результат умножения в однорядном коде, который через коммутатор

16 под управлением кода В53(1) записывается в регистр 6 под воздействие управляющего кода В39(1).

Таким образом, после выполнения девятнадцати микрокоманд в регистре 6 находится старшая часть произведения (15 тетрад), а в регистре 1 - младшая часть произведения (13 тетрад).

В двадцатой микрокоманде старшая часть произведения с выходов 64 регистра 6 через коммутатор 8 под управлением кода В41(2) поступает на входы узла 25 нормализации и сдвига, через который передается транзитом (управляющий код В46(1 ) при нулевой комбинации на входе 30 кода сдвига) на выход 33 результата.

В двадцать первой микрокоманде младшая часть произведения с выходов 59 регистра 1 через коммутатор 8 под управлением кода В41(0 ) поступает на входы узла 25, через который передается транзитом (управляющий код В46(1)(при нулевой комбинации на входе 30 кода сдвига) на выход 33 результата.

Обеспечение высокой скорости выполнения операции умножения достигается тем, что суммирование текущей суммы частичных произведений с текущими разрядными произведениями производится не на всю разрядность, а потетрадно с запоминанием переносов из тетрад, благодаря тому, что одновременно с суммированием текущей суммы частичных произведений с текущими разрядными произведениями в узле 21 и сумматоре 22 в узле 20 разрядных произведений формируются новые разрядные произведения, организуя таким образом конвейер, причем время на выполнение подготовительной и исполнительной фаз близко друг к другу.

Микропрограмма выполнения операции умножения с короткими операндами (мантисса - 6 тетрад) аналогична описанной, причем отличие состоит только в том, что отсутствуют микрокоманды с 10-й по 17-ю и 21-я, а во второй микрокоманде на вход 30 кода сдвига подается код сдвига влево на 40 бит. Результат выполнения операции (12 тетрад произведения) формируется в регистре 6.

Микропрограмма выполнения операции умножения в дополнительных кодах (в ЕС ЭВМ - фиксированная запятая, 32

2715

бита) также аналогична описанной микропрограмме. Различия состоят лишь в том, что в регистр 1 заносятся одновременно множимое и множитель, причем множимое заносится в старшие 32 бита, а множитель - в младшие. В дальшейшем при выполнении умножения в микрокомандах с 4-й по 11-ю под управлением кода В44(1 ) п регистр 111 коррекции узла 23 коррекции заносится код коррекции результата, который поступает в следующем такте в соответствующие разряды накапливаемой суммы частичных произведений, тем самым параллельно с выполнением собственно умножения выполняется коррекция результата. Кроме этого, микрокоманды с 12-й по 17-ю отсутствуют. По окончании 19-й микрокоманды в младших разрядах регистра 6 находятся старшие 15 тетрад произведения, а в старших разрядах регистра 1 - младшая 16-я тетрада произведения. I

Рассмотрим выполнение операции множения в десятичной арифметике. Десятичный множитель в ЕС ЭВМ может содержать до 15 десятичных цифр, а множимое - до 31 десятичной цифры, поэтому целесообразно в регистр 2 заносить множитель, а умножение выполнять с младших разрядов множимого, обрабатывая по одной десятичной цифре за такт. В остальном же выпол- нение операции умножения в десятичной арифметике аналогично выполнению операции умножения в описанной двоичной арифметике. Различие лишь в том, что управляющий код В48(1 ) настраивает узел 20 разрядных произведений, арифметико-логический узел 21 и сумматор 22 на выполнение операций с двоично- десятичными кодами чисел.

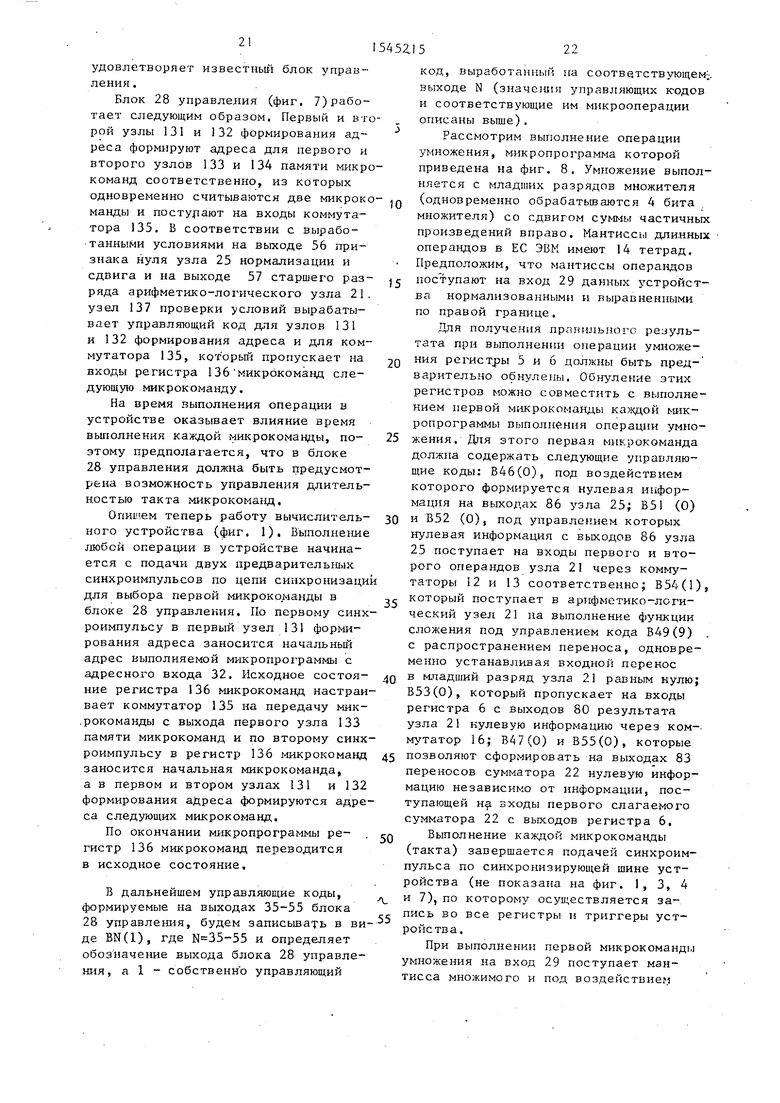

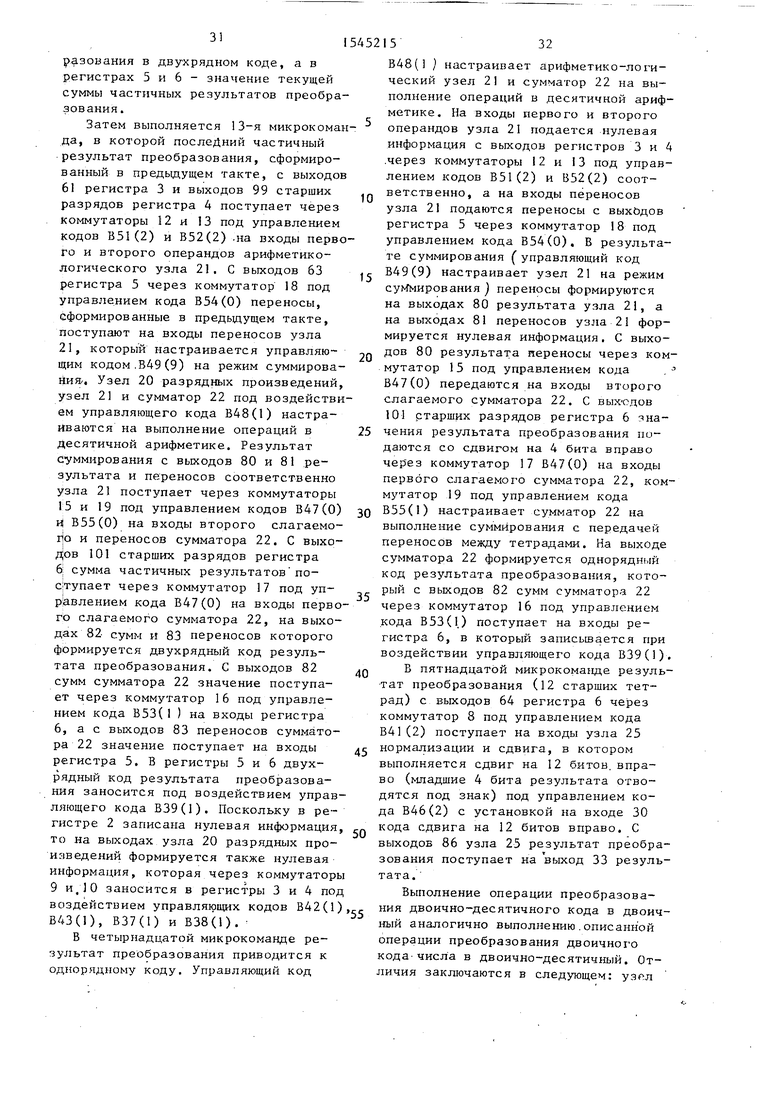

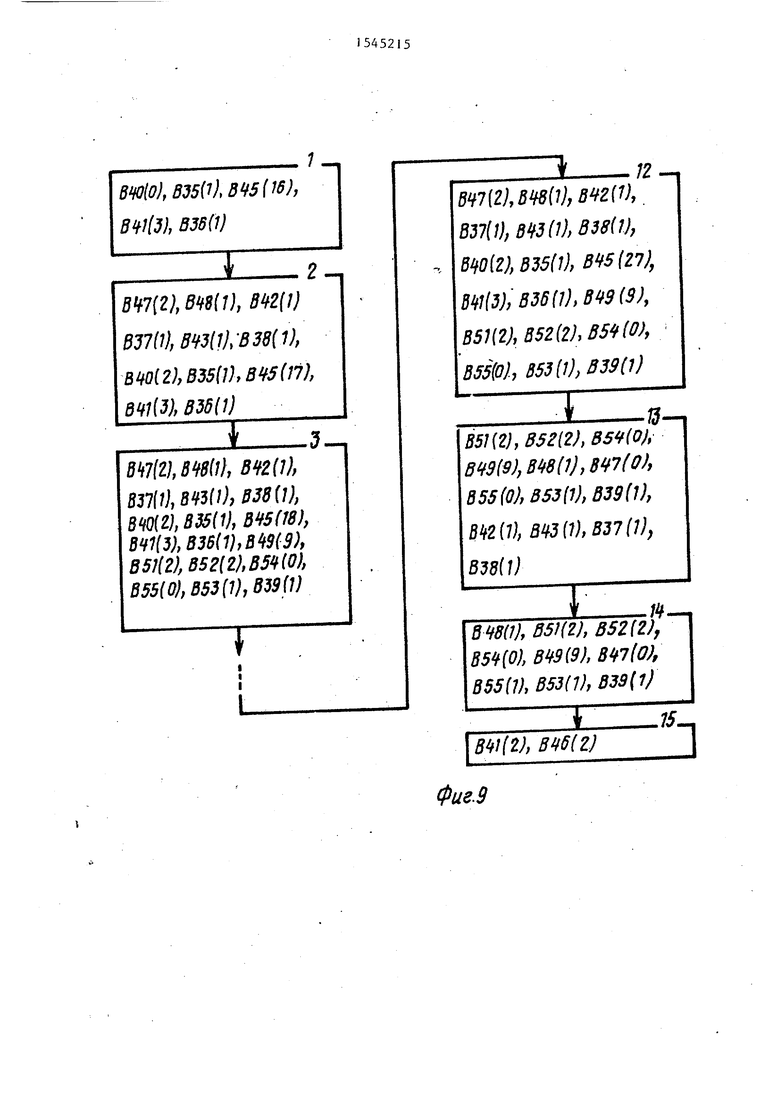

Операции преобразования в устрой- стве выполняются по методу суммирования эквивалентов цифр (групп цифр). Так, при преобразовании двоичного кода в двоично-десятичный суммируются эквиваленты групп, состоящих из трех битов, а при преобразовании двоично- десятичного кода в двоичный суммируются эквиваленты групп, состоящих из 4-х .битов (эквиваленты одной десятичной цифры).

Рассмотрим выполнение операции преобразования двоичного кода числа в двоично-десятичный. Для определенности принимаем положительным преоб528

разуемое число. Микропрограмма для этого случая приведена на фиг. 9.

При выполнении операции преобразования для получения правильного результата необходимо в первой микрокоманде обнулить содержимое регистро 5 и 6 так же, как в операции умножения .

При выполнении первой микрокоманд на вход 29 данных поступает преобразуемое число и через коммутатор 7 под управлением кода В40(0) поступает на входы регистра 1, в младшие 32 разряда которого записывается под воздействием кода В35(1). В этой же микрокоманде на адресный вход узла 24 смещенных эквивалентов подается управляющий код В45(16), по которому считывается первый эквивалент. С выходов 85 узла 24 первый эквивалент л через коммутатор 8 под управлением кода В41(3) поступает на входы регистра 2, в который записывается под воздействием управляющего кода В36(1).

Вторая микрокоманда включает следующие действия. Текущие 3 младших бита преобразуемого числа с выходов 90 младших разрядов регистра 1 через коммутатор 14 под управлением кода В47(2) поступают на вход множителя учла 20 разрядных произведений. Управляющий код В48(1) настраивает узе 20 разрядных произведений, арифметико-логический узел 21 и сумматор 22 на выполнение операций в десятичной арифметике. На выходах 78 и 79 узла 20 формируются разрядные произведения частичного результата преобразования (произведения смещенного эквивалента на значение текущих младших 3 бит преобразуемого числа), В случае преобразования за один такт более 3 бит двоичного числа (или более одной цифры десятичного числа в преобразовании двоично-десятичного кода в двоичный) на линии передачи преобразуемой группы разрядов необходимо установить преобразователи двоичного кода в двоично-десятичный (или преобразователь двоично-десятичного кода в десятичный), посколку узел 20 разрядных произведений настраипается на работу с операндами в двоично-десятичном (или в двоичном) кодах. При разрядности групп преобразуемого двоичного числа до 3 бит двоичный и двоично-десятичные

коды совпадают как и при ратряднис- ти группы преобразуемого двоично-десятичного числа, равной одной десятичной цифре.

Старшие цифры разрядных произведений частичного результата преобразования с выходов 78 узла 20 через коммутатор 9 под управлением кода В42(1) поступают на входы регистра 3, в который записываются под воздействием управляющего кода В37(1). Младшие цифры разрядных произведений частичного результата преобразования с выходов 79 узла 20 через коммутатор 10 под управлением кода В43(1) подаются со сдвигом на А бита влево на входы регистра 4, в который записываются под воздействием управляющего кода В38(1).

С выходов 92 старших разрядов регистра 1 значение преобразуемого числа через коммутатор 7 под управлением кода В40(2) поступает со сдвигом на 3 бита вправо на входы регист- pa I, в который записывается под воздействием управляющего кода В35(1). Таким образом подготавливаются следующие три младших разряда преобразуемого числа для обработки. На ад- ресный вход узла 24 смещенных эквивалентов подается управляющий код В45(17), по которому считывается второй смещенный двоично-десятичный эк-, вивалент и с выходов 85 узла 24 че- рез коммутатор 8 под управлением кода В41(3) поступает на входы регистра 2, в который записывается под воздействием управляющего кода В36(1).

Затем выполняется третья микрокоманда, которая включает все действия, входящие во вторую микрокоманду (отличается лишь управляющий код 845(18) по которому считывается третий сме- щенный эквивалент из узла 24), и дополнительно содержит следующие действия. Арифметико-логический узел 21 управляющим кодом В49(9) настраивается на функцию сложения. Стар- шие цифры разрядных произведений текущего частичного результата преобразования, сформированные в предыдущем такте, с выходов 61 регистра 3 через коммутатор 12 под управлением кода В51(2) поступают на входы первого операнда узла 21. Младшие цифры разрядных произведений текущего частичного результата преобразования,

сформированные в предыдущем такте, с выходов 99 Старших разрядов регистра 4 через коммутатор 13 под управлением кода В52(2) поступают со сдвигом на 4 бита вправо на входы второго операнда узла 21 (сдвиг на 4 бита вправо младших цифр разрядных произведений текущего частичного результата преобразования, хранимых в регистре 4, компенсирует сдвиг на 4 бита влево при записи этих же младших цифр разрядных произведений частичного результата преобразования с выходов 79 узла 20 в регистр 4 в предыдущем такте). Управляющий код B54(OJ настраивает узел 21 на потетрадное выполнение операции, подавая переносы с выходов 63 регистра 5 через коммутатор 18 со сдвигом на 4 разряда вправо на Ъходы переносов узла 21 (сдвиг соответствует сдвигу суммы частичных результатов преобразования) . Результат потетрадного суммирования и переносы поступают с выходов 80 и 81 результата и переносов соответственно узла 21 через коммутаторы 15 и 19 под управлением кодов В47(2) и В55(0) на входы второго слагаемого и переносов сумматора 22. Текущая сумма частичных результатов преобразования с выходов 101 старших разрядов регистра 6 через коммутатор 17 под управлением кода B47(2 поступает на входы первого слагаемого сумматора 22 со сдвигом на 4 разряда вправо. Результат потетрадного суммирования с выходов 82 сумм сумматора 22 через коммутатор 16 под управлением кода В53(1 ) поступает на входы регистра 6, ас выходов 84 переносов сумматора 22 поступает на входы регистра 5, в которые записывается под воздействием управляющего кода В39(1).

Затем выполняются микрокоманды с 4-й по 12-ю, которые аналогичны третьей и отличаются лишь управляющим кодом В45, который задает последовательно соответствующие адреса смещенных эквивалентов (или нулевой комбинации в 1 2-й микрокоманде). По окончании 12-й микрокоманды полностью обработаны разряды пре- обравуемого числа (в регистре 1 находится нулевая информация), в регистр - 2 записана нулевая информация, в регистрах 4 и 3 находится значение последнего частичного результата преоб31

15452

разования в двухрядном коде, а в регистрах 5 и 6 - значение текущей суммы частичных результатов преобразования.

Затем выполняется 13-я микрокоманда, в которой последний частичный результат преобразования, сформированный в предыдущем такте, с выходов 61 регистра 3 и выходов 99 старших разрядов регистра 4 поступает через коммутаторы 12 и 13 под управлением кодов В51(2) и В52(2) -на входы первого и второго операндов арифметико- логического узла 21. С выходов 63 регистра 5 через коммутатор 18 под управлением кода В54(0) переносы, сформированные в предыдущем такте, поступают на входы переносов узла 21, который настраивается управляющим кодом В49(9) на режим суммирования. Узел 20 разрядных произведений, узел 21 и сумматор 22 под воздействием управляющего кода В48(1) настраиваются на выполнение операций в десятичной арифметике. Результат суммирования с выходов 80 и 81 результата и переносов соответственно узла 21 поступает через коммутаторы 15 и 19 под управлением кодов В47(0) и В55(0) на входы второго слагаемого и переносов сумматора 22. С выходов 101 старших разрядов регистра 6 сумма частичных результатов поступает через коммутатор 17 под управлением кода В47(0) на входы первого слагаемого сумматора 22, на выходах 82 сумм и 83 переносов которого формируется двухрядный код результата преобразования. С выходов 82 сумм сумматора 22 значение поступает через коммутатор 16 под управлением кода В53( 1 ) на входы регистра 6, а с выходов 83 переносов сумматора 22 значение поступает на входы регистра 5. В регистры 5 и 6 двухрядный код результата преобразования заносится под воздействием управляющего кода В39(1). Поскольку в регистре 2 записана нулевая информация то на выходах узла 20 разрядных произведений формируется также нулевая информация, которая через коммутаторы 9 и(10 заносится в регистры 3 и 4 под воздействием управляющих кодов В42(1) В43(1), В37(1) и В38(1).

В четырнадцатой микрокоманде ре- чультат преобразования приводится к однорчдному коду. Управляющий код

10

15

0

5

0

35

0

5

0

5

1532

В48(1 ) настраивает арифметико-логический узел 21 и сумматор 22 на выполнение операций в десятичной арифметике. На входы первого и второго операндов узла 21 подается нулевая информация с выходов регистров 3 и 4 через коммутаторы 12 и 13 под управлением кодов В51(2) и В52(2) соответственно, а на входы переносов узла 21 подаются переносы с выходов регистра 5 через коммутатор 18 под управлением кода В54(0). В результате суммирования (управляющий код В49(9) настраивает узел 21 на режим суммирования ) переносы формируются на выходах 80 результата узла 21, а на выходах 81 переносов узла 21 формируется нулевая информация. С выходов 80 результата переносы через коммутатор 15 под управлением кода 1 В47(0) передаются на входы второго слагаемого сумматора 22. С иых отрв 101 старших разрядов регистра 6 чна- чения результата преобразования нп- даются со сдвигом на 4 бита вправо через коммутатор 17 В47(0) на входы первого слагаемого сумматора 22, коммутатор 19 под управлением кода В55(1) настраивает сумматор 22 на выполнение суммирования с передачей переносов между тетрадами. На выходе сумматора 22 формируется однорядний код результата преобразования, который с выходов 82 сумм сумматора 22 через коммутатор 16 под управлением кода В53(1.) поступает на входы регистра 6, в который записывается при воздействии управляющего кода В39(1).

В пятнадцатой микрокоманде результат преобразования (12 старших тетрад) с выходов 64 регистра 6 через коммутатор 8 под управлением кода В41(2) поступает на входы узла 25 нормализации и сдвига, в котором выполняется сдвиг на 12 битов вправо (младшие 4 бита результата отводятся под знак) под управлением кода В46(2) с установкой на входе 30 кода сдвига на 12 битов вправо. С выходов 86 узла 25 результат преобразования поступает на выход 33 результата.

Выполнение операции преобразования двоично-десятичного кода в двоичный аналогично выполнению описанной операции преобразования двоично го кода числа в двоично-десятичный. Отличия заключаются в следующем: у-эгл

33

20 разрядных произведений, арифметико-логический узел 21 и сумматор 22 управляющим кодом ВА8(0 ) настраиваются на выполнение операций в двоичной арифметике; в каждом такте преобразуется одна тетрада (одна десятичная цифра) числа, которая с выходов 90 младших разрядов регистра 1 передается через коммутатор 14 под JQ управлением кода В47(1) на вход множителя узла 20; преобразуемое число, которое хранится в регистре 1, сдвигается на 4 бита вправо на коммутато- ре 8 под управлением кода 840(1), 15 подготавливая тем самым новую тетраду для преобразования.

Рассмотрим выполнение операции деления. В устройстве примечен метод предсказания по Старшим разрядам 20 делимого (остатка) и делителя цифр частного с получением очередного остатка в двухрядном коде.

Рассмотрим более подробно операцию деления мантисс длинных операндов 25 (в ЕС ЭВМ - 14 тетрад). Для опрееленности предполагаем, что мантиссы поступают нормализованными шест- надцатерично. Микропрограмма для этого случая приведена на фиг. 10. 30

В первой микрокоманде нормализованная мантисса делимого, выравненная по левой границе, поступает с входа

29данных через коммутатор 7 под управлением кода В40(0) на.входы реги - 35 стра 1 и записывается в него под воздействием управляющего кода В35(1).

Во второй микрокоманде мантисса елимого с выходов 59 регистра 1 передается через коммутатор 8 под уп- 40 равлением кода В41(0) на входы узла 25 нормализации и сдвига, где сдвигается вправо на 1 бит под управлением кода В46(2) при установке на входе

30узла 25 кода сдвига на 1 бит впра- 45 во. С выходов 86 узла 25 сдвинутая вправо на 1 бит мантисса делимого поступает через коммутатор 10 под управлением кода В43( 0 ) на входы регитра 4 и записывается в него под воз- 50 ействием управляющего кода В38(1).

В этой же микрокоманде нормализованная мантисса делителя, выравненная о левой границе, с входа 29 данных устройства поступает через коммутатор с 7 под управлением кода В40(0)- на ходы регистра 1 и записывается в него под воздействием управляющего кода В35(1).

JQ 15

20

25 30

40

45 50

с

15-34

В третьем такте производится двоичная нормализация мантиссы делителя, для чего мантисса делителя с выходов 59 регистра I через коммутатор 8 под управлением кода В41(0) поступает на входы узла 25 нормализации и сдвига, в котором под управлением кода В46(4) происходит двоичная нормализация мантиссы (на выходе 34 кода нормализации устанавливается код двоичной нормализации мантиссы) и Q выходов 86 узла 25 двоично-нормали- зованная мантисса поступает через коммутатор 7 под управлением кода В40(3) на входы регистра 1, в который записывается под управлением кода В35(1).

В четвертой микрокоманде двоично- нормализованный делитель с выходов 59 регистра 1 через коммутатор 8 под управлением кода В41(0) заносится в регистр 2 под воздействием управляющего кода В36(1).

В пятой микрокоманде выполняются следующие действия. Сформированная на выходах 89 узла 27 цифр частного текущая цифра частного на основе старших разрядов двухрядного кода остатка, поступающих с выходов 97 и 98 старших разрядов регистров 3 и 4 соответственно (в первом такте - это старшие разряды делимого), и старших разрядов делителя, поступающих на узел 27 с выходов 96 старших разрядов регистра 2, поступает через коммутатор 14 под управлением кода В47(3) на нход множителя узла 20 разрядных произведений и через коммутатор 15 под управлением того же кода В47(3) на входы второго слагаемого сумматора 22, В узле 20 формируются разрядные произведения мантиссы делителя на цифру частного, которые с выходов 78 старших и 79 младших цифр разрядных произведений узла 20 поступают на входы вычитаемого и заема вычита- теля 26,

Двухрядный код текущего остатка с выходов 61 и 62 регистров 3 и 4 со- ответственно поступает через коммутаторы 12 и 13 под управлением кодов В51(2) и В52(2) соответственно на входы первого и второго операндов арифметико-логического узла 21. Управляющий код В54(2) настраивает мутатор 18 на передачу переносов между тетрадами узла 21 с установкой в уровень логической единицы входного переноса н младшую тетраду учла 21. Управляющий код В49( 9 ) настраивает узел 21 на выполнение функции сложения. Сформированный на выходах 80 узла 21 однорядный код текущего остатка поступает на входы уменьшаемого вычитателя 26, на выходах соответственно 88 и 87 заема разности которого формируется двухрядный код следующего остатка, который через коммутаторы 9 и 10 под управлением кодов В42(2) vi В43(2) поступает на входы регистров 3 п 4 и записывается в них под воздействием управляющих кодов В37(1) и В38(1). С выходов 100 младших разрядов регистра текущее частное (или нулевая информация в 5-й микрокоманде, подготовленная заранее как и в операциях умножения) через коммутатор 17 под управлением кода В47(3) поступает со сдвигом на 3 бита влево на входы первого слагаемого сумматора 22, где складывается с текущей цифрой частного, при этом коммутатор 19 управляющим кодом В-55(1) настраивается на передачу переносов сумматора 22 между тетрадами. С выходов 82 суммы сумматора 22 следующее частное через коммутато 16 под управлением кода В53(1) посту на входы регистра 6, в который записывается под воздействием управляющего кода В39(1). Таким образом п окончании микрокоманды в регистре 6 хранится текущее частное, в регистрах 3 и 4 - двухрядный код текущего остатка, а в регистре 2 - двоично- нормалнзованний делитель.

Затем выполняются микрокоманды с 6-й по 23-ю, аналогичные описанной пятой микрокоманде. По окончании 23-й микрокоманды в регистре 6 в младших 58 разрядах находится частное, в регистрах 3 и 4 - двухрядный код последнего остатка.

В двадцать четвертой микрокоманде приводится к однорядному коду двухрядный код остатка, который с выходов 61 и 62 регистров 3 и 4 через коммутаторы 12 и 13 под управлением кодов В51(2) и В52(2) соответственно поступает на входы первого и второго операндов арифметико-логического узла 21, который управляющим кодом В49(9) настраивается на выполнение функции сложения. Коммутатор 18 настраивается кодом В54(1) на передач перенос он между тетрадами учла 21.

Сформированный на входах 80 результата узла 21 однорядныи код остатка через коммутатор 10 под управлением кода В43(3) поступает на входы регистра 4, в который записывается под воздействием управляющего кода В38(1)

I

В двадцать пятой микрокоманде выполняется пробное вычитание делителя из остатка. С выходов 62 регистра 4 через коммутатор 12 под управлением кода Ь51(1) однорядный код остатка поступает на входы первого операнда арифметико-логического узла 21. Значение делителя с выходов 60 регистра 2 через коммутатор 13 под управлением кода В52(3) поступает со сдвигом на 1 бит вправо на входы второго операнда узла 21 (сдвиг на 1 бит вправо выравнивает весовые значения остатка и делителя У, Управляющий код В49(б) настраивает узел 21 на выполнение функции сложения .с обратным кодом. Коммутатор 18 управляющим кодом В54(2) настраивается на передачу переносов между тетрадами с установкой уровня логической единицы на входе переноса в младший разряд узла 21. ha выходах 80 результата узла 21 формируется разность, причем, если остаток был меньше делителя, то разность отрицательна, в противоположном случае - разность положительна и, следовательно, в остатке содержится делитель, что вызывает необходимость корректировки текущего частного, которое осуществляется в 26-й микрокоманде. Коли корректировки не требуется, то осуществляется переход к выполнению микрокоманды.

Переход осуществляется следующим образом. Во время выполнения двадцать питой микрокоманды из узлов 133 и 134 памяти считываются микрокоманды 26-я и 27-я одновременно по адресам, сформированным заранее в узлах 131 и 132 формирования адреса соответственно. Значение, образованное на выходе 57 старшего разряда арифметико-логического узла 21, поступает на вход узла 137 проверки условий, который вырабатывает соответствующие управляющие сигналы для коммутатора 135. Так, в случае наличия уровня логической единицы на выходе 57 старшего разряда узла 21 на входы регистра 136 поступает 27-и микрокоманда,

л в случае наличия уровня логического пуля - 26-я микрокоманда.

В двадцать шестой микрокоманде производится коррекция частного, для. этого текущее частное с выходов 64 регистра 6 через коммутатор 12 под управлением кода В51(3) поступает на вход первого узла 21, который управляющим кодом В49(0) настроен на выполнение функции транзита-коррекции. Коррекция вводится через вход переноса в младший разряд арифметико- логического узла 21 установкой коммутатора 18 управляющим кодом В54(2) . Сдвиг вправо операнд, поступающий

на входы узла 25 нормализации и сдви га, сдвигается по коду, установленному на входе 30 кода сдвига. Сдви- /нутый операнд поступает на выход 33 результата устройства.

в режим передачи переносов между тетрадами узла 21 с одновременной ус- тановкой в уровень логической единицы входного переноса в младший разряд узла 21. Сформированное на выходах 80 узла 21 частное, поступает через коммутатор 16 под управлением кода В53(0) на входы регистра 6, в который записывается под воздействием управляющего кода 839(1).

В двадцать седьмой микрокоманде частное с выходов 64 регистра 6 поступает через коммутатор 8 под управлением кода В41(2) на входы узла 25 нормализации и сдвига.

Под воздействием управляющего кода В46(1) в узле 25 производится корректирующий сдвиг влево частного по коду двоичной нормализации делите ля (проведенной в третьей микрокоман- мный блок управления, причем выходы

де), который устанавливается на входе 30 кода сдвига.

С выходов 86 узла 25 частное поступает на выход 33 результата устройства.

Выполнение операции деления в целочисленной арифметике сводится к выполнению описанной операции деления с плавающей запятой после перевода делимого и делителя в прямой код.

При сложении (вычитании) с фиксированной запятой операнды поступают на регистры 3 и 4, затем арифметико-логический узел 21 настраивается на выполнение функции сложения (сложения с обратным кодом с дополнением единицы в младший разряд узла 21) с распространением переносов между тетрадами узла 21. Окончательный результат заносится .в регистр 6.

При сложении (вычитании) с плавающей запятой в устройстве обраба40

45

коммутаторов с первого по четвертый соединены с информационными входами соответствующих регистров, вход данных устройства соединен с первым информационным входом первого коммутатора, второй информационный вход которого соединен с выходом результата устройства, выход второго регистра соединен с входом множимого узла разрядных произведений и с первым ин формационным входом седьмого коммутатора, выходы шестого и седьмого коммутаторов соединены соответственно с первым и вторым информационными CQ входами арифметико-логического узла, - выход признака нуля узла нормализаци и сдвига и выход старшего разряда ре зультата арифметико-логического узла соединены соответственно с первым и вторым входами условий микропрограммного блока управления, адресный вхо которого соединен с адресным входом устройства, вход кода сдвига которого соединен с входом задания величин

55

тываются мантиссы операндов. Сдвиг мантисс операндов производится при передаче их с входа 29 данных в регистры 3 или 4 в узле 25 нормализации и сдвига с установкой соответствующего кода сдвига на входе 30. Затем в арифметико-логическом узле 21 производится сложение (вычитание) мантисс и результат записывается в регистр 6. Если результат получается отрицательным, то производится его перевод в прямой код.

При операции Сдвиг влево.и

на входы узла 25 нормализации и сдвига, сдвигается по коду, установленному на входе 30 кода сдвига. Сдви- /нутый операнд поступает на выход 33 результата устройства.

Устройство может выполнять все те логические операции, на которые ориентирована микросхема 500ИШ81, .при реализации на них узла 21.

Формула изобретения

Вычислительное устройство, содержащее с первого по шестой регистры, с первого по девятый коммутаторы, узел разрядных произведений, арифметико-логический узел, сумматор, узел нормализации и сдвига и микропрограм0

5

коммутаторов с первого по четвертый соединены с информационными входами соответствующих регистров, вход данных устройства соединен с первым информационным входом первого коммутатора, второй информационный вход которого соединен с выходом результата устройства, выход второго регистра соединен с входом множимого узла разрядных произведений и с первым информационным входом седьмого коммутатора, выходы шестого и седьмого коммутаторов соединены соответственно с первым и вторым информационными Q входами арифметико-логического узла, - выход признака нуля узла нормализации и сдвига и выход старшего разряда результата арифметико-логического узла соединены соответственно с первым и вторым входами условий микропрограммного блока управления, адресный вход, которого соединен с адресным входом устройства, вход кода сдвига которого соединен с входом задания величины

5

сдвига узла нормализации и сдвига, выход кода нормализации которого является выходом кода нормализации устройства, выход третьего регистра соединен с первым информационным входом шестого коммутатора; первые информа-i ционные входы третьего и четвертого коммутаторов объединены с вторым информационным л входом первого коммутатора и соединены с информационным выходом узла нормализации и сдвига, выход переносов сумматора соединен с информационным входом пятого регистра, выход шестого регистра соединен с вто- рым информационным входом шестого коммутатора, выходы с первого по четвертый микропрограммного блока управления соединены с входами разрешения записи регистров с первого по четвертый соответственно, пятый выход микропрограммного блока управления соединен с входами разрешения записи пятого и шестого регистров, шестой, седьмой, восьмой и девятый вы- ходы микропрограммного блока управления соединены с управляющими входами коммутаторов с первого по четвертый соответственно, отличающееся тем, что, с целью по- вышения быстродействия, оно содержит с десятого по тринадцатый коммутаторы, узел коррекции, узел смещенных эквивалентов, вычитатель и узел цифр частного, причем выход узла смещенных эквивалентов соединен с первым информационным входом аторого коммутатора, второй информационный вход которого соединен с выходом первого регистра, выходы старших разрядов которого сое- динены с входами младших разрядов третьего и четвертого информационных входов первого коммутатора, входы старших разрядов третьего и четвертого информационных входов которого соединены с выходом пятого коммутатора, первый информационный вход которого соединен с входами младших разрядов входа данных устройства, выход результата которого соединен с третьим информационным входом шестого коммутатора и с вторым информационным входом седьмого коммутатора, информационный вход узла нормализации и сдвига соединен с выходом второго коммутатора, третий информационный вход которого соединен с выходом шестого регистра, выход чет- - вертого регистра соединен с четвертым информационным входом шестого коммутатора и с третьим информационным входом седьмого коммутатора, вход множителя узла ра-зрядных произведений соединен с выходом восьмого коммутатора, с первым информационным входом узла коррекции и с первым информационным входом девятого коммутатора, второй информационный вход которого соединен с выходом результата арифметико-логического узла, с первым информационным входом десятого коммутатора, с входом уменьшаемого вычитателя и с вторым информа- цийнным входом четвертого коммутатора, выход старших цифр узла разрядных произведений соединен с входом вычитаемого вычитателя и с вторым информационным входом третьего коммутатора, выход младших цифр узла разрядных произведений соединен с входом заема вычитателя и с третьим информационным входом четвертого коммутатора, выходы разности и заема вычитателя соединены соответст-. венно с четвертым информационным входом четвертого коммутатора и с третьим информационным входом третьего коммутатора, выходы старших разрядов четвертого регистра соединены с четвертым информационным входом седьмого коммутатора, выход десятого коммутатора соединен с информационным входом шестого регистра, выходы младших и старших разрядов которого соединены соответственно с первым информационным входом одиннадцатого коммутатора и с входами младших разрядов второго информационного входа одиннадцатого коммутатора, входы старших разрядов второго информационного входа которого соединены с выходом узла коррекции, второй информационный вход которого соединен с выходами младших разрядов старшей части первого регистра, выход переносов арифметико-логического узла соединен с первыми информационными входами двенадцатого и тринадцатого коммутаторов, выход пятого регистра соединен с вторым информационным входом двенадцатого коммутатора, выход переносов сумматора соединен с вторым информационным входом тринадцатого коммутатора, выход сумм сумматора соединен с вторым информационным входом десятого коммутатора, выходы младших разрядов суммы сумматора соедиисны с вторым информационным «ходом пятого коммутатора, выход двенадцатого коммутатора соединен с входом переносов арифметико-логического узла, выходы одиннадцатого и девятого коммутаторов соединены с входами первого и второго слагаемых сумматора соответственно, выход тринадцатого коммутатора соединен с входом переносов сумматора, выход четвертого регистра соединен с четвертым информационным входом второго коммутатора, выходы старших разрядов второго, третьего и четвертого регистров соединены с входами первой, второй и третьей групп узла цифр частного соответственно, выход которого соединен с первым информационным входом восьмого коммутатора, второй информационный вход которого соединен с выходами младших разрядов первого регистра, выход переноса в группу старших разрядов арифметико-логического узла соединен с входом разрешения узла цифр частного, вход знаков множимого и множителя устройства соединен с третьим информационным входом узла

5

0

5

коррекции, вход ра (решения которого соединен с десятым выходом микропрограммно го блока управления, адресный вход узла смещенных эквивалентов соединен с одиннадцатым выходом микропрограммного блока управления, двенадцатый выход которого соединен с входом задания вида сдвига узла нормализации и сдвига, управляющие входы восьмого, девятого и одиннадцатого коммутаторов объединены и соединены с тринадцатым выходом микропрогр раммного блока управления, четырнад- цат ый выход которого соединен с входами задания режима узла разрядных произведений, сумматора и арифметико-логического узла, вход задания вида операции которого соединен с пятнадцатым выходом микропрограммного блока управления, управляющие входы пятого, шестого, седьмого, десятого, двенадцатого и тринадцатого коммутаторов соединены с выходами с .. шестнадцатого по двадцать первый микропрограммного блока управления соответственно.

«4 72 91

Фигл

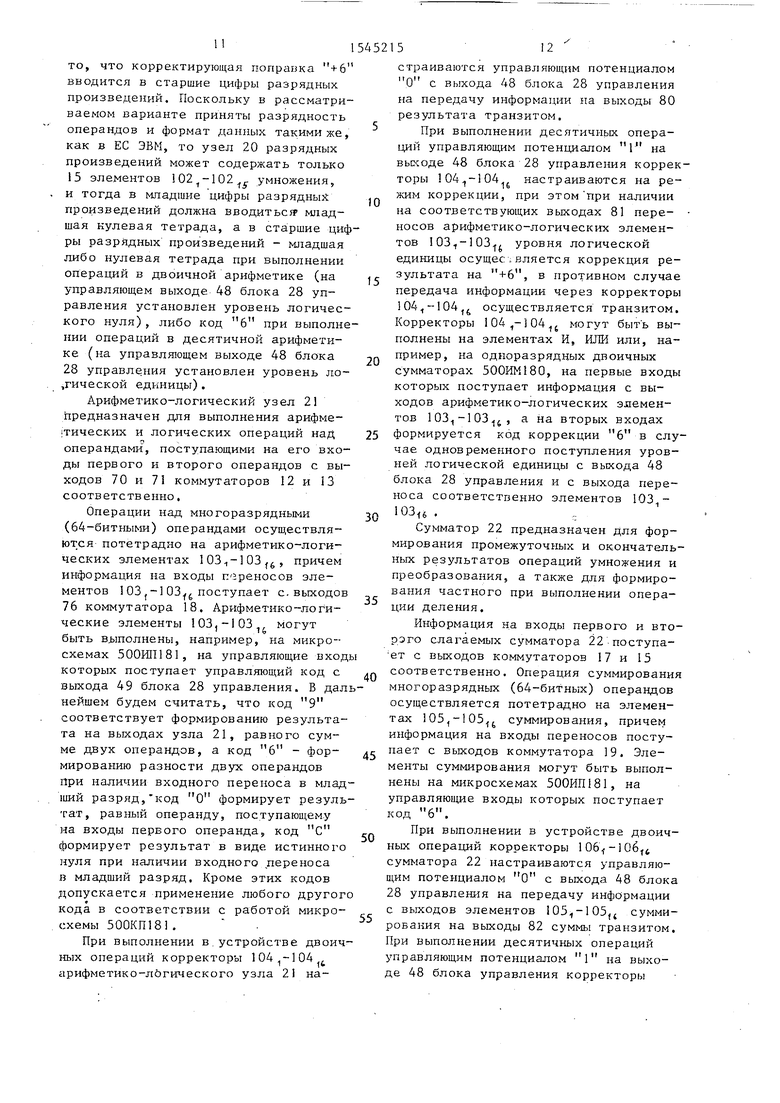

BW(0), ВЭ5(1)

1

I

2

В1ЩВШ1),ВЮ(0), В38(1),ВМ(0), 335(1)

1

J -

ВЧЩ), В36(1)

I

BW(1),BW{0), В37(1), B38(l),Bn(1),Bto(1), ВЧ919),В5Ц2), 852(2), B54(0),B55(0),ff53{1),

В39(1), ВМ(1), 850(0), В35 (1)

#I

i

, ВЧВ(0), В37(1), B38(l),B42(1),fft3(1), B49(9),B5l(Z),B52(2), B5t(0),B55{0), В53(1),

B39(1),BW(1}, 350(0), 635 (Ц

1

./(--,

ВЫ{0)ВЧ8(0),В37(1), B38(D, Bf2(1), ВЩ1), 8W(9), B51(2), B52 (Z), B5t(0),B55(0),ff53(7), 839(1), BW(1), 350(0), 535 f 1)

I

#-.

В49(9),851(2),В52(2),

854(0), В47(0), 355(1), B53ID, В39(1)

I

BW2), ВЧ6(1)

2°

I

вы(о) BWd)

Фиг. 8

in

LO

ST 0

/

В35(1), BW(0)I

izj

0w(o), в«б (г), в чз(о),

В38(1),В40(0), 535(1)

i

3-.

B41(0),B4B(4), B40(3), 835(1)

1

BW(0), 336(1)

1

I

5-1

B47(3},eS7(2), B52(2), B5(2))(9)Btt2(Z),

BttHV 637(1), B38(D, BSS(l),d53(l),B39(l)

V

Z3.

ВЧ7№,В51(2), В52 (2),

В5Ч(2},ВМ(д),ВМ12), ям(ПВ37(1),ВЭ8(1), В55(1),В53(1),В39(1)

1

л гл

В54(1), В43(3), В38(1)

2

1

25

BSlll),8S2U)Bt3(6) В 5 4(2)

26 -,

;,

,

27

Ш#, (/

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Бетонный полый камень | 1925 |

|

SU2366A1 |

| М., 1983, с | |||

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-02-23—Публикация

1988-05-06—Подача