Изобретение относится к вычислительной технике и может быть использовано для построения надежных вычислительных систем со встроенным контролем.

Цель изобретения - расширение области применения за счет возможности контроля прохождения произвольной программы без замены аппаратуры в

системе.

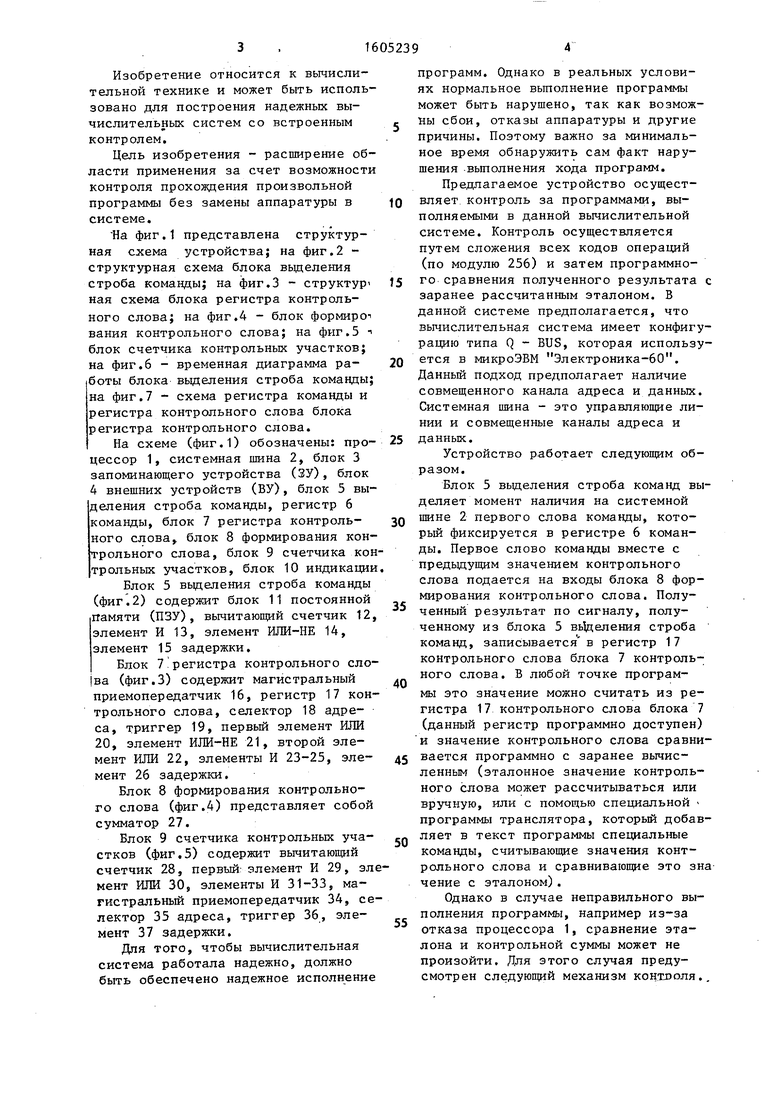

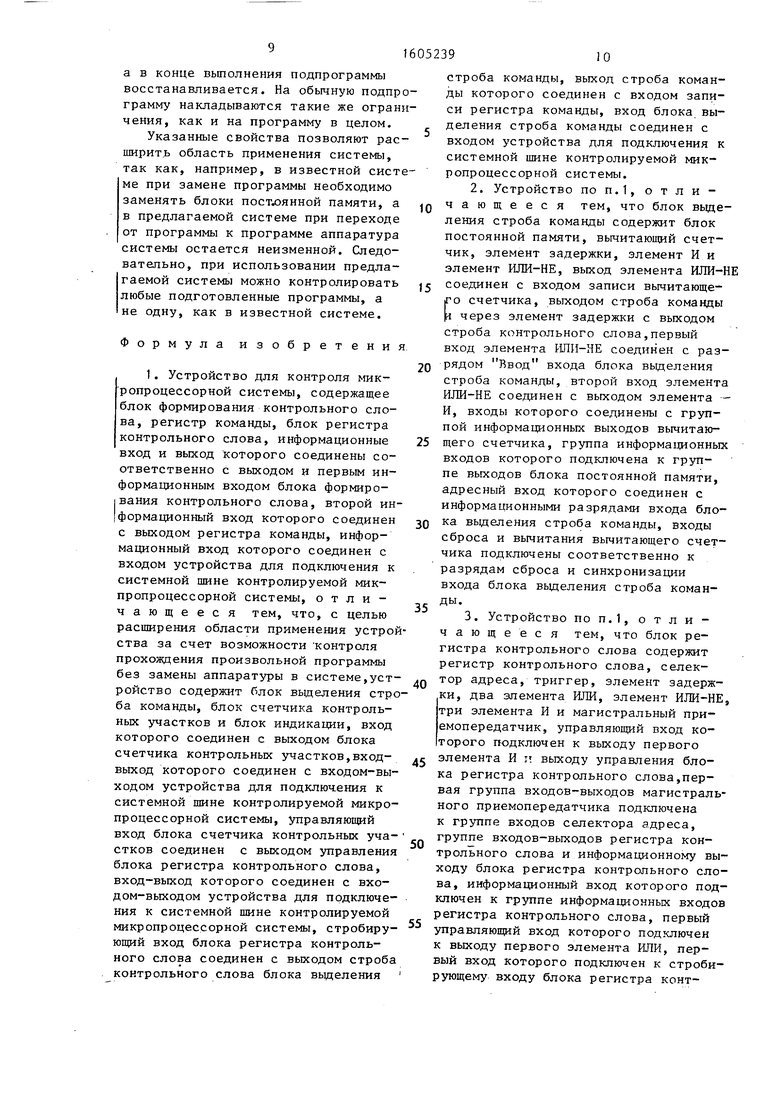

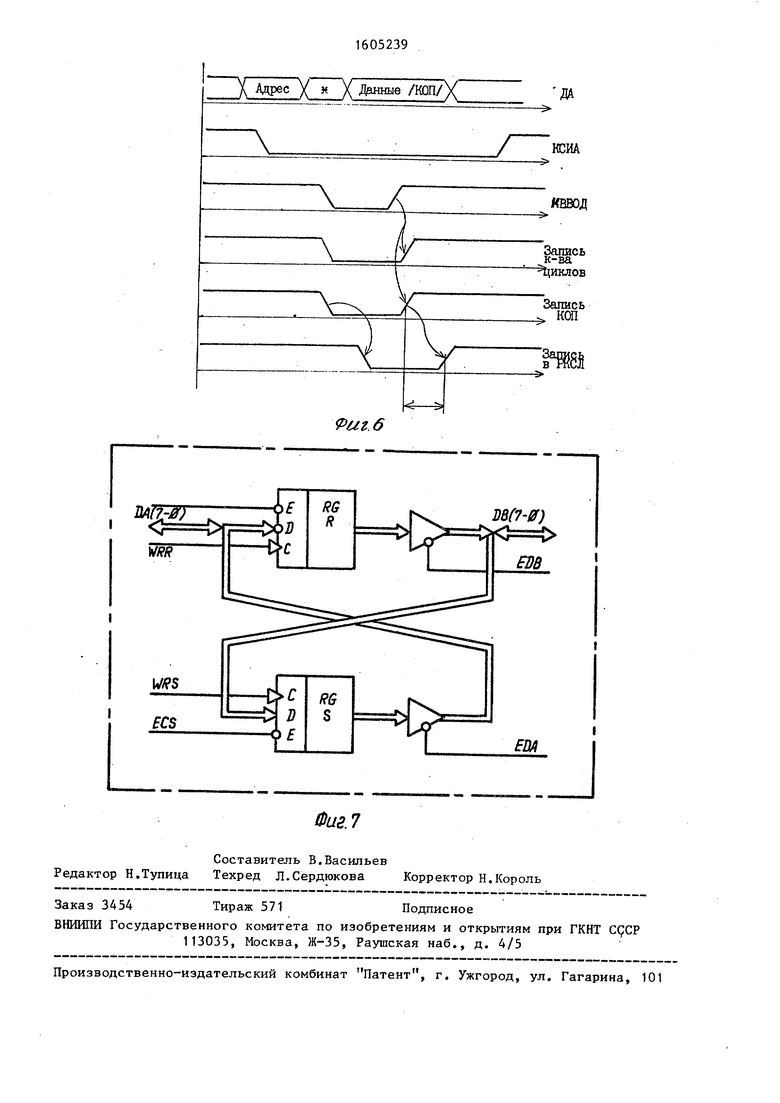

На фиг. 1 представлена структурная схема устройства; на фиг.2 - структурная схема блока вьщеления строба команды; на фиг.З - структур- ная схема блока регистра контрольного слова; на фиг.4 - блок формирот вания контрольного слова; на фиг.З i блок счетчика контрольных участков; на фиг.б - временная диаграмма ра- боты блока вьщеления строба команды; на фиг.7 - схема регистра команды и регистра контрольного слова блока регистра контрольного слова.

На схеме (фиг.1) обозначены: про- цессор 1, системная шина 2, блок 3 запоминающего устройства (ЗУ), блок 4 внешних устройств (ВУ), блок 5 выделения строба команды, регистр 6 команды, блок 7 регистра контроль- ного слова блок 8 формирования контрольного слова, блок 9 счетчика контрольных участков, блок 10 индикации

Блок 5 вьщеления строба команды (фиг.2) содержит блок 11 постоянной памяти (ПЗУ), вычитающий счетчик 12, элемент И 13, элемент ИЛИ-НЕ 14, элемент 15 задержки.

Блок 7 регистра контрольного сло- |ва (фиг.З) содержит магистральный

приемопередатчик 16, регистр 17 контрольного слова, селектор 18 адреса, триггер 19, первый элемент ИЛИ 20, элемент ИЛИ-НЕ 21, второй элемент ИЛИ 22, элементы И 23-25, эле- мент 26 задержки.

Блок 8 формирования контрольного слова (фиг.4) представляет собой сумматор 27.

Блок 9 счетчика контрольных уча- стков (фиг,5) содержит вычитающий счетчик 28, первый: элемент И 29, элмент ИЛИ 30, элементы И 31-33, магистральный приемопередатчик 34, селектор 35 адреса, триггер 36, элемент 37 задержки.

Для того, чтобы вычислительная система работала надежно, должно быть обеспечено надежное исполнение

5

Q

5

Q

5

программ. Однако в реальных условиях нормальное выполнение программы может быть нарушено, так как возможны сбои, отказы аппаратуры и другие причины. Поэтому важно за минимальное время обнаружить сам факт нарушения выполнения хода программ.

Предлагаемое устройство осуществляет контроль за программами, выполняемыми в данной вычислительной системе. Контроль осуществляется путем сложения всех кодов операций (по модулю 256) и затем программного сравнения полученного результата с заранее рассчитанным эталоном. В данной системе предполагается, что вычислительная система имеет конфигурацию типа Q - BUS, которая используется в микроэвм Электроника-60. Данный подход предполагает наличие совмещенного канала адреса и данных. Системная шина - это управляющие линии и совмещенные каналы адреса и данных.

Устройство работает следующим образом.

Блок 5 вьщеления строба команд выделяет момент наличия на системной шине 2 первого слова команды, который фиксируется в регистре 6 команды. Первое слово команды вместе с предьщушлм значением контрольного слова подается на входы блока 8 формирования контрольного слова. Полученный результат по сигналу, полученному из блока 5 вьщеления строба команд, записывается в регистр 17 контрольного слова блока 7 контрольного слова. В любой точке программы это значение можно считать из регистра 17 контрольного слова блока 7 (данный регистр программно доступен) и значение контрольного слова сравнивается программно с заранее вычисленным (эталонное значение контрольного слова может рассчитываться или вручную, или с помощью специальной программы транслятора, который добавляет в текст программы специальные команды, считывающие значения контрольного слова и сравнивающие это зна чение с эталоном).

Однако в случае неправильного выполнения программь, например из-за отказа процессора 1, сравнение эталона и контрольной суммы может не произойти. Для этого случая предусмотрен следующий механизм контиоля..

В самом начале программы в счетчик 28 контрольных участков блока 9 счетчика контрольных участков заносися количество контрольных участков в программе. Под контрольным участком понимается часть программы, которая заканчивается операцией считывания контрольного слова и сравнения его с эталоном. Во время программного обращения к блоку регистра контрольного слова формируется сигна о программном обращении к регистру контрольного слова, который передается в счетчик 28 контрольных участков блока 9, где из заданного количества обращений вычитается 1. В таком случае после нормального выполнения программы счетчик 28 блока 9 должен содержать значение О, которое вызывает срабатывание блока индикации (например, свечение светоди- ода). В противном случае, например, если вьппел из строя процессор 1, све тодиод гореть не будет, что свидетельствует об ошибке выполнения программы.

Структуры блоков 5-9 предлагаемого устройства приведены для случая использоваш я микроЭБМ Электрони- ка-60 М. При описании работы предлагаемой системы используются следующие обозначения:

КСИА - сигнал синхронизации активного устройства,

КСИП - сигнал синхронизации пассивного устройства, КВВОД - ввод данных КВЫВОД - вывод данных, КВУ - вьшод внешнего устройства, КСБРОС - первоначальная установка канала.

В блоке 5 выделения строба команд при включении питания в указанных вьше микроэвм генерируется канальный сигнал общего сброса КСБРОС. По этому сигналу вычитающий счетчик 12 блока 5 вьщеления строба команды сбрасывается в О.

Первыми данными, которые появятся на шине, будет первое слово команды, которое поступит на вход ПЗУ 11 блока 5, и на выходе ПЗУ появится код, определяющий, сколько в данной команде будет обращений к памяти.Данная операция необходима, так как в произвольном случае невозможно отделить первое слово команды от операндов. Поэтому необходимо отслеживать с первой команды время появления первых слов операции на системной шине. Таким образом, по адресам соответствующим кодам первых слов команд, записаны коды, определяющие длительность команды в циклах обращения к системной шине (сколько нужно пропустить циклов, чтобы учитывать

д только следующее первое слово команды) . Приведен пример такого соответствия: первое слово команды - код количества обращения к системному каналу (шине). Команда CLRR1 имеет

5 первое слово 005001 (значение кода приведено в .восьмеричном значении). Так как для выполнения этой команды не нужны дополнительные обращения к памяти, а следовательно, и к сис0 темной шине, то значение, которое будет находиться по адресу 005001 в ПЗУ 11, будет 1.

У команды CLRUH#1000 (восьмеричный код команды 005037 001100) пер5 вое слово команды 005037. Для данной команды нужно еще одно обращение к памяти, поэтому значение в соответствующей ячейке ПЗУ 11 будет 2. После сброса в вычитающем счетчи-

0 ке 12 будет значение О, на выходе элемента И 13 также будет значение О. Поэтому, начиная с первой команды, и далее в случае значения счетчика О и по отрицательному перепа

ду сигнала КВВОД появится сигнал За

пись на управляющем входе счетчика 12. По этому же сигналу код операции запишется в регистр 6 команды. В конце каждого цикла по положительному перепаду канального сигнала КСЙА из вычитающего счетчика будет вычтена 1, что обеспечит его значение О во время приема следующего кода операции. Первое слово команды поступит

на один из групповых информационных входов блока 8 формирования контрольного слова, на второй вход будет подано значение,поступающее с регистра 17 контрольного слова блока 7.Блок

8 формирования контрольного слова представляет собой комбинационную схему. Поэтому сигнал, формируемый огическим элементом ИЛИ 14 блока 5, проходит через элемент 15 задержки (RC-цепочка), которая учитывает заержку, необходимую на формирование контрольного слова в блоке 8 форми- ; ования контрольного слова, и являет ся стробом для записи полученного

значения контрольного слова в регистр 17 блока 7. Временная диаграмма сигналов, сопровождающих описанный процесс работы блока 5, приведена на фиг.6.

При программном обращении к регистру 17 контрольного слова блок 7 работает следующим образом. Магистральный приемопередатчик в исходном состоянии включен на прием с системной шины 2. Таким образом, если адрес системной шины соответствует адресу регистра 17 контрольного слова, то на выходе селектора 18 адреса появится логическая еди1шца (селектор адреса представляет собой схему сравнения кода с константой). Логический результат работы селектора адреса по сигналу КСИА записывается в триггер 19. Выход триггера 19 включается сигналом разрешения обращения к регистру. Сигнал с триггера 19 в случае операции записи (КВЫВОД) или чтения (КВВОД) через элемент 26 задержки фор мирует ответный сигнал блока 7. Величина задержки, формируемой элементом задержки, определяется требованиями к временным соотношениям. В случае программного чтения магистральный приемопередатчик 16 блока 7 переключается на направление от регистра 17 контрольного слова к системной шине 2. Это обеспечивается логическим элементом 24, выход которого подключен к управляющему входу магистрального приемопередатчика 16. Возможное исполнение регистра 17 представлено на фиг.7. Управление таким регистром обеспечивается Л огичес1шми элементами 20, 21 и 25. В случае программного обращения к регистру 17 контрольного слова формируется сигнал о программном обращении к регистру 17 контрольного слова с помощью логического элемента 24. Этот логический сиг- нал поступает на управляющий вход вычитающего счетчика 28 блока 9.

Блок 9 счетчика контрольных участ ков работает следующим образом. В начале программы в счетчике 28, ко- торьш является программно-доступным, записывается значение количества контрольных участков. По сигналу, приходящему из блока 7 регистра контрольного слова (И 24), из значения кода, находящегося в вычитающем счетчике 28, вычитается 1. Таким образом, в конце программы при правиль

5

0

5

0

5

0

5

0

5

hOM выполнении ее значение, хранимое в счетчике должно быть равно О. Если нет, то сигнал, формируемый на выходе элемента 29, вызовет срабатывание блока индикации (загорание све- тодиода), что свидетельствует о неправильной работе системы. Работа магистрального приемопередатчика 34, селектора 35 адреса, триггера 36 рассматривалась при описании блока 7. Элементы 30-33 и 37 необходимы для синхронизации работы указанных выше элементов.

Рассмотрим ограничения, накладываемые на программирование в данной системе. Дпя предоставления структуры любой сложной программы можно пользоваться комбинацией трех базовых структур: Следование, Развилка и Цикл. Все данные структуры имеют один вход и один выход. Суммы первых слов команд в общем случае и в различных ветвях этих структур различны. Поэтому без дополнительных мер аппаратура контроля на данных участках может зафиксировать сбой программы, которого фактически нет. Дпя того, чтобы этого не случилось, необходимо искусственно выравнивать суммы первых слов команды (контрольные слова) в ветвях структуры до одинакового значения перед каждый объединением ветвей. Выравнивание сумм первых слов команды может быть легко выполнено следующим образом. Перед каждой точкой объединения ветвей базовых структур вставляются дополнительные команды, которые заносят в регистр 17 контрольного слова блока 7 скорректированное значение контрольного слова. Вьфавнивание контрольного слова может быть вьшолнено одной командой. Так как суммирование первых слов команд производится по некоторому модулю, например по модулю 256, всегда можно указать число, дополняющее сумму до нужного значения. Расчет корректирующих значений может быть произведен либо программистом, либо с помощью специального траслятора, который рассчитывает корректирующее значение и вставляет необходимые дополнительные команды в программу. При использовании подпрограмм обработки прерываний можно использовать следующий прием. В начале указанных подпрограмм значение контрольного слова запоминается.

а в конце выполнения подпрограммы восстанавливается. На обычную подпрграмму накладываются такие же огранчения, как и на программу в целом.

Указанные свойства позволяют расширить область применения системы, так как, например, в известной систме при замене программы необходимо заменять блоки пост.оянной памяти, а в предлагаемой системе при переходе от программы к программе аппаратура системы остается неизменной. Следовательно, при использовании предлагаемой системы можно контролировать любые подготовленные программы, а не одну, как в известной системе.

Формула изобретения

1. Устройство для контроля микропроцессорной системы, содержащее блок формирования контрольного слова, регистр команды, блок регистра контрольного слова, информационные вход и выход которого соединены соответственно с выходом и первым информационным входом блока формирования контрольного слова, второй информационный вход которого соединен с выходом регистра команды, информационный вход которого соединен с входом устройства для подключения к системной шине контролируемой мик- пропроцессорной системы, отличающееся тем, что, с целью расширения области применения устройства за счет возможности контроля прохождения произвольной программы без замены аппаратуры в системе,устройство содержит блок вьщеления строба команды, блок счетчика контроль- ньк участков и блок индикации, вход которого соединен с выходом блока счетчика контрольных участков,вход- выход которого соединен с входом-выходом устройства для подключения к системной тине контролируемой микропроцессорной системы, управляющий вход блока счетчика контрольных участков соединен с выходом управления блока регистра контрольного слова, вход-выход которого соединен с входом-выходом устройства для подключения к системной шине контролируемой микропроцессорной системы, стробиру- ющий вход блока регистра контрольного слова соединен с выходом строба контрольного слова блока вьзделения

15

20

25

5

строба команды, выход строба команды которого соединен с входом записи регистра команды, вход блока вы- g деления строба команды соединен с входом устройства для подключения к системной шине контролируемой микропроцессорной системы.

2. Устройство по П.1, о т л и - JQ чающееся тем, что блок выделения строба команды содержит блок постоянной памяти, вычитающий счетчик, элемент задержки, элемент И и элемент ИЛИ-НЕ, выход элемента ИЛИ-НЕ соединен с входом записи вычитающего счетчика, выходом строба команды И через элемент задержки с выходом строба контрольного слова,первый вход элемента РШИ-НЕ соединен с разрядом Ввод входа блока вьщелания строба команды, второй вход элемента ИЛИ-НЕ соединен с выходом элемента - И, входы которого соединены с группой информационных выходов вычитающего счетчика, группа информационных входов которого подключена к группе выходов блока постоянной памяти, адресный вход которого соединен с информационными разрядами входа блока выделения строба команды, входы сброса и вычитания вычитающего счетчика подключены соответственно к разрядам сброса и синхронизации входа блока выделения строба команды.

3. Устройство по П.1, отличающееся тем, что блок регистра контрольного слова содержит регистр контрольного слова, селектор адреса, триггер, элемент задержки, два апемента ИЛИ, элемент ИЛИ-НЕ, три элемента И и магистральный приемопередатчик, управляющий вход которого гюдключен к выходу первого элемента И и выходу управления блока регистра контрольного слова,первая группа входов-выходов магистрального приемопередатчика подключена к группе входов селектора адреса, группе входов-выходов регистра контрольного слова и информационному выходу блока регистра контрольного слова, информационный вход которого подключен к группе информационных входов регистра контрольного слова, первый управляющий вход которого подключен к выходу первого элемента ИЛИ, первый вход которого подключен к строби- рующему входу блока регистра конт30

35

0

5

0

рольного слова, второй вход первого элемента ИЛИ, второй управляющий вход регистра контрольного слова и вход элемента ИЛИ-НЕ подключены к вы- ходу второго элемента И, первый вход которого, первые входы первого и третьего элементов И подключены к выхо- ду триггера, информационный вход которого подключен к выходу селектора адреса, вход элемента задержки подключен к выходу третьего элемента И, второй вход которого подключен к выходу второго элемента ИЛИ, первый вход которого и второй вход первого элемента И подключены к разряду Ввод входа-выхода блока регистров контрольного слова, второй вход второго элемента ИЛИ и второй вход второго элемента И подключены к разряду Вывод входа-выхода блока регистра контрольного слова, разряд синхронизации входа-выхода которого соединен с синхронизирующим входом триггера, разряд ответного сигнала входа выхода блока регистра контрольного слова подключен к выходу элемента задержки, вторая группа входов-выходов магистрального приемопередатчика соединена с информационными разрядами входа-выхода блока регистра контрольного слова, третий управляющий вход регистра контрольного слова подключен к выходу элемента ИЛИ-НЕ.

4, Устройство ПОП.1, отличающееся тем, что блок счетчика контрольных участков содержит селектор адреса, вычитающий счетчик, триггер, четыре элемента И, элемент

5 О

5

0

5

0

задержки, элемент ИЛИ и магистральный приемопередатчик, первая группа входов-выходов которого подключена соответственно к группам информационных входов селектора адреса и вычитающего счетчика, группа выходов которого, подключена к входам первого элемента И, выход которого подключен к выходу блока счетчика контрольных участков, первые входы второго, третьего и четвертого элементов И объединены и подключены к выходу триггера, информационный вход которого подключен к выходу селектора адреса, выход второго элемента И подключен к счетному входу вычитающего счетчика, выход третьего элемента И подключен к входу элемента задержки, выход четвертого элемента И подключен к управляющему входу магистрального приемопередатчика, вторая группа входов-выходов которого подключена к информационным разрядам входа-выхода блока счетчика контрольных участков, Вывод, Ввод синхронизации и ответного сигнала входа-выхода которого подключены соответственно к объединенным второму входу второго элемента И и первому входу элемента ИЛИ, объединенным второму входу элемента ИЛИ и второму входу четвертого элемента И, синхронизирующему входу триггера и выходу элемента задержки, выход элемента ИЛИ подключен к второму входу третьего элемента И, управляющий вход вычитаю- щегр счетчика подключен к управляющему входу блока счетчика контрольных участков.

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

| Программируемый логический контроллер | 1984 |

|

SU1497616A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО МЕЖМАШИННОГО ПРЯМОГО ДОСТУПА К ПАМЯТИ | 2021 |

|

RU2775703C1 |

| Устройство для контроля канала связи | 1987 |

|

SU1478351A1 |

| Устройство для контроля вычислительного процесса ЭВМ | 1988 |

|

SU1596332A1 |

| Система для контроля микропроцессорных устройств | 1983 |

|

SU1228108A1 |

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

| Устройство для контроля хода программы и перезапуска ЭВМ | 1985 |

|

SU1337901A1 |

| Устройство для контроля хода программы и перезапуска ЭВМ | 1987 |

|

SU1501066A2 |

| Устройство для отладки программно-аппаратных комплексов | 1990 |

|

SU1795464A1 |

Изобретение относится к вычислительной технике и предназначается для построения надежных вычислительных систем со встроенным контролем. Цель изобретения - расширение области применения за счет возможности контроля прохождения произвольной программы без замены аппаратуры в системе. Система содержит процессор 1, блок 3 запоминающего устройства, блок 4 внешних устройств, регистр 6 команды, блок 5 выделения строба команды, блок 7 регистра контрольного слова, блок 8 формирования контрольного слова, блок 9 счетчика контрольных участков и блок 10 индикации. Блок выделения строба команды выделяет момент наличия на системной шине первого слова команды, который запоминается в регистре команды. Код команды подается на блок формирования контрольного слова и складывается с предыдущим значением контрольного слова. Результирующее контрольное слово запоминается в блоке регистра контрольного слова и может быть считано программой и проверено. Блок счетчика контрольных участков считает количество программных обращений к блоку регистра контрольного слова. В случае, если к концу выполнения программы число обращений к блоку контрольного слова не соответствует заданному, то блок индикации генерирует сигнал ошибки. 3 з.п.ф-лы, 7 ил.

г

Фиг. If

Фиг.5

Риг.6

ЕШ

| Устройство для контроля блока управления роботом | 1982 |

|

SU1119018A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля хода программ | 1984 |

|

SU1191912A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-11-07—Публикация

1988-08-05—Подача