И

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации динамических процессов | 1989 |

|

SU1702358A1 |

| Устройство для отладки программ | 1983 |

|

SU1174932A1 |

| Регистрирующее устройство | 1988 |

|

SU1509595A1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для регистрации динамических процессов | 1988 |

|

SU1624437A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1985 |

|

SU1322362A1 |

| МНОГОМОДУЛЬНОЕ УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ТЕКСТОВОЙ И ГРАФИЧЕСКОЙ ИНФОРМАЦИИ | 1992 |

|

RU2037885C1 |

Изобретение относится к вычислительной технике и может быть использовано для запоминания информации при измерении амплитудных и временных параметров, анализе формы исследуемых процессов. Цель изобретения - повышение быстродействия устройства. Устройство содержит блоки 2 и 3 памяти, счетчики 7 и 8, элемент ИЛИ 9, мультиплексоры 11 - 13, триггеры 14 - 16, блок 17 синхронизации. На выход устройства подключается цифроаналоговый преобразователь 5. Быстродействие устройства повышается за счет обеспечения режима непрерывного запоминания и индикации формы исследуемого сигнала. 2 ил.

О

s

с о а :

i

Изобретение относится к вычислительной технике и может быть использовано для запоминания информации при измерении амплитудных и временных параметров анализе формы исследуемых процессов

Цель изобретения повышение быстро действия устройства

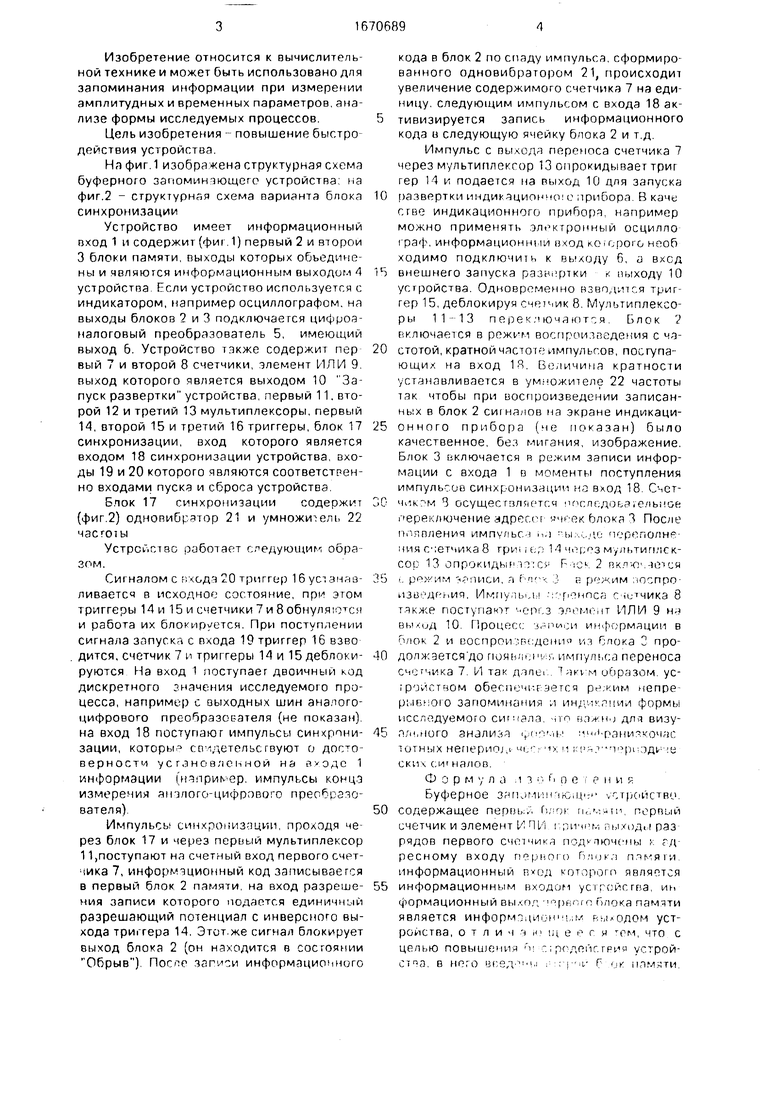

На фиг 1 изобра-кена структурная схема буферного запоминающего устройства на фиг.2 - структурная схема варианта блока синхронизации

Устройство имеет информационный вход 1 и содержит (фи( 1) первый 2 и второй 3 блоки памяти выходы которых обьедине- ны и являются информационным выходом А устройства Если устройство используется с индикатором, например осциллографом, на выходы блоков 2 и 3 подключается цифроа- налоговый преобразователь 5, имеющий выход б Устройство также содержит пер вый 7 и второй 8 счетчики, элемент ИЛИ 9 выход которого является выходом 10 Запуск развертки устройства первый 11.второй 12 и третий 13 мультиплексоры, первый 14, второй 15 и третий 16 триггеры, блок 17 синхронизации, вход которого является входом 18 синхронизации устройства входы 19 и 20 которого являются соответственно входами пуска и сброса устройства

Бпок 17 синхронизации содержит (фиг 2) одновибрятор 21 и умножитель 22 часг01Ы

Устройство оаботает следующим обра зом.

Сиi налом с F, одч 20 триггер 16 уст знав- ливаетсч в исходное состояние, npi/1 этом триггеры 14 и 15 и счетчики 7 и 8 обнуляющем и работа их блокируется При поступлении сигнала запуска с 19 триггер 16 взво дится, счетчик 7 и триггеры 14 и 15 деблоки- руются На вход 1 поступает двоичный код дискретного значения исследуемого процесса, например с выходных шин аналого- цифрового преобразователя (не показан) на вход 18 поступают импульсы синхрпни- зации, которы3 со 1гтстельсгвуют о верности установленной на 1 информации unnpnivep импульсы концэ измерения ашлого-цифрового прегбраяо- вателя)

Импульсы синхронизации проходя че рез блок 17 и через первый мультиплексор 11,поступают на счетный вход первого счет- вика 7, информационный код записывается в первый блок 2 памяти на вход разреше- ния записи которого подается единичной разрешающий потенциал с инверсного выхода триггера 14. Этот же сигнал блокирует выход блока 2 (он находится в состоянии Обрыв) Погге записи информационного

кода в блок 2 по спаду импульса сформированного одновибратором 21, происходит увеличение содержимого счетчика 7 на единицу следующим импульсом с входа 18 активизируется запись информационного кода в следующую ячейку блока 2 и т д

Импульс с вы мзда переноса счетчика 7 через мультиплексор 13 опрокидываеттриг тер 14 и подается на выход 10 для запуска оазвертки индикационно с прибора В каче сгве индикационного прибора например можно применять электронный осцилло i раф информационн л вход KOI open о необ ходимо подключить к выходу 6, с) вхсд внешнего запуска развертки к пыходу 10 устройства Одновременно взво JUK я триг тер 15, деблокируя -Чр чик 8 Мультиплексоры 11-13 п е р е к ю ч a to т, я Блок 2 включается в режгм воспроизведения с иа- стотой, кратной частот 1 импульсов, поступающих на вход 18 Величина кратности устанавливается в умножителе 22 частоты так чтобы при воспроизведении записанных в блок 2 сигналов на экране индикационного прибора (не показан) было качественное, без мигания, изображение Блок 3 включается в режим записи информации с входа 1 в моменты поступления импуль ив синхронизации на вход 18 Счет- 3 осуществляется шглсдоьгъемы ое 1 ерр члючение dflperot яч(-ек блока 3 После петпления ИМПУЛЬС i n.i ы пореполн0 шя С .етчика 8 rpmit, 14 чег, м/льтиплскСОС 13 ОПр КИДЬ| П О Г- 0k 2 ВКП-О ЮТСЯ

шеи i f п I Р робким iGcnpn изв демия Импуть и читчика 8 тчкже )т .ер- з эпем нт ИЛИ 9 н-- вы ид 10 Процег; ппи.и информации в плок 2 и воспрри в- денио ич Спока 2 продолжается до поян(|| Iм i имп/льс,а переноса счетчика 7 И так дтп1.1 7 --н v м ипразоги ус- ;роигтвом обегпьчсгчетсч ре сим непре рмв1- ого запоминания л ин м рнии формы исследуемого on длл визу- огн.ного анализа титных неперип;, ч| 1 и , -1 )дь j скпх с и налов

Формула 11 б о е Р и и F Буферное зг-тк Ш н (Ю. у трсатство содержащее первь., б, г, первый ичетчик и элемент V Hh i ,m (ем , 1,1 од1| раз рядов первого счетчика под тючены : гд

реСНОМу ВХОДУ )hOU) fi iiuj ПТМЯ1И

информационный пход которого является информационным входим ycircnrrpja ин цюрмационный вы-оп . i п п/юка памяти является информ иин1 / диодом устройства, о т л и ч ч ю i( е е г я тм мто с целью nosbiujeHHH п . ргдргк ТРИ) угтрой- стг-а в него Bie, v Г у |Щм-;ти

первый, второй и третий мультиплексоры, второй счетчик, первый, второй и третий триггеры и блок синхронизации, вход которого является входом синхронизации устройства, выходы блока синхронизации подключены к соответствующим информационным входам первого и второго мультиплексоров, выходы которых подключены соответственно к счетным входам первого и второго счетчиков, выход переноса первого счетчика соединен с первым информационным входом третьего мультиплексора, установочным входом второго триггера и первым входом элемента ИЛИ, выход которого является выходом Запуск развертки устройства, выход переноса второго счет чи- ка соединен с вторым входом элемента ИЛИ и вторым информационным входом третьего мультиплексора, выход которого подключен к входу синхронизации первого триггера, инверсный выход которого соединен с управляющими входами первого и третьего мультиплексоров и входами блокировки и разрешения записи первого блока памяти, прямой выход первого триггера подключен к управляющему входу второго мультиплексора и входам блокировки и разрешения записи второго блока памяти, информационный и адресный входы которого подключены соответственно к информационному входу устройства и выходам разрядов второго счетчика, информационный выход второго блока памяти соединен с информаци онным выходом устройства, инверсный выход -третьего триггера соединен с входами сброса первого и второго триггеров и первого счетчика, а также с первым входом сброса второго счетчика, второй вход сброса которого соединен с инверсным выходом второго триггера, установочный вход и вход сброса третьего триггера являются соответственно входами пуска и сброса устройства.

| Запоминающее устройство | 1985 |

|

SU1619282A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-08-15—Публикация

1985-12-16—Подача