Изобретение относится к вьгчислительной технике и может быть использовано при отладке программ и для настройки вычислительных аппаратных средств при наличии отлаженной программы.

Целью изобретения является рас.ширение функциональных возможностей устройства путем,запоминания групп адресов, предшествукяцих заданному адресу.

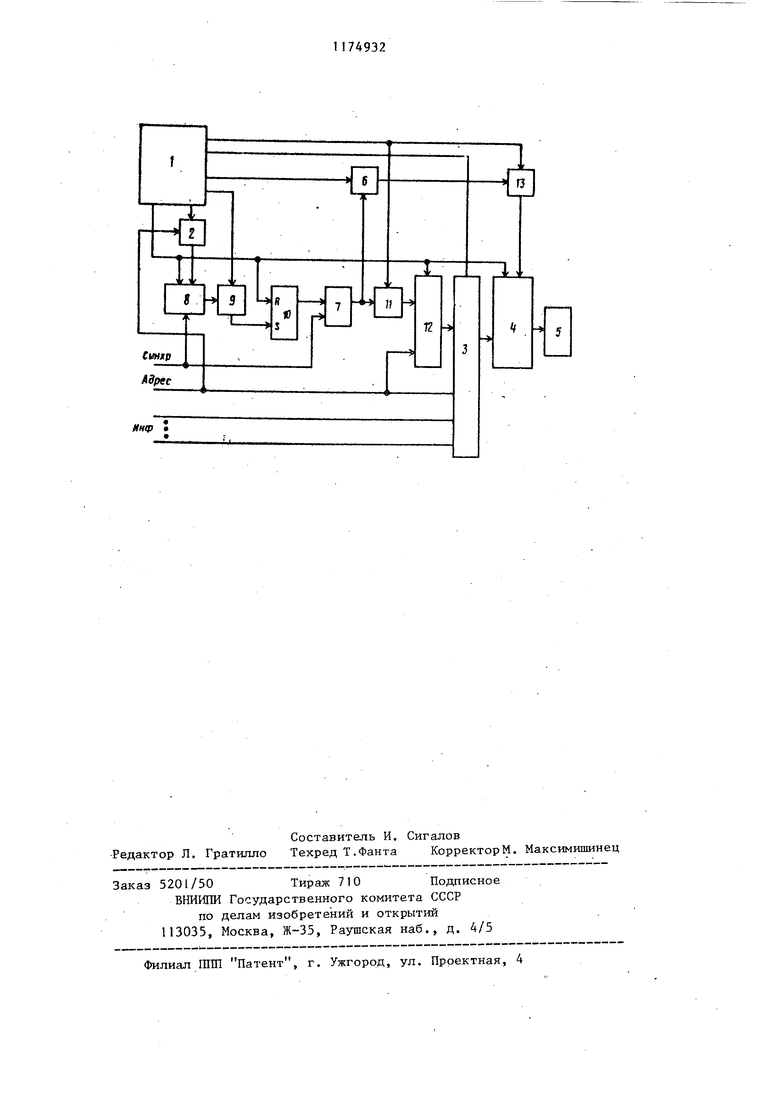

На чертеже изображена блок-схема предлагаемого устройства.

Устройство содержит блок 1 задания режимов, соединенный с блоком 2 сравнения, адресный вход которого подключен к адресному входу устройства. Последний соединен с первым информационным входом мультиплексора 3, управляющий вход которого соединен с вторым входом блока 1 задания режимов. Группа информационных входов мультиплексора 3 соединена с группой информационных входов устройства, выход мультиплексора 3 сое динен с входом индикационного регистра 4, выход которого соединен с блоком 5 индикации. Третий выход блока 1 задания режимов подключен к первому входу блока 6 управляемой задержки, второй вход которого подключен к выходу элемента И 7, первый вход которого соединен с синхронизирующим входом устройства. Информационный и синхронизирующий входы счетчика 8 соединены соответственно с выходом первого блока 2 сравнения и с синхронизирующим входом устройства, а в.ыход счетчика 8 - с первым входом второго .блока 9 сравнения, второй вход которого подключен к четвертому выходу клавиатуры I набора информации, а выход к входу RS-триггера 10. Выход триггера 10 соединен с вторым входом элемента И 7, выход которого соединен с первым входом первого элемента ИЛИ 11, который является синхронизирующим входом блока 12 регистров. Второй вход первого элемента ИЛИ 11 подключен к пятому выг ходу блока 1 задания режимов, который соединен с первым входом второго элемента ИЛИ 13. Второй вход второго элемента ИЛИ 13 подключен к выходу блока 6 управляемой задержKii, а выход - к синхронизирующему входу индикационного регистра 4.

Обнуляющий выход блока 1 задания режимов соединен с обнуляюпщми входами счетчика 8, блока 12 регистров, индикационного регистра 4 .и Р-входом

триггера 10. Информационный вход блока 12 регистров соединен с адресным входом устройстве, а выход - с вторым информационным входом мультиплексора 3.

Посредством выходов блока 1 задаются тип индицируемой информации, величина задержки синхроимпульса или номер микротакта .операции, адрес синхронизации, количество обращений

по заданному адресу или номер цикла, сдвиговый сигнал для перезаписи информации из регистра в регистр в блоке 12 регистров и из блока 12 регистров в индикационный регистр 4,

приведение устройства в исходное состояние.

Устройство работает следующим образом.

В исходном состоянии счетчик 8,

триггер 10, блок 12 регистров и регистр 4 индикации обнулены. Перед запуском программного устройства на блоке 1 набираются адрес синхронизации, номер цикла или количество

обращений по заданному адресу синхронизации, величина задержки или номер микротакта операции и тип информации, поступающей на регистр 4 индикации.

После запуска программного устройства на вход устройства для отладки программ начинают поступать .синхронизирующие curna ibi, а также адрес, по которому идет обращение,

;и необходимая для отладки информация.

Все адреса, по которым идет обращение в программе, поступают на информационный вход блока 12 регистров, представляющего собой набор

параллельных регистров, информационный вход одного из которых является адресным входом устройства, а информационные входы остальных соединены с выходами предащущих регистров блока, выход последнего регистра подключен к входу мультиплексора, синхронизирующие входы всех регистров объединены и являются синхронизирукщими входами блока 12 регистров.

Объем блока 12 регистров выбирается исходя из сложности программы и требуемого для ускорения отладки

31

количества информации. До появления на инверсном выходе RS-триггера 10 запрещающего сигнала состояние регистров блока 12 регистров и индикационного регистра 4 может изменяться по приходу каждого очередного синхроимпульса.

При появлении на входе устройства адреса, совпадающего с адресом синхронизации, формируется выходной сигнал блоком 2 сравнения, который является разрешающим для синхронного счетчика 8. После появления на входе устройства адреса синхронизации в том цикле, номер которого задан клавиатурой Т, счетчик 8 принимает значение, равное этому номеру, и на выходе блока 9 сравнения формируется сигнал, который переводит RSтриггер 10 в единичное состояние. При этом инверсный выход RS-триггера 10 блокирует прохождение синхроимпульсов с входа устройства на вход блока 12 регистров и индикационного регистра 4. Все адреса, которые записаны в блок 12 регистров запуска RS-триггера 10, сохраняются в нем до момента начала сдвига или обнуления блоком I задания режимов. ПоС ледний синхроимпульс, по которому происходит запись адреса в блок 12 регистров, задерживается в блоке 6 управляемой задержки на заданное блоком 1 количество микротактов и является синхроимпульсом записи информации в индикационный регистр 4 через мультиплексор 3.

После окончания или останова программы в индикационном регистре 4 записывается либо текущий адрес программы, либо адрес программы, зафиксированный в последнем регистре блока 12 регистров, либо состояние группы информационных входов устройства на момент совпадения содержимого счетчика 8 со значением выхода блока 1, задержанного на заданное число микротактов, либо адрес последующей команды программы (при совпадении значения выхода блока 1 с количеством микротактов выполнения операций).

24

После визуального контроля информации индикационного регистра 4 программист имеет возможность записи на блок индикации содержимого поочередно всех регистров блока I2 регистров, нажимая и отпуская кнопку Сдвиг блока 1, так как в блоке регистров записаны адреса, предшествующие заданному, то не требуется многократный перезапуск программы, чтобы проследить ее ход, что обеспечивает уменьшение времени отладки. Кроме того, часто невозможно проследить ход программы

по одной-двум точкам, даже перезапуская ее, так как начальные и промежуточные условия и порядок выполнения программы изменяются от запуска к запуску.

Перед очередным запуском программы необходимо обнулить устройство путем нажатия кнопки Обнуление.

Таким образом, за счет введения в устройство счетчика, второго блока сравнения, RS-триггера, блока

регистров и двух злементов ИЛИ обеспечиваются фиксация момента появления адреса синхронизации заданное число раз, а также фиксация и последующая индикация необходимого количества предшествующих заданному адресов. Все это позволяет вести отладку циклических и сложгазгх разветвленных программ, в том числе

в реальном масштабе времени, уменьшить время отладки, а также настра1шать сложные программируемые устройства, проводить поиск неисправностей в них тоже в реальном масштабе времени.

Предложенное устройство обеспечивает программиста достаточным объемом информации для отладки линейных, циклических, разветвленных программ (в том числе в реальном масштабе времениJ с изменяющимися начальными и промежуточными условиями, когда трудно определить участок

или ветку программы по двум имеющимся точкам.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1979 |

|

SU960821A1 |

| Устройство для отладки программ | 1980 |

|

SU1043657A2 |

| Устройство для отладки программ | 1984 |

|

SU1275452A1 |

| Устройство для записи и коррекции программ | 1982 |

|

SU1149268A1 |

| Устройство для отладки программ | 1986 |

|

SU1410038A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1587514A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Логический анализатор | 1987 |

|

SU1476474A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Нанопрограммное устройство управления | 1983 |

|

SU1136160A1 |

УСТРОЙСТВО ДЛЯ ОТЛАДКИ ;ПРОГРАММ, содержащее блок задания режимов, первьш блок сравнения, элемент И, блок управляемой задержки, индикационный регистр, блок индикации и мультиплексор, причем выход адреса синхронизации блока задания режимов соединен с первым входом первого блока сравнения, второй вход которого соединен с адресным входом устройства, вход синхронизации устройства соединен с первым входом элемента И, выход которого соединен с входом блока управляемой задержки, выходы вида информации номера микротакт а блока задания режимов соединены соответственно с вторым входом блока управляемой задержки и управляющим , входом мультиплексора, выход которого соединен с информационным входом индикационного регистра, выход индикационного регистра соединен с входом блока индикации, адресный вход устройства соединен с первым информационным входом мультиплексора, группа информационных входов которого соединена с группой информационных входов устройств, о т. л и чающееся тем, что, с целью расширения функциональных возможностей устройства путем запоминания групп адресов, предшествующих заданному адресу, в устройство введены триггер, второй блок сравнения, первьш и второй элементы ИЛИ, блок регистров и счетчик, причем вход синхронизации устройства и выход первого блока сравнения соединены соответственно с входом синхронизации счетчика и информационным входом счетчика, выход которого соединен с первым входом второго блока сравнения, выход второго блока сравнения соединен с единичным входом триггера, выход которого соединен с ю вторым входом элемента И, выход ко(Л торого соединен с первым входом первого элемента ИЛИ, выход первого элемента ИЛИ соединен с входом синхронизации блока регистров, адресный вход устройства соединен с информационным входом блока регистров, выход которого соединен с вторым информационным входом мультиплек-1 сора, выходы номера цикла и переза со со ю писи блока задания режимов соединены соответственно с вторым входом второй схемы сравнения и первым входом второго элемента ИЛИ, выход которого соединен с входом разрешения индикаторного регистра, выход блока управляемой задержки и выход перезаписи блока задания режимов соединены соответственно с вторьтми входами второго элемента ИЛИ и первого элемента ИЛИ, выход начальной установки блока задания режимов соединен с входом начальной установки счетчика, нулевым входом триггера, входом установки в О блока регистров и регистра индикации.

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Устройство для отладки программ | 1979 |

|

SU960821A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| . | |||

Авторы

Даты

1985-08-23—Публикация

1983-06-20—Подача