Изобретение относится к вычислительной технике и может быть использовано при обработке цифровой информации, в частности при построении конвейерной системы выработки команд для процессора.

Целью изобретения является увеличение быстродействия и расширение области применения за счет обеспечения возможности динамического изменения величины интервала.

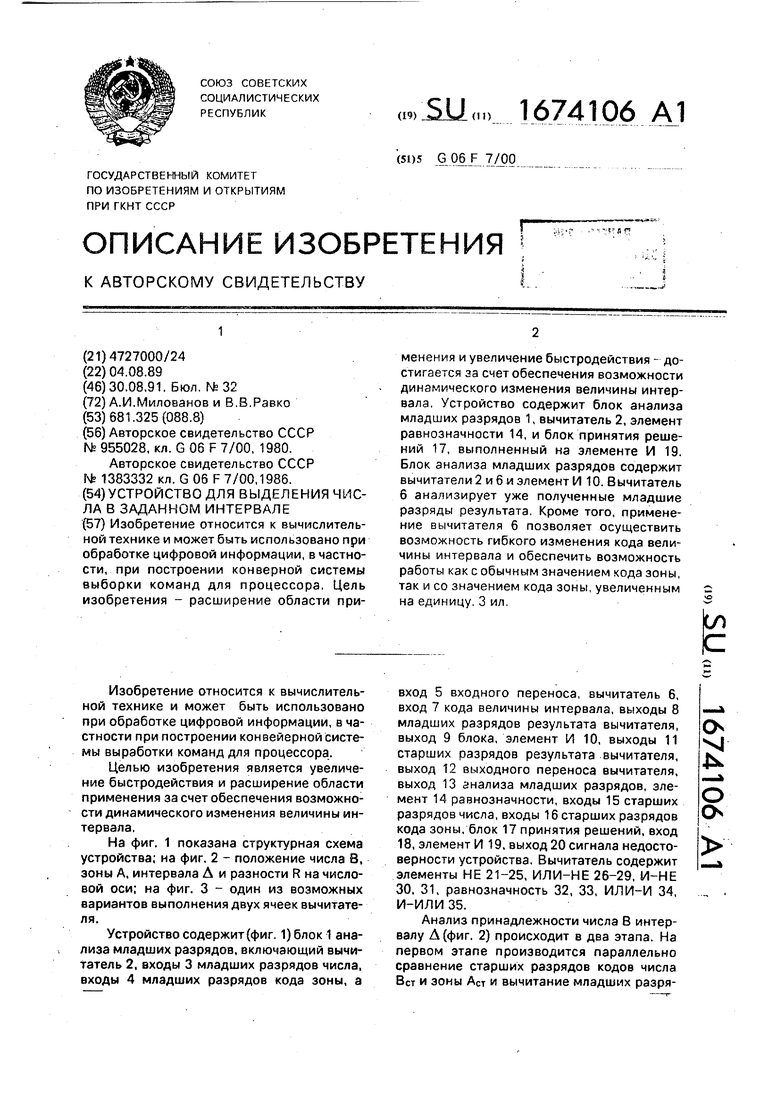

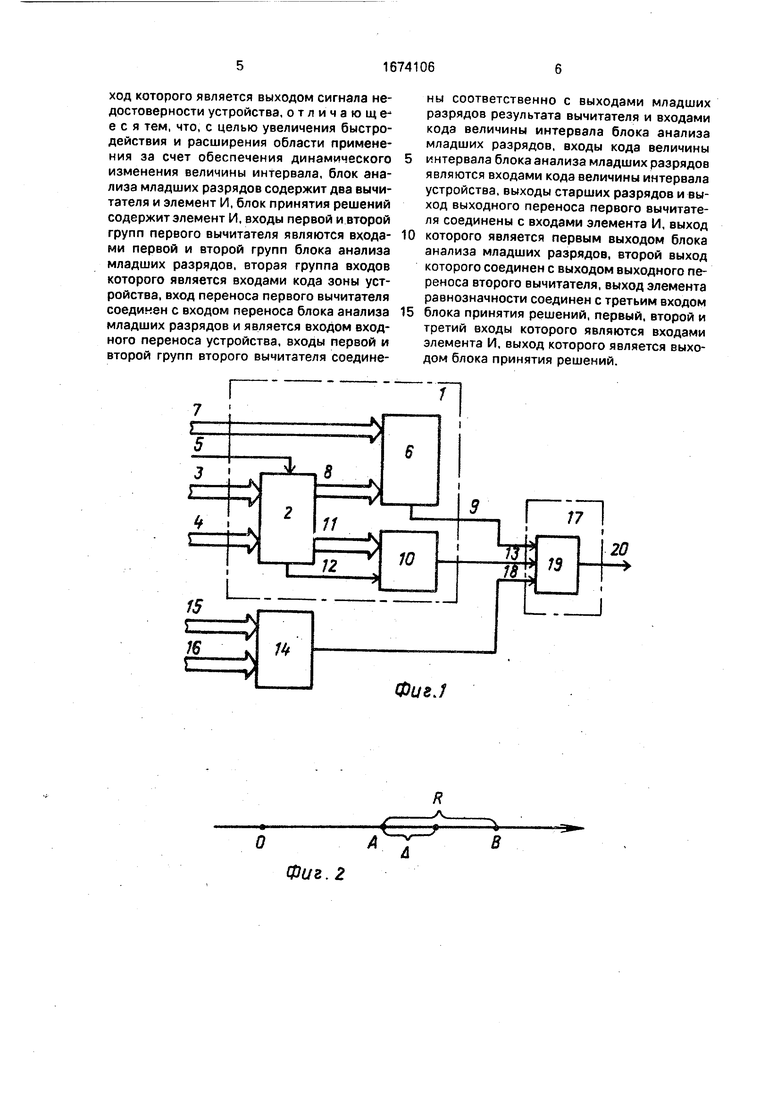

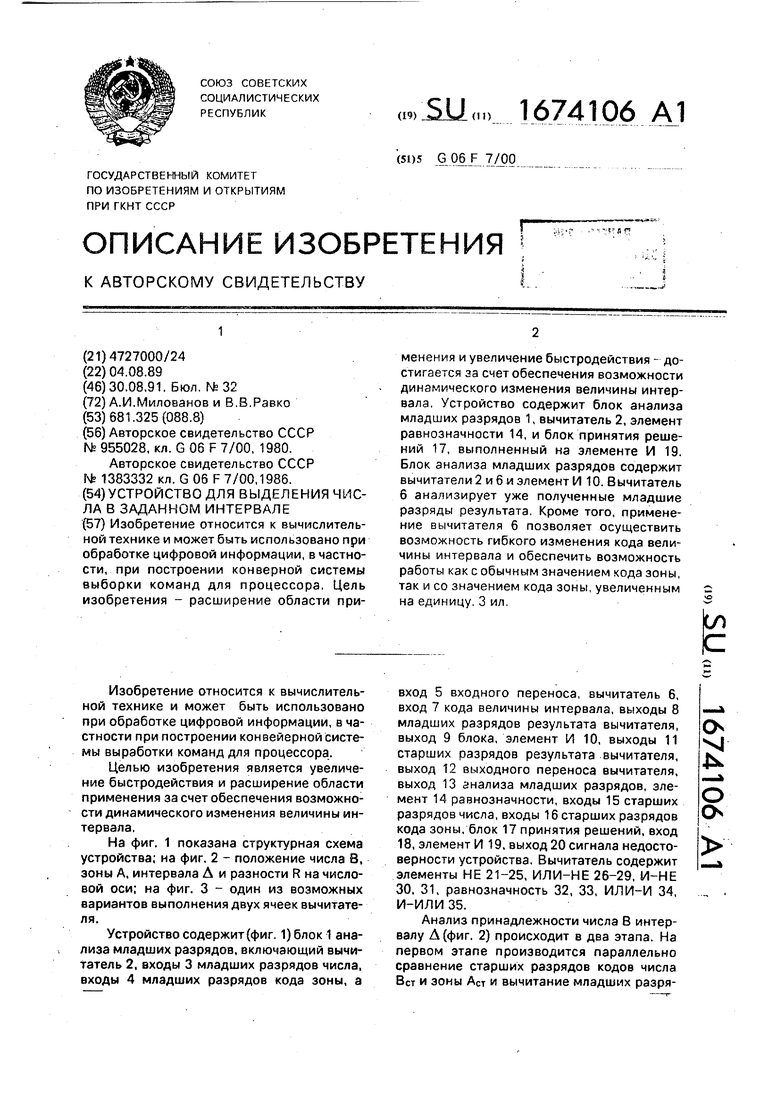

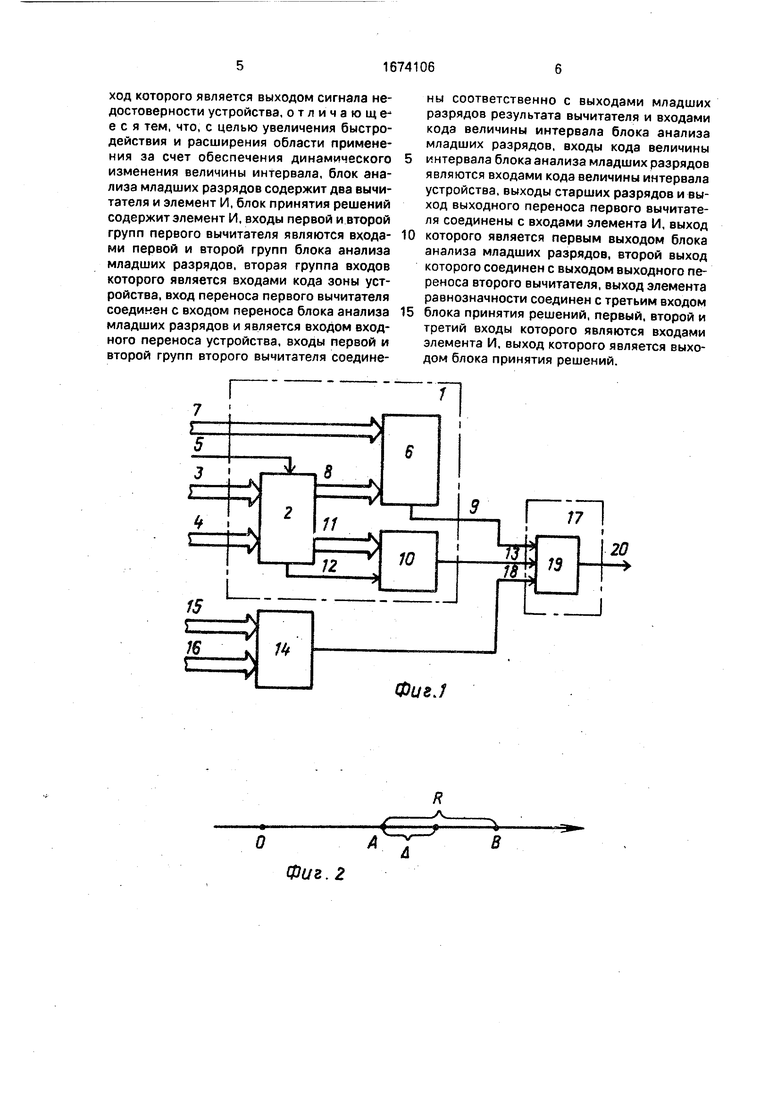

На фиг. 1 показана структурная схема устройства; на фиг. 2 - положение числа В, зоны А, интервала Л и разности R на числовой оси; на фиг. 3 - один из возможных вариантов выполнения двух ячеек вычитателя.

Устройство содержит (фиг. 1)блок 1 анализа младших разрядов, включающий вычитатель 2, входы 3 младших разрядов числа, входы 4 младших разрядов кода зоны, а

вход 5 входного переноса, вычитатель 6, вход 7 кода величины интервала, выходы 8 младших разрядов результата вычитателя, выход 9 блока, элемент И 10, выходы 11 старших разрядов результата вычитателя, выход 12 выходного переноса вычитателя, выход 13 анализа младших разрядов, элемент 14 равнозначности, входы 15 старших разрядов числа, входы 16 старших разрядов кода зоны, блок 17 принятия решений, вход 18, элемент И 19, выход 20 сигнала недостоверности устройства. Вычитатель содержит элементы НЕ 21-25, ИЛИ-НЕ 26-29, И-НЕ 30, 31, равнозначность 32, 33, ИЛИ-И 34, И-ИЛИ 35.

Анализ принадлежности числа В интервалу Л (фиг. 2) происходит в два этапа. На первом этапе производится параллельно сравнение старших разрядов кодов числа Вст и зоны ACT и вычитание младших разря О Ы Ј

О

о

дов этих кодов, т.е. ВМл-АМл. Параллельность этих действий сокращает общее время анализа. Если число В отличается от зоны А на величину, гораздо большую значения интервала Л (старшие разряды А и В не совпадают), то сразу делается вывод о том, что В не принадлежит А (выдается сигнал недостоверности). Если старшие разряды А и В совпадают, то анализируется разность младших разрядов В и А. Если разность Вмл-Амл, обозначим ее R, отрицательна, то это означает, что анализируемое число В принадлежит интервалу ОА (не включая точку А), а следовательно, не входит в интервал А. При этом выдается сигнал недостоверности. В случае R 0 анализируется старшая и младшая части кода разности R. Число разрядов младшей части разности должно быть больше либо равно разрядности кода максимально возможного интервала Д.Если старшая часть разности Р отлична от нуля, то это означает, что число В не попадает в интервал Д.поскольку разность В-А в этом случае заведомо больше интервала А по абсолютной величине. В этом случае выдается сигнал недостоверности. В случае равенства нулю старшей части R производится вычитание кода величины интервала А из младшей части разности R. Если эта разность положительна, то В не попадает в интервал А и выдается сигнал недостоверности, если R- А 0, то В принадлежит интервалу Л т.е. при совпадении всех трех перечисленных условий на выходе сигнала недостоверности появляется сигнал логической единицы, означающий принадлежность анализируемого числа В интервалу А.

Схема работает следующим образом.

Старшие разряды кодов числа В 15 и зоны А 16 поступают на входы элемента 14 равнозначности, который выдает на третий вход 18 блока принятия решений результат сравнения этих разрядов. В случае равенства старших разрядов В и А на выходе элемента равнозначности появляется сигнал логической единицы, означающий, что первое условие анализа выполнено. Одновременно на выходы вычитателя 2 поступают разряды младших частей кодов числа 3 и зоны 4, после чего на выходах вычитателя появляется результат вычитания ВМл - Амл R. Старшая часть 11 этой разности и выходной перенос 12 из старшего разряда вычитателя поступают на входы первого элемента И 10, который в случае равенства нулю старшей части разности и наличия выходного переноса выдает на второй вход 13 блока принятия решений разрешающий сигнал логической единицы, означающий, что второе условие анализа выполнено. Одновременно вычитатель 6 кода величины интервала производит вычитание

кода величины интервала, поступающего по входу 7, из кода младшей части разности R 8. Появляющийся при этом перенос 9 из старшего разряда вычитателя кода величины интервала означает, что разность положительна и устанавливает на первом входе блока принятия решений разрешающий сигнал логической единицы. Таким образом, при выполнении всех трех условий на всех входах второго элемента И 19 появляются

сигналы логических единиц, приводящие к тому, что на выходе 20 сигнала недостоверности устройства также появляется сигнал логической единицы, означающий, что анализируемое число В находится в пределах

интервала Д,в противном случае число В не принадлежит интервалу А.

Две чередующиеся друг за другом ячейки вычитателя изображены на фиг. 3. Первая из них имеет инверсный входной и прямой

выходной переносы, вторая - прямой входной и инверсный выходной переносы. Это различие позволяет уменьшить задержку распространения переноса от одной ячейки к другой при использовании инвертирующей логики. Как видно из фиг. 3, обе ячейки представляют собой обычные ячейки сумматора, на входы которого первое число (уменьшаемое В) подается напрямую, а второй (вычитаемое А) - через инвертор, т.е.

инвертированным. В результате этого, манипулируя входным переносом Со, можно осуществитьдве операции - либо В-А, либо В-А-1. При Ср - 0 выполняется первая операция, при Со 1 - вторая. Аналогично с

помощью вычитателя 6 кода величины интервала можно организовать выполнение двух операций - это R-AnR-A-1. Это позволяет расширить функциональные возможности устройства, а отсутствие элементов памяти, счетчиков, линии синхросигнала } позволяет сократить аппаратные затраты. Формула изобретения Устройство для выделения числа в заданном интервале, содержащее блок анализа младших разрядов числа, блок принятия решений, элемент равнозначности, входы первой и второй групп которого являются соответственно входами старших разрядов числа и старших разрядов кода зоны устройства, входы младших разрядов числа устройства соединены с первой группой входов блока анализа младших разрядов числа, первый и второй выходы которого соединены с входами блока принятия решений, выход которого является выходом сигнала недостоверности устройства, отличающееся тем, что, с целью увеличения быстродействия и расширения области применения за счет обеспечения динамического изменения величины интервала, блок анализа младших разрядов содержит два вычи- тателя и элемент И, блок принятия решений содержит элемент И, входы первой и второй групп первого вычитателя являются входами первой и второй групп блока анализа младших разрядов, вторая группа входов которого является входами кода зоны устройства, вход переноса первого вычитателя соединен с входом переноса блока анализа младших разрядов и является входом входного переноса устройства, входы первой и второй групп второго вычитателя соединены соответственно с выходами младших разрядов результата вычитателя и входами кода величины интервала блока анализа младших разрядов, входы кода величины

интервала блока анализа младших разрядов являются входами кода величины интервала устройства, выходы старших разрядов и выход выходного переноса первого вычитателя соединены с входами элемента И, выход

которого является первым выходом блока анализа младших разрядов, второй выход которого соединен с выходом выходного переноса второго вычитателя, выход элемента равнозначности соединен с третьим входом

блока принятия решений, первый, второй и третий входы которого являются входами элемента И, выход которого является выходом блока принятия решений.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный сумматор | 2016 |

|

RU2635247C1 |

| Устройство для определения знака разности фаз | 1984 |

|

SU1265642A1 |

| Параллельный сумматор-вычитатель на нейроподобных элементах | 2023 |

|

RU2805774C1 |

| Устройство для выделения числа в заданном интервале | 1986 |

|

SU1383332A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Сумматор-вычислитель на элементах нейронной логики | 2019 |

|

RU2715177C1 |

| Многоканальный преобразователь разности частот в код | 1975 |

|

SU590849A1 |

| Одноразрядный четверичный сумматор-вычитатель | 1984 |

|

SU1229756A1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| Сигнализатор совпадения фаз | 1987 |

|

SU1515120A1 |

Изобретение относится к вычислительной технике и может быть использовано при обработке цифровой информации, в частности, при построении конвейерной системы выборки команд для процессора. Цель изобретения - расширение области применения и увеличение быстродействия - достигается за счет обеспечения возможности динамического изменения величины интервала. Устройство содержит блок анализа младших разрядов 1, вычитатель 2, элемент равнозначности 14, и блок принятия решений 17, выполненный на элементе И 19. Блок анализа младших разрядов содержит вычитатели 2 и 6 и элемент И 10. Вычитатель 6 анализирует уже полученные младшие разряды результата. Кроме того, применение вычитателя 6 позволяет осуществить возможность гибкого изменения кода величины интервала и обеспечить возможность работы как с обычным значением кода зоны, так и со значением кода зоны, увеличенным на единицу. 3 ил.

О

Фиг. 2

20

А

&

В

| Устройство для выделения числового интервала | 1980 |

|

SU955028A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для выделения числа в заданном интервале | 1986 |

|

SU1383332A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1991-08-30—Публикация

1989-08-04—Подача