1

(21)4343441/24-21

(22)14.12о87

(46) 15,10.89, Бюл, № 38

(72) В.Н.Вавилов, Е.СоВальшонок

и АоСоСигалов

(53)621.317о373(088,8)

(56)Авторское свидетельство СССР № 602880, кл„ G 01 R 25/00, 1979,

Авторское свидетельство СССР W 1195253, кл. G 01 R 25/00, 1985,

(54)СИПШгаЗАТОР СОВПАДЕНИЯ ФАЗ

(57)Изобретение относится к измерительной технике и может быть использовано в фазометрах и устройствах, где требуется совмещение электрического и механического нулей датчиков фазовращательного типа. Цель изобретения - расширение области применения - достигается путем обеспечении сигнализации совпадения фазы измеряемого напряжения с произвольно заданной фазой опорного напряжения при одновременном исключении необходимости настройки устройства в процессе перехода к измеряемым сигналам другого уровня. Сигнализатор совпадения фаз содержит компараторы 1 и 2, формирователь 3 импульсов, блок 4 D,-триггеров, блоки 5 и 7 индикаторов, кодовый наборный блок 6, генератор 8 импульсов, счетчик 9, сут матор- вычитатель 10, постоянный запоминающий блок 1I, При эксплуатации устройства не требуется осуществлять настройку пороговых уровней грубой и точной зон. 3 ил.

Ju3ff

i

(Л

ел сд to

3151

Изобретение относится к измерительной технике и может быть использовано в фазометрах и устройствах, где требуется совмещение электричес- кого и механического нулей датчиков фазовращательного типа

Целью изобретения является расти- рение области применения путем обеспечения сигнализации совпадения фа- зы измеряемого напр жения с произволно заданной фазой опорного напряжени с одновременным исключением необходимости настройки устройства при переходе к измеряемым сигналам другого уровня.

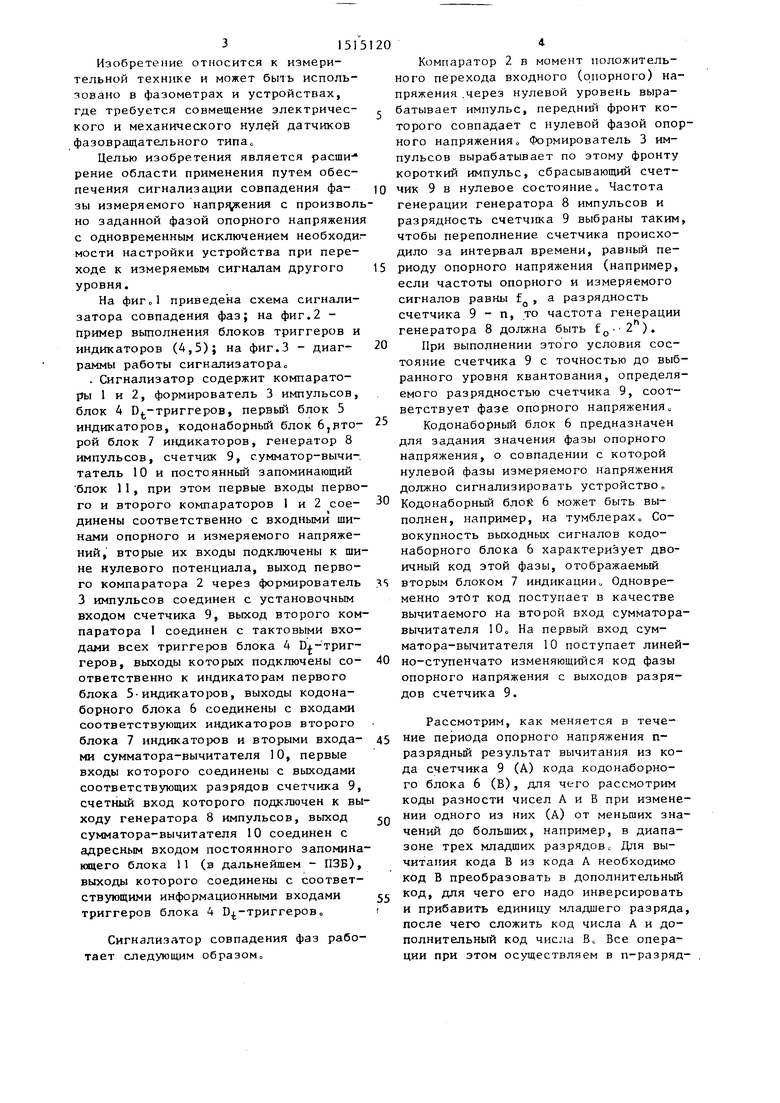

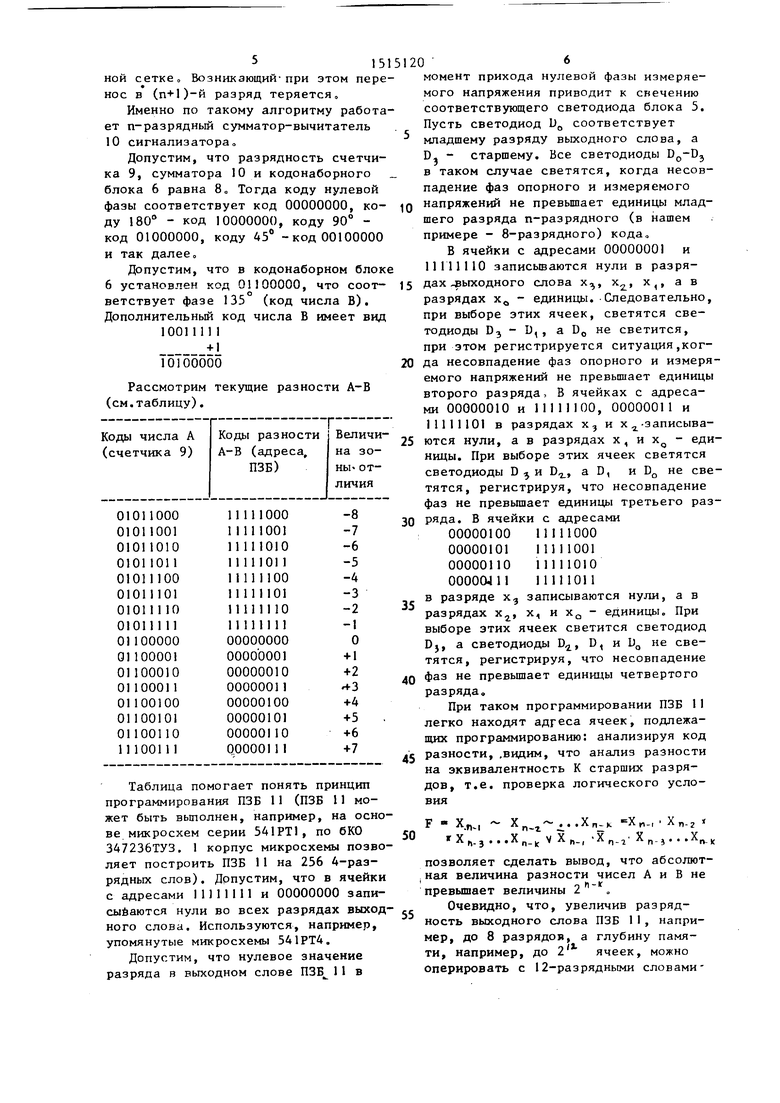

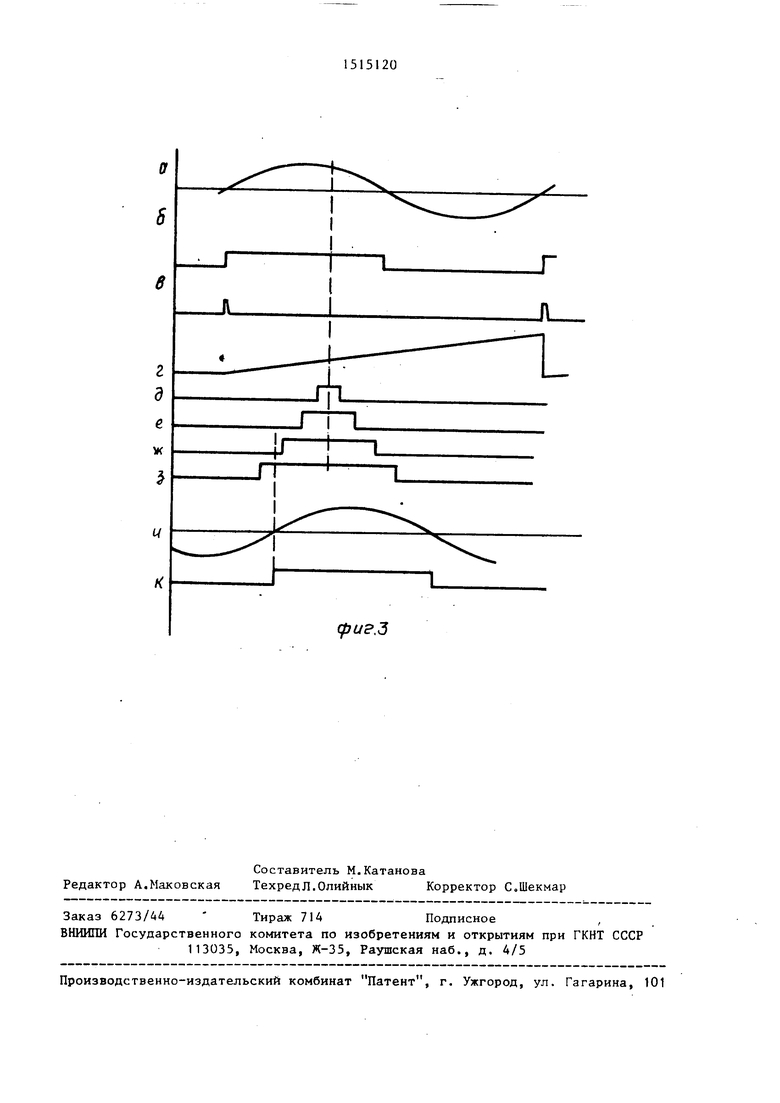

На фиг о 1 приведена схема сигнализатора совпадения фаз; на фиг.2 - пример вьтолнения блоков триггеров и индикаторов (4,5); на фиг.З - диаг- раммы работы сигнализаторао

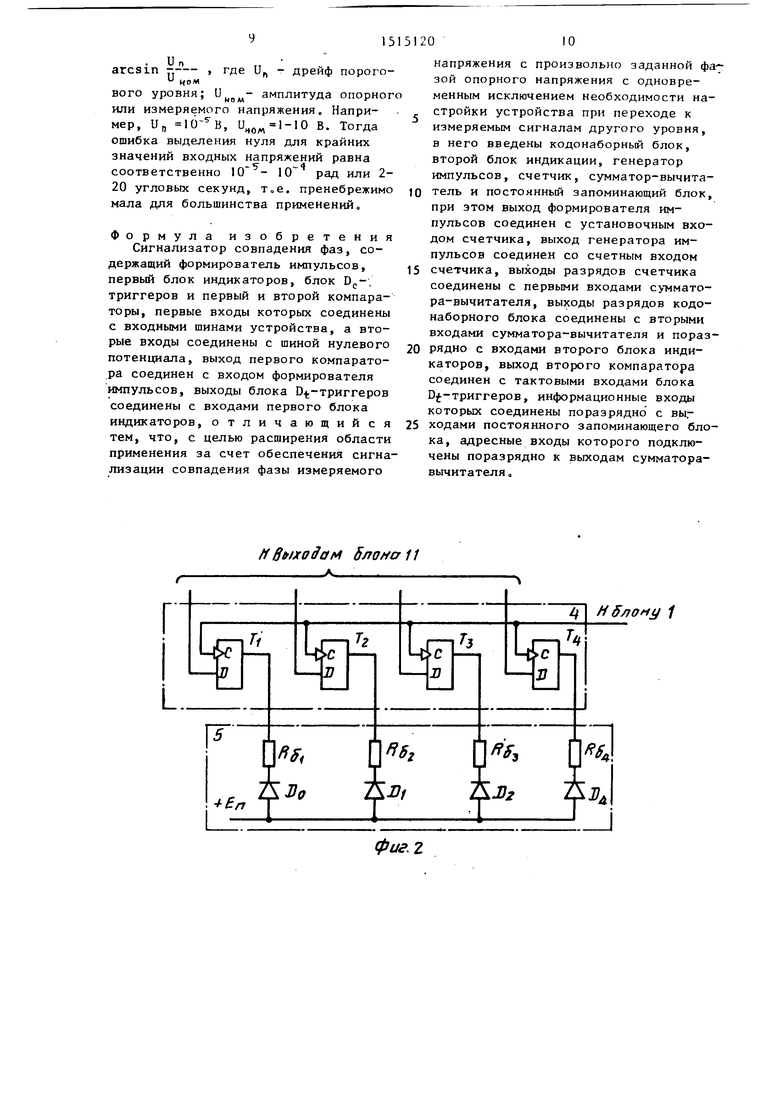

. Сигнализатор содержит компараторы 1 и 2, формирователь 3 импульсов, блок 4 D -триггеров, первый блок 5 индикаторов, кодонаборньш блок 6,вто- рой блок 7 индикаторов, генератор 8 импульсов, счетчик 9, сумматор-вычи- татель 10 и постоянный запоминающий блок 11, при этом первые входы первого и второго компараторов 1 и 2 сое- динены соответственно с входными щи- нами опорного и измеряемого напряжений, вторые их входы подключены к шине нулевого потенциала, выход первого компаратора 2 через формирователь 3 импульсов соединен с установочным входом счетчика 9, выход второго компаратора 1 соединен с тактовыми входами всех триггеров блока 4 D - триг- геров, выходы которых подключены со- ответственно к индикаторам первого блока 5-индикаторов, выходы кодона- борного блока 6 соединены с входами соответствующих индикаторов второго блока 7 индикаторов и вторыми входа- ми сумматора-вычитателя 10, первые входы которого соединены с выходами соответствующих разрядов счетчика 9, счетный вход которого подключен к выходу генератора 8 импульсов, выход сумматора-вычитателя 10 соединен с адресным входом постоянного запоминающего блока 11 (в дальнейшем - ПЗБ), выходы которого соединены с соответствующими информационными входами триггеров блока 4 D -триггероВо

Сигнализатор совпадения фаз работает следующем образомо

Компаратор 2 в момент положительного перехода входного (опорного) напряжения .через нулевой уровень вырабатывает импульс, переднш 1 фронт которого совпадает с нулевой фазой опоного напряжения. Формирователь 3 импульсов вырабатьшает по этому фронту короткий импульс, сбрасывающий счетчик 9 в нулевое состояние„ Частота генерации генератора 8 импульсов и разрядность счетчика 9 выбраны таким чтобы переполнение счетчика происходило за интервал времени, равный периоду опорного напряжения (например, если частоты опорного и измеряемого сигналов равны f, а разрядность счетчика 9 - п, то частота генерации генератора 8 должна быть ).

При выполнении этого условия состояние счетчика 9 с точностью до выбранного уровня квантования, определяемого разрядностью счетчика 9, соответствует фазе опорного напряжения.

Кодонаборньш блок 6 предназначен для задания значения фазы опорного напряжения, о совпадении с кото.рой нулевой фазы измеряемого напряжения должно сигнализировать устройство, Кодонаборньш блок 6 может быть выполнен, например, на тумблерах„ Совокупность выходных сигналов кодо- наборного блока 6 характеризует двоичный код этой фазы, отображаемый вторым блоком 7 индикации„ Одновременно этОт код поступает в качестве вычитаемого на второй вход сумматора вычитателя 10 На первый вход сумматора-вычитателя 10 поступает линейно-ступенчато изменяющийся код фазы опорного напряжения с выходов разрядов счетчика 9.

Рассмотрим, как меняется в течение периода опорного напряжения п- разрядный результат вычитания из кода счетчика 9 (А) кода кодонаборно- го блока 6 (в), для чего рассмотрим коды разности чисел А и В при изменении одного из них (А) от меньших значений до больших, например, в диапазоне трех младших разрядов с Для вычитания кода В из кода А необходимо код В преобразовать в дополнительный код, для чего его надо инверсировать и прибавить единицу младшего разряда после чего сложить код числа А и дополнительный код числа Во Все операции при этом осуществляем в п-разряд5151

ной сетке Возникающий-при этом перенос в (п+1)-й разряд теряется.

Именно по такому алгоритму работает п-разрядный сумматор-вычитатель 10 сигнализатора

Допустим, что разрядность счетчика 9, сумматора 10 и кодонаборного блока 6 равна 8„ Тогда коду нулевой фазы соответствует код 00000000, коду 180° - код 10000000, коду 90° - код 01000000, коду 45 -код 00100000 и так далее

Допустим, что в кодонаборном блоке 6 установлен код 01100000, что соответствует фазе 135 (код числа В). Дополнительньш код числа В имеет вид 10011111 +1

Toiooooo

Рассмотрим текущие разности А-В (см.таблицу).

Таблица помогает понять принцип программирования ПЗБ 11 (ПЗБ 11 может быть выполнен, например, на основе микросхем серии 541РТ1, по бКО 347236ТУЗ. 1 корпус микросхемы позволяет построить ПЗБ 11 на 256 4-разрядных слов). Дрпустим, что в ячейки с адресами 11111111 и 00000000 запи- сыбаются нули во всех разрядах выходного слова. Используются, например, упомянутые микросхемы 541РТ4.

Допустим, что нулевое значение разряда в выходном слове в

0

5

120 6

момент прихода нулевой фазы измеряемого напряжения приводит к свечению соответствующего светодиода блока 5. Пусть светодиод D соответствует младшему разряду выходного слова, а D- - старшему. Все светодиоды Dp-D, в таком случае светятся, когда несовпадение фаз опорного и измеряемого напряжений не превышает единицы младшего разряда п-разрядного (в нашем примере - 8-разрядного) кода

В ячейки с адресами 00000001 и 11111110 записьтаются нули в разря5 дах выходного слова х, х, х,, а в разрядах х - единицы.-Следовательно, при выборе этих ячеек, светятся светодиоды БЗ - D,, а DO не светится, при этом регистрируется ситуация,ког0 да несовпадение фаз опорного и измеряемого напряжений не превьш1ает единицы второго разряда, В ячейках с адресами 00000010 и 11111100, 00000011 и 111 11 101 в разрядах х и х -записыва5 ются нули, а в разрядах х, и х, - единицы. При выборе этих ячеек светятся светодиоды D и D, а D, и D не светятся, регистрируя, что несовпадение фаз не превьппает единицы третьего раз0 ряда. В ячейки с адресами 00000100 11111000 11111001 11111010 11111011

, записываются нули, а в X, и XQ - единицы. При выборе этих ячеек светится светодиод DJ, а светодиоды D, D, и D не светятся, регистрируя, что несовпадение

0 фаз не превьш1ает единицы четвертого разряда.

При таком программировании ПЗБ 11 легко находят адреса ячеек, подлежащих программированию: анализируя код

с разности, .видим, что анализ разности на эквивалентность К старших разрядов, т.е. проверка логического условия

F Хп., - Х„..Хп.к Х„., . Х„.г Х.З...Х„ vX,,., Х, Х„,...Х

позволяет сделать вывод, что абсолют- j ная величина разности чисел А и В не превышает величины ,

Очевидно, что, увеличив разрядность выходного слова ПЗБ 1I, например, до В разрядов, а глубину памяти, например, до 2 ячеек, можно оперирювать с 12-разрядными словами

00000101 00000110 00000411 в разряде х, разрядах х.

715

А и В (в этом случае разрядность ко- донаборного блока 6, счетчика 9, сумматора-вычитателя 10 также должна быть равна 12).

Объем программируемой памяти при этом невелик: при п-адресном ПЗБ 11 программируется только ячеек (для 8-разрядного ПЗБ, как мы вид дели, из 256 ячеек программируется только 16 ячеек, т.е. для , , 16).

Иезапрограммированные ячейки содержат во всех разрядах логические единицы, и при их выборе кодом разности А-В на выходах ПЗБ 11 формируется код, не приводящий к свечению светодиодов.

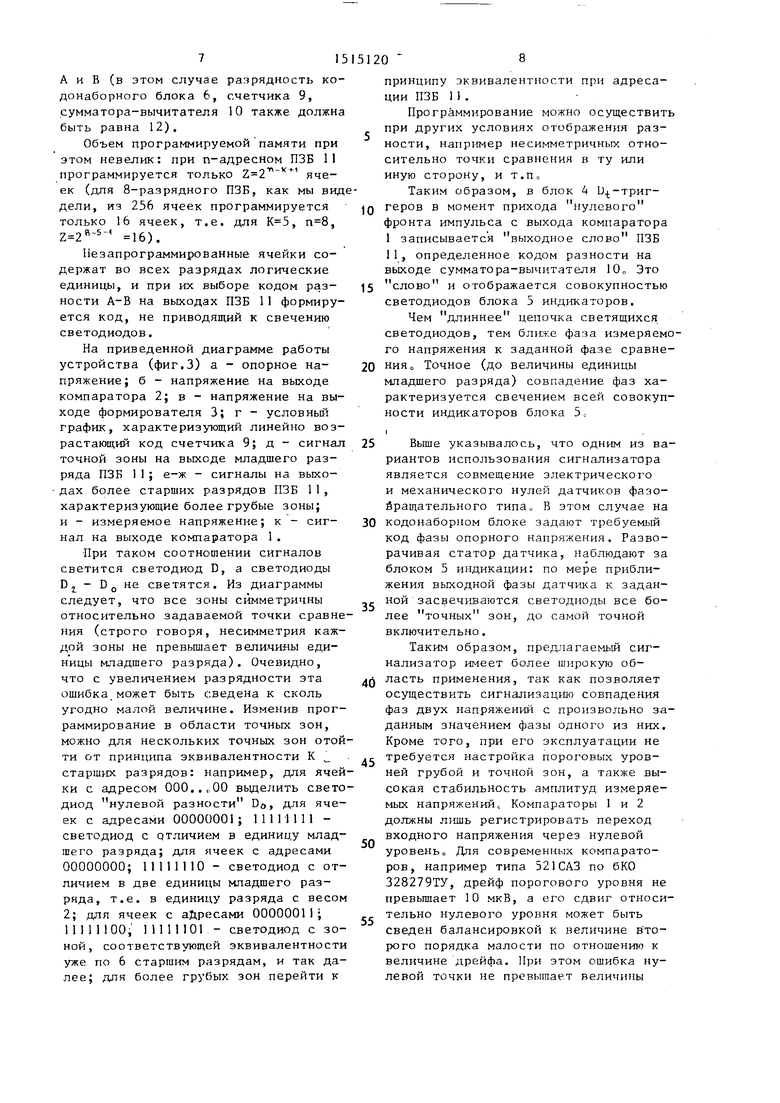

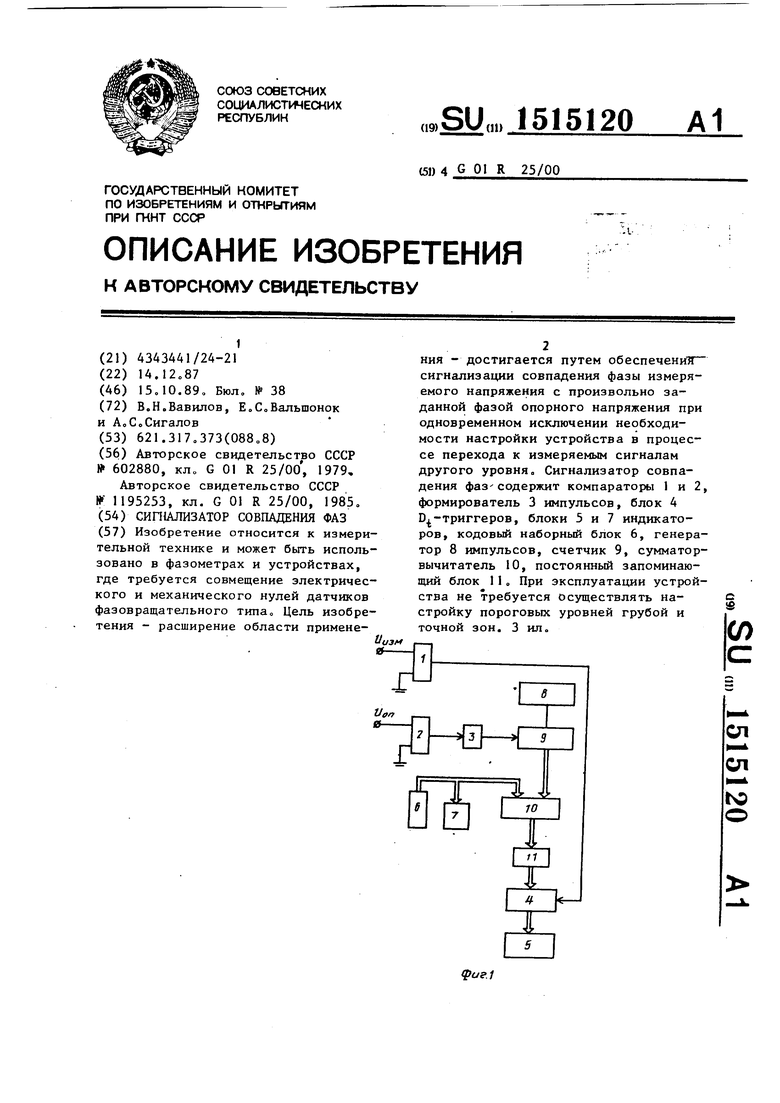

На приведенной диаграмме работы устройства (фиг.З) а - опорное напряжение; б - напряжение на выходе компаратора 2; в - напряжение на выходе формирователя 3; г - условньш график, характеризующий линейно возрастающий код счетчика 9; д - сигнал точной зоны на выходе младшего разряда ПЗБ 11; е-ж - сигналы на выходах более старших разрядов ПЗБ 11, характеризующие более грубые зоны; и - измеряемое напряжение; к - сигнал на выходе компаратора 1.

При таком соотношении сигналов светится светодиод D, а светодиоды D 2 - D Q не светятся. Из диаграммы следует, что все зоны симметричны относительно задаваемой точки сравнения (строго говоря, несимметрия каждой зоны не превышает величины единицы младшего разряда). Очевидно, что с увеличением разрядности эта ошибка может быть сведена к сколь угодно малой величине. Изменив программирование в области точных зон, можно для нескольких точных зон отойти от принципа эквивалентности К старших разрядов: например, для ячейки с адресом 000..„00 вьзделить светодиод нулевой разности DO, для ячеек с адресами 00000001; 11111111 - светодиод с отличием в единицу младшего разряда; для ячеек с адресами 00000000; 11111110 - светодиод с отличием в две единицы младшего разряда, т.е. в единицу разряда с весом 2; для ячеек с адресами 0000001I 11111100, 11111101 - светодиод с зоной, соответствующей эквивалентности уже по 6 старш1-1м разрядам, и так далее; для более грубых зон перейти к

8

0

5

0

5

0

5

0

5

0

5

принципу эквивалентности при адресации ПЗБ П .

Программирование можно осуществить при других условиях отображения разности, например несимметричных относительно точки сравнения в ту или

иную сторону, и т.По

Таким образом, в блок 4 U -триг- геров в момент прихода нулевого фронта импульса с выхода компаратора 1 записывается выходное слово ПЗБ 11, определенное кодом разности на выходе сумматора-вычитателя 10„ Это слово и отображается совокупностью светодиодов блока 5 инд1-1каторов.

Чем длиннее цепочка светящихся светодиодов, тем бл1Ет;е фаза измеряемого напряжения к заданной фазе сравнения „ Точное (до величины единицы младшего разряда) совпадение фаз характеризуется свечением всей совокупности индикаторов блока 5с

I

Выше указывалось, что одним из вариантов 11спользования сигнализатора является совмещение электрического и механического нулей датчиков фазо- ёращательного типа, В этом случае на кодонаборном блоке задают требуем151Й код фазы опорного напряжения. Разворачивая статор датчика, наблюдают за блоком 5 индикации: по мере приближения выходной фазы датчика к заданной засвечиваются светодноды все более точных зон, до самой точной включительно.

Таким образом, предлагаемый сигнализатор имеет более широкую область применения, так как позволяет осуществить сигнализацию совпадения фаз двух напряжений с произвольно заданным значением фазы одного из них. Кроме того, при его эксплуатации не требуется настройка пороговых уровней грубой и точной зон, а также высокая стабильность амплитуд измеряемых напряжений с Компараторы 1 и 2 должны лишь регистрировать переход входного напряжения через нулевой уровень Для современных компараторов, например типа 521 САЗ по бКО 328279ТУ, дрейф порогового уровня не превьшает 10 мкВ, а его сдвиг относительно нулевого уровня может быть сведен балансировкой к величине в то- рого порядка малости по отношению к величине дрейфа. При этом ошибка нулевой точки не превышает величины

и

arcs in f-- , где U - дрейф порого MOM

вого уровня; амплитуда опорног или измеряемого напряжения. Например, и„ , В. Тогда ошибка выделения нуля для крайних значений входных напряжений равна соответственно Ю рад или 2- 20 угловых секунд, т.е. пренебрежимо мала для большинства применений,

Формула изобретения

Сигнализатор совпадения фаз, содержащий формирователь импульсов, первый блок индикаторов, блок триггеров и первый и второй компараторы, первые входы которых соединены с входными шинами устройства, а вторые входы соединены с шиной нулевого потенциала, выход первого компарато- ,ра соединен с входом формирователя импульсов, выходы блока D -триггеров соединены с входами первого блока индикаторов, отличающийся тем, что, с целью расширения области применения за счет обеспечения сигнализации совпадения фазы измеряемого

напряжения с произвольно заданной зой опорного напряжения с одновременным исключением необходимости на- стройки устройства при переходе к измеряемым сигналам другого уровня, в него введены кодонаборный блок, второй блок индикации, генератор импульсов, счетчик, сумматор-вычитатель и постоянный запоминающий блок, при этом выход формирователя импульсов соединен с установочным входом счетчика, выход генератора импульсов соединен со счетным входом

счетчика, выходы разрядов счетчика соединены с первыми входами суммато- ра-вычитателя, выходы разрядов кодо- наборного блока соединены с вторыми входами сумматора-вычитателя и поразрядно с входами второго блока индикаторов, выход второго компаратора соединен с тактовыми входами блока D -триггеров, информационные входы которых соединены поразрядно с вы.ходами постоянного запоминающего блока, адресные входы которого подключены поразрядно к выходам сумматора- вычитателя о

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнализатор совпадения фаз | 1990 |

|

SU1824595A1 |

| Способ цифрового управления многофазным инвертором | 1989 |

|

SU1683154A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Устройство для контроля экспоненциальных процессов | 1990 |

|

SU1732331A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Регулируемая мера фазовых сдвигов | 1985 |

|

SU1347034A1 |

| Устройство для определения знака разности фаз | 1984 |

|

SU1265642A1 |

| Устройство для определения фазовой ошибки | 1985 |

|

SU1397848A1 |

| ЦИФРОВОЙ СЧЕТЧИК ЭЛЕКТРОЭНЕРГИИ КСР-ТИПА | 1991 |

|

RU2061243C1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

Изобретение относится к измерительной технике и может быть использовано в фазометрах и устройствах, где требуется совмещение электрического и механического нулей датчиков фазовращательного типа. Цель изобретения - расширение области применения - достигается путем обеспечения сигнализации совпадения фазы измеряемого напряжения с произвольно заданной фазой опорного напряжения при одновременном исключении необходимости настройки устройства в процессе перехода к измеряемым сигналам другого уровня. Сигнализатор совпадения фаз содержит компараторы 1 и 2, формирователь 3 импульсов, блок 4 DT- триггеров, блоки 5 и 7 индикаторов, кодовый наборный блок 6, генератор 8 импульсов, счетчик 9, сумматор-вычитатель 10, постоянный запоминающий блок 11. При эксплуатации устройства не требуется осуществлять настройку пороговых уровней грубой и точной зон. 3 ил.

ff Выхода 1 5лона 11

А,

Н 5лону 1

фиг. 2

О

J г

(f3U.3

Г п

Авторы

Даты

1989-10-15—Публикация

1987-12-14—Подача