Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих устройств обработки цифровой информации.

Цель изобретения - упрощение конструкции одноразрядного четверичного сумматора-вычитателя.

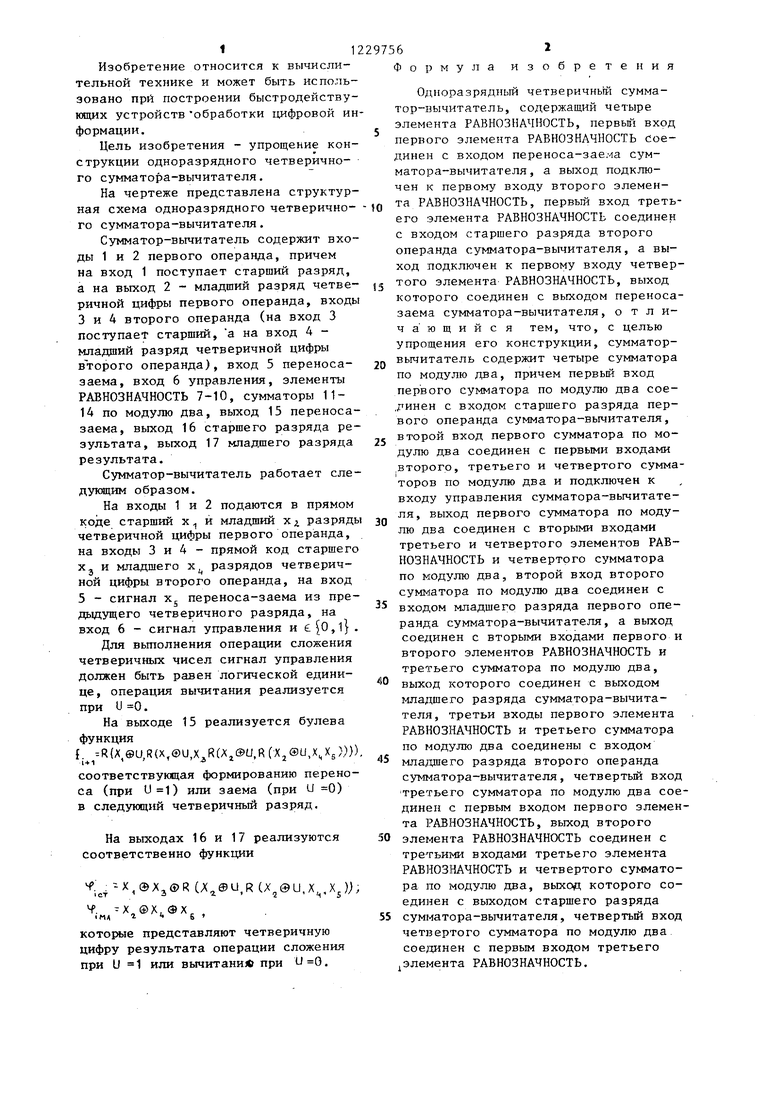

На чертеже представлена структурная схема одноразрядного четверично- го сумматора-вычитателя.

Сумматор-вычитатель содержит входы 1 и 2 первого операнда, причем на вход 1 поступает старший разряд, а на выход 2 - младший разряд четверичной цифры первого операнда, входы 3 и 4 второго операнда (на вход 3 поступает старщий, а на вход 4 - младший разряд четверичной цифры второго операнда), вход 5 переноса- заема, вход 6 управления, элементы РАВНОЗНАЧНОСТЬ 7-10, сумматоры 11- 14 по модулю два, выход 15 переноса- заема, выход 16 старшего разряда результата, выход 17 младшего разряда результата.

Сумматор-вычитатель работает сле- дукщим образом.

На входы 1 и 2 подаются в прямом коде старший х и младший Хд разряды четверичной цифры первого операнда, на входы 3 и 4 - прямой код старшего Xj и младшего х разрядов четверичной цифры второго операнда, на вход 5 - сигнал Xj переноса-заема из предыдущего четверичного разряда, на вход 6 - сигнал управления и е 0,1}.

Для вьшолнения операции сложения четверичных чисел сигнал управления должен быть равен логической единице , операция вычитания реализуется при и 0.

На выходе 15 реализуется булева функция {.R{A,®U,R(X,®U,XjjR(Xj®U,RCx.j®U, ),)))

соответствующая формированию переноса (при ) или заема (при U 0) в следующий четверичный разряд.

На выходах 16 и 17 реализуются соответственно функции

,сГ- ® з®«Сл фи,,х,,х)),

.,,,

которые представляют четверичную цифру результата операции сложения при и 1 или вычитанил при .

0

5

Формула изобретения

Одно)разрядный четверичньгй сумма- тор-БЫчитатель, содержащий четыре элемента РАВНОЗНАЧНОСТЬ, первый вход первого элемента РАВНОЗНАЧНОСТЬ соединен с входом переноса-заема сумматора-вычитателя, а выход подключен к первому входу второго элемен, та РАВНОЗНАЧНОСТЬ, первый вход третьего элемента РАВНОЗНАЧНОСТЬ соединен с входом старшего разряда второго операнда сумматора-вычитателя, а выход подключен к первому входу четвертого элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с выходом переноса- заема сумматора-вычитателя, о т л и- ч а ю щ и и с я тем, что, с целью упрощения его конструкции, сумматор- вычитатель содержит четыре сумматора по модулю два, причем первый вход первого сумматора по модулю два сое- .динен с входом старшего разряда первого операнда сумматора-вычитателя, второй вход первого сумматора по модулю два соединен с первыми входами .второго, третьего и четвертого сумматоров по модулю два и подключен к входу управления сумматора-вычитателя, выход первого сумматора по модулю два соединен с вторыми входами третьего и четвертого элементов РАВНОЗНАЧНОСТЬ и четвертого сумматора по модулю два, второй вход второго сум :1атора по модулю два соединен с входом младшего разряда первого операнда сумматора-вычитателя, а выход соединен с вторыми входами первого и второго элементов РАВНОЗНАЧНОСТЬ и третьего сумматора по модулю два, выход которого соединен с выходом младшего разряда сумматора-вычитателя, третьи входы первого элемента РАВНОЗНАЧНОСТЬ и третьего сумматора по модулю два соединены с входом младшего разряда второго операнда сумматора-вычитателя, четвертьй вход третьего сумматора по модулю два соединен с первым входом первого элемента РАВНОЗНАЧНОСТЬ, выход второго

0 элемента РАВНОЗНАЧНОСТЬ соединен с третьими входами третьего элемента РАВНОЗНАЧНОСТЬ и четвертого сумматора по модулю два, выход которого соединен с выходом старшего разряда

5 сумматора-вычитателя, четвертый вход четвертого сумматора по модулю два coefytHBH с первым входом третьего элемента РАВНОЗНАЧНОСТЬ.

0

5

0

5

Редактор М.Бланар

Составитель А.Степанов

Техред Г.Гербер Корректор Е.Рошко

Заказ 2451/49 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный четверичный сумматор | 1983 |

|

SU1160400A1 |

| Четверичный сумматор | 1983 |

|

SU1124290A1 |

| Одноразрядный четверичный сумматор | 1981 |

|

SU1023322A1 |

| Одноразрядный адаптируемый четверичный сумматор | 1981 |

|

SU1053102A1 |

| Одноразрядный сумматор-вычитатель | 1986 |

|

SU1368875A1 |

| Устройство для вычитания десятичных чисел | 1975 |

|

SU607216A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Одноразрядный десятичный сумматор- ВычиТАТЕль | 1977 |

|

SU807275A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ СЕМИ ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2018930C1 |

Изобретение относится к вычислительной технике и предназначено для построения быстродействующих устройств обработки цифровой информации. Цель изобретения - упрощение конструкции. Поставленная цель достигается тем, что сумматор-вычитатель содержит четыре элемента РАВНОЗНАЧНОСТЬ, четьфе сумматора по модулю два, два входа первого операнда, два входа второго операнда, вход перено- са/заема, вход управления, два выхода результата и выход переноса/заема. Оба операнда поступают в прямом коде, результат также формируется в прямом коде. 1 ил.

| Одноразрядный четверичный сумматор | 1981 |

|

SU1023322A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1136376, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-07—Публикация

1984-05-23—Подача