Изобретение относится к автоматике и вычислительной технике и может быть использовано при формировании тестов для контроля вычислительных средств.

Цель изобретения - расширение перечня имитируемых неисправностей.

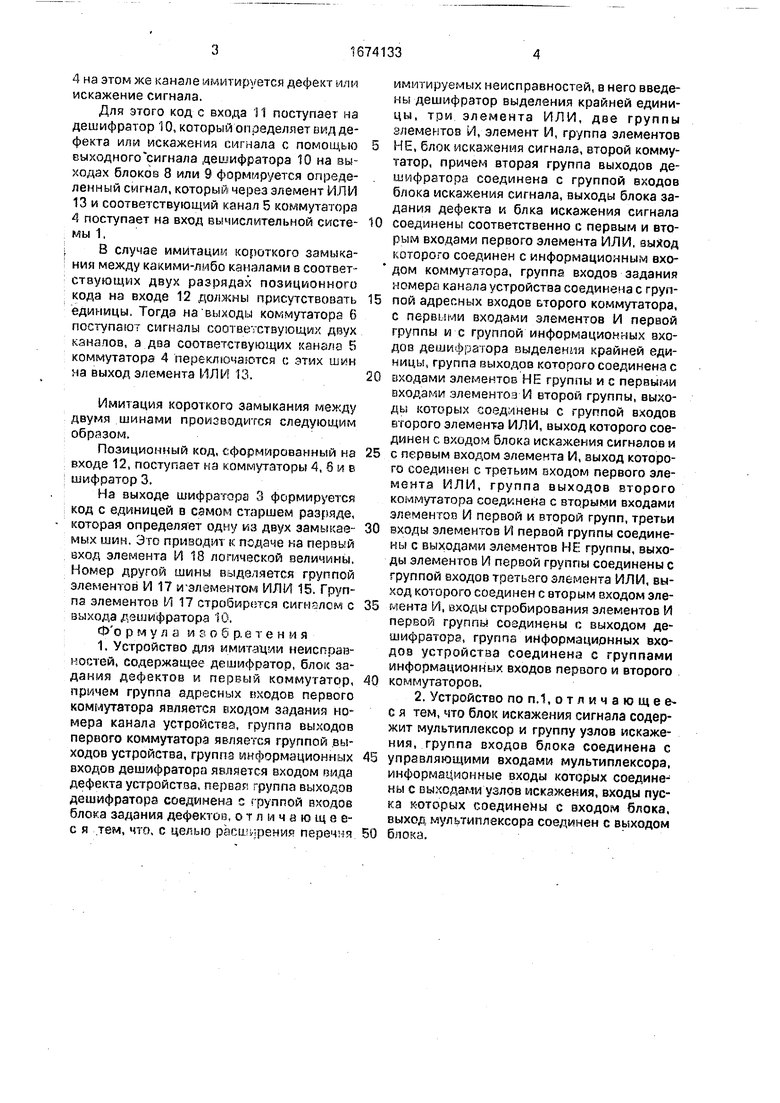

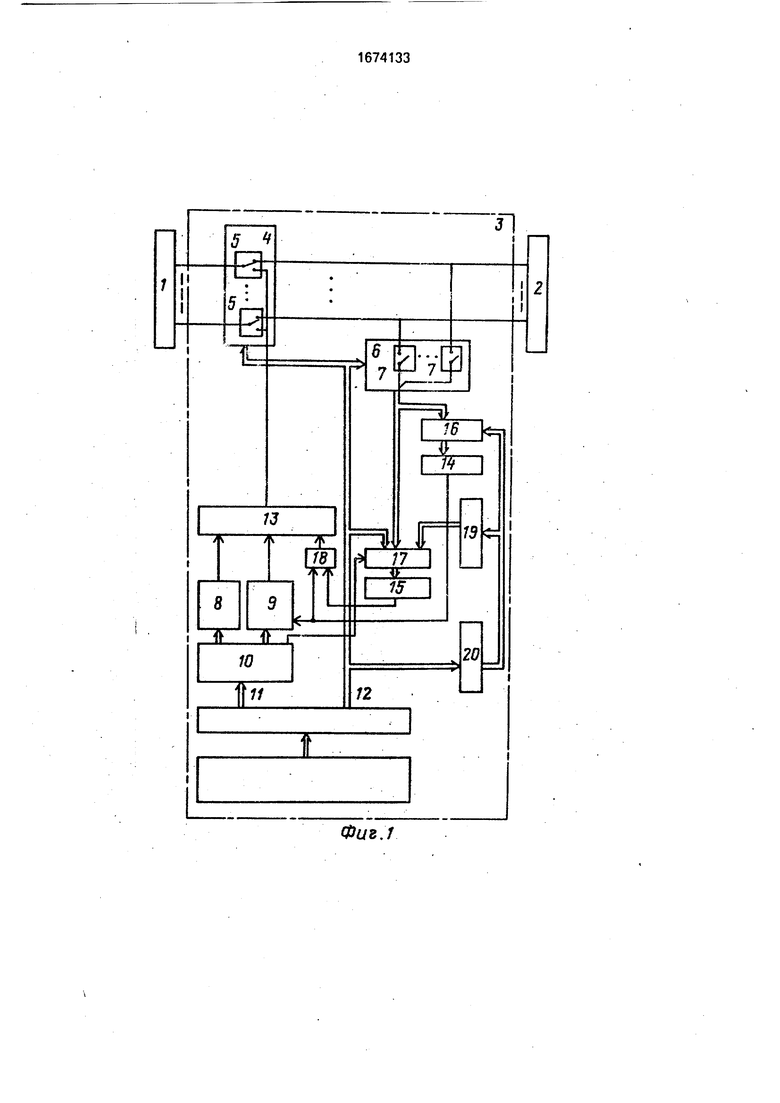

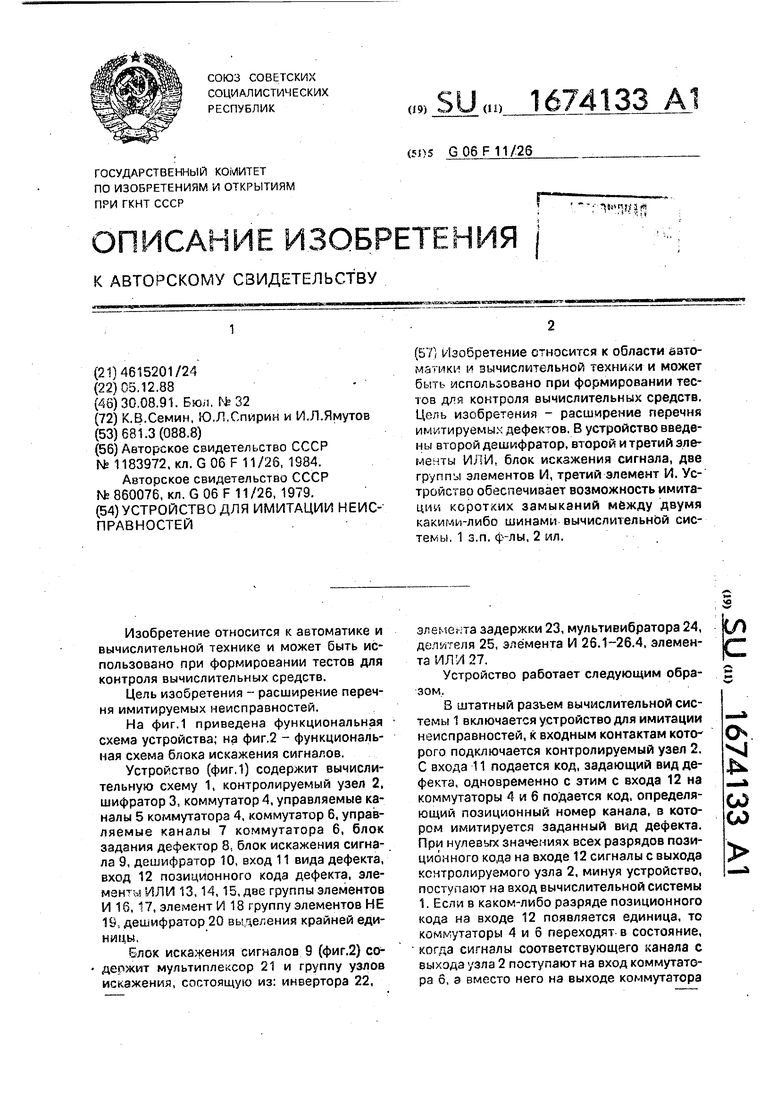

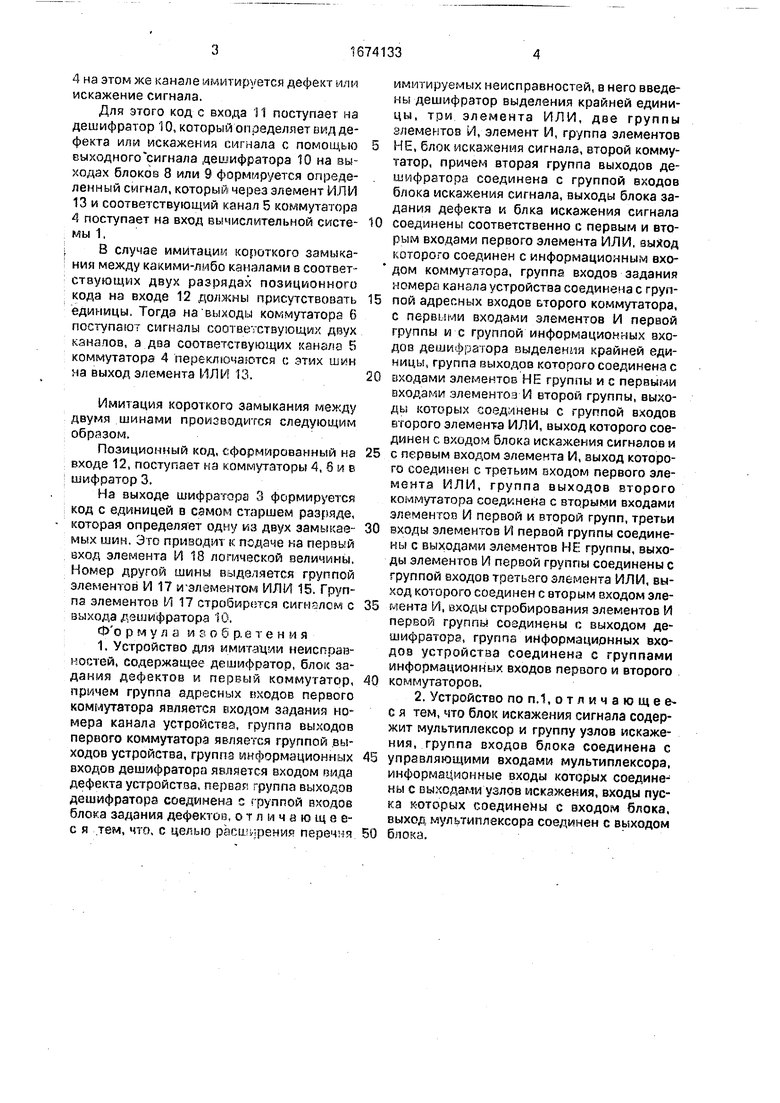

На фиг.1 приведена функциональная схема устройства; на фиг.2 - функциональная схема блока искажения сигналов.

Устройство (фиг.1) содержит вычислительную схему 1, контролируемый узел 2, шифратор 3, коммутатор 4, управляемые каналы 5 коммутатора 4, коммутатор 6, управляемые каналы 7 коммутатора 6, блок задания дефекгор 8 блок искажения сигнала 9, дешифратор 10. вход 11 вида дефекта, вход 12 позиционного кода дефекта, эле- мэн j ИЛИ 13, 14, 15, две группы элементов И 16, 7, элемент И 18 i руппу элементов Н Е 10 дешифратор 20 аь1 деления крайней единицы

Елок искажения сигналов 9 (фиг.2) СО- мультиплексор 21 и группу узлов искажения, состоящую из: инвертора 22,

эгемй та задержки 23, мультивибратора 24, детителя 25, элемента И 26.1-26.4, элемента И ЛИ 27.

Устройство работает следующим образом.

В штатный разъем вычислительной системы 1 включается устройство для имитации неисправностей, к входным контактам которого подключается контролируемый узел 2. С входа 11 подается код. задающий вид дефекта, одновременно с этим с входа 12 на коммутаторы 4 и 6 подается код, определяющий позиционный номер канала, в котором имитируется заданный вид дефекта. При нулевых значениях всех разрядов позиционного кода на входе 12 сигналы с выхода контролируемого узла 2, минуя устройство, поступают на вход вычислительной системы 1. Если в каком-либо разряде позиционного кода на входе 12 появляется единица, то коммутаторы 4 и 6 переходят в состояние, когда сигналы соответствующего канала с выхода узла 2 поступают на вход коммутатора 6, а вместо него на выходе коммутатора

fe

О

VI

00 СО

4 на этом же канале имитируется дефект или искажение сигнала.

Для этого код с входа 11 поступает на дешифратор 10, который определяет вид дефекта или искажения сигнала с помощью выходного сигнала дешифратора 10 на выходах блоков 8 или 9 формируется определенный сигнал, который через элемент ИЛИ 13 и соответствующий канал 5 коммутатора 4 поступает на вход вычислительной системы 1.

В случае имитации короткого замыкания между какими-либо каналами в соответствующих двух разрядах позиционного кода на входе 12 должны присутствовать единицы. Тогда на выходы коммутатора 6 поступают сигналы соответствующих двух каналов, а два соответствующих канала 5 коммутатора 4 переключаются с этих шин на выход элемента ИЛИ 13.

Имитация короткого замыкания между двумя шинами производится следующим образом.

Позиционный код, сформированный на входе 12, поступает на коммутаторы 4, б и в шифратор 3.

На выходе шифратора 3 формируется код с единицей в самом старшем разряде, которая определяет одну из двух замыкаемых шин. Это приводит к подаче на первый вход элемента И 18 логической величины. Номер другой шины выделяется группой элементов И 17 и-элементом ИЛИ 15. Группа элементов И 17 стробирется сигнтлом с выхода дешифратора 10.

Ф о рмула изобретения

1. Устройство для имитации неисправностей, содержащее дешифратор, блок задания дефектов и первый коммутатор, причем группа адресных входов первого коммутатора является входом задания номера канала устройства, группа выходов первого коммутатора является группой выходов устройства, группа информационных входов дешифратора является входом вида дефекта устройства, первая группа выходов дешифратора соединена с группой входов блока задания дефектов, отличающее- с я тем, что, с целью расширения перечня

имитируемых неисправностей, в него введены дешифратор выделения крайней единицы, три элемента ИЛИ, две группы элементов И, элемент И, группа элементов

НЕ, блок искажения сигнала, второй коммутатор, причем вторая группа выходов дешифратора соединена с группой входов блока искажения сигнала, выходы блока задания дефекта и блка искажения сигнала

соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с информационным вхо- дом коммутатора, группа входов задания номера канала устройства соединена с грумпой адресных входов ьторого коммутатора, с первими входами элементов И первой группы и с группой информационных входов дешифратора выделения крайней единицы, группа выходов которого соединена с

входами элементов НЕ группы и с первыми входами элементов И второй группы, выходы которых соединены с группой входов второго элемента ИЛИ, выход которого соединен с входом блока искажения сигналов и

с первым входом элемента И, выход которого соединен с третьим пходом первого элемента ИЛИ, группа выходов второго коммутатора соединена с вторыми входами элементоп И первой и второй групп, третьи

входы элементов И первой группы соединены с выходами элементов НЕ группы, выходы элементов И первой группы соединены с группой входов третьаго элемента ИЛИ, выход которого соединен с вторым входом элемента И, входы стробирования элементов И первой группы соединены с выходом дешифратора, группа информационных входов устройства соединена с группами информационных входов первого и второго

коммутаторов.

2. Устройство по п.1, о т л и ч а ю щ е е- с я тем, что блок искажения сигнала содержит мультиплексор и группу узлов искажения, группа входов блока соединена с

управляющими входами мультиплексора, информационные входы которых соединены с выходами узлов искажения, входы пуска которых соединены с входом блока, выход мультиплексора соединен с выходом

0 блока.

Фиг.1

Л/Ш

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Устройство для сопряжения эвм с каналами связи | 1984 |

|

SU1229766A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1129599A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1985 |

|

SU1298762A2 |

| Устройство для имитации сбоев | 1985 |

|

SU1298925A2 |

| Устройство для отладки тестов | 1982 |

|

SU1084804A2 |

| Устройство для вывода информации на телеграфный аппарат | 1985 |

|

SU1293735A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при формировании тестов для контроля вычислительных средств. Цель изобретения - расширение перечня имитируемых дефектов. В устройство введены второй дешифратор, второй и третий элементы ИЛИ, блок искажения сигнала, две группы элементов И, третий элемент И. Устройство обеспечивает возможность имитации коротких замыканий между двумя какими-либо шинами вычислительной системы. 1 з.п. ф-лы, 2 ил.

Отю Фиг. 2.

ОтМ

| Устройство для имитации отказов дискретной аппаратуры | 1984 |

|

SU1183972A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отладки тестов | 1979 |

|

SU860076A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-08-30—Публикация

1988-12-05—Подача