1

Изобретение относится к вычислительной технике, в частности к устройствам, имитирующим сбои и отказы аппаратных средств вычислительных систем, и может быть использовано при отладке и контроле аппаратно-программных средств вычислительной системы, предназначенных обеспечивать защиту системы от сбо,ев и отказов.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения режима имитации сбоев.

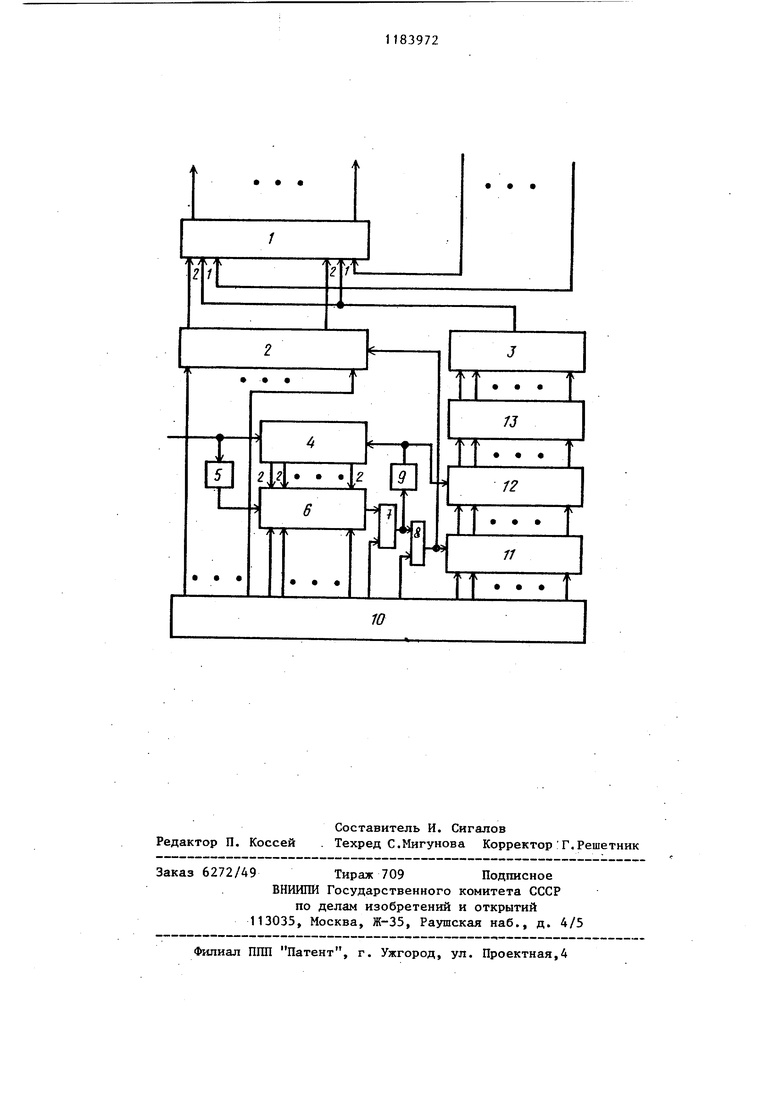

На чертеже приведена структурная схема предлагаемого устройства.

Устройство состоит из коммутатора 1, дешифратора 2 номера канала, формирователя 3 дефекта, счет чика 4 циклов, элемента НЕ 5, схемы 6 сравнения, элемента И 7, элемента ИЛИ 8, элемента 9 задержки, блока 10 задания режима имитации, блока 11 памяти, регистра 12, дешифратора 13 дефекта.

Устройство работает следующим образом.

Пользователь информационные входы и выходы устройства подключает к соответствующим выходам и входам дискретной аппаратуры, в которую необходимо внести дефект, а тактовый вход устройства соединяет с синхронизирующим выходом указанной дискретной аппаратуры.

Перед пуском контролируемой аппаратуры с блока 10 задания режима имитации заказывается номер канала, В котором необходимо имитировать дефект, режим имитации (отказ или сбой), адрес ячейки блока 11 памяти, в которой хранится в соответствующем масштабе тестовое воздействие и, в режиме имитаи;ии сбоя номер цикла работы аппаратуры, в течение которого требуется имитировать дефект. Перечисленные признаки хранятся в блоке 10 задания режима имитации в течение всего включения контролируемой аппаратуры.

Информация, содержащая номер коммутируемого канала, с группы выходов задания номера канала блока 10 задания режима имитации поступает на входы дешифратора 2 номера канала. Номер цикла работы, в ходе которого требуется имитировать сбой, задается с группы выходов

839722

номера цикла с блока 10 задания режима имитации и поступает на первые информационные входы схемы 6 сравнения, вторые информационные входы

5 которой связаны с информационными выходами счетчика 4 циклов, функционирование которого происходит при поступлении импуЛьсов на счетный вход счетчика 4 с тактового

О входа устройства, подключенного к соответствующему выходу контролируемой дискретной аппаратуры. Этими же импульсами, поступающими через элемент НЕ 5 на тактовый вход

15 схемы 6 сравнения, производится опрос схемы 6 сравнения. При равнозначности информации, поступающей на первые и вторые информационные входы схемы 6 сравнения, на

20 выходе последней формируется сигнал, поступающий на первый вход элемента И 7, второй вход которого является выходом сбоя блока 10 задания режима имитации. Сигнал,

25 формируемый на выходе элемента И 7, поступает на первый вход элемента ИЛИ 8 и через элемент 9 задержки - на входы обнуления счетчика 4 циклов и регистра 12. На второй вход

30 элемента ИЛИ 8 поступает сигнал о наличии режима имитации отказа с выхода блока 10, с адресных выходов которого информация поступает на адресные входы блока 11 памя35 ти, на вход обращения которого поступает сигнал, формируемьй на выходе элемента ИЛИ 8 и служащий для стробирования как блока 11 памяти, так и дешифратора 2 номера

40 канала, выходы которого подключены к управляющим входам коммутатора 1. Реформация с выходов блока 11 памяти через регистр 12 поступает на входы дешифратора 13

45 дефекта, в результате чего возбуждается один из выходов дешифратора 1 3 дефекта. Посредством сигнала, появляющегося на одном из выходов дешифратора 13 дефекта, являющихся

50 входами формирователя 3 дефекта, на выходе формирователя генерируется дефект заказанного пользовате лем вида,напримеробрыв,короткое замыкание, тактовая частота,одиночныйим55 пульс ит.д.Сгенерированный дефектпоступает на вторую группуинформационных входов коммутатора 1 и далее на заказанный выход устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации отказов дискретной аппаратуры | 1987 |

|

SU1451702A1 |

| Устройство для имитации отказов дискретной аппаратуры | 1990 |

|

SU1815642A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ И ВНУТРИСХЕМНОГО ТЕСТИРОВАНИЯ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АППАРАТУРЫ | 1995 |

|

RU2093885C1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Устройство для диагностирования периферийных устройств | 1990 |

|

SU1716518A1 |

| Устройство для отладки цифровых систем | 1985 |

|

SU1254492A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1695309A1 |

| Имитатор канала | 1987 |

|

SU1425675A2 |

УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ ДИСКРЕТНОЙ АППАРАТУРЫ, содержащее блок памяти, регистр, дешифратор дефекта, формирователь дефекта и коммутатор, причем выходы коммутатора образуют группу информационных выходов устройства, группа информационных входов устройства соединена с первой, группой информационных входов коммутатора, группа выходов формирователя дефекта соединена с второй группой информационных входов коммутатора, информационные выходы блока памяти соединены с информационными входами регистра, выходы которого соединены с входами дешифратора дефекта, выходы которого соединены с входами формирователя дефекта, отличающееся тем, что, с целью расширения его функциональных возможностей за счет обеспечения режима имитации сбоя, в него введены блок задания режима имитации, схема сравнения, элемент НЕ, элемент ИЛИ, элемент И, элемент задержки, счетчик циклов и дешифратор номера канала, причем группа выходов задания номера канала блока задания режима имитации соединена с грзшпой входов дешифратора номера канала, выходы которого соединены с управляющими входами коммутатора, группа выходов номера цикла блока задания режима имитации соединена с первой группой информационных входов схемы сравнения, выход которой соединен с первым входом элемента И, тактовый вход устройства соединен со счетным входом счетчика циклов и через элемент НЕ - с тактовым w входом схемы сравнения, группа информационных выходов счетчика циклов соединена с второй группой информационных входов схемы сравнения, выход сбоя блока задания режима имитации соединен с вторым входом элемента И, выход которого сх соединен с первым входом элемента ИЛИ и через элемент задержки оо с входами обнуления счетчика цикСР лов и регистра, выход отказа блока ч1 задания режима имитации соединен N9 с вторым входом элемента ИЛИ, выход которого соединен с входом обращения блока и стробирзтощим входом дешифратора номера канала, группа адресных выходов блока задания режима имитации соединена с группой адресных входов блока памяти.

| Устройство для тестового контроля цифровых узлов электронных вычислительных машин | 1976 |

|

SU694863A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отладки тестов | 1979 |

|

SU860076A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-10-07—Публикация

1984-01-06—Подача