Изобретение относится к вычислительной технике и предназначено для имитации неисправностей - отказов и сбоев различной продолжительности и

кратности процессоров, работающих в составе вычислительных машин (комплексов) в реальном масштабе времени, и может быть использовано для экспе

риментального исследования надежности отказоустойчивых вычислительных систем.

Цель изобретения - расширение области применения за счет имитации отказов и сбоев активных узлов.

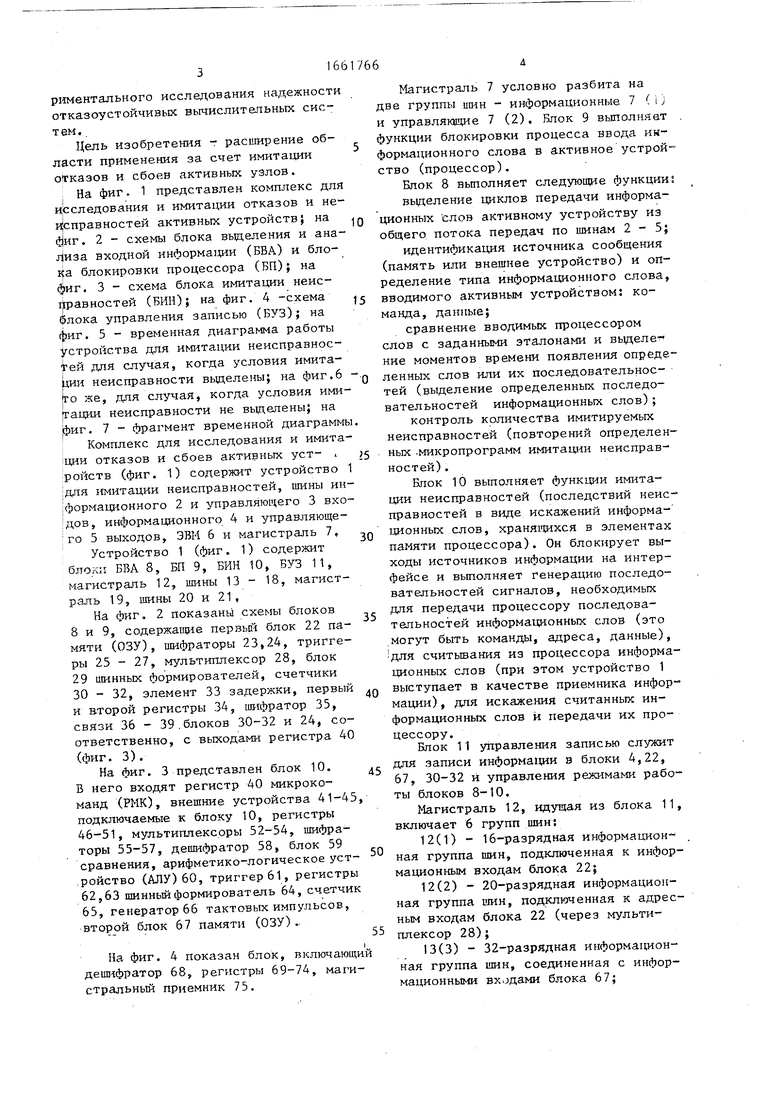

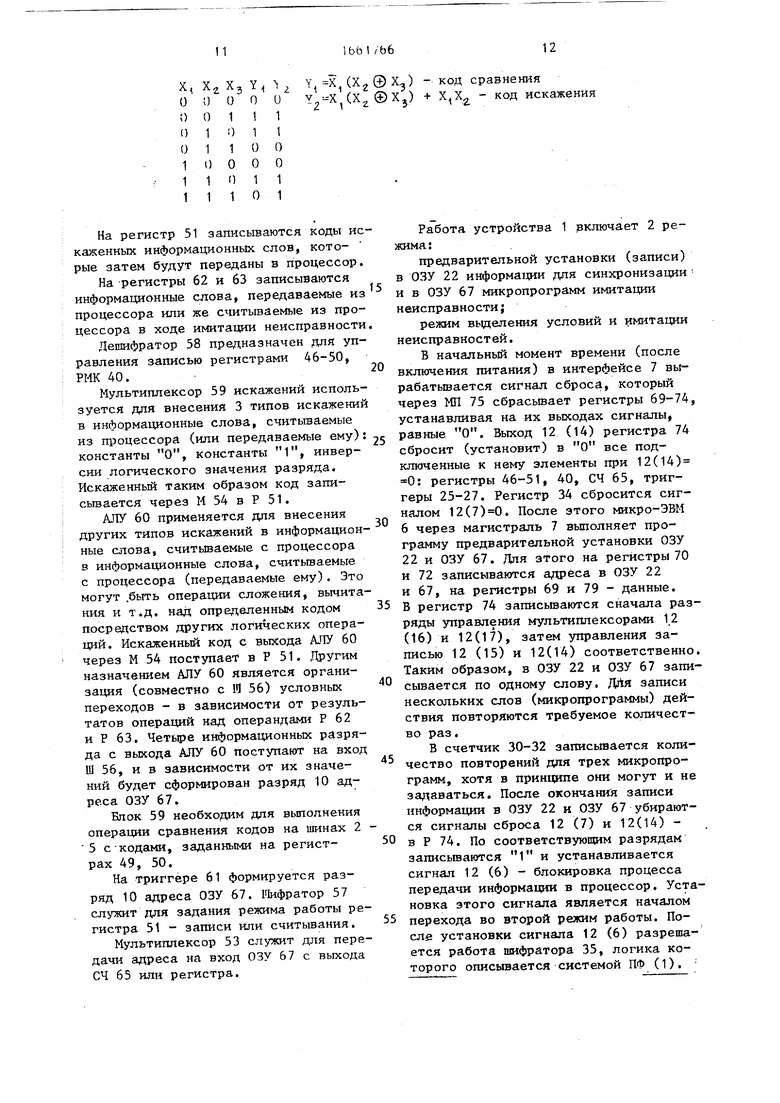

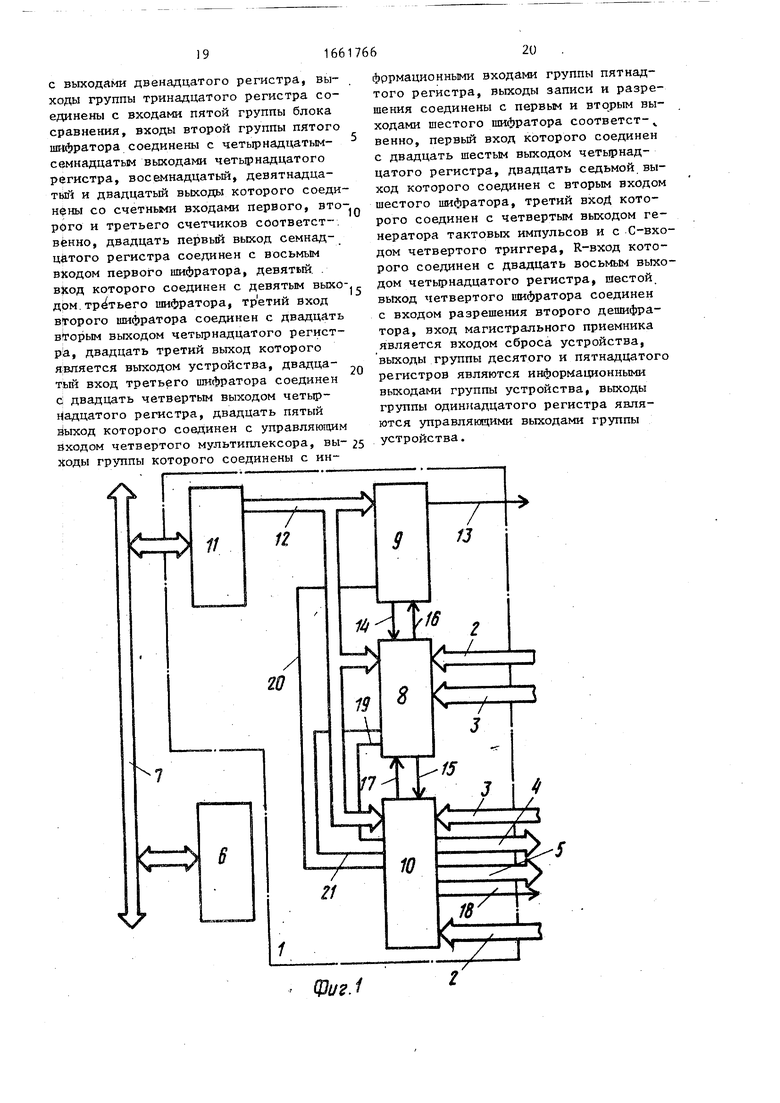

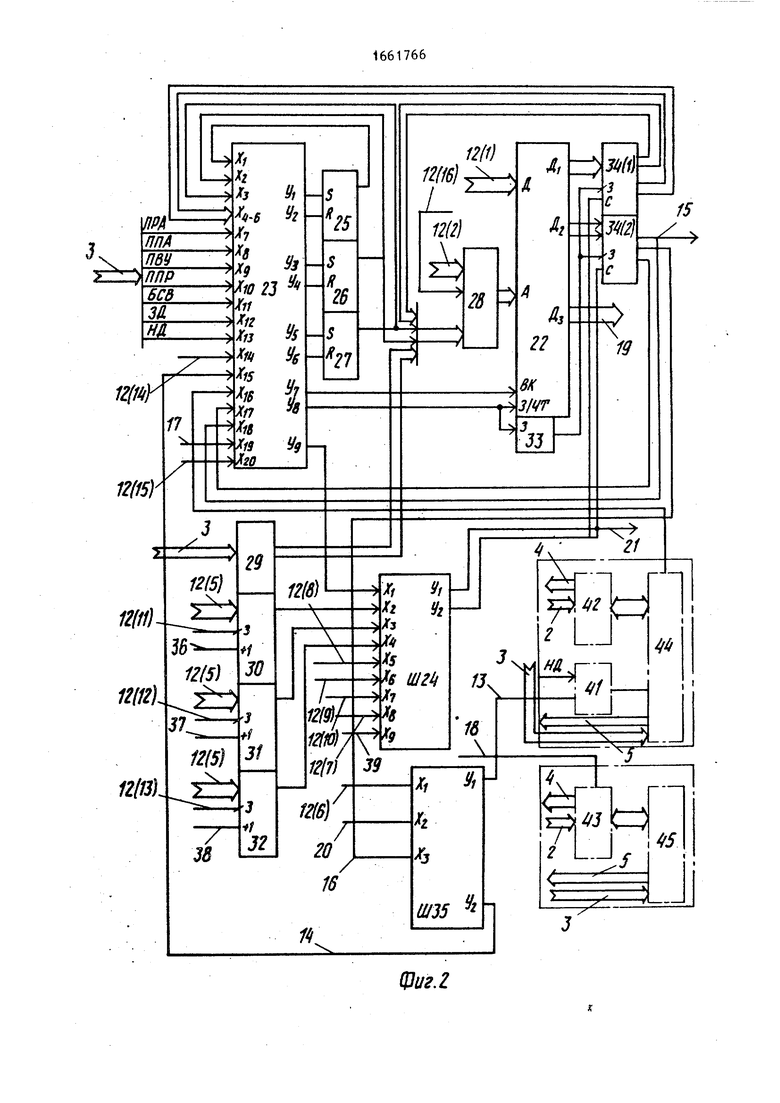

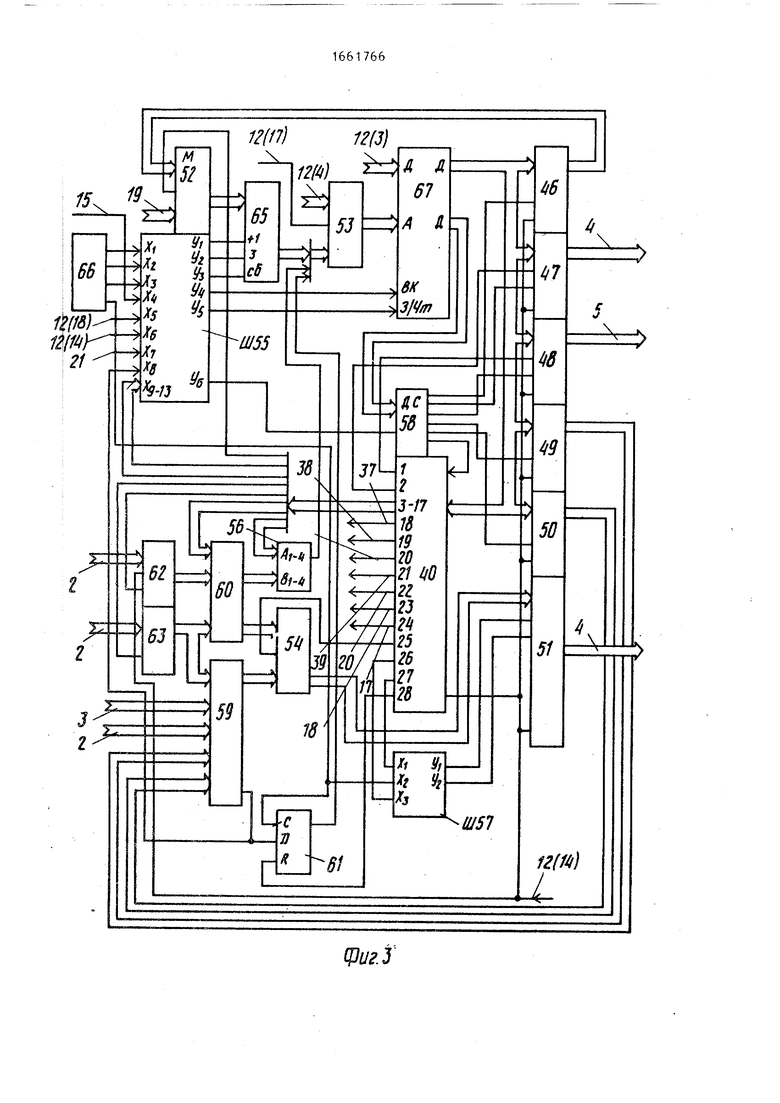

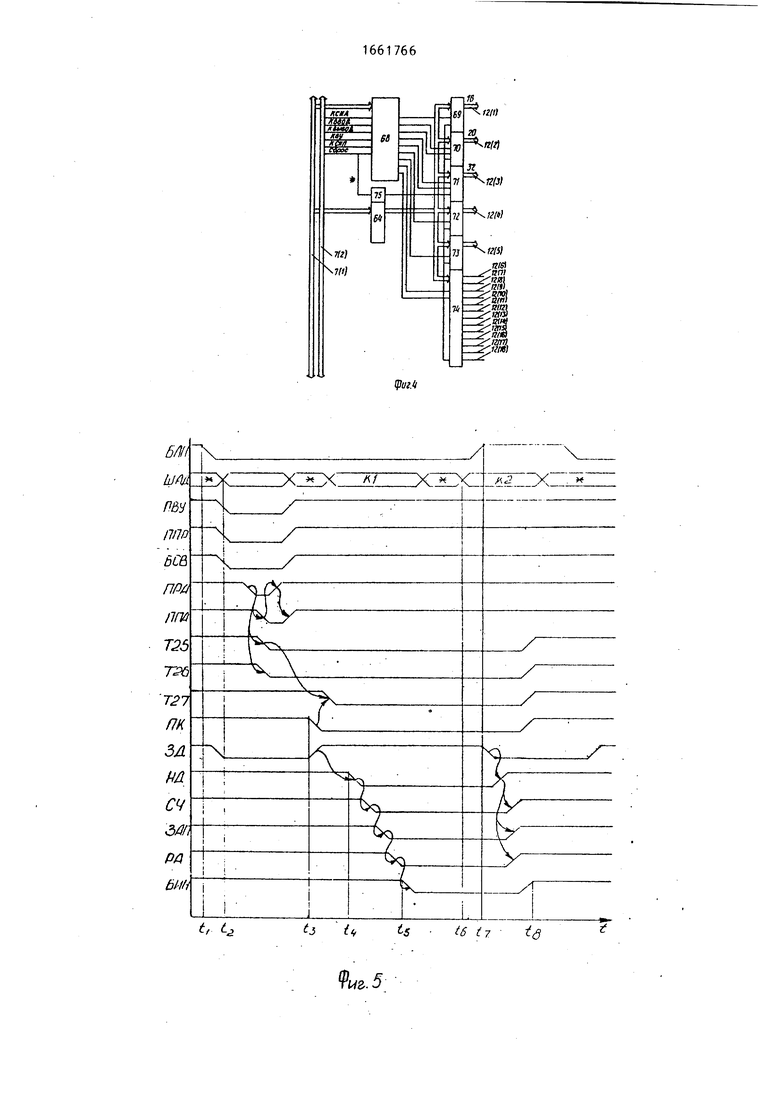

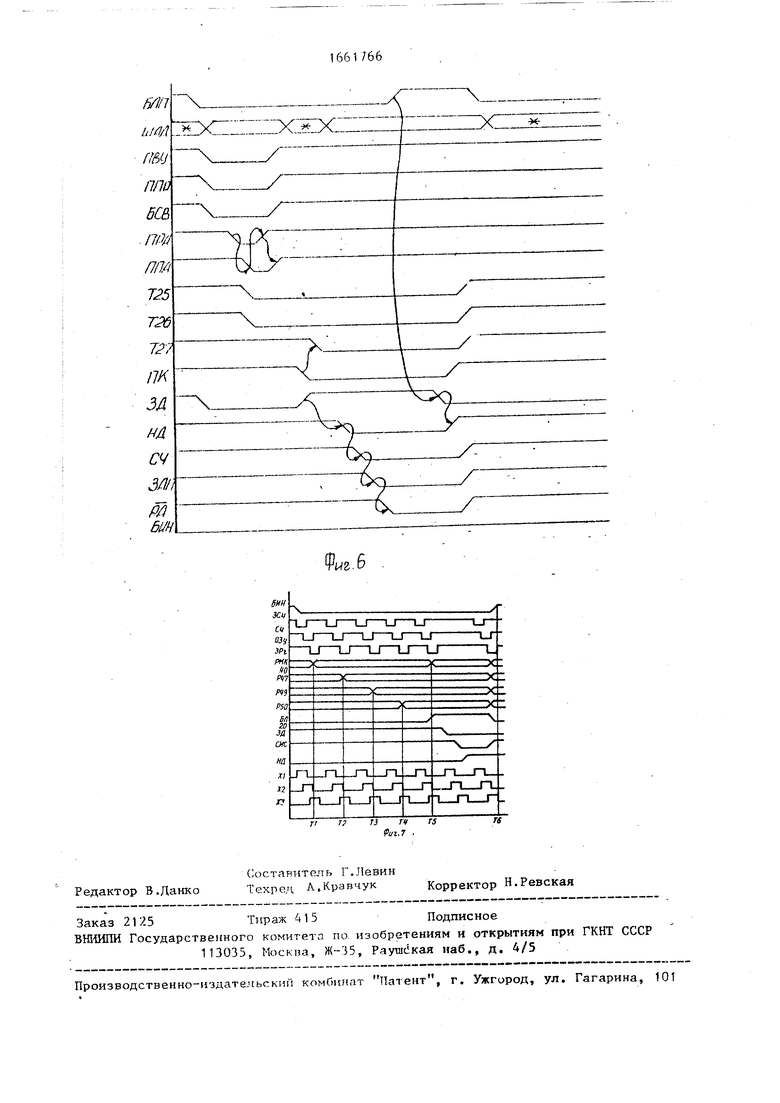

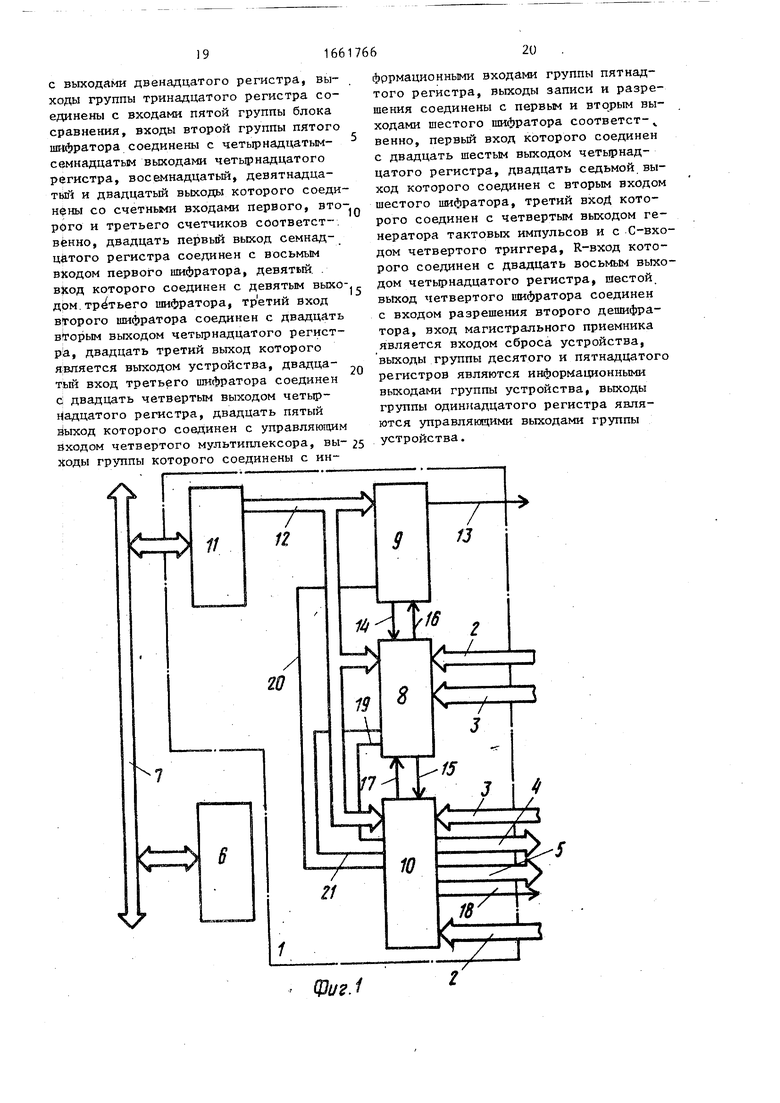

На фиг. 1 представлен комплекс для исследования и имитации отказов и не- и|справностей активных устройств; на Ј|иг. 2 - схемы блока выделения и анализа входной информации (ВБА) и бло- «а блокировки процессора (БП); на фиг. 3 - схема блока имитации неисправностей (ВИН); на фиг. 4 -схема флока управления записью (БУЗ); на фиг. 5 - временная диаграмма работы устройства для имитации неисправностей для случая, когда условия имитации неисправности выделены; на фиг.6 (го же, для случая, когда условия имитации неисправности не выделены; на фиг. 7 - фрагмент временной диаграммы

Комплекс для исследования и имитации отказов и сбоев активных уст- L ройств (фиг. 1) содержит устройство 1 для имитации неисправностей, шины информационного 2 и управляющего 3 входов, информационного 4 и управляющего 5 выходов, ЭВМ 6 и магистраль 7,

Устройство 1 (фиг. 1) содержит БВА 8, БП 9, БИН 10, БУЗ 11, магистраль 12, шины 13 - 18, магистраль 19, шины 20 и 21,

На фиг. 2 показаны схемы блоков 8 и 9, содержащие первый блок 22 памяти (ОЗУ), шифраторы 23,24, триггеры 25 - 27, мультиплексор 28, блок

29шинных формирователей, счетчики

30- 32, элемент 33 задержки, первый и второй регистры 34, шифратор 35, связи 36 - 39 блоков 30-32 и 24, соответственно, с выходами регистра 40 (фиг. 3).

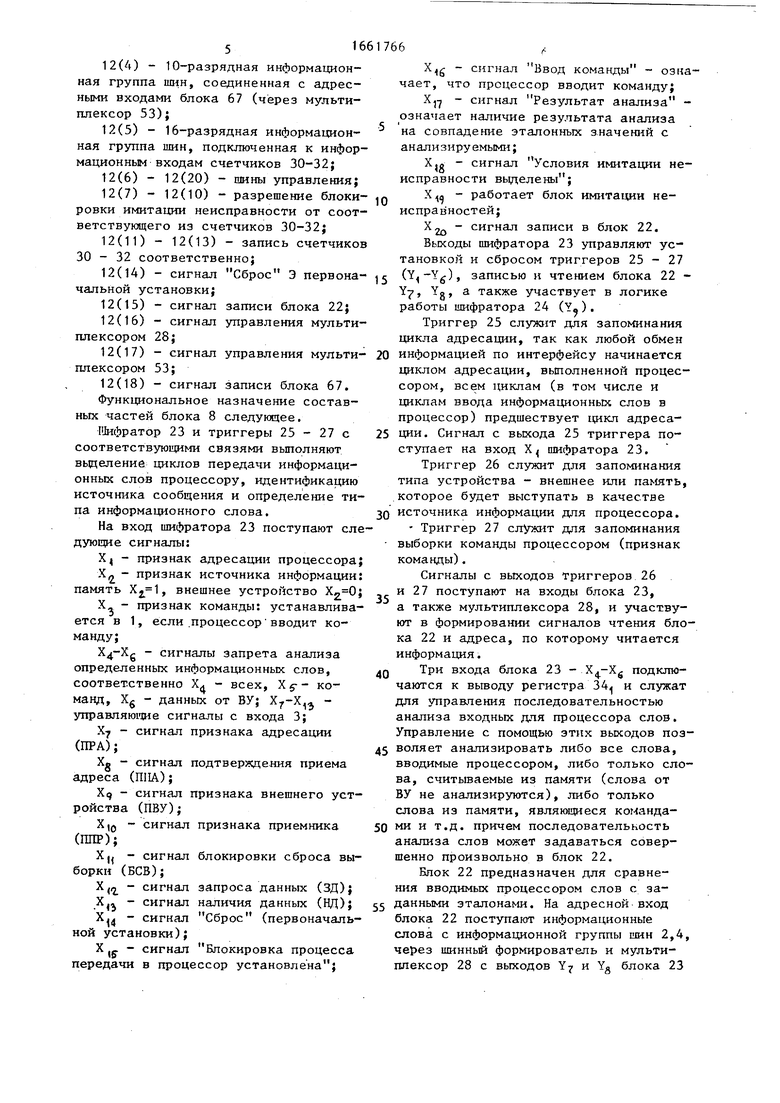

На фиг. 3 представлен блок 10. В него входят регистр 40 микрокоманд (РМК), внешние устройства 41-45 подключаемые к блоку 10, регистры 46-51, мультиплексоры 52-54, шифраторы 55-57, дешифратор 58, блок 59 сравнения, арифметико-логическое устройство (АЛУ) 60, триггер 61, регистры 62,63 шинный формирователь 64, счетчик 65, генератор 66 тактовых импульсов, второй блок 67 памяти (ОЗУ) .

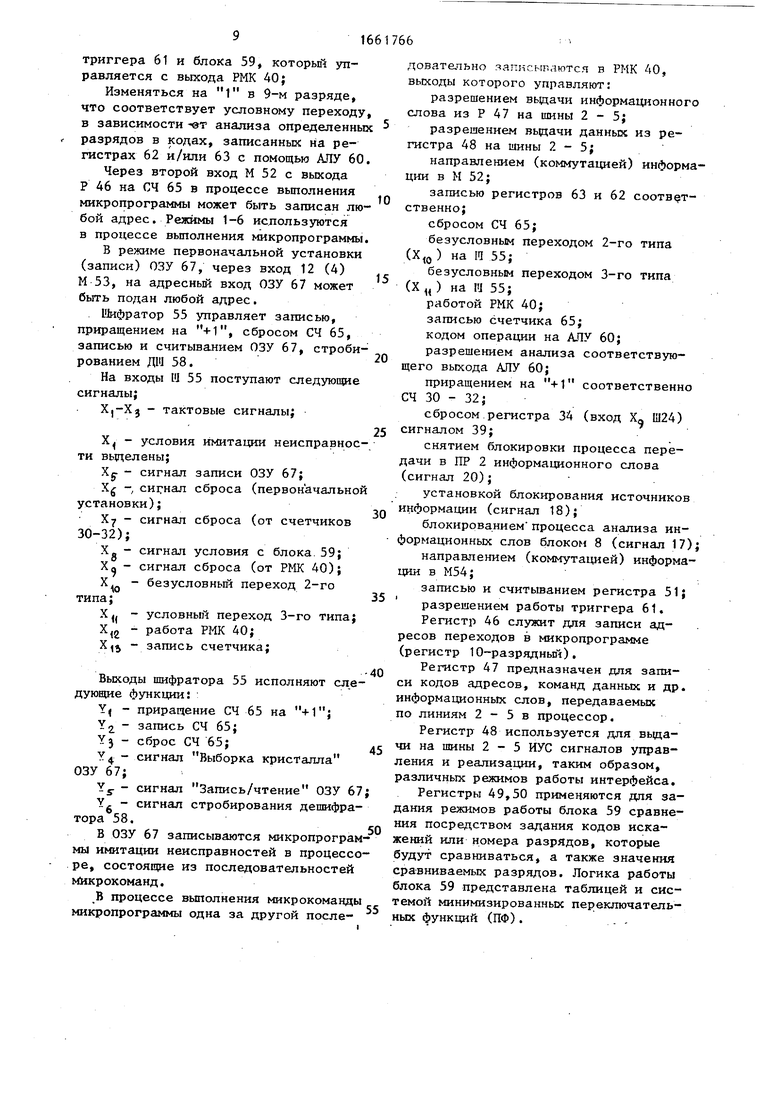

На фиг. 4 показан блок, включающий дешифратор 68, регистры 69-74, магистральный приемник 75.

о

$

0

5

0

5

0

5

Магистраль 7 условно разбита на две группы шин - информационные 7 ( , и управляющие 7 (2). Блок 9 выполняет функции блокировки процесса ввода информационного слова в активное устройство (процессор).

Блок 8 выполняет следующие функции;

выделение циклов передачи информационных слов активному устройству из общего потока передач по шинам 2-5;

идентификация источника сообщения (память или внешнее устройство) и определение типа информационного слова, вводимого активным устройством: команда, данные;

сравнение вводимых процессором слов с заданными эталонами и выделе- ние моментов времени появления определенных слов или их последовательностей (выделение определенных последовательностей информационных слов);

контроль количества имитируемых неисправностей (повторений определенных микропрограмм имитации неисправностей) .

Блок 10 выполняет функции имитации неисправностей (последствий неисправностей в виде искажений информационных слов, хранящихся в элементах памяти процессора). Он блокирует выходы источников информации на интерфейсе и выполняет генерацию последовательностей сигналов, необходимых для передачи процессору последовательностей информационных слов (это могут быть команды, адреса, данные), для считывания из процессора информационных слов (при этом устройство 1 выступает в качестве приемника информации) , для искажения считанных информационных слов и передачи их процессору.

Блок 11 управления записью служит для записи информации в блоки 4,22, 67, 30-32 и управления режимами работы блоков 8-10.

Магистраль 12, идущая из блока 11, включает 6 групп шин.

12(1) - 16-разрядная информационная группа шин, подключенная к информационным входам блока 22;

12(2) - 20-разрядная информационная группа шин, подключенная к адресным входам блока 22 (через мультиплексор 28);

13(3) - 32-разрядная информационная группа шин, соединенная с информационными входами блока 67;

516

12(А) - 10-разрядная информационная группа шин, соединенная с адресными входами блока 67 (через мультиплексор 53);

12(5) - 16-разрядная информационная группа шин, подключенная к информационным входам счетчиков 30-32;

12(6) - 12(20) - шины управления;

12(7) - 12(10) - разрешение блокировки имитации неисправности от соответствующего из счетчиков 30-32;

12(11) - 12(13) - запись счетчиков 30 - 32 соответственно;

12(14) - сигнал Сброс Э первоначальной установки;

12(15) - сигнал записи блока 22}

12(16) - сигнал управления мультиплексором 28;

12(17) - сигнал управления мультиплексором 53;

12(18) - сигнал записи блока 67.

Функциональное назначение составных частей блока 8 следующее.

Шифратор 23 и триггеры 25 - 27 с соответствующими связями выполняют выделение циклов передачи информационных слов процессору, идентификацию источника сообщения и определение типа информационного слова.

На вход шифратора 23 поступают следующие сигналы:

Х( - признак адресации процессора;

Х - признак источника информации: память , внешнее устройство

X, - признак команды: устанавливается в 1, если процессор вводит команду;

- сигналы запрета анализа определенных информационных слов, соответственно Х - всех, X §- - команд, Xg - данных от ВУ; - управляющие сигналы с входа 3;

Х7 - сигнал признака адресации (ПРА);

Х- - сигнал подтверждения приема адреса (П11А);

Xcj - сигнал признака внешнего устройства (ПВУ);

Х,0 - сигнал признака приемника (ППР);

Хц - сигнал блокировки сброса выборки (БСВ);

X4/i - сигнал запроса данных (ЗД);

Х4- сигнал наличия данных (НД);

Х,д - сигнал Сброс (первоначальной установки);

X ( - сигнал Блокировка процесса передачи в процессор установлена ;

766,,

- сигнал Ввод команды - означает, что процессор вводит команду;

Х17 - сигнал Результат анализа - означает наличие результата анализа на совпадение эталонных значений с анализируемыми;

Х,„ - сигнал Условия имитации не йи

исправности выделены ;

Х« - работает блок имитации неисправностей;

2о сигнал записи в блок 22. Выходы шифратора 23 управляют установкой и сбросом триггеров 25-27

г (), записью и чтением блока 22 - Y-p, Yg, а также участвует в логике работы шифратора 24 (Y-).

Триггер 25 служит для запоминания цикла адресации, так как любой обмен

0 информацией по интерфейсу начинается циклом адресации, выполненной процессором, всем циклам (в том числе и циклам ввода информационных слов в процессор) предшествует цикл адреса5 ции. Сигнал с выхода 25 триггера поступает на вход Х шифратора 23.

Триггер 26 служит для запоминания типа устройства - внешнее или память, которое будет выступать в качестве

о источника информации для процессора. Триггер 27 служит для запоминания - выборки команды процессором (признак команды).

Сигналы с выходов триггеров 26 и 27 поступают на входы блока 23, а также мультиплексора 28, и участвуют в формировании сигналов чтения блока 22 и адреса, по которому читается информация.

Q Три входа блока 23 - подключаются к выводу регистра 34 и служат для управления последовательностью анализа входных для процессора слов. Управление с помощью этих выходов поэ5 воляет анализировать либо все слова, вводимые процессором, либо только слова, считываемые из памяти (слова от ВУ не анализируются), либо только слова из памяти, являющиеся команда0 ми и т.д. причем последовательность анализа слов может задаваться совершенно произвольно в блок 22.

Блок 22 предназначен для сравнения вводимых процессором слов с за5 данными эталонами. На адресной вход блока 22 поступают информационные слова с информационной группы шин 2,4, через шинный формирователь и мультиплексор 28 с выходов Y7 и Ys блока 23

5

15

20

25

сигналы считываются. Резупьтат сравнения фиксируется на регистре 34.

Информационные выходы блока 22 разбиты на 3 группы: D1, D2, D3.

D1 - 6-разрядная группа шин, 3 разяда используются для управления поледовательностью анализа входных лов, и 3 разряда являются признаками последовательности - т.е. используют- Q ся для выделения определенных последовательностей.

D2 - 2-разрядная группа шин:

1 шина - Условия имитации неисправности выделены ;

1 шина - Снятие блокировки процесса передачи слова процессору (условия не выделены).

D3 - 8-разрядная группа шин, по которой в блок 10 передается начальный адрес микропрограммы имитации неисправности.

Мультиплексор 28 служит для организации записи в блоке предварительной установки - адрес поступает на вход 12(2) чтения по адресу, поступающему на второй информационный вход блока 22. Управляющий вход - 12(16) мультиплексора 28 подключается к регистру 74.

Регистр 34 служит для фиксации данных с выхода D1 и D2 блока 22. Регистр разбит на две части, которые записываются по одному сигналу, а входы сброса - разные. Выход регистра 34,,с подключенный к входу . - Результат сравнения не имеет соответствующего выхода на ОЗУ 22. Вход, соответствующий этому выходу, подключен к -М .

Элемент 33 задержки служит для организации записи в регистр 34 информации с выхода блока 22.

Блок 29 шинных формирователей включает 4 микросхемы К589АП26 и служит для согласования сигналов, поступающих с 16 шин адреса (данных на вход мультиплексора 28).

На каждый из счетчиков 30-32 для трех различных микропрограмм имитации неисправностей может быть записано количество повторений. Шифратор 24 управляет сбросом регистра 34 в том случае, если количество повторений имитаций неисправностей исчерпано (счетчики 30-32 обнулились) по управлению от шифратора 40 или 74.

На входы шифратора 24 поступают следующие сигналы:

Xо сигнал сброса от шифратора 23;

30

40

45

50

55

5

0

5

Q

,с

30

40

45

50

55

-сигналы равенства О чиков 30 - 32 соответственно;

- сигналы разрешения действия (сброса) регистра 34 от .; ,.

Хо - сигнал сброса от регистра 74}

Х- - сигнал сброса от регистра 40.

Выходы Y, и Y шифратора 23 сбрасывают соответственно первую и вторую части регистра 34.

Шифратор 35, выполняющий функцию блокировки процесса передачи в процессор информационного слова и входящий в блок 9, имеет следующие входы:

X. - сигнал Блокировку процесса

передачи установить (Блокировка процессора);

I

Х - снятие блокировки процессора

от РМК 40;

X - - снятие блокировки процесса передачи (в случае, если условия имитации неисправности не выделены).

На фиг. 3 показаны составные части блока 10. Группа из ОЗУ 67, регистров 40, 46-51, 62, 63 шифраторов 55- 57, дешифратора 58, схемы 59 искажения и сравнения, мультиплексоров 52- 54, АЛУ 60, триггера 61, генератора 66 тактовых импульсов представляет собой микропрограммный автомат, выполняющий функции условной и безусловной генерации сигналов через шины 2-5 для записи и считьюания элементов памяти процессора, выполнения анализа считанных слов - кодов из РОН, СК, ССП, УС, выполнения анализа состояния внутренних элементов памяти и условных переходов в зависимости от состояния отдельных битов и их совокупностей в анализируемых словах.

Адрес для ОЗУ 67 может быть сформирован семью различными способами и зафиксирован на СЧ 65;

Записываться с выхода ОЗУ 22- D3 через М 52. Таким образом, устанавливается первоначальный адрес микропрограммы имитации неисправности.

Увеличиваться на +1, что соответствует безусловному переходу и управляется сигналом Х с выхода РМК 10;

Увеличиваться на -Н в зависимости от состояния шин 2-5, выделяемого блоком 59 (сигнал X на Ш 55) - управляется сигналом X с выхода РМК 40.

Изменяться на 1 в старшем (10-м) разряде, в зависимости от состояния

триггера 61 и блока 59, который управляется с выхода РМК 40;

Изменяться на 1 в 9-м разряде, что соответствует условному переходу, в зависимости -вт анализа определенных разрядов в кодах, записанных на регистрах 62 и/или 63 с помощью АЛУ 60.

Через второй вход М 52 с выхода Р 46 на СЧ 65 в процессе выполнения микропрограммы может быть записан любой адрес. Режимы 1-6 используются в процессе выполнения микропрограммы.

В режиме первоначальной установки (записи) ОЗУ 67, через вход 12 (4) М 53, на адресный вход ОЗУ 67 может быть подан любой адрес.

Шифратор 55 управляет записью, приращением на +1, сбросом СЧ 65, записью и считыванием ОЗУ 67, строби- рованием ДШ 58.

На входы Ш 55 поступают следующие сигналы;

Xj-Xj - тактовые сигналы;

X, - условия имитации неисправности выделены;

Xg- - сигнал записи ОЗУ 67;

Xg - сигнал сброса (первоначальной установки);

X - сигнал сброса (от счетчиков 30-32);

Х - сигнал условия с блока 59;

Хд - сигнал сброса (от РМК 40);

X. - безусловный переход 2-го типа;

X ( - условный переход 3-го типа;

- работа РМК 40;

- запись счетчика;

-40

Выходы шифратора 55 исполняют следующие функции:

У - приращение СЧ 65 на

У2 - запись СЧ 65;

УЗ - сброс СЧ 65;45

У4 - сигнал Выборка кристалла ОЗУ 67;

Уs - сигнал Запись/чтение ОЗУ 67;

Y, - сигнал стробирования дешифратора 58.

В ОЗУ 67 записываются микропрограммы имитации неисправностей в процессоре, состоящие из последовательностей микрокоманд.

В процессе выполнения микрокоманды микропрограммы одна за другой после50

0

5

5

„

0

5

0

5

0

довательно запнгыг.аются в РМК 40, выходы которого управляют:

разрешением выдачи информационного слова из Р 47 на шины 2-5;

разрешением выдачи данных из регистра 48 на шины 2-5;

направлением (коммутацией) информации в М 52;

записью регистров 63 и 62 соответственно;

сбросом СЧ 65;

безусловным переходом 2-го типа (Хю) на II 55;

безусловным переходом 3-го типа (Х„ ) на Ш 55;

работой РМК 40;

записью счетчика 65;

кодом операции на АЛУ 60;

разрешением анализа соответствующего выхода АЛУ 60;

приращением на +1 соответственно СЧ 30-32;

сбросом регистра 34 (вход Х Ш24) сигналом 39;

снятием блокировки процесса передачи в ПР 2 информационного слова (сигнал 20);

установкой блокирования источников информации (сигнал 18);

блокированием процесса анализа информационных слов блоком 8 (сигнал 17);

направлением (коммутацией) информации в М54;

записью и считыванием регистра 51;

разрешением работы триггера 61.

Регистр 46 служит для записи адресов переходов в микропрограмме (регистр 10-разрядный).

Регистр 47 предназначен для записи кодов адресов, команд данных и др. информационных слов, передаваемых по линиям 2 - 5 в процессор.

Регистр 48 используется для выдачи на шины 2-5 ИУС сигналов управления и реализации, таким образом, различных режимов работы интерфейса.

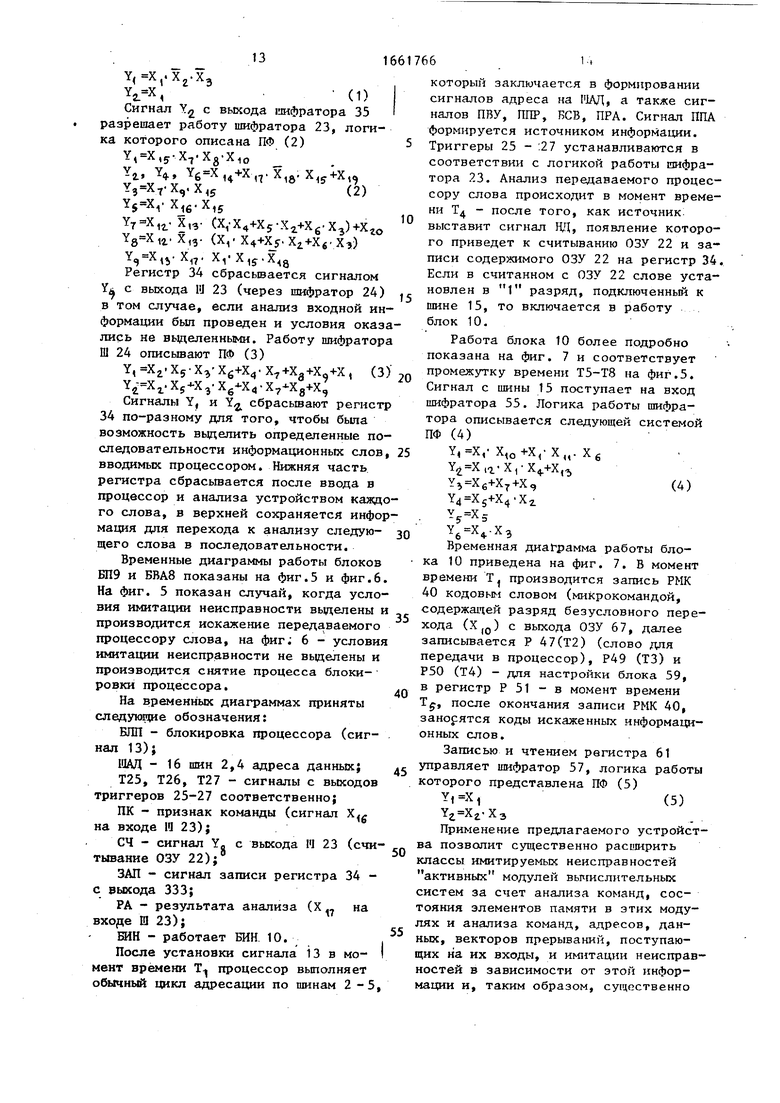

Регистры 49,50 применяются для задания режимов работы блока 59 сравнения посредством задания кодов искажений или номера разрядов, которые будут сравниваться, а также значения сравниваемых разрядов. Логика работы блока 59 представлена таблицей и системой минимизированных переключательных функций (ПФ).. X, X2 X3 Y z Yt X, (X2 © X3) - код сравнения

v -X (X2©X) + Х,Хг - код искажения

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации отказов и сбоев ЭВМ | 1987 |

|

SU1564628A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Устройство для контроля неисправностей | 1991 |

|

SU1798787A1 |

| Устройство для контроля неисправностей | 1987 |

|

SU1564626A1 |

| Устройство сопряжения двух ЭВМ | 1985 |

|

SU1334153A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Устройство для контроля за ходом вычислительного процесса | 1987 |

|

SU1539780A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1536388A1 |

Изобретение относится к вычислительной технике и предназначено для имитации неисправностей в активных устройствах вычислительных систем при экспериментальном исследовании их надежности. Целью изобретения является расширение функциональных возможностей устройства за счет имитации отказов и сбоев активных устройств. Устройство для имитации неисправностей включает блок выделения и анализа входной информации 8, содержащий ОЗУ, шифраторы, триггеры, мультиплексор, блок шинных формирователей, счетчики, элемент задержки, регистры, блок блокировки процессора состоит из шифратора, блок имитации неисправности содержит регистр микрокоманды, регистры, мультиплексоры, шифраторы, дешифратор, СИС, АЛУ, триггер, регистры, счетчик, генератор тактовых импульсов, ОЗУ, блок управления записью, включающий блок шинных формирователей, дешифратор, регистры, магистральный приемник. БВА осуществляет выделение цикла передачи информационных слоев процессору, идентификацию источника сообщения, операцию сравнения и контроль количества имитируемых неисправностей. Блок БП выполняет функции блокировки процесса ввода информационного слова в ПР. Блок имитации неисправности имитирует неисправности. Блок управления записью служит для записи информации в ОЗУ, счетчики и управления режимами работы блоков. Устройство выполняет ряд различных команд имитации неисправностей, зависящие от последовательности информационных слов (команд, адресов, данных, векторов прерываний). При этом имитируются физические неисправности активных устройств ЭВМ, таких как процессор, контролер диска и т. п. Применение предлагаемого устройства в процессе экспериментального исследования надежности устройств ВС позволяет значительно расширить количество имитируемых неисправностей, что дает возможность повысить достоверность оценок надежности этих устройств. 7 ил.

На регистр 51 записываются коды искаженных информационных слов, которые затем будут переданы в процессор.

На регистры 62 и 63 записываются информационные слова, передаваемые из процессора или же считываемые из процессора в ходе имитации неисправности

Дешифратор 58 предназначен для управления записью регистрами 46-50, РМК 40.

Мультиплексор 59 искажений используется для внесения 3 типов искажений в информационные слова, считываемые из процессора (или передаваемые ему): константы О, константы 1, инверсии логического значения разряда. Искаженный таким образом код записывается через М 54 в Р 51.

АЛУ 60 применяется для внесения других типов искажений в информационные слова, считываемые с процессора в информационные слова, считываемые с процессора (передаваемые ему). Это могут .быть операции сложения, вычитания и т.д. над определенным кодом посредством других логических операций. Искаженный код с выхода АЛУ 60 через М 54 поступает в Р 51. Другим назначением АЛУ 60 является организация (совместно с Ш 56) условных переходов - в зависимости от результатов операций над операндами Р 62 и Р 63. Четыре информационных разряда с выхода АЛУ 60 поступают на вход Ш 56, и в зависимости от их значений будет сформирован разряд 10 адреса ОЗУ 67.

Елок 59 необходим для выполнения операции сравнения кодов на шинах 2 - 5 с кодами, заданными на регистрах 49, 50.

На триггере 61 формируется разряд 10 адреса ОЗУ 67. Шифратор 57 служит для задания режима работы регистра 51 - записи или считывания.

Мультиплексор 53 служит для передачи адреса на вход ОЗУ 67 с выхода СЧ 65 или регистра.

0

5

0

5

0

5

0

5

Работа устройства 1 включает 2 режима:

предварительной установки (записи) в ОЗУ 22 информации для синхронизации и в ОЗУ 67 микропрограмм имитации неисправности;

режим выделения условий и имитации неисправностей.

В начальный момент времени (после включения питания) в интерфейсе 7 вырабатывается сигнал сброса, который через МП 75 сбрасывает регистры 69-74, устанавливая на их выходах сигналы, равные О. Выход 12 (14) регистра 74 сбросит (установит) в О все подключенные к нему элементы при 12(14) 0: регистры 46-51, 40, СЧ 65, триггеры 25-27. Регистр 34 сбросится сигналом 12(7)0. После этого микро-ЭВМ 6 через магистраль 7 выполняет программу предварительной установки ОЗУ 22 и ОЗУ 67. Для этого на регистры 70 и 72 записываются адреса в ОЗУ 22 и 67, на регистры 69 и 79 - данные. В регистр 74 записываются сначала разряды управления мультиплексорами 12 (16) и 12(17), затем управления записью 12 (15) и 12(14) соответственно. Таким образом, в ОЗУ 22 и ОЗУ 67 записывается по одному слову. Для записи нескольких слов (микропрограммы) действия повторяются требуемое количество раз.

В счетчик 30-32 записывается количество повторений для трех микропрограмм, хотя в принципе они могут и не задаваться. После окончания записи информации в ОЗУ 22 и ОЗУ 67 убираются сигналы сброса 12 (7) и 12(14) - в Р 74, По соответствующим разрядам записываются 1 и устанавливается сигнал 12 (6) - блокировка процесса передачи информации в процессор. Установка этого сигнала является началом перехода во второй режим работы. После установки сигнала 12 (6) разрешается работа шифратора 35, логика которого описывается системой Ш (1).

Y, X..

Yt-X,

хг хэ

(1)

Сигнал У2 с выхода шифратора 35 разрешает работу шифратора 23, логика которого описана ПФ (2)

Y,X

1

YI. Y

15г Х7- Xg X10

Ч

X7-X«j.

X Ч+Х

(7 Х1б Х15+Х)

(2)

Х16- Х,5

Y$-AV

YT-X№. Х„- (Х1-Х4+Х5-Хг+Х6.Х3)+Х

. Х„- (Х,-Х4+Х г. Х2+Х6-ХЭ)

Y«) X17 Х1 Х1Ј Х48

Регистр 34 сбрасывается сигналом

Y с выхода Ш 23 (через шифратор 24) в том случае, если анализ входной информации был проведен и условия оказались не выделенными. Работу шифратора Ш 24 описывают П (3)

Y,X2.X5-X X6+X4-X7+X3+X9+X, (3)

Ґ4--Хг. Х7-Х8н-Х,

Сигналы Y, и Y сбрасывают регистр 34 по-разному для того, чтобы была возможность выделить определенные последовательности информационных слов, вводимых процессором. Нижняя часть регистра сбрасывается после ввода в процессор и анализа устройством каждо го слова, в верхней сохраняется информация для перехода к анализу следую- щего слова в последовательности.

Временные диаграммы работы блоков БП9 и БВА8 показаны на фиг.5 и фиг.6. На фиг. 5 показан случай, когда условия имитации неисправности выделены и производится искажение передаваемого процессору слова, на фиг; 6 - условия имитации неисправности не выделены и производится снятие процесса блокировки процессора.

На временных диаграммах приняты следующие обозначения:

БЛП - блокировка процессора (сигнал 13);

ШАД - 16 шин 2,4 адреса данных}

Т25, Т26, Т27 - сигналы с выходов триггеров 25-27 соответственно;

ПК - признак команды (сигнал Х на входе Ш 23);

СЧ - сигнал

Y-, с выхода М 23 (считывание ОЗУ 22);

ЗАЛ - сигнал записи регистра 34 - с выхода 333;

РА - результата анализа ( на входе Ш 23);

БИН - работает БИН 10.,

После установки сигнала 13 в мо- I мент времени Т процессор выполняет обычный цикл адресации по шинам 2-5,

10

,5

20

25- зо

35

40

45

,

50

55

который заключается в формировании сигналов адреса на ШАД, а также сигналов ПВУ, ППР, БСВ, ПРА. Сигнал ППА формируется источником информации. Триггеры 25-27 устанавливаются в соответствии с логикой работы шифратора 23. Анализ передаваемого процессору слова происходит в момент времени Т - после того, как источник выставит сигнал НД, появление которого приведет к считыванию ОЗУ 22 и записи содержимого ОЗУ 22 на регистр 34. Если в считанном с ОЗУ 22 слове установлен в 1 разряд, подключенный к шине 15, то включается в работу блок 10.

Работа блока 10 более подробно показана на фиг. 7 и соответствует промежутку времени Т5-Т8 на фиг.5. Сигнал с шины 15 поступает на вход шифратора 55. Логика работы шифратора описывается следующей системой ПФ (4)

YJ Х, +Х( X ,,. X g

IT. X | ,

Y,X6+X7+X9 У4 Х5+Х4 Хг

v Y - лэ

(4)

Временная диаграмма работы блока 10 приведена на фиг. 7. В момент времени Т1 производится запись РМК 40 кодовым словом (микрокомандой, содержащей разряд безусловного перехода (Х(0) с выхода ОЗУ 67, далее записывается Р 47(Т2) (слово для передачи в процессор), Р49 (ТЗ) и Р50 (Т4) - для настройки блока 59, в регистр Р 51 - в момент времени Т, после окончания записи РМК 40, заносятся коды искаженных информационных слов.

Записью и чтением регистра 61 управляет шифратор 57, логика работы которого представлена ПФ (5)

Yi-X1(5)

Y Х X з

Применение предлагаемого устройства позволит существенно расширить классы имитируемых неисправностей активных модулей вычислительных систем за счет анализа команд, состояния элементов памяти в этих модулях и анализа команд, адресов, данных, векторов прерываний, поступающих на их входы, и имитации неисправностей в зависимости от этой информации и, таким образом, существенно

2

увеличить глубину и детализрлщю проводимых с помощью устройства экспериментальных исследований надежности ВС.

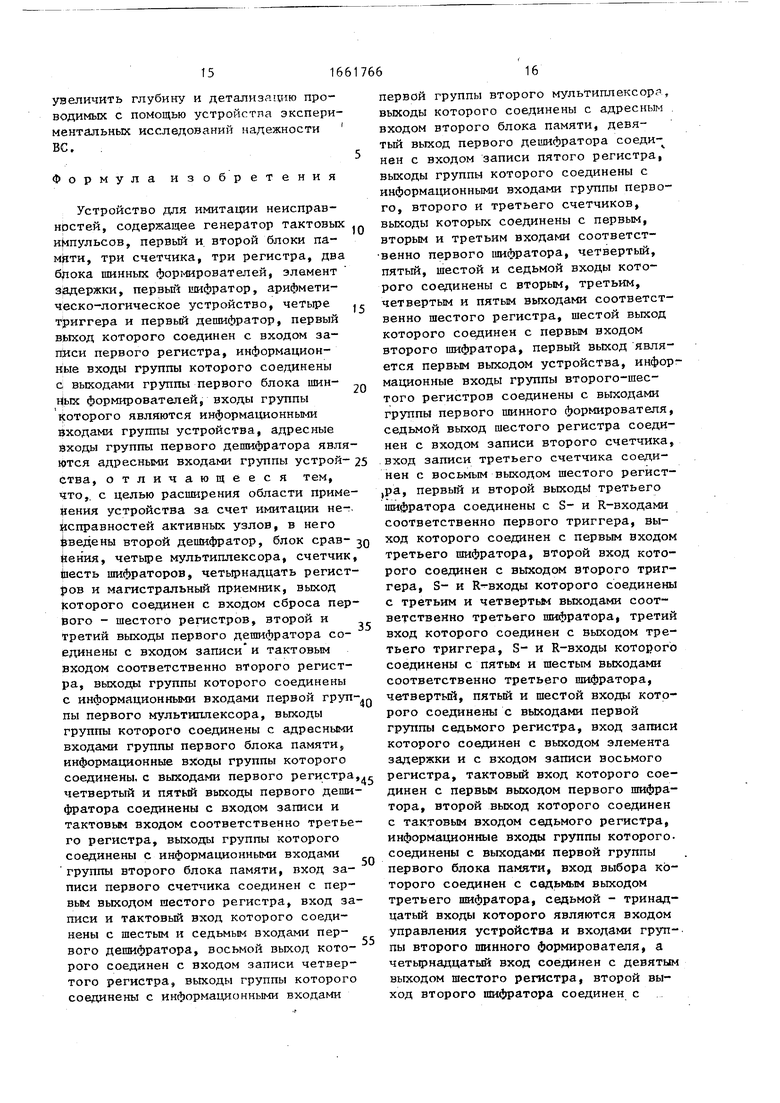

Формула изобретения

Устройство для имитации неисправностей, содержащее генератор тактовых . импульсов, первый и второй блоки памяти, три счетчика, три регистра, два блока шинных формирователей, элемент задержки, первый шифратор, арифмети- ческо-логическое устройство, четыре . триггера и первый дешифратор, первый выход которого соединен с входом записи первого регистра, информационные входы группы которого соединены с выходами группы первого блока шин- Ных формирователей, входы группы которого являются информационными Входами группы устройства, адресные входы группы первого дешифратора являются адресными входами группы устрой- 2 ства, отличающееся тем, что, с целью расширения области применения устройства за. счет имитации неисправностей активных узлов, в него введены второй дешифратор, блок срав- зд нения, четыре мультиплексора, счетчик, Ьесть шифраторов, четырнадцать регистров и магистральный приемник, выход Которого соединен с входом сброса первого - шестого регистров, второй и третий выходы первого дешифратора соединены с входом записи и тактовым входом соответственно второго регистра, выходы группы которого соединены с информационными входами первой группы первого мультиплексора, выходы группы которого соединены с адресными входами группы первого блока памяти, информационные входы группы которого соединены, с выходами первого регистра, четвертый и пятый выходы первого дешифратора соединены с входом записи и тактовым входом соответственно третьего регистра, выходы группы которого соединены с информационными входами группы второго блока памяти, вход записи первого счетчика соединен с первым выходом шестого регистра, вход записи и тактовый вход которого соединены с шестым и седьмым входами первого дешифратора, восьмой выход которого соединен с входом записи четвертого регистра, выходы группы которого соединены с информационными входами

3

5

5

0

-. ,. 5зд .п ., 35

50

55

первой группы второго мультиплексор, выходы которого соединены с адресным входом второго блока памяти, девятый выход первого дешифратора соеди- нен с входом записи пятого регистра, выходы группы которого соединены с информационными входами группы первого, второго и третьего счетчиков, выходы которых соединены с первым, вторым и третьим входами соответственно первого шифратора, четвертый, пятый, шестой и седьмой входы которого соединены с вторым, третьим, четвертым и пятым выходами соответственно шестого регистра, шестой выход которого соединен с первым входом второго шифратора, первый выход является первым выходом устройства, информационные входы группы второго-шес- того регистров соединены с выходами группы первого шинного формирователя, седьмой выход шестого регистра соединен с входом записи второго счетчика, вход записи третьего счетчика соединен с восьмым выходом шестого регистра, первый и второй выходь третьего шифратора соединены с S- и R-входами соответственно первого триггера, выход которого соединен с первым входом третьего шифратора, второй вход которого соединен с выходом второго триггера, S- и R-входы которого соединены с третьим и четвертым выходами соответственно третьего шифратора, третий вход которого соединен с выходом третьего триггера, S- и R-входы которого соединены с пятым и шестым выходами соответственно третьего шифратора, четвертый, пятый и шестой входы которого соединены с выходами первой группы седьмого регистра, вход записи которого соединен с выходом элемента задержки и с входом записи восьмого регистра, тактовый вход которого соединен с первым выходом первого шифратора, второй выход которого соединен с тактовым входом седьмого регистра, информационные входы группы которого, соединены с выходами первой группы первого блока памяти, вход выбора которого соединен с седьмым выходом третьего шифратора, седьмой - тринадцатый входы которого являются входом управления устройства и входами группы второго шинного формирователя, а четырнадцатый вход соединен с девятым выходом шестого регистра, второй выход второго шифратора соединен с

пятнадцатым входом третьего шифратора шестнадцатый вход которого является входом ввода команды устройства, а семнадцатый вход соединен с первым выходом восьмого регистра, второй вы- ход которого соединен с вторым входом второго шифратора, третий выход восьмого регистра соединен с восемнадцатым входом третьего шифратора, девятнадцатьй вход которого соединен с десятым выходом шестого регистра, одиннадцатый выход которого соединен с управляющим входом первого мультиплексора, информационные входы вто- рой группы которого соединены с выходами второй группы седьмого регистра, с выходами второго и третьего триггеров, с выходами группы второго шинного формирователя, восьмой выход третьего шифратора соединен с входом элемента задержки и с входом чтения- записи первого блока памяти, информационные входы группы восьмого регистра соединены с выходами второй груп- пы первого блока памяти, выходы третьей группы которого соединены с информационными входами первой группы третьего мультиплексора, информационные входы второй группы которого сое- динены с выходами группы девятого регистра, информационные входы группы которого соединены с выходами первой группы второго блока памяти и с информационными входами группы десятое го - четырнадцатого регистров, выходы второй группы второго блока памяти соединены с информационными входами группы второго дешифратора, первый - пятый выходы которого соединены с входом записи девятого-тринадцатого регистров, а шестой выход соединен с входом записи четырнадцатого регистра, первый выход которого соединен с входом разрешения одиннадцатого регистра, второй выход соединен с входом разрешения десятого регистра, третий выход четырнадцатого регистра соединен с управляющим входом третьего мультиплексора, выходы группы которого соединены с информационными входами группы четвертого счетчика, счетный вход которого соединен с первым выходом четвертого шифратора, второй выход которого соединен с вхо

дом записи четвертого счетчика, вход сброса которого соединен с третьим выходом четвертого шифратора, четвертый выход которого соединен с входом

0

-п , 5 Q % Q 5 -

5

5

выбора второго блока памяти, ьчод записи-чтения которого соединен с пятым выходом четвертого шифратора, первый, второй и третий входы которого соединены с первым, вторым и третьим выходами соответственно генератора тактовых импульсов, четвертый вход четвертого шифратора соединен с третьим выходом восьмого регистра, пятый вход соединен с двенадцатым выходом шестого регистра, тринадцатый выход которого соединен с управляющим входом второго мультиплексора, информационные входы второй группы которого соединены с выходами группы четвертого счетчика, с выходом четвертого триггера и с выходом пятого шифратора, входы первой группы которого соединены с выходами первой группы арифметическо-логического устройства, выходы второй группы которого соединены с информационными входами первой группы четвертого мультиплексора, информационные входы второй группы которого соединены с выходами группы блока сравнения, выход которого соединен с D-входом четвертого триггера и с шестым входом четвертого шифратора, седьмой вход которого соединен с восьмым входом шестого регит стра и с входами сброса девятого - шестнадцатого регистров, четвертый и пятый выходы четырнадцатого регистра соединены с входами записи шестнадцатого и семнадцатого регистров соответственно, информационные входы группы которых являются информационным входом группы устройства, первый выход первого шифратора соединен с восьмым входом четвертого шифратора, девятый - тринадцатый входы которого соединены с шестым - десятым выходами четырнадцатого регистра, одиннадца- t тый - тринадцатый выходы которого соединены с входами команд группы ариф- метическо-логического устройства, информационные входы первом группы которого соединены с выходами группы шестнадцатого регистра, а информационные входы второй группы соединены с выходами группы семнадцатого регистра и с входами первой группы блока сравнения, входы второй группы которого являются входами управления группы устройства, информационные входы группы которого являются входами третьей группы блока сравнения, входы четвертой группы которого соединены

с выходами двенадцатого регистра, выходы группы тринадцатого регистра соединены с входами пятой группы блока сравнения, входы второй группы пятого шифратора соединены с четырнадцатым- семнадцатым выходами четырнадцатого регистра, восемнадцатый, девятнадцатый и двадцатый выходы которого соеди н$ны со счетными входами первого, второго и третьего счетчиков соответственно, двадцать первый выход семнадцатого регистра соединен с восьмым входом первого шифратора, девятый вХод которого соединен с девятым выхо дом третьего шифратора, третий вход второго шифратора соединен с двадцать вторым выходом четырнадцатого регистра, двадцать третий выход которого является выходом устройства, двадцатый вход третьего шифратора соединен с двадцать четвертым выходом четырнадцатого регистра, двадцать пятый выход которого соединен с управляющим йходом четвертого мультиплексора, вы- ходы группы которого соединены с ин

Шиг.1

5

5

0

фррмационными входами группы пятнад- того регистра, выходы записи и разрешения соединены с первым и вторым выходами шестого шифратора соответст-х венно, первый вход которого соединен с двадцать шестым выходом четырнадцатого регистра, двадцать седьмой выход которого соединен с вторым входом шестого шифратора, третий вход которого соединен с четвертым выходом генератора тактовых импульсов и с С-вхо- дом четвертого триггера, R-вход которого соединен с двадцать восьмым выходом четырнадцатого регистра, шестой выход четвертого шифратора соединен с входом разрешения второго дешифратора, вход магистрального приемника является входом сброса устройства, выходы группы десятого и пятнадцатого регистров являются информационными выходами группы устройства, выходы группы одиннадцатого регистра являются управляющими выходами группы устройства.

«41

I

ЈJ

S1

$5i

ЈM

x%

/

14 /

$

3

31

и

tv.

ч :

ч

« vЈ

Г

4D О

X

§

5

N.

SRE

/

§

/

ER

fc

i . в.в

v.cs.4 c Jемсчч, Csje

sR-sft 5

Г«-5

I

«SI

WJ 7

6 (-.

%г.5

Si

JO

«W

J ««W

: х/даУ яй

ora

/),

дли

2r«

pa

ш,

9м В

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-07—Публикация

1988-12-01—Подача