(54) УСТРОЙСТВО ДЛЯ ОТЛАДКИ ТЕСТОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки тестов | 1982 |

|

SU1084804A2 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ И ВНУТРИСХЕМНОГО ТЕСТИРОВАНИЯ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АППАРАТУРЫ | 1995 |

|

RU2093885C1 |

| Устройство для имитации отказов дискретной аппаратуры | 1984 |

|

SU1183972A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1290333A1 |

| Устройство для контроля цифровых узлов | 1977 |

|

SU643876A2 |

| Многоканальное устройство тестового контроля логических узлов | 1985 |

|

SU1265778A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Многоканальное устройство для контроля систем управления | 1985 |

|

SU1345200A1 |

| Устройство для имитации отказов дискретной аппаратуры | 1990 |

|

SU1815642A1 |

I

Изобретение относится к автоматике и вычислительной технике и может быть использовано а аппаратуре контроля цифровых узлов электронных вы ислительных машин.

Известно устройство для контроля субблоков в вычислительных системах, содержащее блок сопряжения, блок памяти и многоканальную схему несовпадения l}.

Недостаток известного устройства заключается в низкой достоверности контроля вследствие невозможности отладки тестов.

Наиболее близким к предлагаемому является многоканальное устройство для контроля цифровых узлов, содержащее .блок памяти, выходы которого соединены со входами регистра, соединенног вькодами со входами блока сопряжения

Это устройство осуществляет контроль цифрсэвого узла посредством задания на его входы тестовых наборов и анализа результатов, снимаемых с выходов контролируемого цифрового узла.

Недостаток устройства - низкая ,достоверность контроля вследствие невозможности отладки и проверки количества используемых тестов методом

имитации возможных неисправностей контролируемого цифрового узла.

Цель изобретения - повышение достоверности контроля.

Поставленная цель достигается тем, что в устройство для отладди тестов, содержащее блок памяти, группа выходов которого соединена с группой входов регистра,первая группа выходов которо10го соединена с группой входов первого коммутатора, введены первый и второй адаптеры, блок входных воздействий дешифратор и второй коммутатор, группа выходов которого соединена с груп15пой входов первого адаптера,группа входов которого является группой выходов устройства, первая группа входов второго коммутатора соединена с группой выходов первого коммутатораJ вторая группа входов - через второй

20 адаптер с группой выходов контролируемого узла, третья группа входов через последовательно включенные блок выходных дефектов и дешифратор

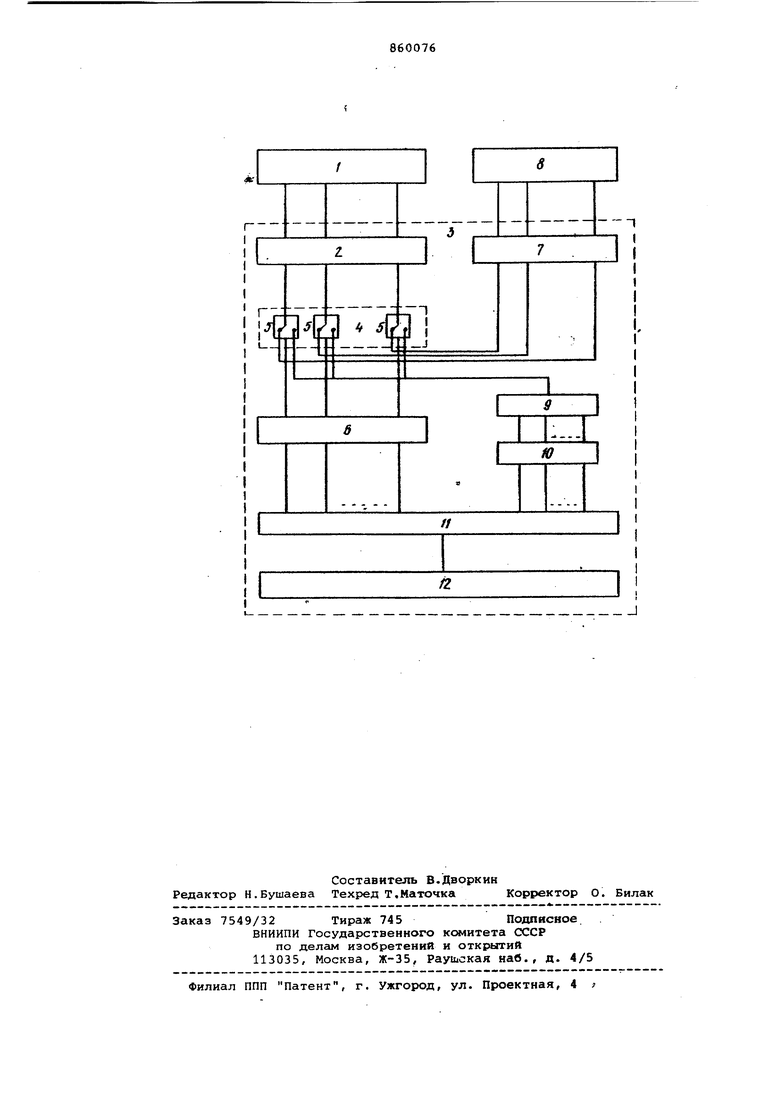

25 со второй группой выходов регистра. На чертеже приведена блок-схема устройства.

К штатному разъему вычислительной системы 1 подключены через адаптер 2 выходы многоканального устройства

30

3 тестового контроля являющиеся выходами второго коммутатора 4, включающего управляемые каналы 5. Управляющий вход каждого из каналов 5 является первым входом коммутатора 4 и соединен с соответству;ощим выходом первого коммутатора 6, предназначенного для коммутации на входы вычислительной системы 1 сигналов разного уровня и длительности. Второй вход каждого канала 5 является вторыми входами коммутатора 4 и соединен через адаптер 7 с вькодами контролируемого узла 8, третий вход каждого канала 5 - третьим входомкоммутатора 4 и соединен с выходом блока 9 выходных дефектов позволяющего имитировать типовые дефекты на выходах контролируемого узла 8. Входы формирователя 9 соединены с выходами дешифратора 10, предназначенного для расшифровки кода типового дефекта, записанного в регистре 11, первые выходы которого соединены со входами первого коммутатора 6, вторые выходы - со входами дешифратора 10,а входы- - с выходами блока 12 памяти хранящего специальные тесты для отладки тестов при контроле узла 8 с помощью вычислительной системы 1.

Устройство работает следующим образом .

В штатный разъем вычислительной системы 1 взамен контролируемого узла 8 подключается адаптером 2 многоканальное устройство 3 тестового контроля, ко второму адаптеру 7 которого подключается контролируемый узел 8. Блок 12 памяти вьщает на регистр 11 первый тестовый набор, задающий характер первого дефекта:номер канала, в котором имитируется дефект, и вид коммутируемого дефекта. Номер канала задается состоянием логическая 1 в первых разрядах регистра 11, связанных с первыгл коммутатором 6, а вид дефекта (обрыв, короткое замыкание, дребезг, неполный уровень, сигнал заданной длительности и т.д.) задается кодом из вторых разрядов регистра 11, связанных с дешифратором 10. Установившийся на регистре 11 код воздействует на первый коммутатор 6, который управляет каналами 5 коммутатора 4 таким образом, что если в первых разрядах регистра 11 установлены нули, то соответствугадие им каналы З.настpoeH J на передачу в вычислительную 1 сигналов, поступающих от контактов контролируемого узла 8, если же в каком-либо разряде из первых разрядов регистра 11 находится единица, то соответствующий ему канал 5 настраивается на передачу в вычислительную систему 1 дефектного сигнала, поступающего от блока 9 выходных дефектов. Код со вторых разрядов регистра 11 поступает на дешифратор 10, где дешифруется и в виде управляющего сигнала задает на входе блока 9 выходных дефектов один из имеющихся в наборе видов дефекта. Блок 9 выходных дефектов форJ мирует выбранный дефект, и воздействует на соответствующий канал 5. После выполнения подготовки к контролю вычислительная система 1 задает тест на проверяемый узел 8 при наличии

введенного дефекта. Если вычислительная систама 1 при прохождении теста самоконтроля обнаруживает заданный дефект, то блок 12 памяти выдает следующий тестовый набор, задающий характер второго дефекта и т.д. Если

5 вычислительная система 1 при прохождении теста самоконтроля не обнаруживает заданный дефект, то корректируется сам тест самоконтроля. Затем устройство 3 повторяет приведенную

0 процедуру для всех последующих тестовых наборов. После завершения проверки устройство 3 повторяет указанную процедуру для всех контролируемых узлов 8 вычислительной системы 1.

5 Таким образом, за счет введения коммутатора 4, блока 9 выходных дефектов и дешифратора 10 устройство отладки тестов осуществляет комплексную отладку тестов самоконтроля вычислительной системы 1 при автоматической дистанционной имитации типовых дефектов различного вида в контролируемом узле 8, что повышает достоверность саглого контроля.

Формула изобретения

Устройство для отладки тестов,содержащее блок памяти, группа выходов

которого соединена с группой входов регистра, первая группа выходов которого соединена с группой входов первого коммутатораj отличающееся тем, что, с целью повьдаения достоверности контроля, в устройство введены первый и второй гщаптеры, блок входных воздействий, дешифратор и второй коммутатор, группа выходов которого соединена с группой входов первого адаптера, группа входов которюго является группой выходов устройства, первая группа входов второго коммутатора соединена с группой выходов первого коммутатора, вторая группа входов - через второй

адаптер с группой выходов контролируемого узла, третья группа входов через последовательно включенные блок выходных дефектов и дешифратор-со второй группой выходов регистра.

Источники информации,

принятые во внимание при экспертизе

Авторы

Даты

1981-08-30—Публикация

1979-04-04—Подача