Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для предварительной обработки операндов переменной длины | 1984 |

|

SU1269147A1 |

| Устройство для поиска информации на ленточном носителе | 1984 |

|

SU1208564A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| Микропроцессорное вычислительное устройство | 1982 |

|

SU1269145A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

| Процессор быстрого преобразования Фурье | 1986 |

|

SU1388892A1 |

| Процессор параллельной обработки | 1990 |

|

SU1797126A1 |

| Устройство для формирования гистограммы случайных чисел | 1988 |

|

SU1702391A1 |

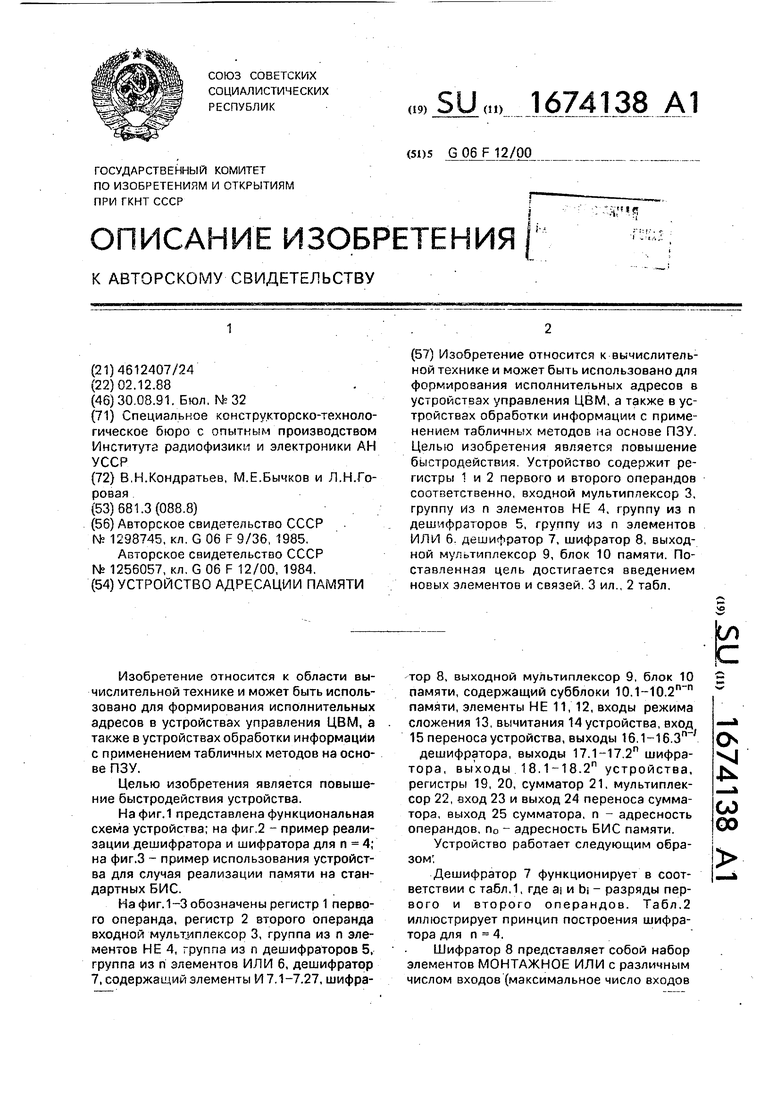

Изобретение относится к вычислительной технике и может быть использовано для формирования исполнительных адресов в устройствах управления ЦВМ, а также в устройствах обработки информации с применением табличных методов на основе ПЗУ. Целью изобретения является повышение быстродействия. Устройство содержит регистры 1 и 2 первого и второго операндов соответственно, входной мультиплексор 3, группу 4 из N элементов, группу 5 из N дешифраторов, группу 6 из N элементов ИЛИ, дешифратор 7, шифратор 8, выходной мультиплексор 9, блок 10 памяти. Поставленная цель достигается введением новых элементов и связей. 3 ил., 2 табл.

Изобретение относится к области вычислительной технике и может быть использовано для формирования исполнительных адресов в устройствах управления ЦВМ, а также в устройствах обработки информации с применением табличных методов на основе ПЗУ.

Целью изобретения является повышение быстродействия устройства.

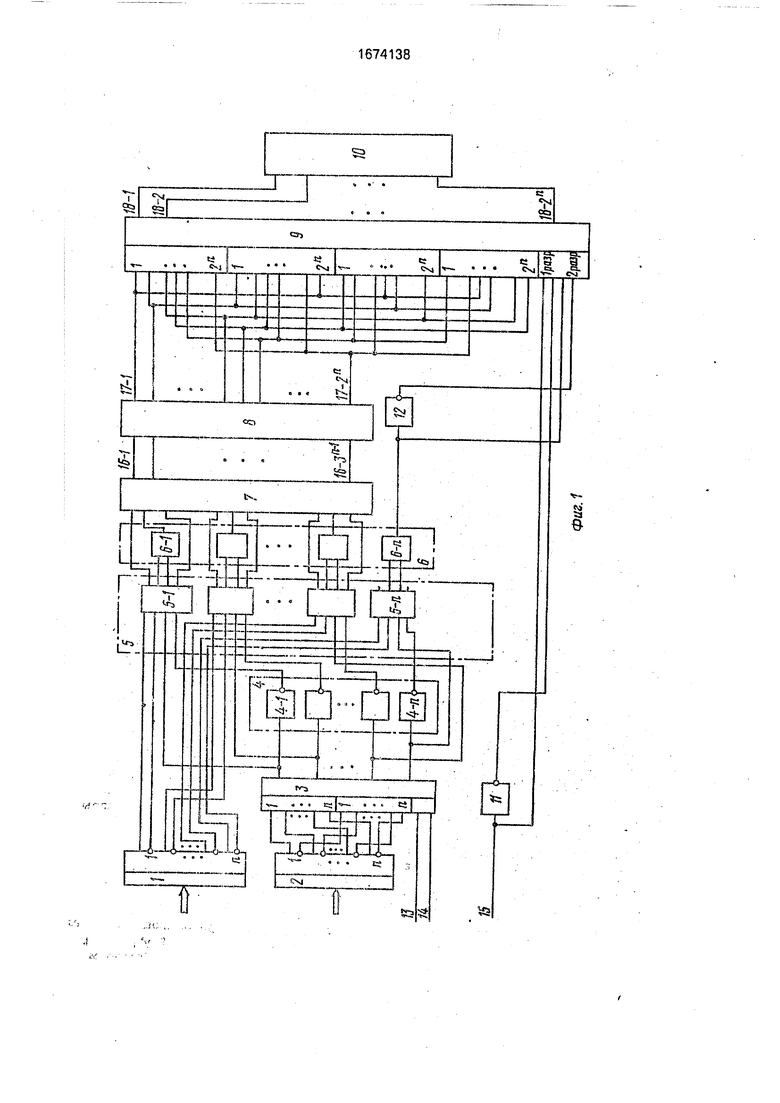

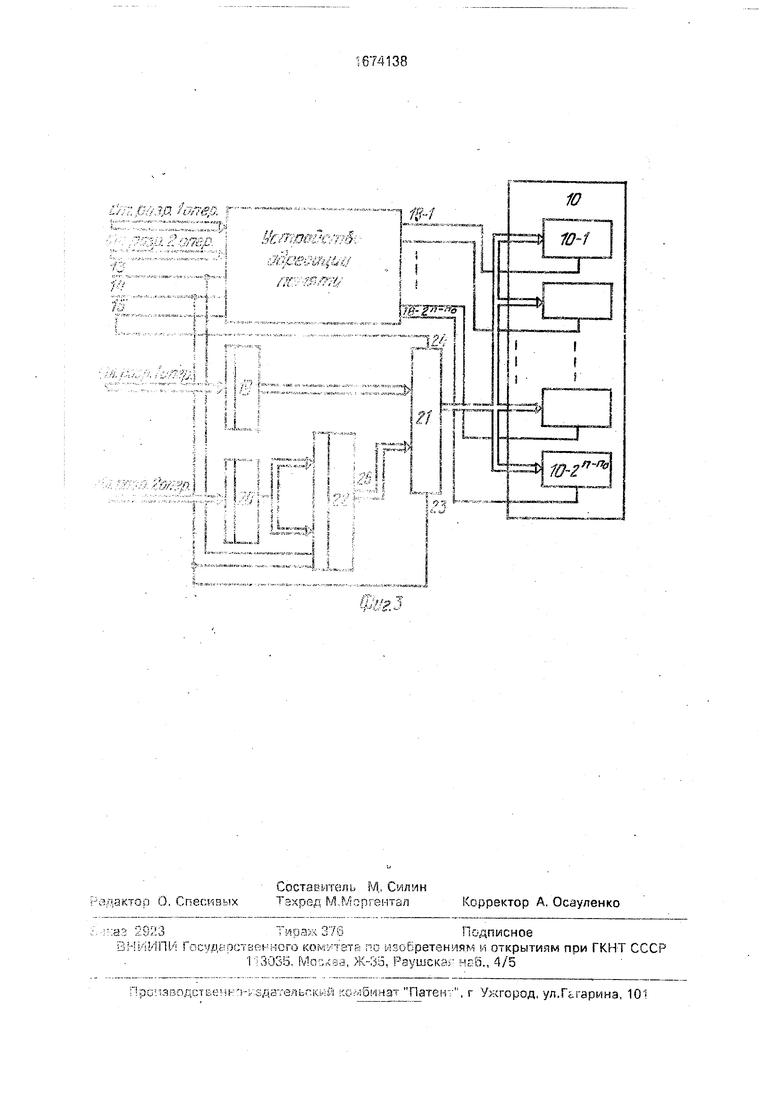

На фиг. 1 представлена функциональная схема устройства; на фиг.2 - пример реализации дешифратора и шифратора для п 4; на фиг.З - пример использования устройства для случая реализации памяти на стандартных БИС.

На фиг. 1-3 обозначены регистр 1 первого операнда, регистр 2 второго операнда входной мультиплексор 3, группа из п элементов НЕ 4, -руппа из п дешифраторов 5, группа из п элементов ИЛИ 6, дешифратор 7, содержаний элементы И 7.1-7.27, шифратор 8, выходной мультиплексор 9, блок 10 памяти, содержащий субблоки 10.1-10.2 памяти, элементы НЕ 11, 12, входы режима сложения 13, вычитания 14 устройства, вход 15 переноса устройства, выходы 16.1-16 дешифратора, выходы 17.1-172 шифратора, выходы 18.1-18.2 устройства, регистры 19, 20, сумматор 21, мультиплексор 22, вход 23 и выход 24 переноса сумматора, выход 25 сумматора, п - адресность операндов. п0 - адресность БИС памяти.

Устройство работает следующим образом:

Дешифратор 7 функционирует в соответствии с табл.1, где ai и bi - разряды первого и второго операндов. Табл.2 иллюстрирует принцип построения шифратора для п 4.

Шифратор 8 представляет собой набор элементов МОНТАЖНОЕ ИЛИ с различным числом входов (максимальное число входов

О

Ч|

Јь

СО 00

F(n), где F(i) - соответствующий член в последовательности чисел Фибоначчи)

В табл.2 представлены номера входов 16, объединенных по ИЛИ шифратора 8 Рассмотрим работу схемы, представленной на фиг.З, для случая, когда п0 - 10, п - 14 и необходимо выбрать код из блока памяти, адрес которого является разностью чисел А 10.111.010,110.001 и В 01.111, I 00,001.1 00. Блок 10 памяти будет в данном случае состоять из 16 субблоков 10-1. 10-16. При правильной работе схемы должен быть выбран код с адресом А-В - 00.111.110.100.101, те. код из субблока 10-4 с адресом 1,110.100.101. В соответствии с изложенным на регистрах 1 и 2 должны находиться коды 1011 и 0111 соответственно, на регистрах 19 и 20 соот ветственно коды 1.010.110.001 и 1.100.001.100, на вход0 13 должен находить- ся нулевой сигнал, на входе 14, а следовательно, и на входе 23 сумматора 21 - единичный код Единичнчи код на втором управляющем входе мультиплексора 22 пропустит инверсный код 0.011.110.011 ре гистра 20. В результате на информационных аходах сумматора 21 будут кодч 1.010.110.001 и 0.011.100 U01 на выходе которого с учетом единицы заносящейся в младший разряд сумматора по входу 23, по- явится сумма 1 110.100.101, а на вьиоде 24 сумматора, а также на входе 15 устройства будет нулевой код fob 1) Код 1.110 1 Hj 101, полученный ьа выходе 21, установится на входах дешифратора адреса всех субблоков 10-1 10-2, 10-2Г П В то же время в устройстве адресации памяти прямой 1011 и инверсный 0100 коды с регистра 1 поступают на соответствующие прямые и инверсные входы первого операнда группы 5 дешифратора. Инверсный код 1000с реги- стра 2 поступает через мультиплексор 3 на прямые входы второго операнда труппы 5 дешифраторов, а также на групг) 4 ишхр- торов, с выходов которых код 0111 -.ncivna- ет на соответствующие инверсные входы второго операнда группы 5 дешифраторов. В результате на выходе дешифратора 5-1 будет находиться код 1001, на входе дешифратора 5-2 - код 1001, дешифратора 5 3 - 0101 и на входе дешифратора 5-4 - 1010. Предполагается, что старшему четвертому разряду кода на пходе дешифратора из группы 5 г.оответстауст прямой вход разряда первого операнда, третьему разряд-; ко- да - инверсный вход разряда первого операнда, второму - прямой вход разряда второго операнда и первому - иноерсиый код разряда первого операнда, Пр i этом первым младшим разрядом кода регистров

1 и 2 соответствует дешифратор 5-1, вторым разрядам регистров - дешифратор 5-2, третьим 5-3 и четвертым - дешифратор 5- 4. Toifla на выходах дешифраторов 5-1, 5-2, 5-3 и 5-4 установятся копы 0100.0100,0001 и 1000 (соответственно прямым кодам первого и второго оперс ша 10 10,00 и 11), а на выходах схем ИЛИ G 1,6 2, 6-3 и 6 -4 - коды 1,1,00 соответственно. В результате на входе пирвого разряда де шифратора 7 установится комбинация 010 вторите 010 и третьего 100 (порядок следование разрядов ода соогветгтьует -аЬя.1). Гггласно схеме с| иг 2 и табл.2 на дешифратора 7 в единичном состоянии буде находился выход и соответственно г-чход 17-13 шифратора 8 Нулевой м.нал влодс) 1Ь и i1, ЛОРОЙ (и.нчл со с-омч ИЛИ Ь 4 через ,0ui raidьуюии г „ к. ш-ч I-IL 11 ч 12 уста- noh.li мультиплексор 0 в сое JHI-MC, соответствующее про кдению информации и .ход пу/итиплекс а П| РЗ ъго четвертую rovriny информационных входов ТР (спас- но и /юженному на i нходе Г1у,ьтпплв чсоря 9 будет пнГ iP 4 R результате из (тюка 10 сигна Ом выборки кристалла с вы- уогл 1Я 4 вгп--;- субблок 10-4, из которого лрийде- ьь борка кода с адресом 1 110 100.101 кзк это и требуется Формула изобретения Устройство адресации памяти, содер- речтсгр первого операнда, регистр второго оп«ран,,э группу из п дешифраторов, дешифратор, шифратор, оькодной мультиплексор, отличающееся тем, что с цел ю повышения быстродействия, в icro введен г годной мультиплексор, группу из ч эдеме чтон НЕ, группу из п элементов ИЛИ, два элемента НЕ, примем прямые и инверсные выходы разрядов регистра первого операнда соединены с прямыми и инверсными входами первых разрядов соответствующих дешифраторов группы из и дешифраторов, прямые и инверсные выходы разрядов регистра (второго операнда соединены СООТВСТСТВРННО с первой и второй группами информационных входов входно- п мультиплексора, выходы входною мультиплексора соединены с прямыми входами вторых разрядов соответствующих дешифраторов группы из п дешифраторов и с соответствующими элементами НЕ группы из п элементов hL, вихог/ы к торых подключены к инв«рсн;- М L .OMOM вторых разрядов соответствующих дешифраторов группы из п дешифратороп, первые и выходы (п-1) дешифраторов группы из п дешифраторов, выходы п -1 --лсментсв ИЛИ группы i 5 п элементов ИЛИ соединены соогветст- енно с пepoы и, вторыми и ipe-ьпмл зходами соответствующих трехпозиционных разрядов дешифратора, Зп выходов которого подключены к соответствующим входам шифратора, третьи выходы п дешифраторов группы из п дешифраторов подключены соответственно к первым входам соответствующих п элементов ИЛИ группы из п элементов ИЛИ, вторые входы которых подключены соответственно к четвертым выходам п дешифраторов группы из п дешифраторов, входы режима сложения и вычитания устройства подключены соответственно к первому и второму управляющим входам входного мультиплексора, вход переноса устройства соединен с прямым вхо- дом первого разряда управляющего входа выходного мультиплексора и входом первого элемента НЕ, выход которого подключен к инверсному входу первого разряда управляющего входа выходного мультиплексора, выход п-го элемента ИЛИ группы из п элементов ИЛИ подключен к прямому входу второго разряда управляющего входа выходного мультиплексора и к входу второго элемента НЕ, выход которого подключен к инверсному входу второго разряда управляющего входа выходного мультиплексора, 1-й

выход шифратора для i 12П соединен с

i-м входом первой группы информационных входов выходного мультиплексора, i-й выход шифратора для I 22П соединен с

(1-1)-м входом второй группы информационных входов выходного мультиплексора, первый выход шифратора подключен ко 2п-му входу из второй группы информационных входов выходного мультиплексора, 1-й выход шифратора для i соединен с

1}-м входом третьей группы информа0+2

ЦИ01

ра, а для i 2r

ционных входов выходного мультиплексо1ПЧ-М2П 1-й выход шифратора

соединен с ()-м входом третьей группы информационных входов выходного мультиплексора. i-й выход шифратора для

i 12пИ+1 соединен с (Н2П 1)-м, а

для i - 2п 1+22П - с ()-м входом четвертой группы информационных входов выходного мультиплексора, выходы которого подключены к выходам устройства, первый и второй информационные входы устройства подключены соответственно к информационным входам регистров первого и второго операндов.

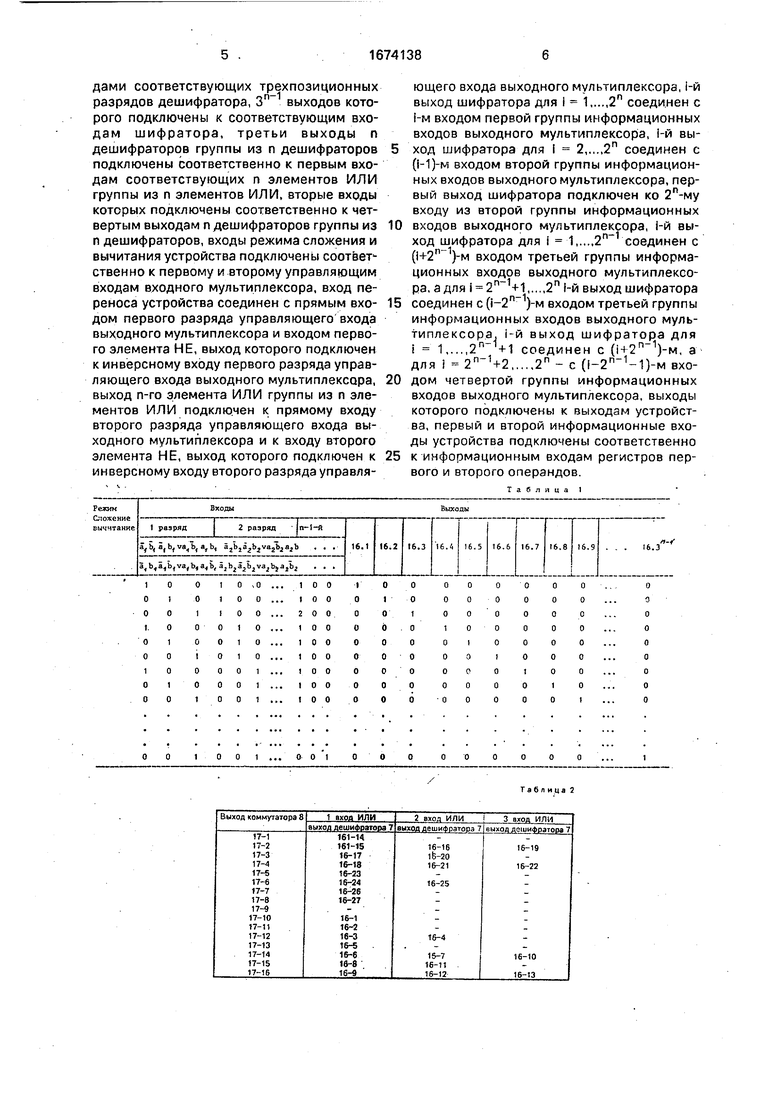

Т а б л л и а 1

Таблица 2

I

N

8GlNL9i

| Авторское свидетельство СССР Мг 1198745, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для поиска информации на микрофильме | 1985 |

|

SU1256057A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1991-08-30—Публикация

1988-12-02—Подача